# Using Feature Set of I<sup>2</sup>C Master on SimpleLink™ MSP432E4 Microcontrollers

Amit Ashara MSP Applications

#### **ABSTRACT**

The inter-integrated circuit (I<sup>2</sup>C) is a multiple-master, multiple-slave, single-ended bus that is typically used for attaching lower-speed peripheral ICs to processors and microcontrollers. The type of slave devices range from nonvolatile memory to data-acquisition devices like analog-to-digital converters (ADC), sensors, and so forth. This application report demonstrates how to use the feature rich I2C master on the SimpleLink™ MSP432E4 microcontrollers to communicate with a host of slave devices in a system.

Project collateral and source code discussed in this document are available in the SimpleLink™ MSP432E4 Software Development Kit (SDK).

#### **Contents**

| 1  | Introduction                                                         | 2  |

|----|----------------------------------------------------------------------|----|

| 2  | Overview of I <sup>2</sup> C Protocol                                |    |

| 3  | Circuit Schematic for Example Code                                   | 6  |

| 4  | Basic I <sup>2</sup> C Controller Initialization                     |    |

| 5  | I <sup>2</sup> C Master Function: Interrupt, μDMA and FIFO Operation |    |

| 6  | I <sup>2</sup> C Glitch Filter Capability                            |    |

| 7  | Conclusion                                                           |    |

| 8  | References                                                           | 18 |

|    | List of Figures                                                      |    |

| 1  | Open-Drain Circuit                                                   | 2  |

| 2  | Address Phase ACK                                                    | 4  |

| 3  | Address Phase NAK                                                    | 4  |

| 4  | Data Frame Write                                                     | 5  |

| 5  | Data Frame Read                                                      | 6  |

| 6  | Circuit Schematic                                                    |    |

| 7  | I2CMSA and Slave Address Representation                              | 9  |

| 8  | I <sup>2</sup> C Transaction for I2C_MASTER_CMD_SINGLE_SEND          | 11 |

| 9  | I <sup>2</sup> C Transaction for I2C_MASTER_CMD_BURST_SEND_START     | 11 |

| 10 | I <sup>2</sup> C Transaction for I2C_MASTER_CMD_BURST_SEND_CONT      | 11 |

| 11 | I <sup>2</sup> C Transaction for I2C_MASTER_CMD_BURST_SEND_FINISH    | 11 |

| 12 | I <sup>2</sup> C Transaction for I2C_MASTER_CMD_SINGLE_RECEIVE       | 12 |

| 13 | I <sup>2</sup> C Transaction for I2C_MASTER_CMD_BURST_RECEIVE_START  | 12 |

| 14 | I <sup>2</sup> C Transaction for I2C_MASTER_CMD_BURST_RECEIVE_CONT   | 12 |

| 15 | I <sup>2</sup> C Transaction for I2C_MASTER_CMD_BURST_RECEIVE_FINISH | 12 |

| 16 | Transmit With CPU and Non FIFO                                       | 13 |

| 17 | Receive With CPU and Non FIFO                                        | 13 |

| 18 | Transmit With CPU and FIFO                                           | 14 |

SimpleLink, LaunchPad are trademarks of Texas Instruments. All other trademarks are the property of their respective owners. 2

#### 1 Introduction

The SimpleLink MSP432E4 family of devices from Texas Instruments integrates up to 10 independent I<sup>2</sup>C modules with the following features:

- I<sup>2</sup>C module with independent master and slave blocks on the same bus without requiring additional pins for separate master and slave functions

- Integrated 8-byte-deep FIFO for transmit and receive operations that can be independently assigned to either master or slave block

- Efficient transfer mechanism using µDMA and FIFO that reduces CPU overhead during large data transfers

- Independent µDMA channel for Transmit and Receive operations

- Programmable glitch suppression capability in terms of system clocks which meets the standard requirements

- · Support for standard, fast, fast plus, and high-speed modes through configurable timer register

- Support for arbitration and clock stretching during master mode initiated transactions

- Support for SMBus clock low time-out, dual-slave address, and quick command features

- · Highly configurable interrupt mechanism to reduce dependency on polling mechanism

#### 2 Overview of I<sup>2</sup>C Protocol

Before the use of I<sup>2</sup>C on the MSP432E4 devices is described, it is important that some of the basic concepts of the I<sup>2</sup>C protocol and bus are described first. This aids the understanding of the protocol and the debugging issues on the physical bus using an oscilloscope or a logic analyzer.

The description is kept concise from the understanding perspective. For more information, see the UM10204: I<sup>2</sup>C-Bus Specification and User Manual.

# 2.1 Physical Layer of &C

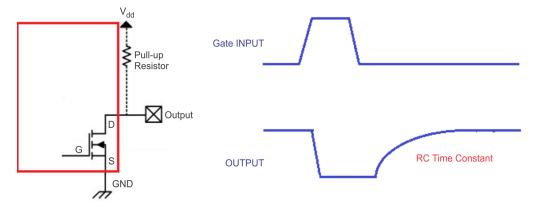

The I<sup>2</sup>C bus consists of two signals: serial clock (SCL) and serial data (SDA). At the I/O level, both SCL and SDA are open-drain (see Figure 1).

Figure 1. Open-Drain Circuit

www.ti.com Overview of FC Protocol

The output transistor drives low to create a logical 0 on the bus. The output transistor is off to float the pin to create a logical 1 on the bus. Hence, an external pullup to VDD is required. The value of the pullup resistor depends on the bus capacitance and the sink current as established by the I<sup>2</sup>C specification. The open-drain configuration is required because the bus is bidirectional; if one device on the bus transmits a logical 0 and another device transmits a logical 1, this condition does not create an electrical contention that could damage the I/O. Instead, a current path is established from the device transmitting a logical 1 to the device transmitting a logical 0 through the pullup resistor.

The important positive consequence of this are:

- Multiple devices can place a different logical value and not damage the other devices due to excessive current flow. It also has an effect on the workings of the I<sup>2</sup>C bus itself.

- When this concept is applied to SCL, it provides the slave a mechanism for stretching the clock and establishes a form of flow control.

- When this concept is applied to SDA, it allows the master to detect another master, which is called bus arbitration.

The important negative consequence of this are:

- The rise time of the SCL and SDA are no longer a function of the drive strength but are defined by the RC time constant, where R is the value of the pullup resistor and C is the value of the parasitic and load capacitance on the bus. This limits the speed of operation.

- The speed of operation requires that the R value be decreased to reduce the RC time constant as parasitic and load capacitance cannot be changed readily, thereby, increasing the current through the R when a logical 0 is applied from a device affecting the current drain on portable power devices.

# 2.2 Communication Layer of fC

The I<sup>2</sup>C bus communicates using the timing of the SCL and SDA; however, there are some concepts that need to be defined first.

- Bus idle: The idle state of a bus is defined when both SCL and SDA are high.

- START bit: The START bit of a I<sup>2</sup>C frame is defined as SDA driven low while SCL is high.

- STOP bit: The STOP bit of an I<sup>2</sup>C frame is defined as SDA pulled high while SCL is high.

All bits are signaled between a start and stop bit. Any bit being transmitted by a device (master or slave) is SCL being pulled high and then driven low (pulsing) with the SDA kept at a steady state. It is invalid in I<sup>2</sup>C for the SDA to change when the SCL is high other than for a START or STOP bit.

Data is always exchanged in a 9-bit format, in which 8 bits are used for data exchange and 1 bit is used for acknowledging the transmission by the receiver of the data. The receiver can be a master or a slave.

#### 2.2.1 Address Frame

The first part of an I<sup>2</sup>C frame is called the address frame where the master presents a slave address. The address frame is comprised of a 7-bit slave address, the 8th bit indicates the direction of transfer and the 9th bit is used to acknowledge the transfer.

When the 8th bit is logical 0, the direction of data is from master to slave and is referred to as master transmit or write and when it is logical 1, the direction of data is from slave to master and is referred to as master receive or read.

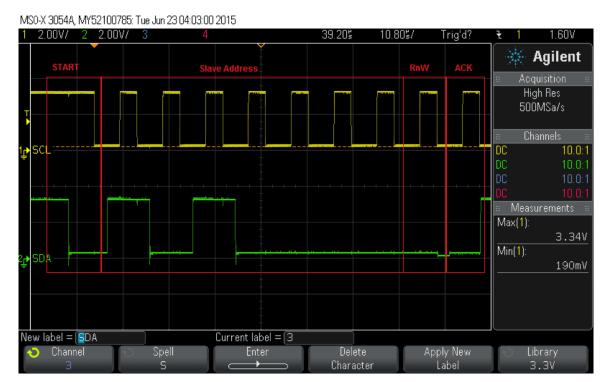

The 9th bit is called the acknowledge bit (ACK) and is used by the device receiving the data to indicate it is ready to accept the address. As shown in Figure 2 for the slave address 0x50, which exists on the bus, the slave device drives the bus logical 0, which indicates to the master that it is ready to move to the data frame.

Overview of f C Protocol www.ti.com

Figure 2. Address Phase ACK

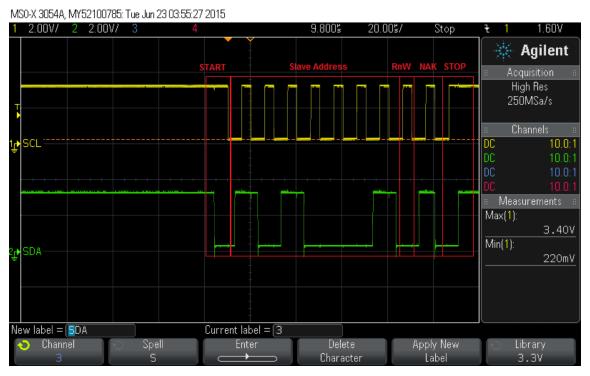

If the slave address does not exist on the bus, then the master reads back a logical 1 (also called NAK) and terminates the transfer with a STOP bit as shown in Figure 3. In some cases, slave devices use the ACK bit to indicate its readiness for further transaction.

Figure 3. Address Phase NAK

www.ti.com Overview of fC Protocol

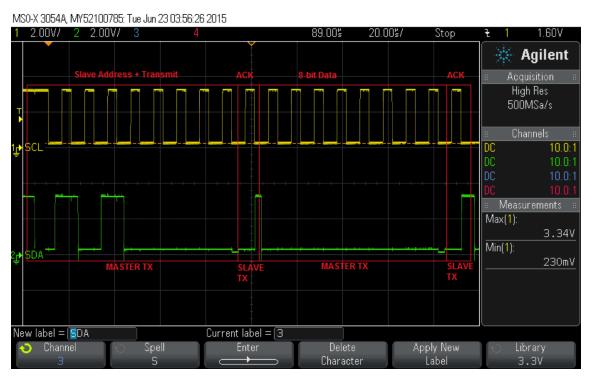

#### 2.2.2 Data Frame Write

After the address frame, the next frame to be sent is the data frame (called a write operation) if a logical 0 is sent in the 8th bit of the address frame. The direction of the transfer is from master to slave for the 8 bits of data frame to follow. The 9th bit is the ACK bit for the data frame and the direction of this bit is from slave to master. If the slave cannot accept the data, it should send a logical 1. The master should stop the 1<sup>2</sup>C frame and the bus must return to idle state. If the slave accepts the data, it should send a logical 0 and the master can send the next byte, stop the frame, or change the direction of the bus using repeated start.

Figure 4. Data Frame Write

#### 2.2.3 Data Frame Read

After the address frame, the next frame to be sent is the data frame (called a read operation) if a logical 1 is sent for the 8th bit in the address frame. The direction of the transfer is from slave to master for the 8 bits of data. The 9th bit is the ACK bit for the data frame and the direction of this bit is from master to slave. If the master cannot accept the data, it should send a logical 1, the master should issue a STOP condition on the I<sup>2</sup>C frame and the bus should return to idle state. If the master accepts the data, it should send a logical 0 and the master can accept the next byte.

Figure 5. Data Frame Read

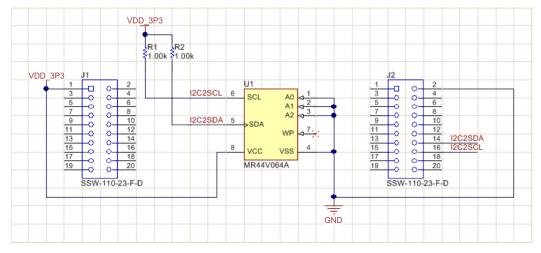

# 3 Circuit Schematic for Example Code

This section discusses the schematic for the slave device (LAPIS semiconductor MR44V064A), which has been used for development of the code examples. The slave device has been interfaced on header 1 (for connection of a BoosterPack plug-in module) on the MSP-EXP432E401Y LaunchPad™ development kit.

Figure 6. Circuit Schematic

#### Basic I<sup>2</sup>C Controller Initialization

NOTE: The I<sup>2</sup>C controller initialization examples that have been described will be I<sup>2</sup>C module instance I2C2 for the master function. Other I2C instances may be used, but the user must see the following section to ensure that the other instances are properly initialized.

To use the I<sup>2</sup>C module on the MSP432E4 family of devices, application peripheral interfaces (APIs) must be called from the SimpleLink MSP432E SDK to correctly initialize the I<sup>2</sup>C module.

Two distinct sets of APIs are required before any operation of the I<sup>2</sup>C controller for the master function is configured:

- Configuring the IOs for I<sup>2</sup>C (see Section 4.1)

- Configuring the I<sup>2</sup>C controller (master function) (see Section 4.2)

When the initialization has been completed, only the I<sup>2</sup>C API can be called to perform data transfers from the master function for which the following operations are important:

- Addressing a slave from the I<sup>2</sup>C master for transmit or receive operations (see Section 4.3)

- Applying the correct command to the I<sup>2</sup>C master for transmit or receive operations (see Section 4.4)

#### Configuration of IOs 4.1

The first step of configuration is to enable and configure the GPIOs corresponding to the SCL and SDA of the I<sup>2</sup>C module. The master and slave I<sup>2</sup>C modules are configured in the same manner. All I<sup>2</sup>C instances use the same API for configuration, except for the parameters passed to the API, which are instance specific.

#### **Code Flow:**

- Enable the clock to the corresponding GPIO module using MAP\_SysCtlPeripheralEnable and wait for the peripheral ready using MAP\_SysCtlPeripheralReady.

- Call the MAP GPIOPinConfigure API to configure the SCL and SDA port mux for the specific GPIO port and pin.

- Call the MAP\_GPIOPinTypel2C API to configure the SDA in open-drain mode, digital enable, and alternate function select in the GPIO port for corresponding SDA pin.

- Call the MAP GPIOPinTypel2CSCL API to configure the SCL for digital enable and alternate function select in the GPIO port for the corresponding SCL pin. The open-drain behavior is controlled by the I2C controller; hence, it must not be set in the GPIO Open Drain Select (GPIOODR) register.

```

/* Enable GPIO for Configuring the I2C Interface Pins */

MAP_SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOL);

/* Wait for the Peripheral to be ready for programming */

while(!MAP_SysCtlPeripheralReady(SYSCTL_PERIPH_GPIOL));

/* Configure Pins for I2C2 Master Interface */

MAP_GPIOPinConfigure(GPIO_PL1_I2C2SCL);

MAP_GPIOPinConfigure(GPIO_PL0_I2C2SDA);

MAP_GPIOPinTypeI2C(GPIO_PORTL_BASE, GPIO_PIN_0);

MAP_GPIOPinTypeI2CSCL(GPIO_PORTL_BASE, GPIO_PIN_1);

```

# 4.2 Configuring the fC Controller (Master Function)

The next step is configuring the I<sup>2</sup>C controller master function. Some examples of the I<sup>2</sup>C controller may use a polling mechanism, but this application report emphasizes the use of interrupts instead of polling.

#### Code Flow:

On MSP432E4 devices, there is no System Control API to report the clock frequency.

1. Use the MAP\_SysCtlClockFreqSet API, or hard code a variable with the value of 16 MHz, because the default clock after power up is a 16-MHz precision oscillator (PIOSC). The clock frequency is required by the I<sup>2</sup>C API to compute the divider to generate the final I<sup>2</sup>C SCL clock frequency for different modes of operation.

Disable the clock, reset the I<sup>2</sup>C master module and then enable the clock to the I<sup>2</sup>C master module using the MAP\_SysCtlPeripheralDisable, MAP\_SysCtlPeripheralReset and MAP\_SysCtlPeripheralEnable APIs. Then, wait for the peripheral ready using MAP\_SysCtlPeripheralReady. This step is required to ensure that any stale state of the bus or the master function (due to a previous run) is removed.

```

/* Stop the Clock, Reset and Enable I2C Module in Master Function */

MAP_SysCtlPeripheralDisable(SYSCTL_PERIPH_I2C2);

MAP_SysCtlPeripheralReset(SYSCTL_PERIPH_I2C2);

MAP_SysCtlPeripheralEnable(SYSCTL_PERIPH_I2C2);

/* Wait for the Peripheral to be ready for programming */

while(!MAP_SysCtlPeripheralReady(SYSCTL_PERIPH_I2C2));

```

3. Call the MAP\_I2CMasterInitExpClk API to configure the I²C master function for the correct SCL clock frequency. The API uses the I²C base address as the first parameter, the system clock as the second parameter and, based on true or false in the last parameter, configures the SCL clock frequency for 100 kHz or 400 kHz. If the system clock is high enough to support high-speed mode, it will configure the high-speed dividers as well.

```

/* Initialize and Configure the Master Module */

MAP_I2CMasterInitExpClk(I2C2_BASE, ui32SysClock, false);

```

4. Enable the interrupt sources by setting the corresponding bits in the I<sup>2</sup>C master function Interrupt Mask Register. Use the *MAP\_I2CMasterIntEnableEx* API, whose first parameter is the I<sup>2</sup>C base address and then the interrupt bits.

5. Enable the interrupt line from the I<sup>2</sup>C master function to the NVIC using the MAP\_IntEnable API.

```

/* Enable the Interrupt in the NVIC from I2C Master */

MAP_IntEnable(INT_I2C2);

```

# 4.3 Addressing an fC Slave in MSP432E4

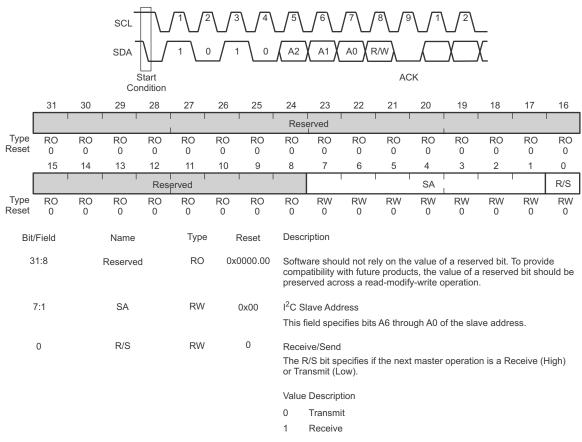

The I<sup>2</sup>C master function uses the *MAP\_I2CMasterSlaveAddressSet* API to set the address of the slave device. The first parameter is the I<sup>2</sup>C base address for the master function, the second parameter is the external slave address (which is explained in detail using the example below) and the third parameter is the direction of transfer. The third parameter is set to "true" for a read operation or "false" for a write operation. In the following example, a call of the function is shown to access a slave device with the slave address as 0x50. Use Figure 7 to calculate the value.

The top part of Figure 7 shows the address phase as expected by the external slave device for which it would ACK the address phase, and the bottom part shows the I²C Master Slave Address (I2CMSA) register information from the MSP432E4 SimpleLink™ Microcontrollers Technical Reference Manual. The bits shown as A2, A1, and A0 are based on the tie off done for the slave device pins, which are connected to GND. Therefore, the binary address as expected by the slave device is 1010000. This sequence in hexadecimal format is 0x50.

In the MSP432E4 I2CMSA register, the address bits appear in bit position 7 to 1. The *I2CMasterSlaveAddressSet* API shifts the slave address to the correct position in the register.

Figure 7. I2CMSA and Slave Address Representation

#### Data Transfer Commands for fC Master in MSP432E4

The I<sup>2</sup>C master has two modes of operation. In the first mode of operation the CPU or DMA can use the I<sup>2</sup>C Master Data (I2CMDR) register to write data to a slave or read data from a slave using a single byte buffer. While the absolute address of the I2CMDR register is programmed in the control structure of µDMA, for the CPU to access the data register there are two APIs that are available.

- MAP 12CDataPut is used to write data to a slave during a transmit operation. The first parameter is the I<sup>2</sup>C base address, and the second parameter is the data that must be transmitted

- MAP\_I2CDataGet is used to read data from a slave during a receive operation. The first parameter is the I<sup>2</sup>C base address, and the function returns the data read from the I2CMDR register.

The example codes of i2c\_master\_cpu\_nonfifo (see Section 5.1) and i2c\_master\_hs (see Section 5.4) uses the first mode of data transfer.

The second mode of operation uses the I<sup>2</sup>C FIFO Data Register (I2CFIFODATA) to write data to a slave or read data from a slave using the FIFO. As with the first mode, the absolute address of the I2CFIFODATA is programmed in the control structure of the µDMA for DMA based transfers. For the CPU to access the data register, there are four APIs that are available.

- MAP I2CFIFODataPut is used to write data to the TX FIFO in blocking mode. The API uses the first parameter of the I<sup>2</sup>C base address to polls the corresponding I<sup>2</sup>C FIFO Status Register (I2CFIFOSTATUS) to see if there is space available in the TX FIFO: if at least one byte space is available, the data then writes the second parameter to the I2CFIFODATA register.

- MAP I2CFIFODataPutNonBlocking is used to write data to the TX FIFO in non-blocking mode. The API uses the first parameter of the I<sup>2</sup>C base address to check the corresponding I2CFIFOSTATUS register to see if there is space available in the TX FIFO and writes the second parameter to the I2CFIFODATA register. The API returns 0 if there is no space available (so it can be retried at a later time) or returns 1 if the space was available and the data was written to the I2CFIFODATA register.

- MAP I2CFIFODataGet is used to read data from the RX FIFO in blocking mode. The API uses the first parameter of the I<sup>2</sup>C base address to poll the corresponding I2CFIFOSTATUS register to see if there is data available in the RX FIFO; if at least one byte is available for read, the data is returned by the

- MAP I2CFIFODataGetNonBlocking is used to read data from the RX FIFO in non-blocking mode. The API uses the first parameter of the I<sup>2</sup>C base address to check the corresponding I2CFIFOSTATUS register to see if there is data available in the RX FIFO, and writes the data read from the IZCFIFODATA into the buffer pointed by the second parameter. The API returns 0 if there is no data available (so it can be retried at a later time) or returns 1 if the data was available and was read from the I2CFIFODATA register.

The example codes of i2c master cpu fifo (see Section 5.2) use the second mode of data transfer in non-blocking mode.

#### Commanding Operation of the f C Master 4.5

The I<sup>2</sup>C master function uses the I<sup>2</sup>C Master Control/Status (I2CMCS) register for performing any bus transaction. This register is a write-only register, and read of this register returns the status of the I<sup>2</sup>C master function. Thus, if a user writes to the register in the application code, it does not read back the last command for the I<sup>2</sup>C master function, but instead it reads back the status of the I<sup>2</sup>C master function resulting from the command.

The i2c.h file defines the different commands that can be sent to the I<sup>2</sup>C master function. From an application code perspective, there are eight major commands that the application can use to control the nature of the transaction from the I<sup>2</sup>C master.

Copyright © 2017, Texas Instruments Incorporated

#### 4.5.1 I<sup>2</sup>C Transmit Command: I2C MASTER CMD SINGLE SEND

This command is used when the I<sup>2</sup>C master function is required to write one byte of data to a slave. As shown in Figure 8 when the I2C\_MASTER\_CMD\_SINGLE\_SEND command is sent, the I<sup>2</sup>C master function sends the start bit (S), slave address of 0x50 with Write Bit clear, transmits the data written to the I2CMDR and sends the stop bit (P).

Figure 8. I<sup>2</sup>C Transaction for I2C\_MASTER\_CMD\_SINGLE\_SEND

#### 4.5.2 I<sup>2</sup>C Transmit Command: I2C MASTER CMD BURST SEND START

This command is used when the I<sup>2</sup>C master function is required to write one byte of data to a slave and own the bus. As shown in Figure 9 when the I2C\_MASTER\_CMD\_BURST\_SEND\_START command is sent, the I<sup>2</sup>C master function sends the start bit (S), slave address of 0x50 with Write Bit clear, transmits the data written to the I2CMDR and holds the bus low for further operations.

Figure 9. I<sup>2</sup>C Transaction for I2C\_MASTER\_CMD\_BURST\_SEND\_START

#### 4.5.3 I<sup>2</sup>C Transmit Command: I2C MASTER CMD BURST SEND CONT

This command is used when the I<sup>2</sup>C master function is required to an additional byte of data to a slave when it owns the bus. As shown in Figure 10 when the I2C\_MASTER\_CMD\_BURST\_SEND\_CONT command is sent, the I<sup>2</sup>C master function transmits the data written to the I2CMDR and holds the bus low for further operations.

Figure 10. I<sup>2</sup>C Transaction for I2C\_MASTER\_CMD\_BURST\_SEND\_CONT

#### 4.5.4 I<sup>2</sup>C Transmit Command: I2C MASTER CMD BURST SEND FINISH

This command is used when the I<sup>2</sup>C master function is required to write one byte of data to a slave and release the bus. As shown in Figure 11 when the I2C\_MASTER\_CMD\_BURST\_SEND\_FINISH command is sent, the I<sup>2</sup>C master function transmits the data written to the I2CMDR and sends the stop bit (P).

Figure 11. I<sup>2</sup>C Transaction for I2C\_MASTER\_CMD\_BURST\_SEND\_FINISH

#### 4.5.5 I<sup>2</sup>C Receive Command: I2C MASTER CMD SINGLE RECEIVE

This command is used when the I<sup>2</sup>C master function is required to read one byte of data from a slave. As shown in Figure 12 when the I<sup>2</sup>C\_MASTER\_CMD\_SINGLE\_RECEIVE command is sent, the I<sup>2</sup>C master function sends the start bit (S), sets the slave address of 0x50 with Write Bit, receives the data from the slave, writes it to the I<sup>2</sup>CMDR, asserts a NAK to indicate to the slave that the transaction is completed and sends the stop bit (P).

Figure 12. I<sup>2</sup>C Transaction for I2C\_MASTER\_CMD\_SINGLE\_RECEIVE

#### 4.5.6 I<sup>2</sup>C Receive Command: I2C MASTER CMD BURST RECEIVE START

This command is used when the I²C master function is required to read one byte of data from a slave and own the bus. As shown in Figure 13 when the I2C\_MASTER\_CMD\_BURST\_RECEIVE\_START command is sent, the I²C master function sends the start bit (S), sets the slave address of 0x50 with Write Bit, receives the data from the slave, sends the data byte for ACK, writes the data to the I2CMDR and holds the bus for further operations.

Figure 13. I<sup>2</sup>C Transaction for I2C\_MASTER\_CMD\_BURST\_RECEIVE\_START

# 4.5.7 I<sup>2</sup>C Receive Command: I2C\_MASTER\_CMD\_BURST\_RECEIVE\_CONT

This command is used when the  $I^2C$  master function is required to read one byte of data from a slave when it owns the bus. As shown in Figure 14 when the  $I^2C$ \_MASTER\_CMD\_BURST\_RECEIVE\_CONT command is sent, the  $I^2C$  master function receives the data from the slave, sends ACK for the data byte, writes it to the  $I^2C$  and holds the bus for further operations.

Figure 14. I<sup>2</sup>C Transaction for I2C MASTER CMD BURST RECEIVE CONT

#### 4.5.8 I<sup>2</sup>C Receive Command: I2C\_MASTER\_CMD\_BURST\_RECEIVE\_FINISH

This command is used when the I<sup>2</sup>C master function is required to read one byte of data from a slave when it owns the bus and then release the bus. As shown in Figure 15 when the I2C\_MASTER\_CMD\_BURST\_RECEIVE\_FINISH command is sent, the I<sup>2</sup>C master receives the data from the slave, sends a NAK to indicate that the transaction has completed and sends the stop bit (P).

Figure 15. I<sup>2</sup>C Transaction for I2C\_MASTER\_CMD\_BURST\_RECEIVE\_FINISH

Copyright © 2017, Texas Instruments Incorporated

# 5 I<sup>2</sup>C Master Function: Interrupt, μDMA and FIFO Operation

The I<sup>2</sup>C master supports both the polling and interrupt driven mechanisms for performing bus transactions. While the polling mechanism is simpler, the action of polling requires precious CPU cycles performing status checks. The MSP432E4 family of devices now supports an exhaustive interrupt mechanism that an application code may use to free precious CPU clocks for other device activities.

The MSP432E4 family of devices includes an 8-byte deep transmit and receive FIFO with configurable trigger threshold. The FIFO enables the CPU to setup a bulk transfer with fewer interrupts per I<sup>2</sup>C transactions leaving the CPU for other device activities.

The FIFO can be coupled with the efficient µDMA so that the CPU can be notified of a transaction completion, thus, reducing the overall CPU clocks managing a data transaction.

The code examples in the following subsections illustrate each of the features so that the application developer can leverage the I<sup>2</sup>C features of the MSP432E4 devices for improving overall CPU bandwidth for essential system functions.

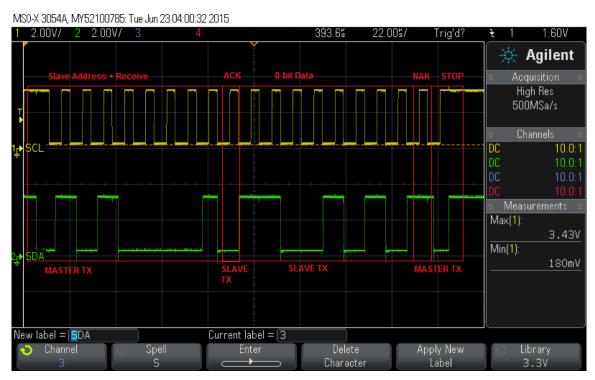

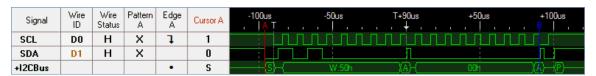

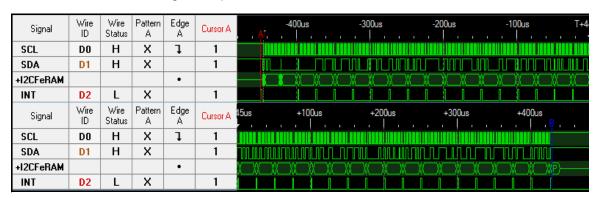

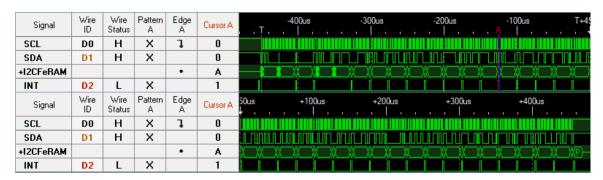

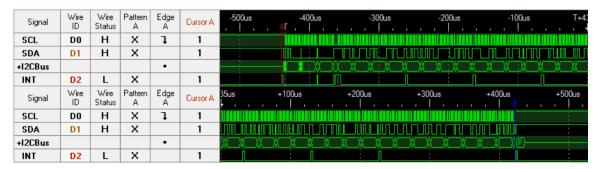

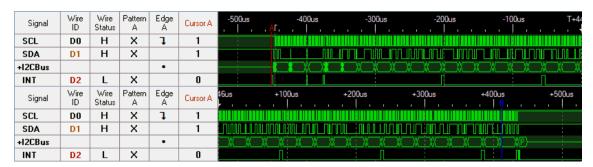

Each of the code examples mentioned below have logic analyzer captures associated with them, which shows both transmit and receive plots. The plot contains the SCL and SDA IO for the I<sup>2</sup>C master function and a GPIO toggle for interrupt, which is made high when the interrupt handler is called and made low on exit.

#### 5.1 Master Function for CPU With Non-FIFO Transaction

*i2c\_master\_cpu\_nonfifo* is a simple code example in which the CPU uses the traditional I2CMDR to access the slave for write and read operations with interrupts.

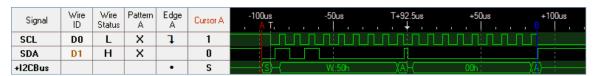

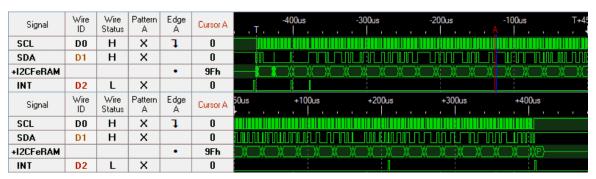

Figure 16 and Figure 17 show the transmit and receive operations. As can be seen for every data transaction, the CPU is being interrupted.

Figure 16. Transmit With CPU and Non FIFO

Figure 17. Receive With CPU and Non FIFO

#### 5.2 Master Function for CPU With FIFO

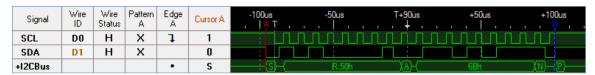

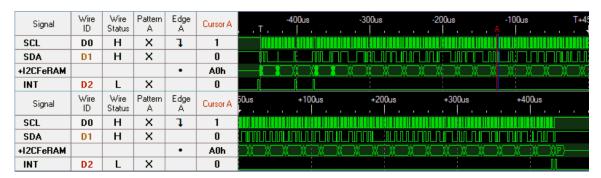

*i2c\_master\_cpu\_fifo* is a simple code example in which the CPU uses the I2CFIFODATA to access transmit and receive FIFO to perform write and read operations to a slave with interrupts.

Figure 18 and Figure 19 show the transmit and receive operations. As can be seen, the CPU is now being interrupted less than before; during the interrupt, the CPU can write or read the threshold of the data to the FIFO. However, this is still sub-optimal as the buffer management has to be done by the CPU.

Figure 18. Transmit With CPU and FIFO

Figure 19. Receive With CPU and FIFO

# 5.3 Master Function for µDMA With FIFO

$i2c\_master\_udma\_fifo$  is a simple code example where the CPU initializes and configures the  $\mu$ DMA to use the I2CFIFODATA to access transmit and receive FIFO to perform write and read operations to a slave with interrupt for the CPU on bus transaction completion. An important consideration in the code is setting the arbitration size of the  $\mu$ DMA based on the threshold of the FIFO triggers. The code itself has the optimal settings for the arbitration size as per the threshold of the TX and RX FIFOs.

Figure 20 and Figure 21 show the transmit and receive operations. As can be seen, the CPU is now being interrupted only when the data transfer is completed by the  $\mu DMA$  and for handling bus events. This is an optimal use of the FIFO when the  $\mu DMA$  performs the buffer management and only informing the CPU of a transaction completion.

Figure 20. Transmit With µDMA and FIFO

Figure 21. Receive With µDMA and FIFO

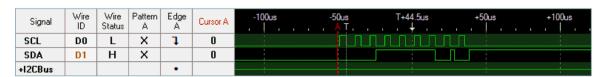

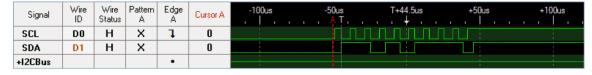

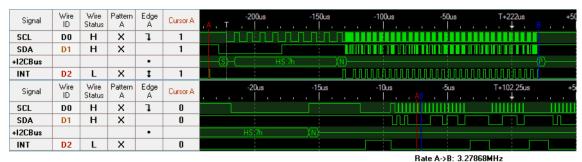

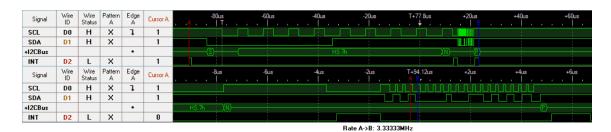

# 5.4 Master Function for High-Speed Operation

*i2c\_master\_hs* is a simple code example where the CPU uses the traditional I2CMDR to access the slave for write and read operations with interrupts. The main transactions in this example are performed in high-speed mode reducing the overall time spent by the CPU for write and read bus transactions.

For both transmit and receive, Figure 22 shows the entire transmission and Figure 23 shows the zoomed in version with the baud rate for high speed.

Note that just like the other examples of using FIFO, CPU bandwidth for performing other system tasks can be improved while reducing the overall transaction time for the I<sup>2</sup>C bus transaction.

11d(0 A 7 D. 3.21 000)

Figure 22. Transmit in HS Mode

Figure 23. Receive in HS Mode

# 6 I<sup>2</sup>C Glitch Filter Capability

An important feature on the MSP432E4 device is the I<sup>2</sup>C glitch filter that allows the application code to robustly handle transient noises that may affect the master. This feature is applicable for both the master and slave function of the MSP432E4 devices. The glitch filter feature is enabled or disabled without having the requirement to set or clear a control bit.

The I<sup>2</sup>C specification requirement for glitch suppression is 50 ns for standard (fast and fast plus mode) and 10 ns for high speed mode. The MSP432E4 glitch filters work on the system clock and, based on the system clock frequency, the value assigned to the filter must be adjusted to the nearest available setting in the glitch filter register I<sup>2</sup>C Master Timer Period Register (I2CMTPR). For example, if the system clock is 120 MHz (8.33 ns), then for the standard mode glitch suppression of 50 ns would be a value of 6 system clocks. The nearest available value is 8 system clocks. Similarly for high-speed mode, a glitch suppression of 10 ns would be 1.2 system clocks, for which the value of 2 has to be programmed in the I2CMTPR register.

The I<sup>2</sup>C glitch filter on the MSP432E4 devices uses the API *MAP\_I2CMasterGlitchFilterConfigSet*. The first parameter for the API is the base address of the I<sup>2</sup>C module and the second parameter is the filter setting. By setting the value of the filter as 0 (I2C\_MASTER\_GLITCH\_FILTER\_DISABLED), the glitch filter is automatically disabled.

```

/* Enable the Glitch Filter. Writing a value 0 will disable the glitch * filter *

I2C_MASTER_GLITCH_FILTER_DISABLED * I2C_MASTER_GLITCH_FILTER_1

* I2C_MASTER_GLITCH_FILTER_2 : Ideal Value when in HS Mode for 120MHz

* clock

* I2C_MASTER_GLITCH_FILTER_4

* I2C_MASTER_GLITCH_FILTER_8 : Ideal Value when in Std, Fast, Fast+ for

* 120MHz clock

* I2C_MASTER_GLITCH_FILTER_16

* I2C_MASTER_GLITCH_FILTER_32 */

```

MAP\_I2CMasterGlitchFilterConfigSet(I2C2\_BASE, I2C\_MASTER\_GLITCH\_FILTER\_8);

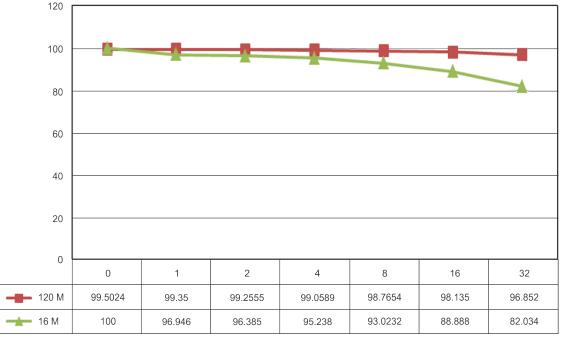

However, the I<sup>2</sup>C glitch filter on the MSP432E4 has an effect on the baud rate. Figure 24 shows the actual baud rate for a system clock of 120 MHz and 16 MHz when the device is programmed for 100-kHz operation. This can be compensated by overriding the TPR value in the I2CMTPR register after the initialization APIs have been called.

Figure 24. Glitch Filter vs Baud Rate

Conclusion www.ti.com

#### 7 Conclusion

The new features of FIFO and  $\mu$ DMA for the I²C controller allow you to substantially improve the performance of the application in terms of CPU execution cycle allocation to the other system tasks, while ensuring that the I²C, in conjunction with the  $\mu$ DMA and FIFO, have better management of the data and control transfer from the peripheral devices in the end system.

#### 8 References

- MSP432E4 SimpleLink™ Microcontrollers Technical Reference Manual

- UM10204: I2C-Bus Specification and User Manual

- SimpleLink MSP432E4 SDK

- MR44V064A 64k (8,192-Word x 8-Bit) Ferroelectric Random Access Memory (FeRAM) Data Sheet -LAPIS Semiconductor

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ("TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated