CC2564C

#### ZHCSFX3A - APRIL 2016 - REVISED NOVEMBER 2016

## CC2564C 双模 Bluetooth® 控制器

#### 1 器件概述

## 1.1 特性

- TI 的单片 蓝牙<sup>®</sup>解决方案支持蓝牙基本速率 (BR)、 增强型数据速率 (EDR) 以及低功耗 (LE);提供两种型号;

- 符合标准的蓝牙 4.2 组件(声明 ID: D032801); 最高可兼容 HCI 层

- 针对尺寸受限和低成本设计进行了高度优化:

- 单端 50Ω 射频 (RF) 接口

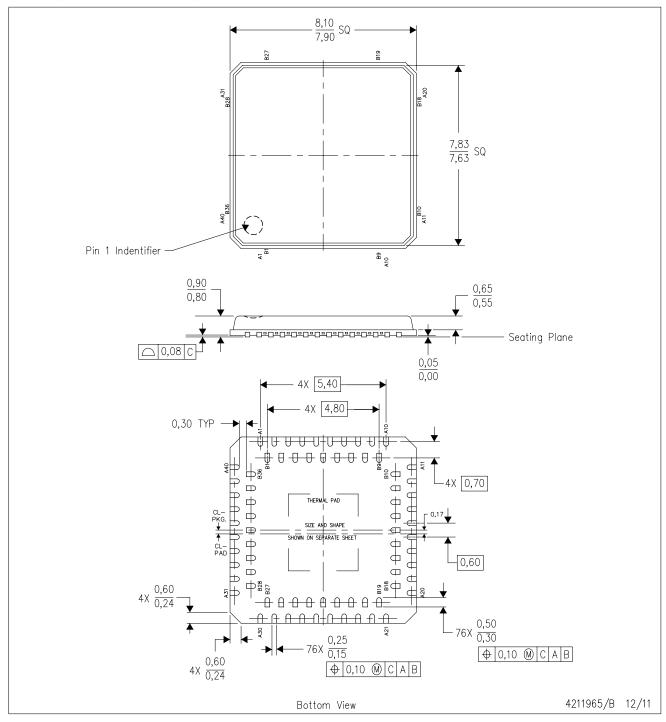

- 封装尺寸: 76 引脚, 间距为 0.6 mm, 8mm×8mm (VQFNP-MR)

- BR 和 EDR 特性 包括:

- 最多可支持七个有源器件

- 散射网:支持多达三个微微网同时运行,其中一个作为主网络,另外两个作为从网络

- 同一微微网中支持多达两条同步面向连接 (SCO) 链路

- 支持所有语音空中编码 连续可变斜率增量 (CVSD) 编码、A 律编码、μ 律编码、改良型子带 编码 (mSBC) 以及透明编码(未编码)

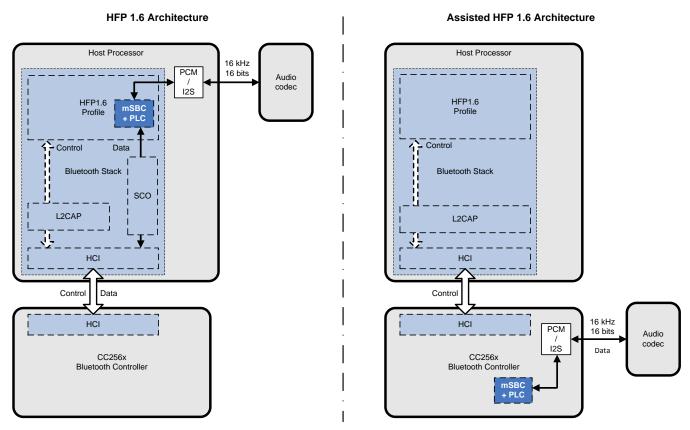

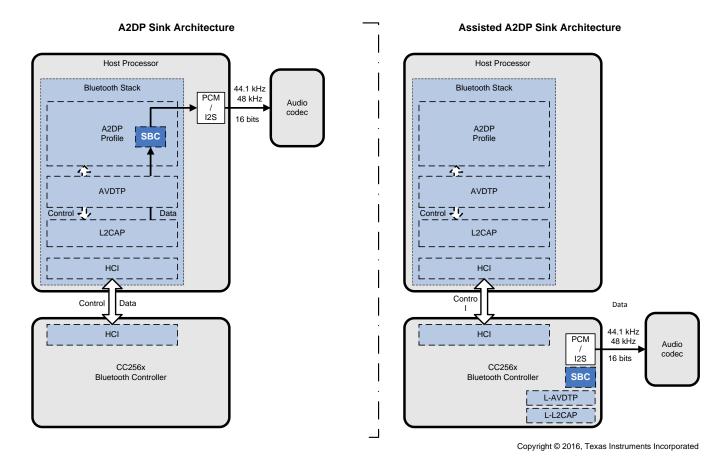

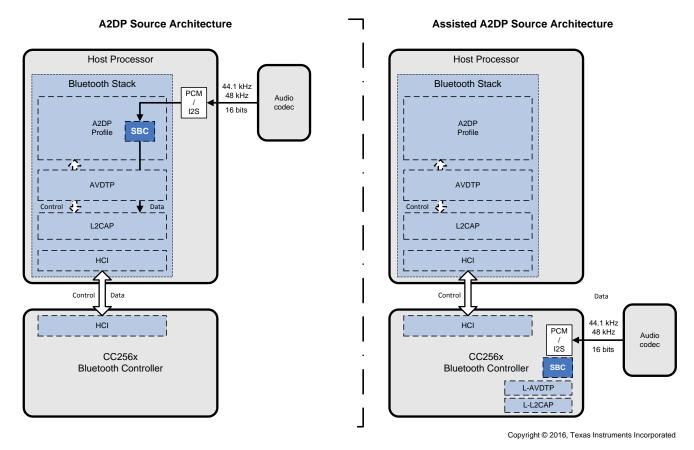

- 为 HFP 1.6 宽带语音配置文件 (WBS) 或 A2DP 配置文件提供辅助模式,旨在降低主机处理负荷和功耗

- 以增强的 QoS 支持多种蓝牙配置文件

- 低耗能 特性 包括:

- 多种嗅探实例紧密结合,最大程度降低功耗

- 针对低功耗模型进行独立缓冲,允许大量实施多种不同连接,同时不影响 BR 或 EDR 性能

- 适用于 BR、EDR 和低功耗模式的内置共存和优

#### 1.2 应用

- 无线音频解决方案

- mPOS

- 医疗设备

- 机顶盒 (STB)

## 先级处理

- 链路层拓扑散射网功能 可以同时作为外围设备 和中央设备

- 最多支持 10 个器件的网络

- 最大程度提升通道利用率的时间线优化算法

- 最佳蓝牙 (RF) 性能 (TX 功率、RX 灵敏度、阻断)

- 第一类 TX 功率高达 +12dBm

- 内部温度检测和补偿,确保 RF 性能在温度范围 内变化最小,无需使用外部校准

- 适应时间最短的改进型自适应跳频 (AFH) 算法

- 范围更大,涵盖其他仅提供低功耗模式的解决方案范围的二倍

- 延长电池寿命并简化设计的高级电源管理

- 片上电源管理,包括直接连接电池

- 激活、待机和扫描蓝牙模式的功耗较低

- 可最大程度降低功耗的关断和休眠模式

- 物理接口:

- 支持最高蓝牙数据速率的 UART 接口

- 最高速率为 4Mbps 的 UART 传输层 (H4)

- 最高速率为 4Mbps 的三线制 UART 传输层 (H5)

- 完全可编程数字脉冲编码调制 (PCM) 集成电路 内置音频总线 (I2S) 编解码器接口

- 支持在 MCU 和 MPU

- CC256x 蓝牙硬件评估工具: 评估器件 RF 性能并配置服务包的 PC 应用程序

- 穿戴式设备

- 传感器集线器,传感器网关

- 家庭与工厂自动化

## 1.3 说明

TI CC2564C 器件是一款完备的 *Bluetooth®* BR、EDR 和低功耗 HCI 解决方案,能够降低设计工作量并缩短上市时间。基于 TI 第七代蓝牙核心,CC2564C 器件提供久经验证的解决方案,符合蓝牙 4.2 标准。当与微控制器单元 (MCU) 结合使用时,该 HCI 器件可提供最佳 RF 性能,射频范围约为其他蓝牙低功耗解决方案的两倍。此外,TI 的电源管理硬件和软件算法可显著降低所有常用蓝牙 BR、EDR 和低功耗运行模式的功耗。

TI 双模蓝牙协议栈软件经认证并免收版税,适用于 MCU 和 MPU。 iPod (Mfi) 协议 由<sup>®</sup>附加软件包提供支持。有关详细信息,请参见 TI 双模蓝牙协议栈。支持多种配置文件和示例 应用, 包括以下内容:

串行端口配置 (SPP)

高级音频分配配置 (A2DP)

音频/视频远程控制配置文件 (AVRCP)

免提配置文件 (HFP)

人机界面设备 (HID)

通用属性配置文件 (GATT)

多种蓝牙低功耗配置文件和服务

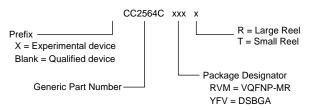

器件信息(1)

| 产品型号       | 封装       | 封装尺寸                     |  |

|------------|----------|--------------------------|--|

| CC2564CRVM | RVM (76) | 8.00mm × 8.00mm × 0.60mm |  |

(1) 有关此类器件的详细信息,请参见节9。

)

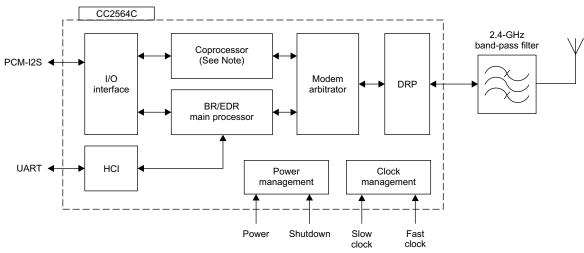

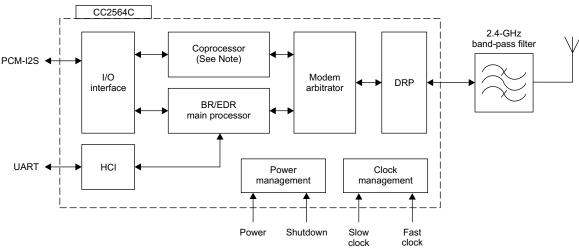

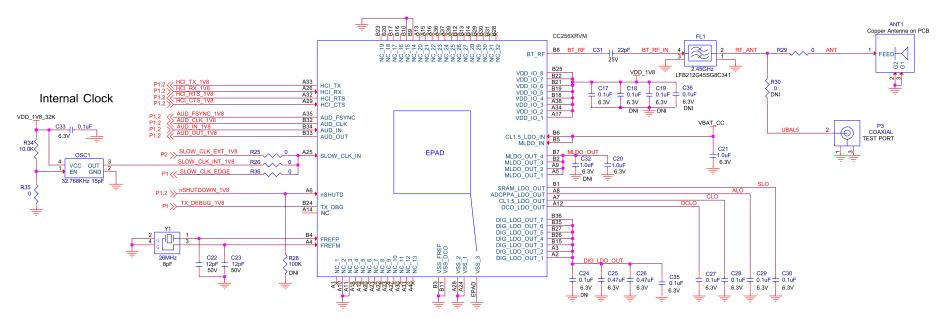

## 1.4 功能框图

Copyright © 2016, Texas Instruments Incorporated

Note: 以下技术和辅助模式无法与协处理器同时使用: 蓝牙低功耗、HFP 1.6 (WBS) 辅助模式以及 A2DP 辅助模式每次仅可使用一种技术或辅助模式。

图 1-1. 功能框图

| . 1 . | ,        |

|-------|----------|

| ᇄ     | <b>1</b> |

| rı    | 707      |

| 1 | 器件   | 概述                                             | <u>1</u>  |   | 6.1 | Overview                                      | 2  |

|---|------|------------------------------------------------|-----------|---|-----|-----------------------------------------------|----|

|   | 1.1  | 特性                                             | <u>1</u>  |   | 6.2 | Functional Block Diagram                      | 2  |

|   | 1.2  | 应用                                             | <u>1</u>  |   | 6.3 | Clock Inputs                                  | 2  |

|   | 1.3  | 说明                                             | <u>1</u>  |   | 6.4 | Functional Blocks                             | 2  |

|   | 1.4  | 功能框图                                           | 2         |   | 6.5 | Bluetooth BR and EDR Features                 | 38 |

| 2 | 修订   | 历史记录                                           | <u>3</u>  |   | 6.6 | Bluetooth low energy Description              | 39 |

| 3 | Devi | ce Comparison                                  | 4         |   | 6.7 | Bluetooth Transport Layers                    | 4  |

|   | 3.1  | Related Products                               | 4         |   | 6.8 | Changes from the CC2564B Device to the        |    |

| 4 | Term | ninal Configuration and Functions              | 5         |   |     | CC2564C Device                                | _  |

|   | 4.1  | VQFN-MR Pin Diagram                            | 5         | 7 |     | cations, Implementation, and Layout           | 4  |

| 5 | Spec | cifications                                    | 8         |   | 7.1 | Reference Design Schematics and BOM for Power | 4. |

|   | 5.1  | Absolute Maximum Ratings                       | 8         |   | 7.0 | and Radio Connections                         | _  |

|   | 5.2  | ESD Ratings                                    | 8         | 8 | 7.2 | PCB Layout Guidelines                         | _  |

|   | 5.3  | Power-On Hours                                 | 8         | • |     | 和文档支持                                         |    |

|   | 5.4  | Recommended Operating Conditions               | 9         |   | 8.1 | Third-Party Products Disclaimer               | _  |

|   | 5.5  | Power Consumption Summary                      | 9         |   | 8.2 | 工具与软件                                         | _  |

|   | 5.6  | Electrical Characteristics                     | 11        |   | 8.3 | 器件命名规则                                        | _  |

|   | 5.7  | Thermal Resistance Characteristics for VQFN-MR |           |   | 8.4 | Community Resources                           | _  |

|   |      | (RVM) Package                                  | <u>11</u> |   | 8.5 | 商标                                            | _  |

|   | 5.8  | Timing and Switching Characteristics           | 12        |   | 8.6 | 静电放电警告                                        |    |

| 6 | Deta | iled Description2                              | <u>23</u> | _ | 8.7 | Glossary                                      |    |

|   |      |                                                |           | 9 | 机械、 | 封装和可订购信息                                      | 49 |

## 2 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

# Changes from April 8, 2016 to October 27, 2016 Page • 已将文档状态更新至"量产数据" 1

## 3 Device Comparison

Table 3-1 lists the features of the CC2564C device.

#### Table 3-1. CC2564C Device Features

| DEVICE  | DESCRIPTION                          | TECHNOLOGY | SUPPORTED     | ASSISTED MODES SUPPORTED <sup>(1)</sup> |      |

|---------|--------------------------------------|------------|---------------|-----------------------------------------|------|

| DEVICE  | DESCRIPTION                          | BR, EDR    | LOW<br>ENERGY | HFP 1.6<br>(WBS)                        | A2DP |

| CC2564C | Bluetooth 4.2 + Bluetooth low energy | √          | √             | √                                       | √    |

<sup>(1)</sup> The assisted modes (HFP 1.6 and A2DP) are not supported simultaneously. Furthermore, the assisted modes are not supported simultaneously with Bluetooth low energy.

#### 3.1 Related Products

**Wireless Connectivity** The wireless connectivity portfolio offers a wide selection of low-power RF solutions suitable for a broad range of application. The offerings range from fully customized solutions to turnkey offerings with precertified hardware and software (protocol).

Companion Products Review products that are frequently purchased or used with the CC2564C product.

Reference Designs for CC2564 The TI Designs Reference Design Library is a robust reference design library spanning analog, embedded processor, and connectivity. Created by TI experts to help you jump-start your system design, all TI Designs include schematic or block diagrams, BOMs and design files to speed your time to market. Search and download designs at ti.com/tidesigns.

## 4 Terminal Configuration and Functions

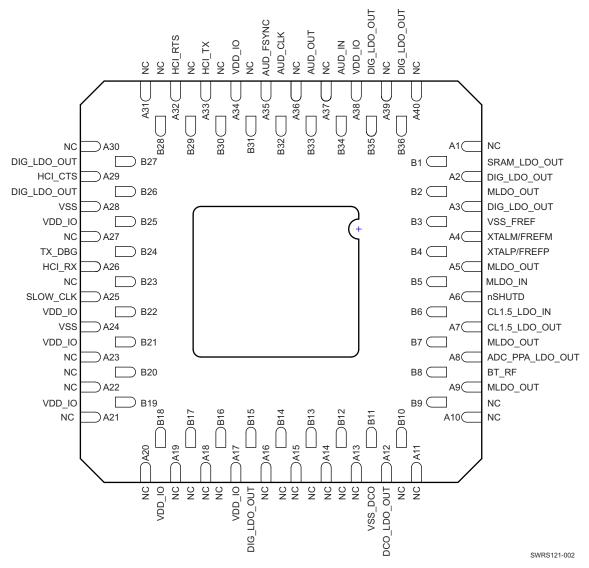

## 4.1 VQFN-MR Pin Diagram

Figure 4-1 shows the bottom view of the pin diagram (VQFN-MR package).

Figure 4-1. VQFN-MR Package Pin Diagram Bottom View

## 4.1.1 Pin Attributes (VQFN-MR Package)

Table 4-1 describes the pin attributes for the VQFN-MR package.

Table 4-1. Pin Attributes (VQFN-MR Package)

| NAME                     | NO.                                         | PULL AT<br>RESET | DEF.<br>DIR. <sup>(1)</sup> | I/O<br>Type <sup>(2)</sup> | DESCRIPTION                                                                                 |           |  |

|--------------------------|---------------------------------------------|------------------|-----------------------------|----------------------------|---------------------------------------------------------------------------------------------|-----------|--|

| I/O Signals              |                                             |                  |                             |                            |                                                                                             |           |  |

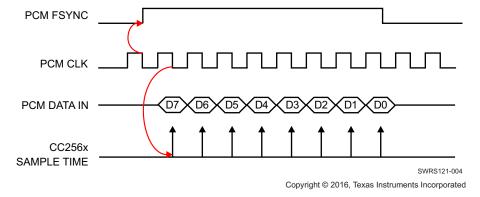

| AUD_CLK                  | B32                                         | PD               | I/O                         | HY, 4<br>mA                | PCM clock                                                                                   | Fail-safe |  |

| AUD_FSYNC                | A35                                         | PD               | I/O                         | 4 mA                       | PCM frame-sync signal                                                                       | Fail-safe |  |

| AUD_IN                   | B34                                         | PD               | I                           | 4 mA                       | PCM data input                                                                              | Fail-safe |  |

| AUD_OUT                  | B33                                         | PD               | 0                           | 4 mA                       | PCM data output                                                                             | Fail-safe |  |

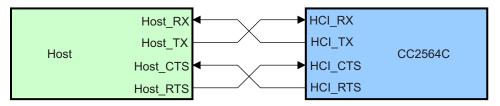

| HCI_CTS                  | A29                                         | PU               | I                           | 8 mA                       | HCI UART clear-to-send<br>The device is allowed to send data<br>when HCI_CTS is low.        |           |  |

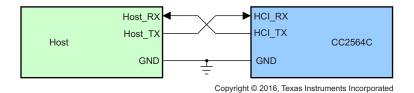

| HCI_RX                   | A26                                         | PU               | I                           | 8 mA                       | HCI universal asynchronous receiver/transmitter (UART) data receive                         |           |  |

| HCI_RTS                  | A32                                         | PU               | 0                           | 8 mA                       | HCI UART request-to-send The host is allowed to send data when HCI_RTS is low.              |           |  |

| HCI_TX                   | A33                                         | PU               | 0                           | 8 mA                       | HCI UART data transmit                                                                      |           |  |

| TX_DBG                   | B24                                         | PU               | 0                           | 2 mA                       | TI internal debug messages. TI recommends leaving an internal test point.                   |           |  |

| Clock Signals            |                                             |                  |                             |                            |                                                                                             |           |  |

| SLOW_CLK                 | A25                                         |                  | I                           |                            | 32.768-kHz clock in                                                                         | Fail-safe |  |

| XTALP/FREFP              | B4                                          |                  | I                           |                            | Fast clock in analog (sine wave) Output terminal of fast-clock crystal                      | Fail-safe |  |

| XTALM/FREFM              | A4                                          |                  | 1                           |                            | Fast clock in digital (square wave) Input terminal of fast-clock crystal                    | Fail-safe |  |

| Analog Signals           |                                             |                  |                             |                            |                                                                                             |           |  |

| BT_RF                    | B8                                          |                  | I/O                         |                            | Bluetooth RF I/O                                                                            |           |  |

| nSHUTD                   | A6                                          | PD               | I                           |                            | Shutdown input (active low)                                                                 |           |  |

| Power and Ground Signals |                                             |                  |                             |                            |                                                                                             |           |  |

| ADC_PPA_LDO_OUT          | A8                                          |                  | 0                           |                            | ADC/PPA LDO output                                                                          |           |  |

| CL1.5_LDO_IN             | В6                                          |                  | 1                           |                            | Power amplifier (PA) LDO input<br>Connect directly to battery                               |           |  |

| CL1.5_LDO_OUT            | A7                                          |                  | 0                           |                            | PA LDO output                                                                               |           |  |

| DCO_LDO_OUT              | A12                                         |                  | 0                           |                            | DCO LDO output                                                                              |           |  |

| DIG_LDO_OUT              | A2, A3,<br>B15,<br>B26,<br>B27,<br>B35, B36 |                  | 0                           |                            | Digital LDO output QFN pin B26 or B27 must be shorted to other DIG_LDO_OUT pins on the PCB. |           |  |

| MLDO_IN                  | B5                                          |                  | I                           |                            | Main LDO input<br>Connect directly to battery                                               |           |  |

| MLDO_OUT                 | A5, A9,<br>B2, B7                           |                  | I/O                         |                            | Main LDO output (1.8-V nominal)                                                             |           |  |

| SRAM_LDO_OUT             | B1                                          |                  | 0                           |                            | SRAM LDO output                                                                             |           |  |

<sup>(1)</sup> I = input; O = output; I/O = bidirectional

<sup>(2)</sup> I/O Type: Digital I/O cells. HY = input hysteresis, current = typical output current

Table 4-1. Pin Attributes (VQFN-MR Package) (continued)

| NAME     | NO.                                                      | PULL AT<br>RESET | DEF.<br>DIR. <sup>(1)</sup> | I/O<br>Type <sup>(2)</sup> | DESCRIPTION                      |

|----------|----------------------------------------------------------|------------------|-----------------------------|----------------------------|----------------------------------|

| VDD_IO   | A17,<br>A34,<br>A38,<br>B18,<br>B19,<br>B21,<br>B22, B25 |                  | I                           |                            | I/O power supply (1.8-V nominal) |

| VSS      | A24, A28                                                 |                  | 1                           |                            | Ground                           |

| VSS_DCO  | B11                                                      |                  | I                           |                            | DCO ground                       |

| VSS_FREF | В3                                                       |                  | I                           |                            | Fast clock ground                |

## 4.1.2 Connections for Unused Signals (VQFN-MR Package)

Section 4.1.2 lists the connections for unused signals for the VQFN-MR package.

| FUNCTION | PIN NUMBER | DESCRIPTION     |

|----------|------------|-----------------|

| NC       | A1         | Not connected   |

| NC       | A10        | Not connected   |

| NC       | A11        | Not connected   |

| NC       | A14        | Not connected   |

| NC       | A18        | Not connected   |

| NC       | A19        | Not connected   |

| NC       | A20        | Not connected   |

| NC       | A21        | Not connected   |

| NC       | A22        | Not connected   |

| NC       | A23        | Not connected   |

| NC       | A27        | Not connected   |

| NC       | A30        | Not connected   |

| NC       | A31        | Not connected   |

| NC       | A40        | Not connected   |

| NC       | B9         | Not connected   |

| NC       | B10        | Not connected   |

| NC       | B16        | Not connected   |

| NC       | B17        | Not connected   |

| NC       | B20        | Not connected   |

| NC       | B23        | Not connected   |

| NC       | A13        | TI internal use |

| NC       | A15        | TI internal use |

| NC       | A16        | TI internal use |

| NC       | A36        | TI internal use |

| NC       | A37        | TI internal use |

| NC       | A39        | TI internal use |

| NC       | B12        | TI internal use |

| NC       | B13        | TI internal use |

| NC       | B14        | TI internal use |

| NC       | B29        | TI internal use |

| NC       | B30        | TI internal use |

| NC       | B31        | TI internal use |

| NC       | B28        | TI internal use |

www.ti.com.cn

## 5 Specifications

Unless otherwise indicated, all measurements are taken at the device pins of the TI test evaluation board (EVB). All specifications are over process, voltage, and temperature, unless otherwise indicated.

## 5.1 Absolute Maximum Ratings<sup>(1)</sup>

Over operating free-air temperature range (unless otherwise indicated). All parameters are measured as follows: VDD\_IN = 3.6 V and VDD\_IO = 1.8 V (unless otherwise indicated).

|                                                              |             | MIN  | MAX          | UNIT             |

|--------------------------------------------------------------|-------------|------|--------------|------------------|

| Cupply voltage                                               | VDD_IN      | -0.5 | 4.8          | V <sup>(2)</sup> |

| Supply voltage                                               | VDDIO_1.8 V | -0.5 | 2.145        | V                |

| Input voltage to analog pins (3)                             |             | -0.5 | 2.1          | V                |

| Input voltage to all other pins                              |             | -0.5 | VDD_IO + 0.5 | V                |

| Bluetooth RF inputs                                          |             |      | 10           | dBm              |

| Operating ambient temperature, T <sub>A</sub> <sup>(4)</sup> |             | -40  | 85           | °C               |

| Storage temperature, T <sub>stg</sub>                        |             | -55  | 125          | °C               |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 5.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±500  |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101 (2) | ±250  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### 5.3 Power-On Hours

| DEVICE  | CONDITIONS                                                        | POWER-ON HOURS   |

|---------|-------------------------------------------------------------------|------------------|

| CC2564C | Duty cycle = 25% active and 75% sleep T <sub>ambient</sub> = 85°C | 15,400 (7 years) |

<sup>2)</sup> Maximum allowed depends on accumulated time at that voltage: VDD\_IN is defined in Section 7.1.

<sup>(3)</sup> Analog pins: BT\_RF, XTALP, and XTALM

<sup>(4)</sup> The reference design supports a temperature range of -20°C to +70°C because of the operating conditions of the crystal.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 5.4 **Recommended Operating Conditions**

|                                   |                                                                             |                           | MIN           | MAX           | UNIT       |

|-----------------------------------|-----------------------------------------------------------------------------|---------------------------|---------------|---------------|------------|

| VDD_IN                            | Power supply voltage                                                        |                           | 1.7           | 4.8           | V          |

| VDD_IO                            | I/O power supply voltage                                                    |                           | 1.62          | 1.92          | V          |

| V <sub>IH</sub>                   | High-level input voltage                                                    | Default condition         | 0.65 × VDD_IO | VDD_IO        | V          |

| $V_{IL}$                          | Low-level input voltage                                                     | Default condition         | 0             | 0.35 × VDD_IO | V          |

| t <sub>r</sub> and t <sub>f</sub> | I/O input rise and all times,<br>10% to 90%—asynchronous mode               |                           | 1             | 10            | ns         |

|                                   | I/O input rise and fall times,<br>10% to 90%—synchronous mode (PCM)         |                           | 1             | 2.5           | ns         |

|                                   |                                                                             | Condition: 0 to 0.1 MHz   |               | 60            |            |

|                                   |                                                                             | Condition: 0.1 to 0.5 MHz |               | 50            |            |

|                                   | Maximum ripple on VDD_IN (sine wave) for 1.8 V (DC-DC) mode                 | Condition: 0.5 to 2.5 MHz |               | 30            | $mV_{p-p}$ |

|                                   | 1.6 V (26 26) mode                                                          | Condition: 2.5 to 3.0 MHz |               | 15            |            |

|                                   |                                                                             | Condition: > 3.0 MHz      |               | 5             |            |

|                                   | Voltage dips on VDD_IN (VBAT) Duration = 577 µs to 2.31 ms, period = 4.6 ms |                           |               | 400           | mV         |

|                                   | Maximum ambient operating temperature <sup>(1)</sup> (2)                    |                           | -40           | 85            | °C         |

The device can be reliably operated for 7 years at T<sub>ambient</sub> of 85°C, assuming 25% active mode and 75% sleep mode (15,400 cumulative active power-on hours).

## **Power Consumption Summary**

## 5.5.1 Static Current Consumption

| OPERATIONAL MODE                             | MIN | TYP | MAX   | UNIT |

|----------------------------------------------|-----|-----|-------|------|

| Shutdown mode <sup>(1)</sup>                 |     | 1   | 7     | μA   |

| Deep sleep mode (2)                          |     | 40  | 105   | μΑ   |

| Total I/O current consumption in active mode |     |     | 1     | mA   |

| Continuous transmission—GFSK <sup>(3)</sup>  |     |     | 107   | mA   |

| Continuous transmission—EDR (4) (5)          |     |     | 112.5 | mA   |

VBAT + VIO + V<sub>SHUTDOWN</sub> VBAT + VIO

A crystal-based solution is limited by the temperature range required for the crystal to meet 20 ppm.

<sup>(3)</sup> At maximum output power dBm

At maximum output power dBm

Both π/4 DQPSK and 8DPSK

## 5.5.2 Dynamic Current Consumption

## 5.5.2.1 Current Consumption for Different Bluetooth BR and EDR Scenarios

Conditions: VDD\_IN = 3.6 V, 25°C, 26-MHz XTAL, nominal unit, 10-dBm output power

| OPERATIONAL MODE                                                  | MASTER AND SLAVE | AVERAGE CURRENT | UNIT |

|-------------------------------------------------------------------|------------------|-----------------|------|

| SCO link HV3                                                      | Master and slave | 13.7            | mA   |

| Extended SCO (eSCO) link EV3 64 kbps, no retransmission           | Master and slave | 13.2            | mA   |

| eSCO link 2-EV3 64 kbps, no retransmission                        | Master and slave | 10              | mA   |

| GFSK full throughput: TX = DH1, RX = DH5                          | Master and slave | 40.5            | mA   |

| EDR full throughput: TX = 2-DH1, RX = 2-DH5                       | Master and slave | 41.2            | mA   |

| EDR full throughput: TX = 3-DH1, RX = 3-DH5                       | Master and slave | 41.2            | mA   |

| Sniff, four attempts, 1.28 seconds                                | Master and slave | 145             | μΑ   |

| Page or inquiry scan 1.28 seconds, 11.25 ms                       | Master and slave | 320             | μΑ   |

| Page (1.28 seconds) and inquiry (2.56 seconds) scans, 11.25 ms    | Master and slave | 445             | μΑ   |

| A2DP source                                                       | Master           | 13.9            | mA   |

| A2DP sink                                                         | Master           | 15.2            | mA   |

| Assisted A2DP source                                              | Master           | 16.9            | mA   |

| Assisted A2DP sink                                                | Master           | 18.1            | mA   |

| Assisted WBS EV3; retransmit effort = 2; maximum latency = 8 ms   | Master and slave | 17.5 and 18.5   | mA   |

| Assisted WBS 2EV3; retransmit effort = 2; maximum latency = 12 ms | Master and slave | 11.9 and 13     | mA   |

## 5.5.2.2 Current Consumption for Different Low-Energy Scenarios

Conditions: VDD\_IN = 3.6 V, 25°C, nominal unit, 10-dBm output power

| MODE                        |             | DESCRIPTION                                                                                       | AVERAGE<br>CURRENT | UNIT |

|-----------------------------|-------------|---------------------------------------------------------------------------------------------------|--------------------|------|

| Advertising, nonconnectable |             | Advertising in all three channels<br>1.28-seconds advertising interval<br>15 bytes advertise data | 114                | μΑ   |

| Advertising, discoverable   |             | Advertising in all three channels<br>1.28-seconds advertising interval<br>15 bytes advertise data | 138                | μΑ   |

| Scanning                    |             | Listening to a single frequency per window 1.28-seconds scan interval 11.25-ms scan window        | 324                | μΑ   |

| _                           | Master role | 500-ms connection interval                                                                        | 169                |      |

| Connected                   | Slave role  | 0-ms slave connection latency<br>Empty TX and RX LL packets                                       | 199                | μΑ   |

#### 5.6 **Electrical Characteristics**

| RATING         |                                           | CONDITION     | MIN                    | MAX          | UNIT         |           |

|----------------|-------------------------------------------|---------------|------------------------|--------------|--------------|-----------|

|                |                                           | At 2, 4, 8 mA | 0.8 × VDD_IO           | VDD_IO       | \/           |           |

| High-level out | put voltage, V <sub>OH</sub>              |               | At 0.1 mA              | VDD_IO - 0.2 | VDD_IO       | V         |

| Low lovel out  | out voltogo V                             |               | At 2, 4, 8 mA          | 0            | 0.2 × VDD_IO | V         |

| Low-level out  | Low-level output voltage, V <sub>OL</sub> |               | At 0.1 mA              | 0            | 0.2          | V         |

| 1/0 :          | V0 1                                      |               | Resistance             | 1            |              | $M\Omega$ |

| I/O input impe | edance                                    |               | Capacitance            |              | 5            | pF        |

| Output rise ar | nd fall times, 10% to 90% (digit          | al pins)      | C <sub>L</sub> = 20 pF |              | 10           | ns        |

|                | DCM 100 hus TV DDC                        | PU            | Typical = 6.5          | 3.5          | 9.7          |           |

| I/O pull       | PCM-I2S bus, TX_DBG                       | PD            | Typical = 27           | 9.5          | 55           |           |

| currents       | All others                                | PU            | Typical = 100          | 50           | 300          | μΑ        |

|                | All others                                | All others PD |                        | 50           | 360          |           |

## Thermal Resistance Characteristics for VQFN-MR (RVM) Package

over operating free-air temperature range (unless otherwise noted)

|                      | THERMAL METRICS <sup>(1)</sup> | C/W <sup>(2)</sup> |

|----------------------|--------------------------------|--------------------|

| $R\theta_{ja}$       | Junction-to-free-air           | 34.6               |

| $R\theta_{jctop}$    | Junction-to-case-top           | 17.9               |

| $R\theta_{jcbottom}$ | Junction-to-case-bottom        | 1.6                |

| $R\theta_{jb}$       | Junction-to-board              | 12.0               |

| φ <sub>jt</sub>      | Junction-to-package-top        | 0.2                |

| Ψjb                  | Junction-to-package-bottom     | 12.0               |

- For more information about traditional and new thermal metrics, see Semiconductor and IC Package Thermal Metrics.

- These values are based on a JEDEC-defined 2S2P system (with the exception of the Theta JC [ROJC] value, which is based on a JEDEC-defined 1S0P system) and will change based on environment as well as application. For more information, see these EIA/JEDEC standards:

- JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions Natural Convection (Still Air)

- JESD51-3, Low Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages

JESD51-7, High Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages

- JESD51-9, Test Boards for Area Array Surface Mount Package Thermal Measurements Power dissipation of 2 W and an ambient temperature of 70°C is assumed.

www.ti.com.cn

#### 5.8 Timing and Switching Characteristics

#### 5.8.1 Device Power Supply

The CC2564C power-management hardware and software algorithms provide significant power savings, which is a critical parameter in an MCU-based system.

The power-management module is optimized for drawing extremely low currents.

#### 5.8.1.1 Power Sources

The CC2564C device requires two power sources:

- VDD\_IN: main power supply for the device

- VDD\_IO: power source for the 1.8-V I/O ring

The HCI module includes several on-chip voltage regulators for increased noise immunity and can be connected directly to the battery.

#### 5.8.1.2 Device Power-Up and Power-Down Sequencing

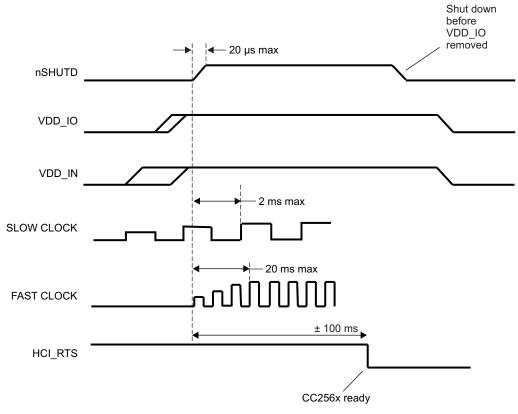

The device includes the following power-up requirements (see Figure 5-1):

- nSHUTD must be low. VDD\_IN and VDD\_IO are don't care I/O pins when nSHUTD is low. However, signals are not allowed on the I/O pins if I/O power is not supplied, because the I/Os are not fail-safe. Exceptions are SLOW\_CLK\_IN and AUD\_xxx, which are fail-safe and can tolerate external voltages with no VDD\_IO and VDD\_IN.

- VDD\_IO and VDD\_IN must be stable before releasing nSHUTD.

- The fast clock must be stable within 20 ms of nSHUTD going high.

- The slow clock must be stable within 2 ms of nSHUTD going high.

The device indicates that the power-up sequence is complete by asserting RTS low, which occurs up to 100 ms after nSHUTD goes high. If RTS does not go low, the device is not powered up. In this case, ensure that the sequence and requirements are met.

Copyright © 2016, Texas Instruments Incorporated

Figure 5-1. Power-Up and Power-Down Sequencing

## 5.8.1.3 Power Supplies and Shutdown—Static States

The nSHUTD signal puts the device in ultra-low-power mode and performs an internal reset to the device. The rise time for nSHUTD must not exceed 20 µs; nSHUTD must be low for a minimum of 5 ms.

To prevent conflicts with external signals, all I/O pins are set to the high-impedance (Hi-Z) state during shutdown and power up of the device. The internal pull resistors are enabled on each I/O pin, as described in Section 4.1.1. Table 5-1 lists and describes the static operation states.

| Table | 5-1. | Power | Modes |

|-------|------|-------|-------|

|-------|------|-------|-------|

|   | VDD_IN (1) | VDD_IO <sup>(1)</sup> | nSHUTD <sup>(1)</sup> | PM_MODE     | COMMENTS                                                                     |

|---|------------|-----------------------|-----------------------|-------------|------------------------------------------------------------------------------|

| 1 | None       | None                  | Asserted              | Shutdown    | I/O state is undefined. No I/O voltages are allowed on nonfail-safe pins.    |

| 2 | None       | None                  | Deasserted            | Not allowed | I/O state is undefined. No I/O voltages are allowed on nonfail-safe pins.    |

| 3 | None       | Present               | Asserted              | Shutdown    | I/Os are defined as tri-state pins with internal pullup or pulldown enabled. |

| 4 | None       | Present               | Deasserted            | Not allowed | I/O state is undefined. No I/O voltages are allowed on nonfail-safe pins.    |

| 5 | Present    | None                  | Asserted              | Shutdown    | I/O state is undefined.                                                      |

| 6 | Present    | None                  | Deasserted            | Not allowed | I/O state is undefined. No I/O voltages are allowed on nonfail-safe pins.    |

| 7 | Present    | Present               | Asserted              | Shutdown    | I/Os are defined as tri-state pins with internal pullup or pulldown enabled. |

| 8 | Present    | Present               | Deasserted            | Active      | See Section 5.8.1.4.                                                         |

<sup>(1)</sup> The terms *None* or *Asserted* can imply any of the following conditions: directly pulled to ground or driven low, pulled to ground through a pulldown resistor, or left NC or floating (high-impedance output stage).

#### 5.8.1.4 I/O States in Various Power Modes

#### **CAUTION**

Some device I/Os are not fail-safe (see Section 4.1.1). Fail-safe means that the pins do not draw current from an external voltage applied to the pin when I/O power is not supplied to the device. External voltages are not allowed on these I/O pins when the I/O supply voltage is not supplied because of possible damage to the device.

Table 5-2 lists the I/O states in various power modes.

Table 5-2. I/O States in Various Power Modes

| I/O NAME  | SHUTDOWN <sup>(1)</sup> |      | DEFAULT ACTIVE <sup>(1)</sup> |      | DEEP SLEEP <sup>(1)</sup> |      |

|-----------|-------------------------|------|-------------------------------|------|---------------------------|------|

| I/O NAME  | I/O State               | Pull | I/O State                     | Pull | I/O State                 | Pull |

| HCI_RX    | Z                       | PU   | I                             | PU   | I                         | PU   |

| HCI_TX    | Z                       | PU   | O-H                           |      | 0                         |      |

| HCI_RTS   | Z                       | PU   | O-H                           |      | 0                         |      |

| HCI_CTS   | Z                       | PU   | 1                             | PU   | I                         | PU   |

| AUD_CLK   | Z                       | PD   | 1                             | PD   | I                         | PD   |

| AUD_FSYNC | Z                       | PD   | I                             | PD   | I                         | PD   |

| AUD_IN    | Z                       | PD   | I                             | PD   | I                         | PD   |

| AUD_OUT   | Z                       | PD   | Z                             | PD   | Z                         | PD   |

| TX_DBG    | Z                       | PU   | 0                             |      |                           |      |

<sup>(1)</sup> I = input, O = output, Z = Hi-Z, - = no pull, PU = pullup, PD = pulldown, H = high, L = low

## 5.8.1.5 nSHUTD Requirements

|                                   | PARAMETER                                           | MIN  | MAX  | UNIT |

|-----------------------------------|-----------------------------------------------------|------|------|------|

| $V_{IH}$                          | Operation mode level <sup>(1)</sup>                 | 1.42 | 1.98 | V    |

| $V_{IL}$                          | Shutdown mode level <sup>(1)</sup>                  | 0    | 0.4  | V    |

|                                   | Minimum time for nSHUT_DOWN low to reset the device | 5    |      | ms   |

| t <sub>r</sub> and t <sub>f</sub> | Rise and fall times                                 |      | 20   | μs   |

<sup>(1)</sup> An internal pulldown retains shutdown mode when no external signal is applied to this pin.

## 5.8.2 Clock Specifications

## 5.8.2.1 Slow Clock Requirements

An external source must supply the slow clock and connect to the SLOW\_CLK\_IN pin (for example, the host or external crystal oscillator). The source must be a digital signal in the range of 0 to 1.8 V. The accuracy of the slow-clock frequency must be 32.768 kHz ±250 ppm for Bluetooth use (as specified in the Bluetooth specification). The external slow clock must be stable within 64 slow-clock cycles (2 ms) following the release of nSHUTD.

|                                   | CHARACTERISTICS                                                      | CONDITION    | MIN           | TYP   | MAX           | UNIT      |

|-----------------------------------|----------------------------------------------------------------------|--------------|---------------|-------|---------------|-----------|

|                                   | Input slow-clock frequency                                           |              |               | 32768 |               | Hz        |

|                                   | Input slow-clock accuracy (Initial + temp + aging)                   | Bluetooth    |               |       | ±250          | ppm       |

| t <sub>r</sub> and t <sub>f</sub> | Input transition time t <sub>r</sub> and t <sub>f</sub> (10% to 90%) |              |               |       | 200           | ns        |

|                                   | Frequency input duty cycle                                           |              | 15%           | 50%   | 85%           |           |

| V <sub>IH</sub>                   | Class alach innut valta an limita                                    | Square wave, | 0.65 × VDD_IO |       | VDD_IO        | V peak    |

| V <sub>IL</sub>                   | Slow-clock input voltage limits                                      | DC-coupled   | 0             |       | 0.35 × VDD_IO | V peak    |

|                                   | Input impedance                                                      |              | 1             |       |               | $M\Omega$ |

|                                   | Input capacitance                                                    |              |               |       | 5             | pF        |

## 5.8.2.2 External Fast Clock Crystal Requirements and Operation

|                 | CHARACTERISTICS                                    | CONDITION                                                        | MIN | TYP      | MAX | UNIT |

|-----------------|----------------------------------------------------|------------------------------------------------------------------|-----|----------|-----|------|

| f <sub>in</sub> | Supported crystal frequencies                      |                                                                  |     | 26, 38.4 |     | MHz  |

|                 | Frequency accuracy (Initial + temperature + aging) |                                                                  |     |          | ±20 | ppm  |

|                 | Crystal oscillator negative resistance             | 26 MHz, external capacitance = 8 pF<br>I <sub>osc</sub> = 0.5 mA | 650 | 940      |     | 0    |

|                 |                                                    | 26 MHz, external capacitance = 20 pF I <sub>osc</sub> = 2.2 mA   | 490 | 710      |     | Ω    |

## 5.8.2.3 Fast Clock Source Requirements (-40°C to +85°C)

| CHARACTERISTICS                                   | CONDITION                    |                                    | MIN  | TYP      | MAX    | UNIT             |

|---------------------------------------------------|------------------------------|------------------------------------|------|----------|--------|------------------|

| Supported frequencies, F <sub>REF</sub>           |                              |                                    |      | 26, 38.4 |        | MHz              |

| Reference frequency accuracy                      | Initial + temp + aging       |                                    |      |          | ±20    | ppm              |

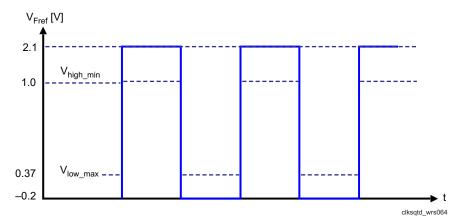

|                                                   | Square wave, DC-coupled      | $V_{IL}$                           | -0.2 |          | 0.37   | V                |

|                                                   | Square wave, DC-coupled      | V <sub>IH</sub>                    | 1.0  |          | 2.1    | V                |

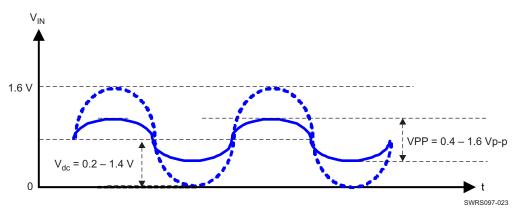

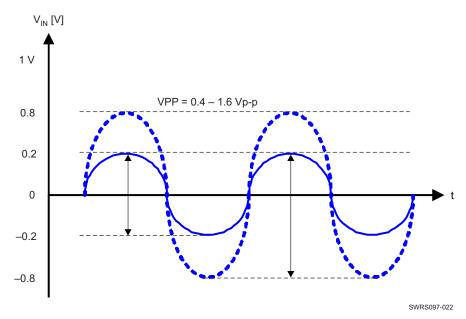

| Fast-clock input voltage limits                   | Sine wave, AC-coupled        |                                    | 0.4  |          | 1.6    | V <sub>p-p</sub> |

|                                                   | Sine wave, DC-coupled        | Sine wave, DC-coupled              |      |          | 1.6    | V <sub>p-p</sub> |

|                                                   | Sine wave input limits, DC-0 | Sine wave input limits, DC-coupled |      |          | 1.6    | V                |

| Fast-clock input rise time (as % of clock period) | Square wave, DC-coupled      |                                    |      |          | 10%    |                  |

| Duty cycle                                        |                              |                                    | 35%  | 50%      | 65%    |                  |

|                                                   | @ offset = 1 kHz             | @ offset = 1 kHz                   |      |          | -123.4 |                  |

| Phase noise for 26 MHz                            | @ offset = 10 kHz            | @ offset = 10 kHz                  |      |          | -133.4 | dBc/Hz           |

|                                                   | @ offset = 100 kHz           | @ offset = 100 kHz                 |      |          | -138.4 |                  |

## 5.8.3 Peripherals

### 5.8.3.1 UART

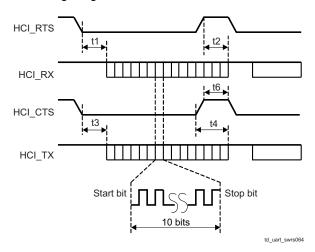

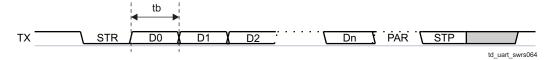

Figure 5-2 shows the UART timing diagram.

Figure 5-2. UART Timing

Table 5-3 lists the UART timing characteristics.

**Table 5-3. UART Timing Characteristics**

| SYMBOL | CHARACTERISTICS             | CONDITION                 | MIN    | TYP | MAX   | UNIT |

|--------|-----------------------------|---------------------------|--------|-----|-------|------|

|        | Baud rate                   |                           | 37.5   |     | 4000  | kbps |

|        | Baud rate accuracy per byte | Receive and transmit      | -2.5%  |     | 1.5%  |      |

|        | Baud rate accuracy per bit  | Receive and transmit      | -12.5% |     | 12.5% |      |

| t1     | RTS low to RX_DATA on       |                           | 0      | 2   |       | μs   |

| t2     | RTS high to RX_DATA off     | Interrupt set to 1/4 FIFO |        |     | 16    | byte |

| t3     | CTS low to TX_DATA on       |                           | 0      | 2   |       | μs   |

| t4     | CTS high to TX_DATA off     | Hardware flow control     |        |     | 1     | byte |

| t6     | CTS-high pulse width        |                           | 1      |     |       | bit  |

Figure 5-3 shows the UART data frame.

Figure 5-3. Data Frame

Table 5-4 describes the symbols used in Figure 5-3.

Table 5-4. Data Frame Key

| SYMBOL | DESCRIPTION           |

|--------|-----------------------|

| STR    | Start bit             |

| D0Dn   | Data bits (LSB first) |

| PAR    | Parity bit (optional) |

| STP    | Stop bit              |

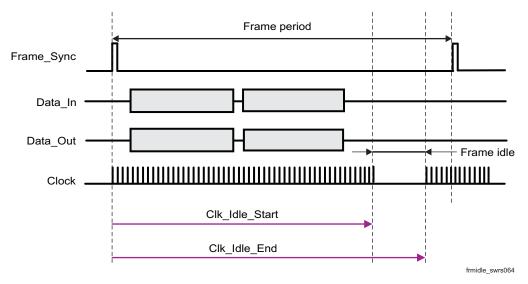

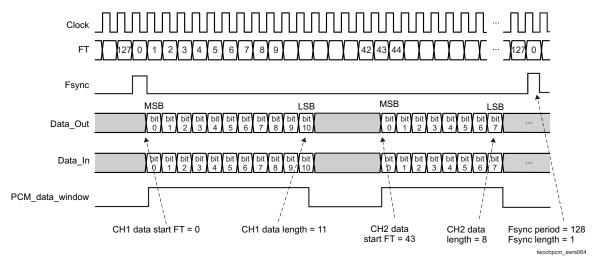

#### 5.8.3.2 PCM

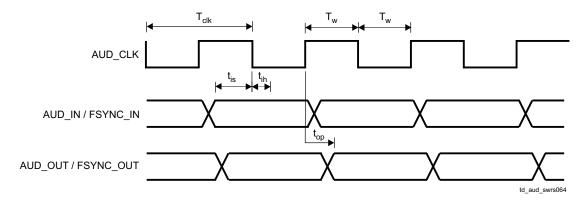

Figure 5-4 shows the interface timing for the PCM.

Figure 5-4. PCM Interface Timing

Table 5-5 lists the associated PCM master parameters.

Table 5-5. PCM Master

| SYMBOL           | PARAMETER                  | CONDITION  | MIN                         | MAX               | UNIT |

|------------------|----------------------------|------------|-----------------------------|-------------------|------|

| t <sub>clk</sub> | Cycle time                 |            | 244.14<br>(4.096 MHz)       | 15625<br>(64 kHz) | ns   |

| t <sub>w</sub>   | High or low pulse width    |            | 50% of T <sub>clk</sub> min |                   | ns   |

| t <sub>is</sub>  | AUD_IN setup time          |            | 25                          |                   | ns   |

| t <sub>ih</sub>  | AUD_IN hold time           |            | 0                           |                   | ns   |

| t <sub>op</sub>  | AUD_OUT propagation time   | 40-pF load | 0                           | 10                | ns   |

| t <sub>op</sub>  | FSYNC_OUT propagation time | 40-pF load | 0                           | 10                | ns   |

Table 5-6 lists the associated PCM slave parameters.

## Table 5-6. PCM Slave

| SYMBOL           | PARAMETER                | CONDITION  | MIN MA                  | X UNIT |

|------------------|--------------------------|------------|-------------------------|--------|

| t <sub>clk</sub> | Cycle time               |            | 66.67<br>(15 MHz)       | ns     |

| t <sub>w</sub>   | High or low pulse width  |            | 40% of T <sub>clk</sub> | ns     |

| T <sub>is</sub>  | AUD_IN setup time        |            | 8                       | ns     |

| t <sub>ih</sub>  | AUD_IN hold time         |            | 0                       | ns     |

| $t_{is}$         | AUD_FSYNC setup time     |            | 8                       | ns     |

| t <sub>ih</sub>  | AUD_FSYNC hold time      |            | 0                       | ns     |

| t <sub>op</sub>  | AUD_OUT propagation time | 40-pF load | 0 2                     | 1 ns   |

#### 5.8.4 RF Performance

#### 5.8.4.1 Bluetooth BR and EDR RF Performance

All parameters in this section that are fast-clock dependent are verified using a 26-MHz XTAL and 38.4-MHz TCXO.

## 5.8.4.1.1 Bluetooth Receiver—In-Band Signals

| CHARACTERISTICS                                  | CONDITION                               |                       | MIN   | TYP        | MAX        | BLUETOOTH<br>SPECIFICATION | UNIT |  |

|--------------------------------------------------|-----------------------------------------|-----------------------|-------|------------|------------|----------------------------|------|--|

| Operation frequency range                        |                                         |                       | 2402  |            | 2480       |                            | MHz  |  |

| Channel spacing                                  |                                         |                       |       | 1          |            |                            | MHz  |  |

| Input impedance                                  |                                         |                       |       | 50         |            |                            | Ω    |  |

|                                                  | GFSK, BER = 0.1%                        |                       | -91.5 | -95        |            | -70                        |      |  |

| Sensitivity, dirty TX on (1)                     | $\pi$ /4-DQPSK, BER = 0.01%             |                       | -90.5 | -94.5      |            | -70                        | dBm  |  |

|                                                  | 8DPSK, BER = 0.01%                      |                       | -81   | -87.5      |            | -70                        |      |  |

| BER error floor at sensitivity +                 | π/4-DQPSK                               |                       | 1E-6  | 1E-7       |            | 1E-5                       |      |  |

| 10 dB, dirty TX off                              | 8DPSK                                   |                       | 1E-6  |            |            | 1E-5                       |      |  |

|                                                  | GFSK, BER = 0.1%                        |                       | -5    |            |            | -20                        |      |  |

| Maximum usable input power                       | $\pi/4$ -DQPSK, BER = 0.1%              |                       | -10   |            |            |                            | dBm  |  |

|                                                  | 8DPSK, BER = 0.1%                       |                       | -10   |            |            |                            |      |  |

| Intermodulation characteristics                  | Level of interferers (for n = 3, 4, and | d 5)                  | -36   | -30        |            | -39                        | dBm  |  |

|                                                  | GFSK, cochannel                         |                       |       | 8          | 10         | 11                         |      |  |

|                                                  | EDR, cochannel                          | π/4-DQPSK             |       | 9.5        | 11         | 13                         |      |  |

|                                                  | EDR, COCHAINTEI                         | 8DPSK                 |       | 16.5       | 20         | 21                         |      |  |

|                                                  | GFSK, adjacent ±1 MHz                   | GFSK, adjacent ±1 MHz |       | -10        | <b>–</b> 5 | 0                          |      |  |

|                                                  | EDR, adjacent ±1 MHz, (image)           | π/4-DQPSK             |       | -10        | <b>-</b> 5 | 0                          |      |  |

|                                                  | EDN, adjacent ±1 Wiriz, (image)         | 8DPSK                 |       | <b>-</b> 5 | -1         | 5                          |      |  |

| (2)                                              | GFSK, adjacent +2 MHz                   |                       |       | -38        | -35        | -30                        |      |  |

| C/I performance <sup>(2)</sup><br>Image = -1 MHz | EDR, adjacent, +2 MHz                   | π/4-DQPSK             |       | -38        | -35        | -30                        | dB   |  |

| - 9-                                             | LDN, adjacent, +2 IVII IZ               | 8DPSK                 |       | -38        | -30        | -25                        |      |  |

|                                                  | GFSK, adjacent –2 MHz                   |                       |       | -28        | -20        | -20                        |      |  |

|                                                  | EDR, adjacent –2 MHz                    | π/4-DQPSK             |       | -28        | -20        | -20                        |      |  |

|                                                  | LDN, adjacent –2 Will2                  | 8DPSK                 |       | -22        | -13        | -13                        |      |  |

|                                                  | GFSK, adjacent ≥  ±3  MHz               |                       |       | -45        | -43        | -40                        |      |  |

|                                                  | EDR, adjacent ≥  ±3  MHz                | π/4-DQPSK             |       | -45        | -43        | -40                        |      |  |

|                                                  | LDIN, aujacent 2   13   Wil 12          | 8DPSK                 |       | -44        | -36        | -33                        |      |  |

| RF return loss                                   |                                         |                       |       | -10        |            |                            | dB   |  |

| RX mode LO leakage                               | Frf = (received RF - 0.6 MHz)           |                       |       | -63        | -58        | ·                          | dBm  |  |

<sup>(1)</sup> Sensitivity degradation up to 3 dB may occur for minimum and typical values where the Bluetooth frequency is a harmonic of the fast clock.

#### 5.8.4.1.2 Bluetooth Receiver—General Blocking

| CHARACTERISTICS                                              | CONDITION        | MIN TYP | UNIT   |

|--------------------------------------------------------------|------------------|---------|--------|

|                                                              | 30 to 2000 MHz   | -6      |        |

| Blocking performance over full range, according to Bluetooth | 2000 to 2399 MHz | -6      | alD as |

| specification <sup>(1)</sup>                                 | 2484 to 3000 MHz | -6      | dBm    |

|                                                              | 3 to 12.75 GHz   | -6      |        |

<sup>(1)</sup> Exceptions are taken out of the total 24 allowed in the Bluetooth specification.

<sup>(2)</sup> Numbers show ratio of desired signal to interfering signal. Smaller numbers indicate better C/I performance.

## 5.8.4.1.3 Bluetooth Transmitter—GFSK

| CI                               | HARACTERISTICS                       | MIN | TYP | MAX | BLUETOOTH<br>SPECIFICATION | UNIT  |

|----------------------------------|--------------------------------------|-----|-----|-----|----------------------------|-------|

| Maximum RF output                | VDD_IN = VBAT                        |     | 12  |     |                            | dBm   |

| power <sup>(1)</sup>             | VDD_IN = external regulator to 1.8 V |     | 10  |     |                            | UDIII |

| Power variation over Blu         | uetooth band                         | -1  |     | 1   |                            | dB    |

| Gain control range               |                                      |     | 30  |     |                            | dB    |

| Power control step               |                                      |     | 5   |     | 2 to 8                     | dB    |

| Adjacent channel power  M-N  = 2 |                                      |     | -45 |     | ≤ –20                      | dBm   |

| Adjacent channel power           | r  M–N  > 2                          |     | -50 |     | ≤ –40                      | dBm   |

<sup>(1)</sup> To modify maximum output power, use an HCI VS command.

## 5.8.4.1.4 Bluetooth Transmitter—EDR

|                                 | CH                  | IARACTERISTICS                       | MIN | TYP | MAX | BLUETOOTH SPECIFICATION | UNIT  |

|---------------------------------|---------------------|--------------------------------------|-----|-----|-----|-------------------------|-------|

|                                 | π/4-DQPSK           | VDD_IN = VBAT                        |     | 5.5 |     |                         |       |

| EDR output                      | π/4-DQPSK           | VDD_IN = external regulator to 1.8 V |     | 5.5 |     |                         | dBm   |

| EDR output power <sup>(1)</sup> | 8DPSK               | VDD_IN = VBAT                        |     | 5.5 |     |                         | UDIII |

|                                 | ODPSK               | VDD_IN = external regulator to 1.8 V |     | 5.5 |     |                         |       |

| EDR relative p                  | oower               | ·                                    | -2  |     | 1   | -4 to +1                | dB    |

| Power variation                 | on over Bluetooth I | pand                                 | -1  |     | 1   |                         | dB    |

| Gain control ra                 | ange                |                                      |     | 30  |     |                         | dB    |

| Power control                   | step                |                                      |     | 5   |     | 2 to 8                  | dB    |

| Adjacent char                   | nel power  M-N  :   | = 1                                  |     | -36 |     | ≤ –26                   | dBc   |

| Adjacent char                   | nel power  M-N  :   | = 2                                  |     | -30 |     | ≤ –20                   | dBm   |

| Adjacent char                   | nel power  M-N  :   | > 2                                  |     | -42 |     | ≤ –40                   | dBm   |

<sup>(1)</sup> To modify maximum output power, use an NCI VS command.

## 5.8.4.1.5 Bluetooth Modulation—GFSK

|        | CHARACTERISTICS CONDITION           |                                                                 | CONDITION                                   |             | TYP MAX | BLUETOOTH SPECIFICATION | UNIT      |

|--------|-------------------------------------|-----------------------------------------------------------------|---------------------------------------------|-------------|---------|-------------------------|-----------|

|        | -20-dB bandwidth                    | GFSK                                                            |                                             |             | 925     | ≤ 1000                  | kHz       |

| F1 avg |                                     | Δf1avg                                                          | Mod data = 4 1 s,<br>4 0 s:<br>111100001111 |             | 165     | 140 to 175              | kHz       |

| F2 max | Modulation characteristics          | $\Delta$ f2max ≥ limit for at least 99.9% of all $\Delta$ f2max | Mod data = 1010101                          |             | 130     | > 115                   | kHz       |

|        |                                     | Δf2avg, Δf1avg                                                  |                                             |             | 88%     | > 80%                   |           |

|        | Absolute carrier frequency          | DH1                                                             |                                             | -25         | 25      | < ±25                   | kHz       |

|        | drift                               | DH3 and DH5                                                     |                                             | -35         | 35      | < ±40                   | KHZ       |

|        | Drift rate                          |                                                                 |                                             |             | 15      | < 20                    | kHz/50 μs |

|        | Initial carrier frequency tolerance | f0-fTX                                                          |                                             | <b>-</b> 75 | +75     | < ±75                   | kHz       |

#### 5.8.4.1.6 Bluetooth Modulation—EDR

| CHARACTERISTICS                     | CONDITION | MIN | TYP | MAX | BLUETOOTH<br>SPECIFICATION | UNIT |

|-------------------------------------|-----------|-----|-----|-----|----------------------------|------|

| Carrier frequency stability         |           |     |     | ±5  | ≤ 10                       | kHz  |

| Initial carrier frequency tolerance |           |     |     | ±75 | ±75                        | kHz  |

| RMS DEVM (1)                        | π/4-DQPSK |     | 6%  |     | 20%                        |      |

| RIVIS DEVIVI VI                     | 8DPSK     |     | 6%  |     | 13%                        |      |

| 99% DEVM <sup>(1)</sup>             | π/4-DQPSK |     |     | 30% | 30%                        |      |

| 99% DEVIVIV                         | 8DPSK     | 20% |     | 20% |                            |      |

| Peak DEVM <sup>(1)</sup>            | π/4-DQPSK |     | 14% |     | 35%                        |      |

| Peak DEVIN (**)                     | 8DPSK     |     | 16% |     | 25%                        |      |

<sup>(1)</sup> Maximum performance refers to maximum TX power.

#### 5.8.4.1.7 Bluetooth Transmitter—Out-of-Band and Spurious Emissions

| CHARACTERISTICS                 | CONDITION                        | TYP | MAX | UNIT |

|---------------------------------|----------------------------------|-----|-----|------|

| Second harmonic <sup>(1)</sup>  |                                  | -14 | -2  | dBm  |

| Third harmonic <sup>(1)</sup>   | Measured at maximum output power | -10 | 9   | dBm  |

| Fourth harmonics <sup>(1)</sup> |                                  | -19 | -11 | dBm  |

<sup>(1)</sup> Meets FCC and ETSI requirements with external filter shown in Figure 7-1.

#### 5.8.4.2 Bluetooth low energy RF Performance

All parameters in this section that are fast-clock dependent are verified using a 26-MHz XTAL and a 38.4-MHz TCXO.

## 5.8.4.2.1 Bluetooth low energy Receiver—In-Band Signals

| CHARACTERISTIC                                   | CONDITION                              | MIN  | TYP        | MAX  | BLUETOOTH<br>low energy<br>SPECIFICATION | UNIT |

|--------------------------------------------------|----------------------------------------|------|------------|------|------------------------------------------|------|

| Operation frequency range                        |                                        | 2402 |            | 2480 |                                          | MHz  |

| Channel spacing                                  |                                        |      | 2          |      |                                          | MHz  |

| Input impedance                                  |                                        |      | 50         |      |                                          | Ω    |

| Sensitivity, dirty TX on (1)                     | PER = 30.8%; dirty TX on               |      | -96        |      | ≤ –70                                    | dBm  |

| Maximum usable input power                       | GMSK, PER = 30.8%                      | -5   |            |      | ≥ –10                                    | dBm  |

| Intermodulation characteristics                  | Level of interferers (for n = 3, 4, 5) |      | -30        |      | ≥ –50                                    | dBm  |

|                                                  | GMSK, cochannel                        |      | 8          |      | ≤ 21                                     |      |

| (2)                                              | GMSK, adjacent ±1 MHz                  |      | <b>-</b> 5 |      | ≤ 15                                     |      |

| C/I performance <sup>(2)</sup><br>Image = -1 MHz | GMSK, adjacent +2 MHz                  |      | -45        |      | ≤ –17                                    | dB   |

| image = Tiviliz                                  | GMSK, adjacent -2 MHz                  |      | -22        |      | ≤ –15                                    |      |

|                                                  | GMSK, adjacent ≥  ±3  MHz              |      | -47        |      | ≤ –27                                    |      |

| RX mode LO leakage                               | Frf = (received RF – 0.6 MHz)          |      | -63        |      |                                          | dBm  |

<sup>(1)</sup> Sensitivity degradation up to 3 dB may occur where the Bluetooth low energy frequency is a harmonic of the fast clock.

<sup>(2)</sup> Numbers show wanted signal-to-interfering signal ratio. Smaller numbers indicate better C/I performance.

## 5.8.4.2.2 Bluetooth low energy Receiver—General Blocking

| CHARACTERISTICS                                                                                      | CONDITION        | MIN TYP | BLUETOOTH<br>low energy<br>SPECIFICATION | UNIT  |

|------------------------------------------------------------------------------------------------------|------------------|---------|------------------------------------------|-------|

| Blocking performance over full range, according to Bluetooth low energy specification <sup>(1)</sup> | 30 to 2000 MHz   | -15     | ≥ –30                                    |       |

|                                                                                                      | 2000 to 2399 MHz | -15     | ≥ –35                                    | dD.m. |

|                                                                                                      | 2484 to 3000 MHz | -15     | ≥ –35                                    | dBm   |

| , , , , , , , , , , , , , , , , , , ,                                                                | 3 to 12.75 GHz   | -15     | ≥-30                                     |       |

<sup>(1)</sup> Exceptions are taken out of the total 10 allowed in the Bluetooth low energy specification.

#### 5.8.4.2.3 Bluetooth low energy Transmitter

|                                                      | CHARACTERISTICS | MIN TYP           | MAX | BLUETOOTH<br>low energy<br>SPECIFICATION | UNIT  |

|------------------------------------------------------|-----------------|-------------------|-----|------------------------------------------|-------|

| DE output nower                                      | VDD_IN = VBAT   | 12 <sup>(1)</sup> |     | ≤10                                      | dD.m. |

| RF output power VDD_IN = External regulator to 1.8 V |                 | 10                |     | ≤10                                      | dBm   |

| Power variation over Bluetooth low energy band       |                 |                   | 1   |                                          | dB    |

| Adjacent channel power  M-N  = 2                     |                 | -45               |     | ≤ –20                                    | dBm   |

| Adjacent channel power  M-N  > 2                     |                 | -50               |     | ≤ –30                                    | dBm   |

<sup>(1)</sup> To achieve the Bluetooth low energy specification of 10-dBm maximum, an insertion loss of > 2 dB is assumed between the RF ball and the antenna. Otherwise, use an HCI VS command to modify the output power.

## 5.8.4.2.4 Bluetooth low energy Modulation

| CHARACTERISTICS |                                     | CON                                             | DITION                                   | MIN TYP MAX     |     | BLUETOOTH<br>low energy<br>SPECIFICATION | UNIT       |           |

|-----------------|-------------------------------------|-------------------------------------------------|------------------------------------------|-----------------|-----|------------------------------------------|------------|-----------|

| ∆f1 avg         |                                     | Δf1avg                                          | Mod data = 4 1s, 4 0 s: 1111000011110000 | 240             | 250 | 260                                      | 225 to 275 | kHz       |

| Δf2 max         | Modulation characteristics          | Δf2max ≥ limit for at least 99.9% of all Δf2max | Mod data = 1010101                       | 185             | 210 |                                          | ≥ 185      | kHz       |

|                 |                                     | ∆f2avg, ∆f1avg                                  |                                          | 0.85            | 0.9 |                                          | ≥ 0.8      |           |

|                 | Absolute carrier frequency drift    |                                                 |                                          | -25             |     | 25                                       | ≤ ±50      | kHz       |

|                 | Drift rate                          |                                                 |                                          |                 |     | 15                                       | ≤ 20       | kHz/50 ms |

|                 | Initial carrier frequency tolerance |                                                 |                                          | <del>-</del> 75 |     | 75                                       | ≤ ±100     | kHz       |

## 5.8.4.2.5 Bluetooth low energy Transceiver, Out-Of-Band and Spurious Emissions

| CHARACTERISTICS                 | CONDITION                        | TYP | MAX | UNIT |

|---------------------------------|----------------------------------|-----|-----|------|

| Second harmonic <sup>(1)</sup>  |                                  | -14 | -2  | dBm  |

| Third harmonic <sup>(1)</sup>   | Measured at maximum output power | -10 | -6  | dBm  |

| Fourth harmonics <sup>(1)</sup> |                                  | -19 | -11 | dBm  |

(1) Meets FCC and ETSI requirements with external filter shown in Figure 7-1.

#### 6 Detailed Description

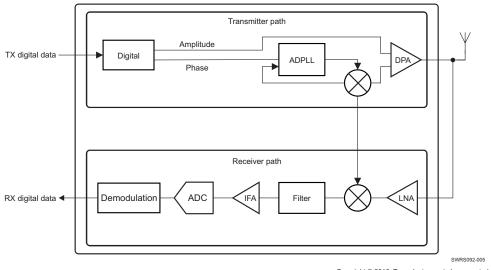

#### 6.1 Overview

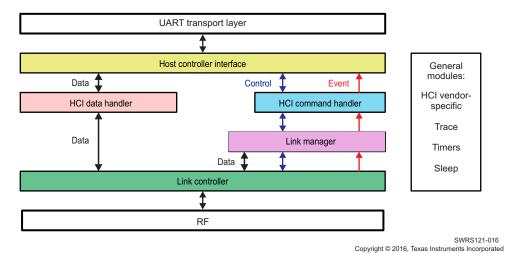

The CC2564C architecture comprises a DRP and a point-to-multipoint baseband core. The architecture is based on a single-processor ARM7TDMI<sup>®</sup> core. The device includes several on-chip peripherals to enable easy communication with a host system and the Bluetooth BR, EDR, and low energy core.

#### 6.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

NOTE: The following technologies and assisted modes cannot be used simultaneously with the coprocessor: Bluetooth low energy, assisted HFP 1.6 (WBS), and assisted A2DP. Only one technology or assisted mode can be used at a time.

Figure 6-1. CC2564C Functional Block Diagram

#### 6.3 Clock Inputs

This section describes the available clock inputs. For specifications, see Section 5.8.2.

#### 6.3.1 Slow Clock

An external source must supply the slow clock and connect to the SLOW\_CLK\_IN pin (for example, the host or external crystal oscillator). The source must be a digital signal in the range of 0 V to 1.8 V. The accuracy of the slow-clock frequency must be 32.768 kHz ±250 ppm for Bluetooth use (as specified in the Bluetooth specification). The external slow clock must be stable within 64 slow-clock cycles (2 ms) following the release of nSHUTD.

#### 6.3.2 Fast Clock Using External Clock Source

An external clock source is fed to an internal pulse-shaping cell to provide the fast-clock signal for the device. The device incorporates an internal, automatic clock-scheme detection mechanism that automatically detects the fast-clock scheme used and configures the FREF cell accordingly. This mechanism ensures that the electrical characteristics (loading) of the fast-clock input remain static regardless of the scheme used and eliminates any power-consumption penalty-versus-scheme used.

The frequency variation of the fast-clock source must not exceed ±20 ppm (as defined by the Bluetooth specification).

The external clock can be AC- or DC-coupled, sine or square wave.

#### 6.3.2.1 External F<sub>REF</sub> DC-Coupled

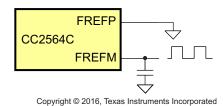

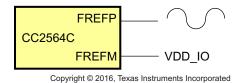

Figure 6-2 and Figure 6-3 show the clock configuration when using a square wave, DC-coupled external source for the fast-clock input.

#### **NOTE**

A shunt capacitor with a range of 10 nF must be added on the oscillator output to reject high harmonics and shape the signal to be close to a sinusoidal waveform.

TI recommends using only a dedicated LDO to feed the oscillator. Do not use the same VIO for the oscillator and the CC2564C device.

Figure 6-2. Clock Configuration (Square Wave, DC-Coupled)

Figure 6-3. External Fast Clock (Square Wave, DC-Coupled)

Figure 6-4 and Figure 6-5 show the clock configuration when using a sine wave, DC-coupled external source for the fast clock input.

Figure 6-4. Clock Configuration (Sine Wave, DC-Coupled)

Figure 6-5. External Fast Clock (Sine Wave, DC-Coupled)

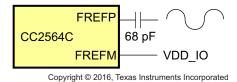

## 6.3.2.2 External F<sub>REF</sub> Sine Wave, AC-Coupled

Figure 6-6 and Figure 6-7 show the configuration when using a sine wave, AC-coupled external source for the fast-clock input.

Figure 6-6. Clock Configuration (Sine Wave, AC-Coupled)

Figure 6-7. External Fast Clock (Sine Wave, AC-Coupled)

In cases where the input amplitude is greater than 1.6  $V_{p-p}$ , the amplitude can be reduced to within limits. Using a small series capacitor forms a voltage divider with the internal input capacitance of approximately 2 pF to provide the required amplitude at the device input.

www.ti.com.cn

## 6.3.2.3 Fast Clock Using External Crystal

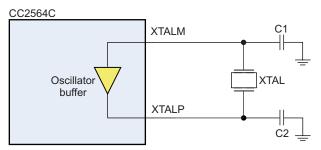

The CC2564C device incorporates an internal crystal oscillator buffer to support a crystal-based fast-clock scheme. The supported crystal frequencies are 26 and 38.4 MHz.

The frequency accuracy of the fast-clock source must not exceed ±20 ppm (including the accuracy of the capacitors, as specified in the Bluetooth specification).

Figure 6-8 shows the recommended fast-clock circuitry.

Copyright © 2016, Texas Instruments Incorporated

Figure 6-8. Fast-Clock Crystal Circuit

Table 6-1 lists component values for the fast-clock crystal circuit.

Table 6-1. Fast-Clock Crystal Circuit Component Values

| FREQ (MHz) | C1 (pF) <sup>(1)</sup> | C2 (pF) <sup>(1)</sup> |

|------------|------------------------|------------------------|

| 26         | 12                     | 12                     |

To achieve the required accuracy, values for C1 and C2 must be taken from the crystal manufacturer's data sheet and layout considerations.

#### 6.4 Functional Blocks

#### 6.4.1 RF

The CC2564C device is the third generation of Bluetooth single-chip devices using DRP architecture from TI. Modifications and new features added to the DRP further improve radio performance.

Figure 6-9 shows the DRP block diagram.

Copyright © 2016, Texas Instruments Incorporated

Figure 6-9. DRP Block Diagram

#### 6.4.1.1 Receiver