🕳 Order

Now

ZHCSHX9L-NOVEMBER 2008-REVISED FEBRUARY 2019

Support &

Community

22

# ADC14155QML-SP 耐辐射、14 位、155MSPS、1.1GHz 带宽模数转换器

Technical

Documents

### 1 特性

### • 5962R0626201VXC

- 总电离剂量 (TID) 为 100krad(Si)

- 单粒子闩锁为 120MeV-cm<sup>2</sup>/mg (请参阅辐射报告)

- 1.1GHz 全功率带宽

- 内部采样保持电路

- 低功耗

- 内部精密 1V 基准

- 单端或差分时钟模式

- 数据就绪输出时钟

- 时钟占空比稳定器

- 由 3.3V 和 1.8V 双电源供电 (±10%)

- 断电模式

- 偏移二进制或二进制补码输出数据格式

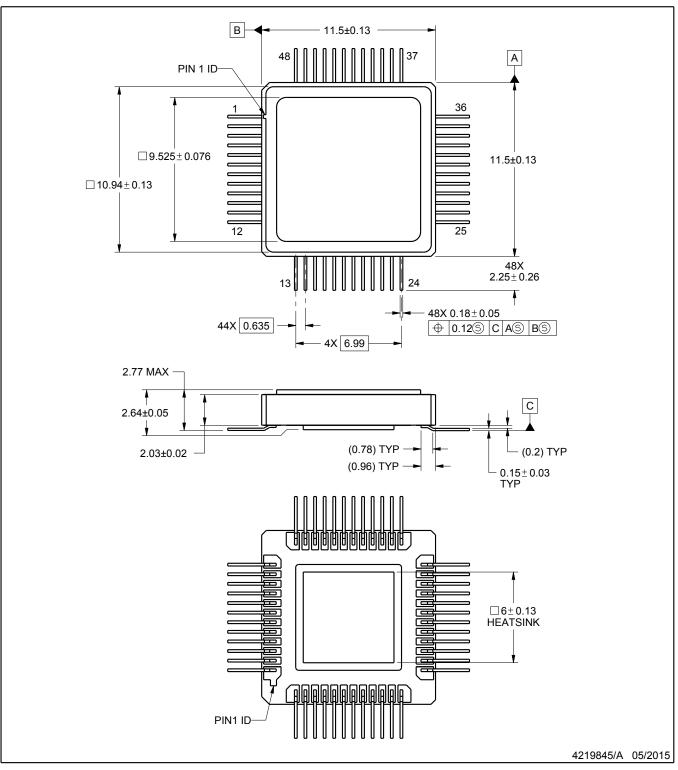

- 48 引脚 CFP 封装(11.5mm × 11.5mm, 0.635mm 引脚间距)

- 主要规格

- 分辨率: 14 位

- 转换速率: 155MSPS

- SNR (f<sub>IN</sub> = 70MHz) 70.1dBFS(典型值)

- SFDR (f<sub>IN</sub> = 70MHz) 82.3dBFS(典型值)

- ENOB (f<sub>IN</sub> = 70MHz) 11.3 位(典型值)

- 全功率带宽: 1.1GHz(典型值)

- 功耗: 967mW (典型值)

### 2 应用

- 高中频 (IF) 采样接收器

- 功率放大器线性化

- 多载波、多模式接收器

- 测试和测量设备

- 通信仪器仪表

- 雷达系统

### 3 说明

🧷 Tools &

Software

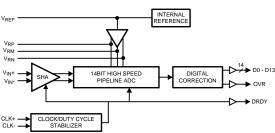

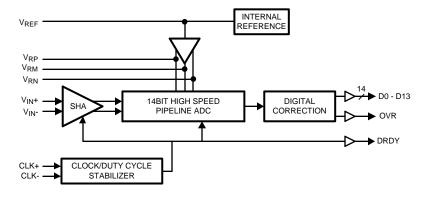

ADC14155QML-SP 是一款高性能 CMOS 模数转换器,能够以高达 155MSPS 的速率将模拟输入信号转换为 14 位数字字。该转换器使用具有数字纠错功能的差分流水线架构和片上采样保持电路,以最大程度地降低功耗并减少外部组件数,同时提供出色的动态性能。独特的采样保持级能够产生 1.1GHz 的全功率带宽。ADC14155 由 3.3V 和 1.8V 双电源供电,以155MSPS 的速率消耗 967mW 的功率。

用于数字输出接口的 1.8V 独立电源能够实现更低的功 耗和更低的噪声。断电功能可以在禁用时钟输入的情况 下将功耗降至 5mW,同时仍能快速唤醒至全功能运 行。差分输入可提供等于基准电压 2 倍的满标量程差 分输入摆幅。提供了稳定的 1V 内部电压基准,也可以 通过外部基准运行 ADC14155。可通过引脚选择时钟 模式(差分与单端)和输出数据格式(偏移二进制与二 进制补码)。占空比稳定器可在各种时钟占空比上维持 性能。

ADC14155QML-SP 采用 48 引线热增强型多层陶瓷四 方封装,可以在 -55℃ 至 +125℃ 的军用温度范围内 运行。

| 器件信息(1) |

|---------|

|---------|

| 器件型号            | 等级                            | 封装        |

|-----------------|-------------------------------|-----------|

| 5962R0626201VXC | QMLV RHA(SMD 器件)<br>[100krad] | CQFP (48) |

| ADC14155W-MLS   | 飞行 RHA(非 SMD 器件)<br>[100krad] | CQFP (48) |

| ADC14155W-MPR   | 工程样片 <sup>(2)</sup>           | CQFP (48) |

| ADC14155LCVAL   | 低频陶瓷评估板                       | _         |

| ADC14155HCVAL   | 高频陶瓷评估板                       | _         |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

(2)这些部件仅适用于工程评估。部件按照不合规的流程进行加工 处理。这些部件不适用于质检、生产、辐射测试或飞行。这些 零部件无法在 -55℃至 125℃ 的完整 MIL 额定温度范围内或 运行寿命中保证其性能。

### 目录

7

8

9 10

11

| 1<br>2 |       |                                                                                                                                  |

|--------|-------|----------------------------------------------------------------------------------------------------------------------------------|

| 3      | // 14 |                                                                                                                                  |

| 4      | 修订    | 历史记录                                                                                                                             |

| 5      | Pin   | Configuration and Functions 3                                                                                                    |

| 6      | Spe   | cifications6                                                                                                                     |

|        | 6.1   | Absolute Maximum Ratings 6                                                                                                       |

|        | 6.2   | ESD Ratings 6                                                                                                                    |

|        | 6.3   | Recommended Operating Conditions 6                                                                                               |

|        | 6.4   | Thermal Information 6                                                                                                            |

|        | 6.5   | ADC14155 Converter Electrical Characteristics DC<br>Parameters                                                                   |

|        | 6.6   | ADC14155 Converter Electrical Characteristics<br>(Continued) DYNAMIC Parameters <sup>(1)</sup>                                   |

|        | 6.7   | ADC14155 Converter Electrical Characteristics<br>(Continued) Logic and Power Supply Electrical<br>Characteristics <sup>(1)</sup> |

|        | 6.8   | ADC14155 Converter Electrical Characteristics (Continued) Timing and AC Characteristics <sup>(1)</sup> 11                        |

|        | 6.9   | Timing Diagram 12                                                                                                                |

|        | 6.10  | Transfer Characteristic 12                                                                                                       |

|        | 6.11  | Typical Performance Characteristics, DNL, INL 14                                                                                 |

|        | 6.12  | Typical Performance Characteristics, Dynamic                                                                                     |

#### 修订历史记录 4

| 注: 之前版本的页码可能与当前版本有所 | 行不同。 |

|---------------------|------|

|---------------------|------|

| Changes from Revision K (September 2018) to Revision L |                 | Page |  |

|--------------------------------------------------------|-----------------|------|--|

| •                                                      | Added Figure 20 | 17   |  |

### Changes from Revision J (March 2018) to Revision K

| • | Deleted inconsistent footnotes                                                                                                        | 6  |

|---|---------------------------------------------------------------------------------------------------------------------------------------|----|

| • | Added standardized thermal values                                                                                                     | 6  |

| • | Changed formatting of temperature conditions in the spec tables                                                                       | 7  |

| • | Added subgroups to all applicable specs                                                                                               | 7  |

| • | Changed location of 12.1- $\Omega$ capacitor on V <sub>IN-</sub> pin in the circuit diagram of the <i>Typical Application</i> section | 24 |

### Changes from Revision I (March 2013) to Revision J

| • | Deleted DYNAMIC CONVER | RTER CHARAC | TERISTICS, AIN | = -1 dBFS duplicate | specs    |         | 9 |

|---|------------------------|-------------|----------------|---------------------|----------|---------|---|

|   | 分,布局部分,器件和文档3          | 支持部分以及机械    | 或、封装和可订购       | 信息部分                |          |         | 1 |

| • | 已添加 添加了器件信息表、          | ESD 额定值表、   | 特性 说明部分,       | 器件功能模式部分,           | 应用和实施部分, | 电源相关建议部 |   |

|      | Performance                  | 15 |

|------|------------------------------|----|

| Deta | ailed Description            | 18 |

| 7.1  | Overview                     | 18 |

| 7.2  | Functional Block Diagram     | 18 |

| 7.3  | Feature Description          | 18 |

| 7.4  | Device Functional Modes      | 22 |

| Арр  | blication and Implementation | 23 |

| 8.1  | Application Information      | 23 |

| 8.2  | Typical Application          | 24 |

| 8.3  | Radiation Environments       | 25 |

| Pow  | ver Supply Recommendations   | 26 |

| Lay  | out                          | 27 |

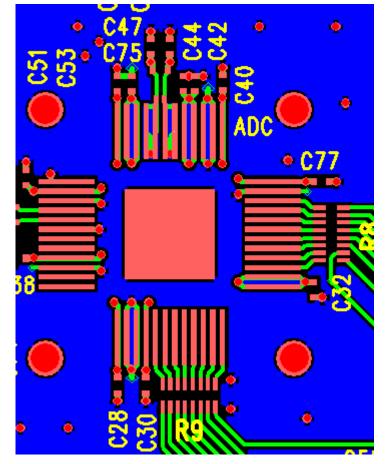

| 10.1 | Layout Guidelines            | 27 |

| 10.2 | 2 Layout Example             | 28 |

| 器件   | <b>‡和文档支持</b>                | 29 |

| 11.1 | 器件支持                         | 29 |

11.2 接收文档更新通知 ...... 30 11.3 社区资源...... 30 11.4 商标 ...... 30 11.5 静电放电警告...... 30 11.6 术语表 ...... 30 12 机械、封装和可订购信息...... 30

www.ti.com.cn

### Page

Page

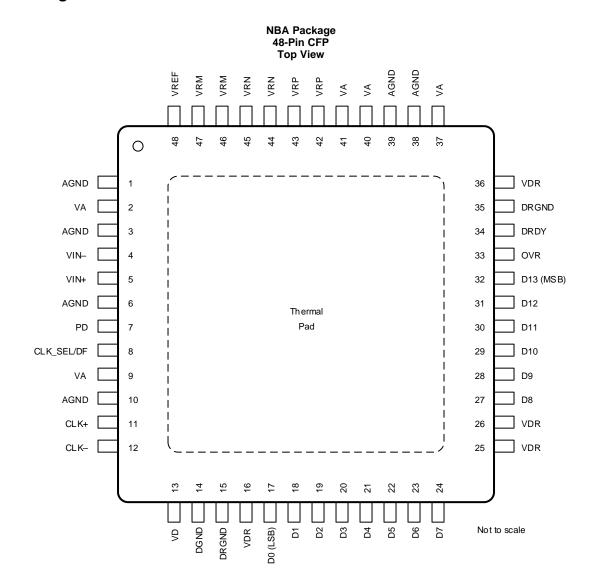

# 5 Pin Configuration and Functions

#### ADC14155QML-SP

ZHCSHX9L-NOVEMBER 2008-REVISED FEBRUARY 2019

Pin Descriptions and Equivalent Circuits PIN NO. SYMBOL **EQUIVALENT CIRCUIT** DESCRIPTION ANALOG I/O v, 4 V<sub>IN</sub> Differential analog input pins. The differential full-scale input signal level is two times the reference voltage with each input pin signal centered on a common mode voltage, V<sub>CM</sub>. 5  $V_{IN+}$ 42, 43  $V_{RP}$ These pins should each be bypassed to AGND with a low ESL (equivalent series inductance) 0.1-µF capacitor placed very close to the pin to minimize stray inductance. A 0.1-µF capacitor should be placed between  $V_{RP}$  and  $V_{RN}$  as close to the pins as possible, and a 10-µF capacitor should be placed in parallel. 46, 47  $V_{RM}$  $V_{RP}$  and  $V_{RN}$  should not be loaded.  $\dot{V}_{RM}$  may be loaded to 1mA for use as a temperature stable 1.5-V reference. It is recommended to use  $\mathsf{V}_{\mathsf{RM}}$  to provide the common mode voltage, V<sub>CM</sub>, for the differential analog inputs, V<sub>IN</sub>+ and V<sub>IN</sub>-. 44, 45  $V_{RN}$ VA This pin can be used as either the 1-V internal reference voltage output (internal reference operation) or as the external reference voltage input (external reference operation). To use the internal reference, V<sub>REF</sub> should be decoupled to AGND IDC with a 0.1-µF, low equivalent series inductance (ESL) capacitor. In this mode,  $V_{REF}$  defaults as the output for the internal 1.0-V 48 VREF reference. To use an external reference, overdrive this pin with a low noise external reference voltage. The output impedance of the internal reference at this pin is  $9k\Omega$ . Therefore, to overdrive this pin, the impedance of the external reference source should be << 9 k $\Omega$ . Υ This pin should not be used to source or sink current. AGND The full scale differential input voltage range is 2 \* V<sub>REF</sub> DIGITAL I/O V۵ The clock input pins can be configured to accept either a single-11 CLK+ ended or a differential clock input signal. When the single-ended clock mode is selected through CLK\_SEL/DF (pin 8), connect the clock input signal to the CLK+ pin and connect the CLK- pin to AGND. When the differential clock mode is selected through CLK SEL/DF (pin 8), connect the positive and negative clock inputs to the CLK+ and CLK- pins, respectively. CLK-The analog input is sampled on the falling edge of the clock input. 12 Ċ AGND

www.ti.com.cn

ADC14155QML-SP ZHCSHX9L-NOVEMBER 2008-REVISED FEBRUARY 2019

### Pin Descriptions and Equivalent Circuits (continued)

| PIN NO.                | SYMBOL          | EQUIVALENT CIRCUIT             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------|-----------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8                      | CLK_SEL/DF      |                                | This is a four-state pin controlling the input clock mode and output data format.<br>CLK_SEL/DF = V <sub>A</sub> , CLK+ and CLK- are configured as a differential clock input. The output data format is 2's complement.<br>CLK_SEL/DF = (2 / 3) * V <sub>A</sub> , CLK+ and CLK- are configured as a differential clock input. The output data format is offset binary.<br>CLK_SEL/DF = (1 / 3) * V <sub>A</sub> , CLK+ is configured as a single-ended clock input and CLK- should be tied to AGND. The output data format is 2's complement.<br>CLK_SEL/DF = AGND, CLK+ is configured as a single-ended clock input and CLK- should be tied to AGND. The output data format is offset binary. |

| 7                      | PD              | AGND                           | This is a two-state input controlling Power Down.<br>$PD = V_A$ , Power Down is enabled. In the Power Down state only the<br>reference voltage circuitry remains active and power dissipation is<br>reduced.<br>PD = AGND, Normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 17-24,<br>27-32        | D0-D13          | V <sub>DR</sub> V <sub>A</sub> | Digital data output pins that make up the 14-bit conversion result. D0 (pin 17) is the LSB, while D13 (pin 32) is the MSB of the output word. Output levels are CMOS compatible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 33                     | OVR             |                                | Over-Range Indicator. This output is set HIGH when the input amplitude exceeds the 14-bit conversion range (0 to 16383).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 34                     | DRDY            |                                | Data Ready Strobe. This pin is used to clock the output data. It has<br>the same frequency as the sampling clock. One word of data is<br>output in each cycle of this signal. The rising edge of this signal<br>should be used to capture the output data.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ANALOG POV             | VER             |                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2, 9, 37, 40,<br>41    | V <sub>A</sub>  |                                | Positive analog supply pins. These pins should be connected to a quiet 3.3-V source and be bypassed to AGND with 100-pF and 0.1- $\mu$ F capacitors located close to the power pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1, 3, 6, 10,<br>38, 39 | AGND            |                                | The ground return for the analog supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DIGITAL POW            | ER              | I                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 13                     | V <sub>D</sub>  |                                | Positive digital supply pin. This pin should be connected to a quiet 3.3-V source and be bypassed to DGND with a 100-pF and 0.1- $\mu$ F capacitor located close to the power pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 14                     | DGND            |                                | The ground return for the digital supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 16, 25, 26,<br>36      | V <sub>DR</sub> |                                | Positive driver supply pin for the output drivers. This pin should be connected to a quiet voltage source of 1.8 V and be bypassed to DRGND with 100-pF and $0.1$ -µF capacitors located close to the power pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 15, 35                 | DRGND           |                                | The ground return for the digital output driver supply. These pins should be connected to the system digital ground. See Layout Guidelines (Layout and Grounding) for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

### 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)(2)</sup>

|                                                   | MIN  | MAX                   | UNIT |

|---------------------------------------------------|------|-----------------------|------|

| Supply voltage (V <sub>A</sub> , V <sub>D</sub> ) | -0.3 | 4.2                   | V    |

| Supply voltage (V <sub>DR</sub> )                 | -0.3 | 2.35                  | V    |

| V <sub>A</sub> -V <sub>D</sub>                    |      | 100                   | mV   |

| Voltage on any input pin (not to exceed 4.2 V)    | -0.3 | V <sub>A</sub> + 0.3  | V    |

| Voltage on any output pin (not to exceed 2.35 V)  | -0.3 | V <sub>DR</sub> + 0.2 | V    |

| Input current at any pin other than supply pins   | -5   | 5                     | mA   |

| Package input current                             | -50  | 50                    | mA   |

| Max junction temperature, T <sub>J</sub>          |      | 150                   | °C   |

| Storage temperature, T <sub>stg</sub>             | -65  | 150                   | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are measured with respect to GND = AGND = DGND = DRGND = 0 V, unless otherwise specified.

### 6.2 ESD Ratings

|                    |                         |                                                                   | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2500 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                                                   | MI   | NOM    | MAX                   | UNIT |

|---------------------------------------------------|------|--------|-----------------------|------|

| Operating temperature                             | -5   | 5      | 125                   | °C   |

| Supply voltage (V <sub>A</sub> , V <sub>D</sub> ) |      | 3      | 3.6                   | V    |

| Output driver supply (V <sub>DR</sub> )           | 1.0  | 6      | 2                     | V    |

| CLK                                               | -0.0 | 5      | V <sub>A</sub> + 0.05 | V    |

| Clock duty cycle                                  | 30%  | ,<br>D | 70%                   |      |

| Analog input pins                                 |      | )      | 2.6                   | V    |

| V <sub>CM</sub>                                   | 1.4  | 1      | 1.6                   | V    |

| AGND-DGND  <sup>(2)</sup>                         |      |        | 100                   | mV   |

(1) All voltages are measured with respect to GND = AGND = DGND = DRGND = 0 V, unless otherwise specified.

(2) All GND voltages should be within 100mv of each other.

### 6.4 Thermal Information

|                               |                                              | ADC14155QML |      |

|-------------------------------|----------------------------------------------|-------------|------|

|                               | THERMAL METRIC                               | NBA (CFP)   | UNIT |

|                               |                                              | 48 PINS     |      |

| $R_{\thetaJA}$                | Junction-to-ambient thermal resistance       | 27.5        | °C/W |

| R <sub>0JC(top)</sub>         | Junction-to-case (top) thermal resistance    | 11.7        | °C/W |

| $R_{\thetaJB}$                | Junction-to-board thermal resistance         | 11.4        | °C/W |

| τιΨ                           | Junction-to-top characterization parameter   | 4.6         | °C/W |

| ΨЈВ                           | Junction-to-board characterization parameter | 11.1        | °C/W |

| $R_{\theta JC(bottom)}^{(1)}$ | Junction-to-case (bottom) thermal resistance | 3.0         | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 6.5 ADC14155 Converter Electrical Characteristics DC Parameters<sup>(1)</sup>

Unless otherwise specified, the following specifications apply: AGND = DGND = DRGND = 0 V,  $V_A = V_D = 3.3 V$ ,  $V_{DR} = 1.8 V$ , Internal V<sub>REF</sub> = 1 V,  $f_{CLK}$  = 155 MHz,  $V_{CM}$  =  $V_{RM}$ ,  $C_L$  = 5 pF/pin, Differential Analog Input, Single-Ended Clock Mode, Offset Binary Format. Typical values are for  $T_A$  = 25°C. <sup>(2)(3)(4)(5)</sup>

|                  | PARAMETER                                | TEST CONDITIONS                          | NOTES              | TYP <sup>(6)</sup> | MIN   | МАХ   | UNITS   | SUB-<br>GROUPS |

|------------------|------------------------------------------|------------------------------------------|--------------------|--------------------|-------|-------|---------|----------------|

| STATIC C         | CONVERTER CHARACTERIS                    | TICS                                     |                    |                    |       |       |         |                |

|                  | Resolution with no missing codes         |                                          |                    |                    | 14    |       | Bits    | [1, 2, 3]      |

| INL              | Integral non linearity                   |                                          | See <sup>(7)</sup> | 2.3                | -5.0  | 5.0   | LSB     | [1, 2, 3]      |

| DNL              | Differential non linearity               |                                          |                    | ±0.5               | -0.9  | 1.1   | LSB     | [1, 2, 3]      |

| PGE              | Maximum positive gain error              |                                          |                    | 0.1                | -3.3  | 3.5   | %FS     | [1, 2, 3]      |

| NGE              | Maximum negative gain error              |                                          |                    | 0.3                | -3.3  | 3.9   | %FS     | [1, 2, 3]      |

| TC GE            | Gain error tempco                        | –55°C ≤ T <sub>A</sub> ≤ +125°C          |                    | 0.007              |       |       | ∆%FS/°C |                |

| V <sub>OFF</sub> | Offset error ( $V_{IN+} = V_{IN-}$ )     |                                          |                    | -0.1               | 0.7   | -0.9  | %FS     | [1, 2, 3]      |

| TC $V_{OFF}$     | Offset error tempco                      | $-55^{\circ}C \le T_A \le +125^{\circ}C$ |                    | 0.0001             |       |       | ∆%FS/°C |                |

|                  | Under range output code                  |                                          |                    | 0                  | 0     | 0     |         |                |

|                  | Over range output code                   |                                          |                    | 16383              | 16383 | 16383 |         |                |

| REFERE           | NCE AND ANALOG INPUT C                   | HARACTERISTICS                           |                    |                    |       |       |         |                |

| V <sub>CM</sub>  | Common mode input voltage                |                                          |                    | 1.5                |       |       | V       |                |

| V <sub>RM</sub>  | Reference ladder midpoint output voltage | Output load = 1 mA                       |                    | 1.5                |       |       | V       |                |

| 0                | V <sub>IN</sub> input capacitance        | $V_{IN}$ = 1.5 Vdc ± 0.5 V(CLK LOW)      | See <sup>(8)</sup> | 9                  |       |       | pF      |                |

| C <sub>IN</sub>  | (each pin to GND)                        | $V_{IN}$ = 1.5 Vdc ± 0.5 V(CLK HIGH)     | See <sup>(8)</sup> | 6                  |       |       | pF      |                |

| V <sub>REF</sub> | Reference voltage                        |                                          | See <sup>(9)</sup> | 1.00               |       |       | V       |                |

|                  | Reference input resistance               |                                          |                    | 9                  |       |       | kΩ      |                |

(1) Pre and post irradiation limits are identical to those listed in the Electrical Characteristics tables. Radiation testing is performed per MIL-STD-883. Test Method 1019.

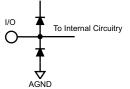

The inputs are protected as shown below. Input voltage magnitudes above VA or below GND will not damage this device, provided (2) current is limited per Note 5. However, errors in the A/D conversion can occur if the input goes above 2.6 V or below GND as described in the Recommended Operating Conditions section.

- To ensure accuracy, it is required that  $|V_A V_D| \le 100 \text{ mV}$  and separate bypass capacitors are used at each power supply pin. (3)

- With the test condition for  $V_{REF} = 1 V (2 V_{P-P} differential input)$ , the 14-bit LSB is 122.1  $\mu V$ . (4)

- (5) When the input voltage at any pin exceeds the power supplies (that is,  $V_{IN} < AGND$ , or  $V_{IN} > V_A$ ), the current at that pin should be limited to ±5 mA. The ±50-mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of ±5 mA to 10.

- (6) Typical figures are at  $T_A = 25^{\circ}C$  and represent most likely parametric norms at the time of product characterization. The typical specifications are not ensured.

- (7) Integral Non Linearity is defined as the deviation of the analog value, expressed in LSBs, from the straight line that passes through positive and negative full-scale. The input capacitance is the sum of the package/pin capacitance and the sample and hold circuit capacitance.

- Optimum performance will be obtained by keeping the reference input in the 0.9-V to 1.1-V range. The LM4051CIM3-ADJ (SOT-23 (9)package) is recommended for external reference applications.

ADC14155QML-SP

ZHCSHX9L-NOVEMBER 2008-REVISED FEBRUARY 2019

#### TEXAS INSTRUMENTS

www.ti.com.cn

### 6.6 ADC14155 Converter Electrical Characteristics (Continued) DYNAMIC Parameters<sup>(1)</sup>

Unless otherwise specified, the following specifications apply: AGND = DGND = DRGND = 0 V,  $V_A = V_D = 3.3 V$ ,  $V_{DR} = 1.8 V$ , Internal  $V_{REF} = 1 V$ ,  $f_{CLK} = 155 MHz$ ,  $V_{CM} = V_{RM}$ ,  $C_L = 5 pF/pin$ , Differential Analog Input, Single-Ended Clock Mode, Offset Binary Format. Typical values are for  $T_A = 25^{\circ}$ C. <sup>(2)(3)(4)(5)</sup>

| PARAMETER |                                     | TEST CONDITIONS                    | NOTES | TYP <sup>(6)</sup> | MIN  | МАХ | UNITS | SUB-<br>GROUPS |

|-----------|-------------------------------------|------------------------------------|-------|--------------------|------|-----|-------|----------------|

| DYNAM     | IC CONVERTER CHARACTE               | RISTICS, A <sub>IN</sub> = -1 dBFS |       |                    |      |     |       |                |

| FPBW      | Full power bandwidth                | -1 dBFS Input, -3 dB Corner        |       | 1.1                |      |     | GHz   |                |

|           |                                     | f <sub>IN</sub> = 10 MHz           |       | 69                 |      |     | dBFS  |                |

|           |                                     | f <sub>IN</sub> = 70 MHz           |       | 70.1               | 66.7 |     | dBFS  | [4, 5, 6]      |

| SNR       | Signal-to-noise ratio               | f <sub>IN</sub> = 169 MHz          |       | 68.5               |      |     | dBFS  |                |

|           |                                     | f <sub>IN</sub> = 238 MHz          |       | 68.5               |      |     | dBFS  |                |

|           |                                     | f <sub>IN</sub> = 398 MHz          |       | 66.4               |      |     | dBFS  |                |

|           |                                     | f <sub>IN</sub> = 10 MHz           |       | 82                 |      |     | dBFS  |                |

|           |                                     | f <sub>IN</sub> = 70 MHz           |       | 82.3               | 68.2 |     | dBFS  | [4, 5, 6]      |

| SFDR      | Spurious free dynamic<br>range      | f <sub>IN</sub> = 169 MHz          |       | 80.5               |      |     | dBFS  |                |

|           | lange                               | f <sub>IN</sub> = 238 MHz          |       | 77.3               |      |     | dBFS  |                |

|           |                                     | f <sub>IN</sub> = 398 MHz          |       | 63.5               |      |     | dBFS  |                |

|           |                                     | f <sub>IN</sub> = 10 MHz           |       | 11.3               |      |     | Bits  |                |

|           |                                     | f <sub>IN</sub> = 70 MHz           |       | 11.3               | 10.7 |     | Bits  | [4, 5, 6]      |

| ENOB      | Effective number of bits            | f <sub>IN</sub> = 169 MHz          |       | 11.0               |      |     | Bits  |                |

|           |                                     | f <sub>IN</sub> = 238 MHz          |       | 11.0               |      |     | Bits  |                |

|           |                                     | f <sub>IN</sub> = 398 MHz          |       | 10.0               |      |     | Bits  |                |

|           |                                     | f <sub>IN</sub> = 10 MHz           |       | -81                |      |     | dBFS  |                |

|           |                                     | f <sub>IN</sub> = 70 MHz           |       | -79.9              |      | -67 | dBFS  | [4, 5, 6]      |

| THD       | Total harmonic disortion            | f <sub>IN</sub> = 169 MHz          |       | -82.4              |      |     | dBFS  |                |

|           |                                     | f <sub>IN</sub> = 238 MHz          |       | -76.6              |      |     | dBFS  |                |

|           |                                     | f <sub>IN</sub> = 398 MHz          |       | -63.2              |      |     | dBFS  |                |

|           |                                     | f <sub>IN</sub> = 10 MHz           |       | -95.4              |      |     | dBFS  |                |

|           |                                     | f <sub>IN</sub> = 70 MHz           |       | -88.5              |      | -70 | dBFS  | [4, 5, 6]      |

| HD2       | Second-order harmonic<br>distortion | f <sub>IN</sub> = 169 MHz          |       | -88.3              |      |     | dBFS  |                |

|           |                                     | f <sub>IN</sub> = 238 MHz          |       | -77.3              |      |     | dBFS  |                |

|           |                                     | f <sub>IN</sub> = 398 MHz          |       | -60.9              |      |     | dBFS  |                |

(1) Pre and post irradiation limits are identical to those listed in the *Electrical Characteristics* tables. Radiation testing is performed per MIL-STD-883, Test Method 1019.

(2) The inputs are protected as shown below. Input voltage magnitudes above V<sub>A</sub> or below GND will not damage this device, provided current is limited per Note 5. However, errors in the A/D conversion can occur if the input goes above 2.6V or below GND as described in the *Recommended Operating Conditions* section.

- (3) To ensure accuracy, it is required that  $|V_A V_D| \le 100 \text{ mV}$  and separate bypass capacitors are used at each power supply pin.

- (4) With the test condition for  $V_{REF} = 1 V (2 V_{P-P} \text{ differential input})$ , the 14-bit LSB is 122.1  $\mu V$ .

- (5) When the input voltage at any pin exceeds the power supplies (that is, V<sub>IN</sub> < AGND, or V<sub>IN</sub> > V<sub>A</sub>), the current at that pin should be limited to ±5 mA. The ±50 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of ±5 mA to 10.

- (6) Typical figures are at T<sub>A</sub> = 25°C and represent most likely parametric norms at the time of product characterization. The typical specifications are not ensured.

### ADC14155 Converter Electrical Characteristics (Continued) DYNAMIC Parameters<sup>(1)</sup> (continued)

Unless otherwise specified, the following specifications apply: AGND = DGND = DRGND = 0 V,  $V_A = V_D = 3.3 V$ ,  $V_{DR} = 1.8 V$ , Internal  $V_{REF} = 1 V$ ,  $f_{CLK} = 155 \text{ MHz}$ ,  $V_{CM} = V_{RM}$ ,  $C_L = 5 \text{ pF/pin}$ , Differential Analog Input, Single-Ended Clock Mode, Offset Binary Format. Typical values are for  $T_A = 25^{\circ}$ C. <sup>(2)(3)(4)(5)</sup>

|                                     | PARAMETER                               | TEST CONDITIONS           | NOTES | TYP <sup>(6)</sup> | MIN  | МАХ  | UNITS | SUB-<br>GROUPS |

|-------------------------------------|-----------------------------------------|---------------------------|-------|--------------------|------|------|-------|----------------|

|                                     |                                         | f <sub>IN</sub> = 10 MHz  |       | -81.6              |      |      | dBFS  |                |

|                                     |                                         | f <sub>IN</sub> = 70 MHz  |       | -82.3              |      | -68  | dBFS  | [4, 5, 6]      |

| HD3 Third-order harmonic distortion | f <sub>IN</sub> = 169 MHz               |                           | -86.4 |                    |      | dBFS |       |                |

|                                     | f <sub>IN</sub> = 238 MHz               |                           | -89.0 |                    |      | dBFS |       |                |

|                                     |                                         | f <sub>IN</sub> = 398 MHz |       | -80.5              |      |      | dBFS  |                |

|                                     |                                         | f <sub>IN</sub> = 10 MHz  |       | 68.2               |      |      | dBFS  |                |

|                                     |                                         | f <sub>IN</sub> = 70 MHz  |       | 69.9               | 66.2 |      | dBFS  | [4, 5, 6]      |

| SINAD                               | Signal-to-noise and<br>distortion ratio | f <sub>IN</sub> = 169 MHz |       | 68.3               |      |      | dBFS  |                |

|                                     |                                         | f <sub>IN</sub> = 238 MHz |       | 67.8               |      |      | dBFS  |                |

|                                     |                                         | f <sub>IN</sub> = 398 MHz |       | 61.5               |      |      | dBFS  |                |

# 6.7 ADC14155 Converter Electrical Characteristics (Continued) Logic and Power Supply Electrical Characteristics<sup>(1)</sup>

Unless otherwise specified, the following specifications apply: AGND = DGND = DRGND = 0 V,  $V_A = V_D = 3.3 V$ ,  $V_{DR} = 1.8 V$ , Internal  $V_{REF} = 1 V$ ,  $f_{CLK} = 155 MHz$ ,  $V_{CM} = V_{RM}$ ,  $C_L = 5 pF/pin$ , Differential Analog Input, Single-Ended Clock Mode, Offset Binary Format. Typical values are for  $T_A = 25^{\circ}$ C. Timing measurements are taken at 50% of the signal amplitude. <sup>(2)(3)(4)(5)</sup>

|                    | PARAMETER                              | TEST CONDITIONS                                                                | NOTES                                                           | TYP <sup>(6)</sup> | MIN       | МАХ       | UNITS | SUB-<br>GROUPS |

|--------------------|----------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------|-----------|-----------|-------|----------------|

| DIGITAL            | . INPUT CHARACTERISTICS (              | CLK, PD/DCS, CLK_SEL/DF)                                                       |                                                                 |                    |           |           |       |                |

| V <sub>IN(1)</sub> | Logical "1" input voltage              | V <sub>D</sub> = 3.6 V                                                         | See <sup>(7)</sup>                                              |                    | 2.0       |           | V     | [1, 2, 3]      |

| V <sub>IN(0)</sub> | Logical "0" input voltage              | V <sub>D</sub> = 3.0 V                                                         |                                                                 |                    |           | 0.8       | V     | [1, 2, 3]      |

| I <sub>IN(1)</sub> | Logical "1" input current              | V <sub>IN</sub> = 3.3 V                                                        |                                                                 | 10                 |           |           | μA    |                |

| I <sub>IN(0)</sub> | Logical "0" input current              | $V_{IN} = 0 V$                                                                 |                                                                 | -10                |           |           | μA    |                |

| C <sub>IN</sub>    | Digital input capacitance              |                                                                                |                                                                 | 5                  |           |           | pF    |                |

| DIGITAL            | OUTPUT CHARACTERISTICS                 | S (D0–D13, DRDY, OVR)                                                          |                                                                 |                    |           | ·         |       |                |

| V <sub>OH</sub>    | Output logic high                      | <sub>OUT</sub> = -0.5 mA , V <sub>DR</sub> = 1.8 V See <sup>(7)</sup> 1.55 1.2 |                                                                 | V                  | [1, 2, 3] |           |       |                |

| V <sub>OL</sub>    | Output logic low                       | I <sub>OUT</sub> = 1.6 mA, V <sub>DR</sub> = 1.8 V                             | T = 1.6 mA, V <sub>DR</sub> = 1.8 V See <sup>(7)</sup> 0.15 0.4 |                    | V         | [1, 2, 3] |       |                |

| +I <sub>SC</sub>   | Output short circuit source<br>current | V <sub>OUT</sub> = 0 V                                                         |                                                                 | -10                |           |           | mA    |                |

| -I <sub>SC</sub>   | Output short circuit sink current      | V <sub>OUT</sub> = V <sub>DR</sub>                                             |                                                                 | 10                 |           |           | mA    |                |

| C <sub>OUT</sub>   | Digital output capacitance             |                                                                                |                                                                 | 5                  |           |           | pF    |                |

| POWER              | SUPPLY CHARACTERISTICS                 |                                                                                |                                                                 |                    |           |           |       |                |

| I <sub>A</sub>     | Analog supply current                  | Full operation                                                                 |                                                                 | 283                |           | 350       | mA    | [1, 2, 3]      |

| I <sub>D</sub>     | Digital supply current                 | Full operation                                                                 |                                                                 | 10                 |           | 11        | mA    | [1, 2, 3]      |

| I <sub>DR</sub>    | Digital output supply current          | Full operation                                                                 | See <sup>(8)</sup>                                              | 15                 |           |           | mA    |                |

|                    | Power consumption                      | Excludes I <sub>DR</sub>                                                       |                                                                 | 967                |           | 1170      | mW    | [1, 2, 3]      |

|                    | Power down power consumption           | Clock disabled                                                                 |                                                                 | 5                  |           |           | mW    |                |

(1) Pre and post irradiation limits are identical to those listed in the *Electrical Characteristics* tables. Radiation testing is performed per MIL-STD-883, Test Method 1019.

(2) The inputs are protected as shown below. Input voltage magnitudes above V<sub>A</sub> or below GND will not damage this device, provided current is limited per Note 5. However, errors in the A/D conversion can occur if the input goes above 2.6 V or below GND as described in the *Recommended Operating Conditions* section.

- (3) To ensure accuracy, it is required that  $|V_A V_D| \le 100 \text{ mV}$  and separate bypass capacitors are used at each power supply pin.

- (4) With the test condition for  $V_{REF} = 1 V (2 V_{P-P} \text{ differential input})$ , the 14-bit LSB is 122.1  $\mu V$ .

- (5) When the input voltage at any pin exceeds the power supplies (that is,  $V_{IN} < AGND$ , or  $V_{IN} > V_A$ ), the current at that pin should be limited to ±5 mA. The ±50-mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of ±5 mA to 10.

- (6) Typical figures are at  $T_A = 25^{\circ}C$  and represent most likely parametric norms at the time of product characterization. The typical specifications are not ensured.

- (7) Specified by characterization.

- (8)  $I_{DR}$  is the current consumed by the switching of the output drivers and is primarily determined by load capacitance on the output pins, the supply voltage,  $V_{DR}$ , and the rate at which the outputs are switching (which is signal dependent).  $I_{DR} = V_{DR}(C_0 \times f_0 + C_1 \times f_1 + ..., C_{11} \times f_{11})$  where  $V_{DR}$  is the output driver power supply voltage,  $C_n$  is total capacitance on the output pin, and  $f_n$  is the average frequency at which that pin is toggling.

### 6.8 ADC14155 Converter Electrical Characteristics (Continued) Timing and AC Characteristics<sup>(1)</sup>

Unless otherwise specified, the following specifications apply: AGND = DGND = DRGND = 0 V, V<sub>A</sub> = V<sub>D</sub> = 3.3 V, V<sub>DR</sub> = 1.8 V, Internal  $V_{REF} = 1 \text{ V}$ ,  $f_{CLK} = 155 \text{ MHz}$ ,  $V_{CM} = V_{RM}$ ,  $C_L = 5 \text{ pF/pin}$ , Differential Analog Input, Single-Ended Clock Mode, Offset Binary Format. Typical values are for  $T_A = 25^{\circ}$ C. Timing measurements are taken at 50% of the signal amplitude. **Boldface** limits apply for  $T_{MIN} \le T_A \le T_{MAX}$ . All other limits apply for  $T_A = 25^{\circ}C^{(2)(3)(4)(5)}$

|                 | PARAMETER                      | TEST CONDITIONS                                                                                                                     | NOTES              | TYP <sup>(6)</sup> | MIN  | МАХ | UNITS           | SUB-<br>GROUPS |

|-----------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|-----|-----------------|----------------|

|                 | Maximum clock frequency        |                                                                                                                                     |                    |                    |      | 155 | MHz             | [7, 8A, 8B]    |

|                 | Minimum clock frequency        |                                                                                                                                     |                    |                    | 5    |     | MHz             |                |

|                 | Clock high time                |                                                                                                                                     |                    | 3.0                |      |     | ns              |                |

|                 | Clock low time                 |                                                                                                                                     |                    | 3.0                |      |     | ns              |                |

|                 | Conversion latency             |                                                                                                                                     | See <sup>(7)</sup> |                    |      | 8   | Clock<br>cycles | [4, 5, 6]      |

| t <sub>OD</sub> | Output delay of CLK to<br>DATA | Relative to falling edge of CLK                                                                                                     |                    | 2.0                |      |     | ns              |                |

| t <sub>SU</sub> | Data output setup time         | Relative to DRDY                                                                                                                    | See <sup>(8)</sup> | 2.1                | 1.22 |     | ns              |                |

| t <sub>H</sub>  | Data output hold time          | Relative to DRDY                                                                                                                    | See <sup>(8)</sup> | 2.1                | 1.83 |     | ns              |                |

| t <sub>AD</sub> | Aperture delay                 |                                                                                                                                     |                    | 0.5                |      |     | ns              |                |

| t <sub>AJ</sub> | Aperture jitter                |                                                                                                                                     |                    | 0.08               |      |     | ps rms          |                |

|                 | Power down recovery time       | 0.1 $\mu F$ to GND on pins 43, 44; 10 $\mu F$ and 0.1 $\mu F$ between pins 43, 44; 0.1 $\mu F$ and 10 $\mu F$ to GND on pins 47, 48 |                    | 3.0                |      |     | ms              |                |

Pre and post irradiation limits are identical to those listed in the Electrical Characteristics tables. Radiation testing is performed per MIL-(1)STD-883, Test Method 1019.

The inputs are protected as shown below. Input voltage magnitudes above VA or below GND will not damage this device, provided (2)current is limited per Note 5. However, errors in the A/D conversion can occur if the input goes above 2.6 V or below GND as described in the Recommended Operating Conditions section.

- To ensure accuracy, it is required that  $|V_A V_D| \le 100 \text{ mV}$  and separate bypass capacitors are used at each power supply pin. With the test condition for  $V_{REF} = 1 \text{ V} (2 V_{P-P} \text{ differential input})$ , the 14-bit LSB is 122.1  $\mu$ V. (3)

- (4)

- When the input voltage at any pin exceeds the power supplies (that is,  $V_{IN} < AGND$ , or  $V_{IN} > V_A$ ), the current at that pin should be (5) limited to ±5 mA. The ±50 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of ±5 mA to 10.

- Typical figures are at T<sub>A</sub> = 25°C and represent most likely parametric norms at the time of product characterization. The typical (6) specifications are not ensured.

- (7)Specified by design.

- Specified by characterization. (8)

### ADC14155QML-SP ZHCSHX9L-NOVEMBER 2008-REVISED FEBRUARY 2019

www.ti.com.cn

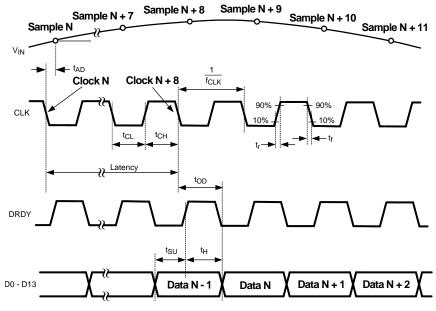

### 6.9 Timing Diagram

Figure 1. Output Timing

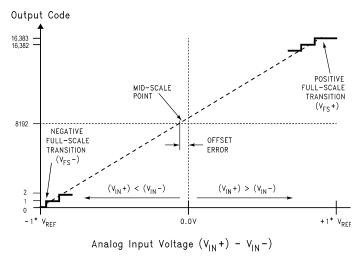

### 6.10 Transfer Characteristic

Figure 2. Transfer Characteristic

### **Transfer Characteristic (continued)**

### Table 1. Quality Conformance Inspection<sup>(1)</sup>

| Subgroup | Description         | Temp (°C) |  |  |  |  |  |  |  |  |

|----------|---------------------|-----------|--|--|--|--|--|--|--|--|

| 1        | Static tests at     | 25        |  |  |  |  |  |  |  |  |

| 2        | Static tests at     | 125       |  |  |  |  |  |  |  |  |

| 3        | Static tests at     | -55       |  |  |  |  |  |  |  |  |

| 4        | Dynamic tests at    | 25        |  |  |  |  |  |  |  |  |

| 5        | Dynamic tests at    | 125       |  |  |  |  |  |  |  |  |

| 6        | Dynamic tests at    | -55       |  |  |  |  |  |  |  |  |

| 7        | Functional tests at | 25        |  |  |  |  |  |  |  |  |

| 8A       | Functional tests at | 125       |  |  |  |  |  |  |  |  |

| 8B       | Functional tests at | -55       |  |  |  |  |  |  |  |  |

| 9        | Switching tests at  | 25        |  |  |  |  |  |  |  |  |

| 10       | Switching tests at  | 125       |  |  |  |  |  |  |  |  |

| 11       | Switching tests at  | -55       |  |  |  |  |  |  |  |  |

(1) MIL-STD-883, Method 5005 - Group A

### ADC14155QML-SP

ZHCSHX9L-NOVEMBER 2008-REVISED FEBRUARY 2019

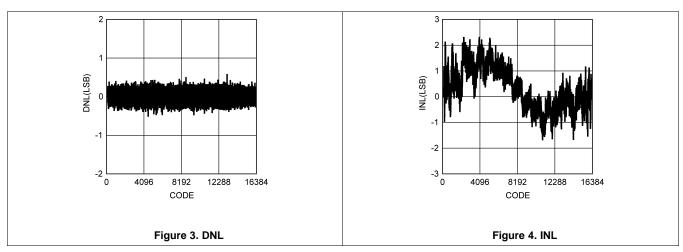

### 6.11 Typical Performance Characteristics, DNL, INL

Unless otherwise specified, the following specifications apply: AGND = DGND = DRGND = 0 V,  $V_A = V_D = 3.3 V$ ,  $V_{DR} = 1.8 V$ , Internal  $V_{REF} = 1 V$ ,  $f_{CLK} = 155 MHz$ ,  $V_{CM} = V_{RM}$ ,  $C_L = 5 pF/pin$ , Differential Analog Input, Single-Ended Clock Mode, Offset Binary Format. Typical values are for TA =  $25^{\circ}$ C.<sup>(1)(2)(3)</sup>

(1) The inputs are protected as shown below. Input voltage magnitudes above V<sub>A</sub> or below GND will not damage this device, provided current is limited per Note 5. However, errors in the A/D conversion can occur if the input goes above 2.6 V or below GND as described in the *Recommended Operating Conditions* section.

- (2) To ensure accuracy, it is required that  $|V_A V_D| \le 100 \text{ mV}$  and separate bypass capacitors are used at each power supply pin.

- (3) With the test condition for  $V_{REF} = 1 V (2 V_{P-P} \text{ differential input})$ , the 14-bit LSB is 122.1  $\mu V$ .

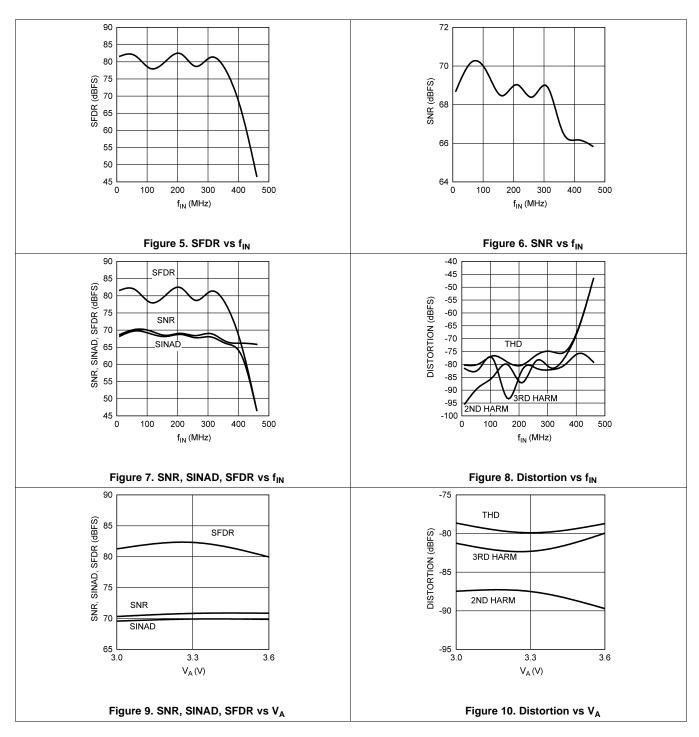

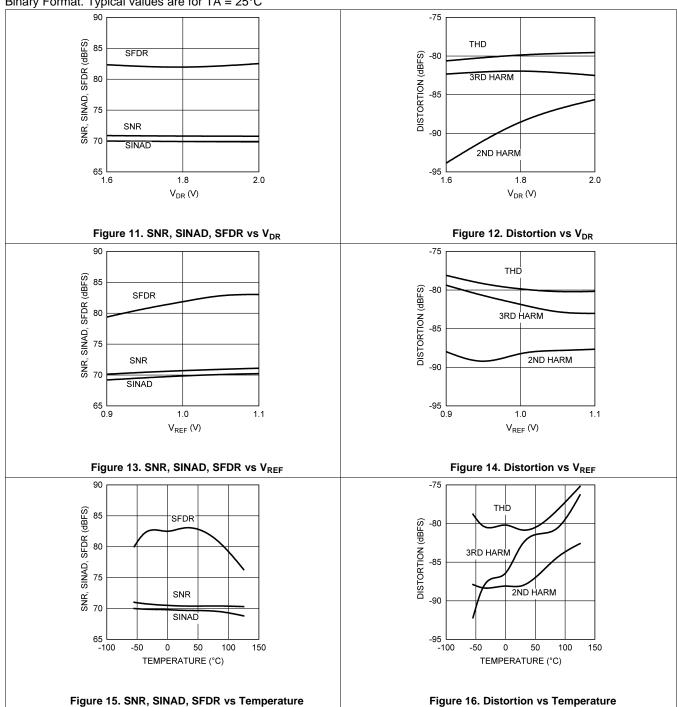

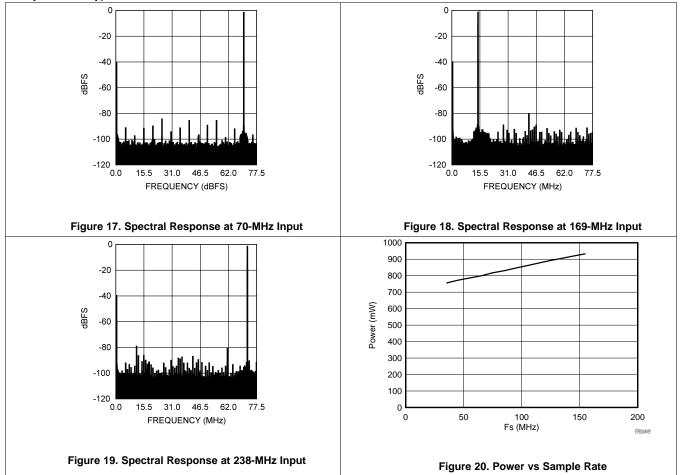

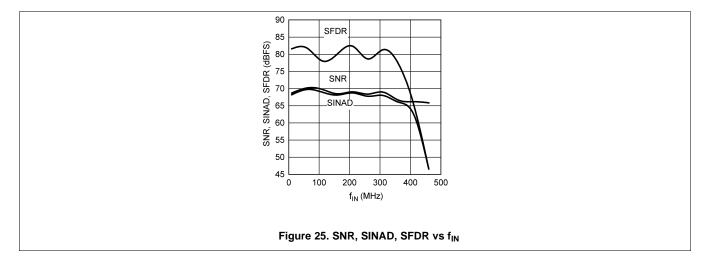

### 6.12 Typical Performance Characteristics, Dynamic Performance

Unless otherwise specified, the following specifications apply: AGND = DGND = DRGND = 0 V,  $V_A = V_D = 3.3 V$ ,  $V_{DR} = 1.8 V$ , Internal  $V_{REF} = 1 V$ ,  $f_{CLK} = 155 MHz$ ,  $V_{CM} = V_{RM}$ ,  $C_L = 5 pF/pin$ , Differential Analog Input, Single-Ended Clock Mode, Offset Binary Format. Typical values are for TA = 25°C

### **Typical Performance Characteristics, Dynamic Performance (continued)**

Unless otherwise specified, the following specifications apply: AGND = DGND = DRGND = 0 V,  $V_A = V_D = 3.3 V$ ,  $V_{DR} = 1.8 V$ , Internal  $V_{REF} = 1 V$ ,  $f_{CLK} = 155 MHz$ ,  $V_{CM} = V_{RM}$ ,  $C_L = 5 pF/pin$ , Differential Analog Input, Single-Ended Clock Mode, Offset Binary Format. Typical values are for TA = 25°C

### **Typical Performance Characteristics, Dynamic Performance (continued)**

Unless otherwise specified, the following specifications apply: AGND = DGND = DRGND = 0 V,  $V_A = V_D = 3.3 V$ ,  $V_{DR} = 1.8 V$ , Internal  $V_{REF} = 1 V$ ,  $f_{CLK} = 155 MHz$ ,  $V_{CM} = V_{RM}$ ,  $C_L = 5 pF/pin$ , Differential Analog Input, Single-Ended Clock Mode, Offset Binary Format. Typical values are for TA = 25°C

### 7 Detailed Description

### 7.1 Overview

Operating on dual 3.3-V and 1.8-V supplies, the ADC14155 digitizes a differential analog input signal to 14 bits, using a differential pipelined architecture with error correction circuitry and an on-chip sample-and-hold circuit to ensure maximum performance.

The user has the choice of using an internal 1-V stable reference, or using an external reference. The ADC14155 will accept an external reference between 0.9 V and 1.1 V (1-V recommended) which is buffered on-chip to ease the task of driving that pin. The 1.8-V output driver supply reduces power consumption and decreases the noise at the output of the converter.

The quad state function pin CLK\_SEL/DF (pin 8) allows the user to choose between using a single-ended or a differential clock input and between offset binary or 2's complement output data format. The digital outputs are CMOS compatible signals that are clocked by a synchronous data ready output signal (DRDY, pin 34) at the same rate as the clock input. For the ADC14155 the clock frequency can be between 5 MSPS and 155 MSPS with fully specified performance at 155 MSPS. The analog input is acquired at the falling edge of the clock and the digital data for a given sample is output on the falling edge of the DRDY signal and is delayed by the pipeline for 8 clock cycles. The data should be captured on the rising edge of the DRDY signal.

Power-down is selectable using the PD pin (pin 7). A logic high on the PD pin disables everything except the voltage reference circuitry and reduces the converter power consumption to 5 mW with no clock running. For normal operation, the PD pin should be connected to the analog ground (AGND). A duty cycle stabilizer maintains performance over a wide range of clock duty cycles.

### 7.2 Functional Block Diagram

### 7.3 Feature Description

### 7.3.1 Analog Inputs

### 7.3.1.1 Differential Analog Input Pins

The ADC14155QML-SP has one pair of analog signal input pins,  $V_{IN+}$  and  $V_{IN-}$ , which form a differential input pair. The input signal,  $V_{IN}$ , is defined as

$$V_{IN} = (V_{IN+}) - (V_{IN-})$$

(1)

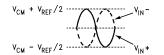

Figure 21 shows the expected input signal range. Note that the common mode input voltage,  $V_{CM}$ , should be 1.5 V. Using  $V_{RM}$  (pin 46 or 47) for  $V_{CM}$  will ensure the proper input common mode level for the analog input signal. The peaks of the individual input signals should each never exceed 2.6 V. Each analog input pin of the differential pair should have a peak-to-peak voltage equal to the reference voltage,  $V_{REF}$ , be 180° out of phase with each other and be centered around  $V_{CM}$ . The peak-to-peak voltage swing at each analog input pin should not exceed the value of the reference voltage or the output data will be clipped.

### Feature Description (continued)

Figure 21. Expected Input Signal Range

For single frequency sine waves the full scale error, E<sub>FS</sub>, in LSB can be described as approximately

$E_{FS} = 16384 (1 - \sin (90^{\circ} + dev))$

(2)

Where dev is the angular difference in degrees between the two signals having a 180° relative phase relationship to each other (see Figure 22). For single frequency inputs, angular errors result in a reduction of the effective full scale input. For complex waveforms, however, angular errors will result in distortion.

# Figure 22. Angular Errors Between The Two Input Signals Will Reduce The Output Level Or Cause Distortion

It is recommended to drive the analog inputs with a source impedance less than 100  $\Omega$ . Matching the source impedance for the differential inputs will improve even ordered harmonic performance (particularly second harmonic).

Table 2 indicates the input to output relationship of the ADC14155.

| V <sub>IN+</sub>                       | V <sub>IN</sub>          | Binary Output     | 2's Complement Output |                     |

|----------------------------------------|--------------------------|-------------------|-----------------------|---------------------|

| $V_{CM} - V_{REF} / 2$                 | $V_{CM}$ + $V_{REF}$ / 2 | 00 0000 0000 0000 | 10 0000 0000 0000     | Negative Full-Scale |

| $V_{CM} - V_{REF} / 4$                 | $V_{CM}$ + $V_{REF}$ / 4 | 01 0000 0000 0000 | 11 0000 0000 0000     |                     |

| V <sub>CM</sub>                        | V <sub>CM</sub>          | 10 0000 0000 0000 | 00 0000 0000 0000     | Mid-Scale           |

| V <sub>CM</sub> + V <sub>REF</sub> / 4 | $V_{CM} - V_{REF} / 4$   | 11 0000 0000 0000 | 01 0000 0000 0000     |                     |

| V <sub>CM</sub> + V <sub>REF</sub> / 2 | $V_{CM} - V_{REF} / 2$   | 11 1111 1111 1111 | 01 1111 1111 1111     | Positive Full-Scale |

Table 2. Input To Output Relationship

### 7.3.1.2 Driving The Analog Inputs

The V<sub>IN+</sub> and the V<sub>IN-</sub> inputs of the ADC14155QML-SP have an internal sample-and-hold circuit which consists of an analog switch followed by a switched-capacitor amplifier. The analog inputs are connected to the sampling capacitors through NMOS switches, and each analog input has parasitic capacitances associated with it.

When the clock is high, the converter is in the sample phase. The analog inputs are connected to the sampling capacitor through the NMOS switches, which causes the capacitance at the analog input pins to appear as the pin capacitance plus the internal sample and hold circuit capacitance (approximately 9 pF). While the clock level remains high, the sampling capacitor will track the changing analog input voltage. When the clock transitions from high to low, the converter enters the hold phase, during which the analog inputs are disconnected from the sampling capacitor. The last voltage that appeared at the analog input before the clock transition will be held on the sampling capacitor and will be sent to the ADC core. The capacitance seen at the analog input during the hold phase appears as the sum of the pin capacitance and the parasitic capacitances associated with the sample and hold circuit of each analog input (approximately 6 pF). Once the clock signal transitions from low to high, the analog inputs will be reconnected to the sampling capacitor to capture the next sample. Usually, there will be a difference between the held voltage on the sampling capacitor and the new voltage at the analog input. This will cause a charging glitch that is proportional to the voltage difference between the two samples to appear at the analog input pin. The input circuitry must be fast enough to allow the sampling capacitor to fully charge before the clock signal goes high again, as incomplete settling can degrade the SFDR performance.

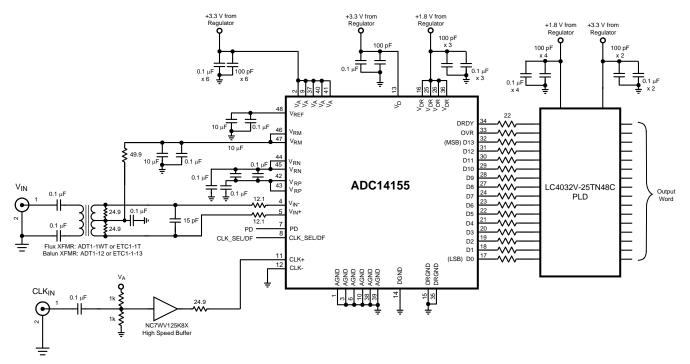

A single-ended to differential conversion circuit is shown in Figure 24. A transformer is preferred for high frequency input signals. Terminating the transformer on the secondary side provides two advantages. First, it presents a real broadband impedance to the ADC inputs and second, it provides a common path for the charging glitches from each side of the differential sample-and-hold circuit.

One short-coming of using a transformer to achieve the single-ended to differential conversion is that most RF transformers have poor low frequency performance. A differential amplifier can be used to drive the analog inputs for low frequency applications. The amplifier must be fast enough to settle from the charging glitches on the analog input resulting from the sample-and-hold operation before the clock goes high and the sample is passed to the ADC core.

The SFDR performance of the converter depends on the external signal conditioning circuity used, as this affects how quickly the sample-and-hold charging glitch will settle. An external resistor and capacitor network as shown in Figure 24 should be used to isolate the charging glitches at the ADC input from the external driving circuit and to filter the wideband noise at the converter input. These filtering components should be placed close to the ADC inputs in order to absorb the sampling glitches as close to the source of the glitches as possible. For Nyquist applications the RC pole should be at the ADC sample rate. The ADC input capacitance in the sample mode should be considered when setting the RC pole. For wideband undersampling applications, the RC pole should be set at about 1.5 to 2 times the maximum input frequency to maintain a linear delay response.

### 7.3.1.3 Input Common Mode Voltage

The input common mode voltage,  $V_{CM}$ , should be in the range of 1.4 V to 1.6 V and be a value such that the peak excursions of the analog signal do not go more negative than ground or more positive than 2.6 V. It is recommended to use  $V_{RM}$  (pin 46 or 47) as the input common mode voltage.

### 7.3.2 Reference Pins

The ADC14155QML-SP is designed to operate with an internal 1-V reference, or an external 1-V reference, but performs well with external reference voltages in the range of 0.9 V to 1.1 V. The internal 1-V reference is the default condition when no external reference input is applied to the  $V_{REF}$  pin. If a voltage in the range of 0.9 V to 1.1 V is applied to the  $V_{REF}$  pin, then that voltage is used for the reference. The  $V_{REF}$  pin should always be bypassed to ground with a 0.1-µF capacitor close to the reference input pin. Lower reference voltages will decrease the signal-to-noise ratio (SNR) of the ADC14155. Increasing the reference voltage (and the input signal swing) beyond 1.1-V may degrade THD for a full-scale input, especially at higher input frequencies.

It is important that all grounds associated with the reference voltage and the analog input signal make connection to the ground plane at a single, quiet point to minimize the effects of noise currents in the ground path.

The Reference Bypass Pins ( $V_{RP}$ ,  $V_{RM}$ , and  $V_{RN}$ ) are made available for bypass purposes. Each of these pins should be bypassed to ground with a 0.1- $\mu$ F capacitor. A 0.1- $\mu$ F and a 10- $\mu$ F capacitor should be placed between the  $V_{RP}$  and  $V_{RN}$  pins, as shown in Figure 24. This configuration is necessary to avoid reference oscillation, which could result in reduced SFDR and/or SNR.  $V_{RM}$  may be loaded to 1 mA for use as a temperature stable 1.5-V reference. The  $V_{RP}$  and  $V_{RN}$  pins should not be loaded.

Smaller capacitor values than those specified will allow faster recovery from the power down mode, but may result in degraded noise performance. Loading any of these pins, other than  $V_{RM}$ , may result in performance degradation.

The nominal voltages for the reference bypass pins are as follows:

$V_{RM} = 1.5 V$  $V_{RP} = V_{RM} + V_{REF} / 2$  $V_{RN} = V_{RM} - V_{REF} / 2$

### 7.3.3 Digital Inputs

Digital CMOS compatible inputs consist of CLK+, CLK–, PD and CLK\_SEL/DF.

### 7.3.3.1 Clock Inputs

The CLK+ and CLK- signals control the timing of the sampling process. The CLK\_SEL/DF pin (pin 8) allows the user to configure the ADC for either differential or single-ended clock mode (see Clock Mode Select/Data Format (CLK\_SEL/DF)). In differential clock mode, the two clock signals should be exactly 180° out of phase from each other and of the same amplitude. In the single-ended clock mode, the clock signal should be routed to the CLK+ input and the CLK- input should be tied to AGND in combination with the correct setting from Table 4.

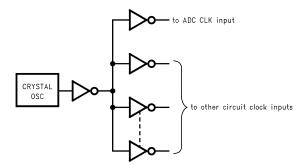

To achieve the optimum noise performance, the clock inputs should be driven with a stable, low jitter clock signal. The clock input signal should also have a short transition region. This can be achieved by passing a low-jitter sinusoidal clock source through a high speed buffer gate. This configuration is shown in Figure 24. The trace carrying the clock signal should be as short as possible and should not cross any other signal line, analog or digital, not even at 90°. Figure 24 shows the recommended clock input circuit.

The clock signal also drives an internal state machine. If the clock is interrupted, or its frequency is too low, the charge on the internal capacitors can dissipate to the point where the accuracy of the output data will degrade. This will limit the minimum sample rate.

The clock line should be terminated at its source in the characteristic impedance of that line. Care should be taken to maintain a constant clock line impedance throughout the length of the line. Refer to Application Note AN-905 (SNLA035) for information on setting characteristic impedance.

It is highly desirable that the source driving the ADC clock pins only drive that pin. However, if that source is used to drive other devices, then each driven pin should be AC terminated with a series RC to ground, such that the resistor value is equal to the characteristic impedance of the clock line and the capacitor value is

$$C \ge \frac{4 \times t_{PD} \times L}{Z_o}$$

(3)

where  $t_{PD}$  is the signal propagation rate down the clock line, "L" is the line length and  $Z_O$  is the characteristic impedance of the clock line. This termination should be as close as possible to the ADC clock pin but beyond it as seen from the clock source. Typical  $t_{PD}$  is about 150 ps/in (60 ps/cm) on FR-4 board material. The units of "L" and  $t_{PD}$  should be the same (inches or centimeters).

The duty cycle of the clock signal can affect the performance of the A/D Converter. Because achieving a precise duty cycle is difficult, the ADC14155 has a Duty Cycle Stabilizer. It is designed to maintain performance over a clock duty cycle range of 30% to 70%.

### 7.3.3.2 Power-Down (PD)

Power-down can be enabled through this two-state input pin. Table 3 shows how to power-down the ADC14155.

| PD Input Voltage | Power State |

|------------------|-------------|

| V <sub>A</sub>   | Power-down  |

| AGND             | On          |

#### Table 3. Power Down Selection Table

The power-down mode allows the user to conserve power when the converter is not being used. In the powerdown state all bias currents of the analog circuitry, excluding the reference are shut down which reduces the power consumption to 5 mW with no clock running. The output data pins are undefined and the data in the pipeline is corrupted while in the power-down mode.

The Power-down Mode Exit Cycle time is determined by the value of the capacitors on the  $V_{RP}$  (pin 42, 43),  $V_{RM}$  (pin 46, 47) and  $V_{RN}$  (pin 44, 45) reference bypass pins (pins 43, 44 and 45) and is approximately 3 ms with the recommended component values. These capacitors lose their charge in the power-down mode and must be recharged by on-chip circuitry before conversions can be accurate. Smaller capacitor values allow slightly faster recovery from the power down mode, but can result in a reduction in SNR, SINAD and ENOB performance.

### 7.3.3.3 Clock Mode Select/Data Format (CLK\_SEL/DF)

Single-ended versus differential clock mode and output data format are selectable using this quad-state function pin. Table 4 shows how to select between the clock modes and the output data formats.

### Table 4. Clock Mode And Data Format Selection Table

| CLK_SEL/DF Input Voltage | Clock Mode   | Output Data Format |

|--------------------------|--------------|--------------------|

| V <sub>A</sub>           | Differential | 2's Complement     |

| (2 / 3) * V <sub>A</sub> | Differential | Offset Binary      |

| (1 / 3) * V <sub>A</sub> | Single-Ended | 2's Complement     |

| AGND                     | Single-Ended | Offset Binary      |

### 7.4 Device Functional Modes

This devices has no specific functional modes.

### 8 Application and Implementation

### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 8.1 Application Information

To achieve the best dynamic performance, the clock source driving the CLK input must have a sharp transition region and be free of jitter. Isolate the ADC clock from any digital circuitry with buffers, as with the clock tree shown in Figure 23. The gates used in the clock tree must be capable of operating at frequencies much higher than those used if added jitter is to be prevented. Best performance will be obtained with a differential clock input drive, compared with a single-ended drive.

As mentioned in Power Supply Recommendations, it is good practice to keep the ADC clock line as short as possible and to keep it well away from any other signals. Other signals can introduce jitter into the clock signal, which can lead to reduced SNR performance, and the clock can introduce noise into other lines. Even lines with 90° crossings have capacitive coupling, so try to avoid even these 90° crossings of the clock line.

Figure 23. Isolating the ADC Clock From Other Circuitry With a Clock Tree

### 8.2 Typical Application

Figure 24. Application Circuit Using Transformer Drive Circuit

### 8.2.1 Design Requirements

We recommend that the following conditions be observed for operation of the ADC14155:

$3 V \le V_A \le 3.6 V$  $V_D = V_A$  $V_{DR} = 1.8 V$

5 MHz ≤ f<sub>CLK</sub> ≤ 155 MHz

1-V internal reference

$0.9 \text{ V} \le \text{V}_{\text{REF}} \le 1.1 \text{ V}$  (for an external reference)

$V_{CM} = 1.5 V \text{ (from } V_{RM} \text{)}$

### 8.2.2 Detailed Design Procedure

Digital outputs consist of the 1.8 V CMOS signals D0-D13, DRDY and OVR.

The ADC14155 has 16 CMOS compatible data output pins: 14 data output bits corresponding to the converted input value, a data ready (DRDY) signal that should be used to capture the output data and an over-range indicator (OVR) which is set high when the sample amplitude exceeds the 14-bit conversion range. Valid data is present at these outputs while the PD pin is low.

Data should be captured and latched with the rising edge of the DRDY signal. Depending on the setup and hold time requirements of the receiving circuit (ASIC), either the rising edge or the falling edge of the DRDY signal can be used to latch the data. Generally, rising-edge capture would maximize setup time with minimal hold time; while falling-edge-capture would maximize hold time with minimal setup time. However, actual timing for the falling-edge case depends greatly on the CLK frequency and both cases also depend on the delays inside the ASIC. Refer to the *ADC14155 Converter Electrical Characteristics (Continued) Timing and AC Characteristics*<sup>(1)</sup> table.

(1) Pre and post irradiation limits are identical to those listed in the *Electrical Characteristics* tables. Radiation testing is performed per MIL-STD-883, Test Method 1019.

### **Typical Application (continued)**