**AFE4403** ZHCSCL7C - MAY 2014 - REVISED APRIL 2021

# AFE4403 用于心率监护仪和低成本脉搏血氧仪的超小型 集成式模拟前端

## 1 特性

- 用于脉搏血氧仪和心率监测应用的完全集成式 AFE :

- 发送:

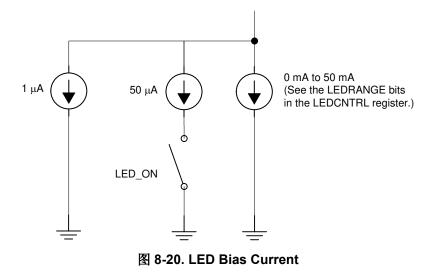

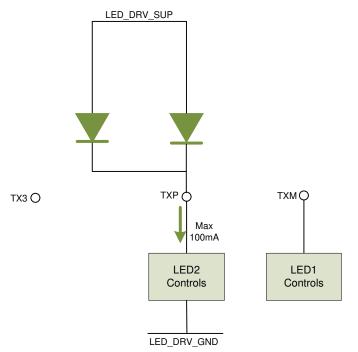

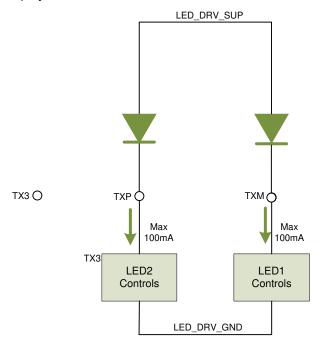

- 集成双路 LED 驱动器 (H桥或共阳极)

- 可支持 3 个 LED,适用于优化型 SPO2、HRM 或多波长 HRM

- 高达 110dB 的动态范围

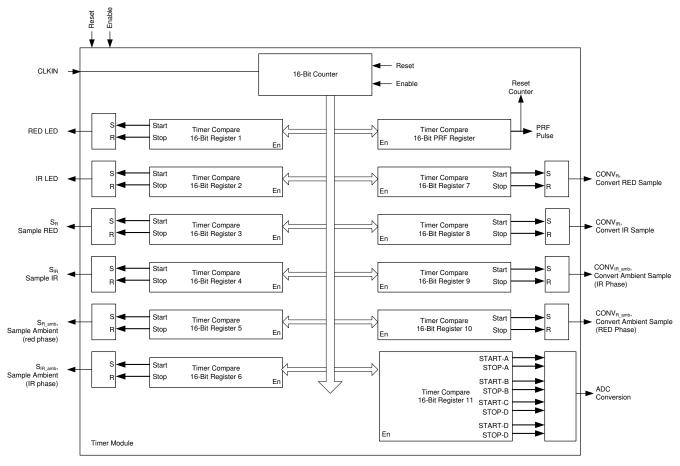

- LED 电流:

- 可编程为 100mA 电流,具有 8 位电流分辨 宻

- 30µA + 平均 LED 电流

- 可编程 LED 接通时间

- 独立的 LED2 和 LED1 电流基准

- 具有高动态范围的接收通道:

- 22 位补码格式输出

- 高达 105dB 的动态范围

- 低功耗: < 650µA

- 动态断电模式,以将电流减少至 300µA

- 可适应极宽范围的信号振幅:

- 可编程总增益:10kΩ 至 4MΩ

- 集成数字环境估算和删减功能

- 通过外部时钟或晶振实现灵活的时钟:

- 脉冲频率: 62.5SPS 至 2000SPS

- 灵活的脉冲时序和定时控制

- 输入时钟范围: 4MHz (最小值) 至 60MHz (最 大值)

- 集成式故障诊断:

- 光电二极管和 LED 开路与 短路检测

- 电源:

- Rx = 2.0V 至 3.6V

- Tx = 3.0V 至 5.25V

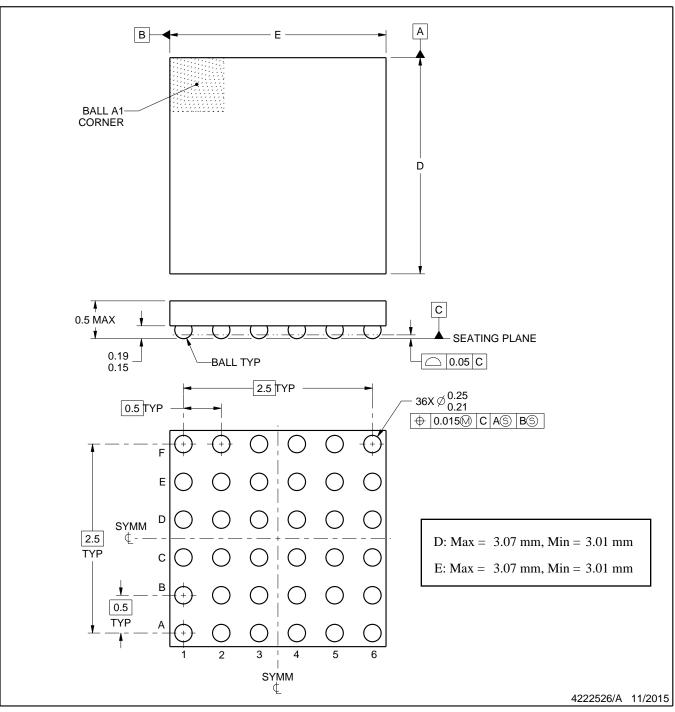

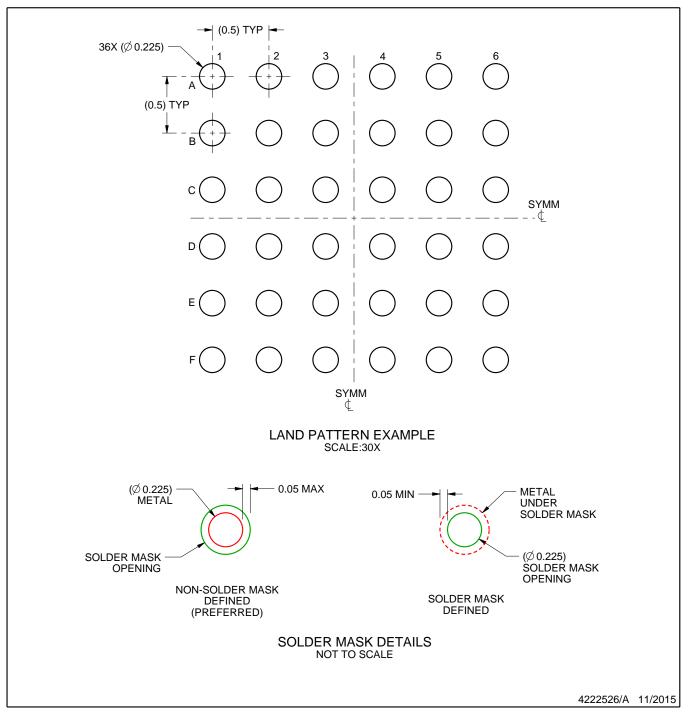

- 封装:紧凑型 DSBGA-36 (3.07mm × 3.07mm × 0.5mm)

- 额定温度范围:0°C-20°C 至 70°C

## 2 应用

- 医疗脉搏血氧仪应用

- 光学心率监视器 (HRM)

- 工业光测量应用

## 3 说明

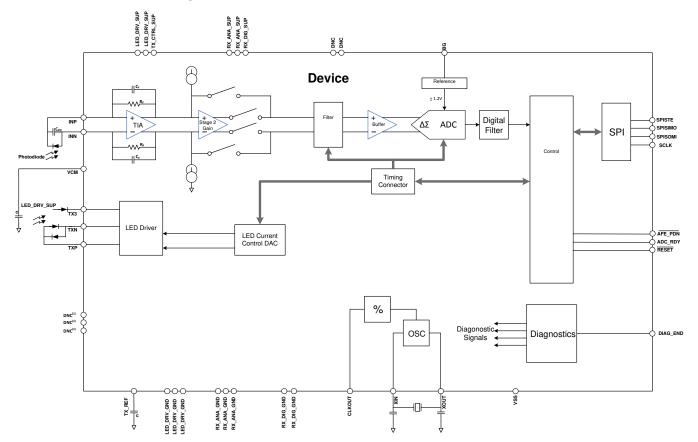

AFE4403 是一款非常适合于脉搏血氧仪应用的完全集 成式模拟前端 (AFE)。此器件包含一个具有集成模数转 换器 (ADC) 的低噪声接收器通道、一个 LED 发射部件 和针对传感器以及 LED 故障检测的诊断功能。此器件 是一款可配置定时控制器。这个灵活性使得用户能够完 全控制器件定时特性。为了轻松满足计时要求并为 AFE4403 提供一个低抖动时钟,还集成了一个由外部 晶振供频的振荡器。该器件使用 SPI<sup>™</sup> 接口与外部微控 制器或主机处理器进行通信。

此器件是一款采用紧凑型 DSBGA-36 封装 (3.07mm × 3.07mm × 0.5mm) 的完整 AFE 解决方案,其额定工作 温度范围为 -20°C 至 70°C。

**哭**件信息

| 器件型号    | 封装 <sup>(1)</sup>                | 封装尺寸(标称值)       |

|---------|----------------------------------|-----------------|

| AFE4403 | 芯片尺寸球状引脚栅<br>格阵列 (DSBGA)<br>(36) | 3.07mm × 3.07mm |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附 (1) 录。

本文档旨在为方便起见,提供有关 TI 产品中文版本的信息,以确认产品的概要。有关适用的官方英文版本的最新信息、请访问 www.ti.com,其内容始终优先。TI不保证翻译的准确性和有效性。在实际设计之前,请务必参考最新版本的英文版本。

## **Table of Contents**

| 1 特性                                            | 1              |

|-------------------------------------------------|----------------|

| 2 应用                                            |                |

| 3 说明                                            | 1              |

| 4 Revision History                              | 3              |

| 5 Device Family Options                         |                |

| 6 Pin Configuration and Functions               |                |

| 7 Specifications                                |                |

| 7.1 Absolute Maximum Ratings                    | 7              |

| 7.2 ESD Ratings                                 | 7              |

| 7.3 Recommended Operating Conditions            |                |

| 7.4 Thermal Information                         | <mark>8</mark> |

| 7.5 Electrical Characteristics                  | 9              |

| 7.6 Timing Requirements                         | . 13           |

| 7.7 Timing Requirements: Supply Ramp and Power- |                |

| Down                                            | . 14           |

| 7.8 Typical Characteristics                     | . 16           |

| 8 Detailed Description                          |                |

| 8.1 Overview.                                   | .22            |

| 8.2 Functional Block Diagram                    | .22            |

| 8.3 Feature Description                 | 23 |

|-----------------------------------------|----|

| 8.4 Device Functional Modes             |    |

| 8.5 Programming                         | 57 |

| 8.6 Register Maps                       |    |

| 9 Application Information Disclaimer    |    |

| 9.1 Application Information             |    |

| 9.2 Typical Application                 |    |

| 10 Power Supply Recommendations         |    |

| 10.1 Power Consumption Considerations   |    |

| 11 Layout                               |    |

| 11.1 Layout Guidelines                  |    |

| 11.2 Layout Example                     |    |

| 12 Device and Documentation Support     |    |

| 12.1 Trademarks                         |    |

| 12.2 静电放电警告                             |    |

| 12.3 术语表                                |    |

| 13 Mechanical, Packaging, and Orderable |    |

| Information                             | 02 |

|                                         |    |

|                                         |    |

## **4 Revision History**

| Changes from Revision B (July 2014) to Revision C (February 2021)                                                | Page              |

|------------------------------------------------------------------------------------------------------------------|-------------------|

| <ul> <li>Moved the Storage temperature range from the ESD table to the Absolute Maximum Ratings table</li> </ul> | 7                 |

| • Added paragraph starting "ADC_RDY is an interrupt issued by the AFE" in the ADC Operation a                    | nd                |

| Averaging Module section                                                                                         | 47                |

| Changed figure Averaging Module in the ADC Operation and Averaging Module section                                | 47                |

| Changed Section Operation Without Averaging                                                                      |                   |

| Changed the introduction paragraph in Section Operation With Averaging                                           |                   |

| Changed all the bullet points in Section Operation With Averaging                                                | 48                |

| • Deleted the paragraph starting with "When the number of averages is 0" in Section Operation With               |                   |

| Averaging                                                                                                        | 48                |

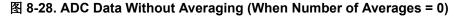

| • Changed Figure - "ADC Data Without Averaging (When Number of Averages = 0)" in Section Operation               | tion With         |

| Averaging                                                                                                        | 48                |

| • Added Note after Figure - "ADC Data Without Averaging (When Number of Averages = 0)" in Section                | n                 |

| Operation With Averaging                                                                                         | 48                |

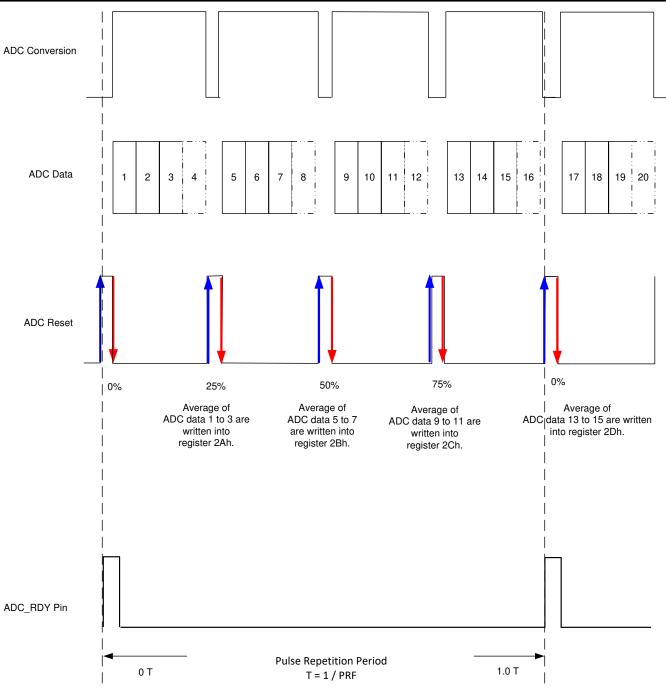

| Changed Figure - "ADC Data with Averaging Enabled" in Section Operation With Averaging                           | 48                |

| · Added Note after Figure - "ADC Data with Averaging Enabled" in Section Operation With Averaging                | 48                |

| · Changed the paragraph startng with "The sequence of the" in Section Dynamic Power-Down Mod                     | e <mark>52</mark> |

| · Added paragraph starting "The time window between the ADC_RDY" in Section Dynamic Power                        | -Down             |

| Mode                                                                                                             | <mark>52</mark>   |

| Changed LED2VAL[23:0] bit description in Section AFE Register Description                                        | <mark>63</mark>   |

| Changed ALED2VAL[23:0] bit description in Section AFE Register Description                                       | <mark>63</mark>   |

| Changed LED1VAL[23:0] bit description in Section AFE Register Description                                        | <mark>63</mark>   |

| Changed ALED1VAL[23:0] bit description in Section AFE Register Description                                       | <mark>63</mark>   |

| Changed LED2-ALED2VAL[23:0] bit description in Section AFE Register Description                                  | <mark>63</mark>   |

| Changed LED1-ALED1VAL[23:0] bit description in Section AFE Register Description                                  | 63                |

|                                                                                                                  |                   |

| C | hanges from Revision A (June 2014) to Revision B (July 2014)       | Page |

|---|--------------------------------------------------------------------|------|

| • | Changed Pin Configuration diagram: changed Top View to Bottom View | 5    |

| • | Added footnote to 图 8-6                                            | 28   |

## Changes from Revision \* (May 2014) to Revision A (June 2014)

| Changes from Revision * (May 2014) to Revision A (June 2014)                                      | Page |

|---------------------------------------------------------------------------------------------------|------|

| • 将文档状态更改为"量产数据"                                                                                  | 1    |

| • 更改了灵活的时钟特性要点的第一个和第三个子要点                                                                         | 1    |

| • 将"器件信息"表中"封装尺寸"列的最小值更改为标称值                                                                      | 1    |

| <ul> <li>Added Device Family Options table and Pin Configuration and Functions section</li> </ul> | 4    |

| Added Specifications section                                                                      | 7    |

| Added Application and Implementation section                                                      | 84   |

| Added Power Supply Recommendations section                                                        |      |

| Added Layout section                                                                              |      |

|                                                                                                   |      |

## **5 Device Family Options**

| PRODUCT | PACKAGE-LEAD | LED DRIVE<br>CONFIGURATION | LED DRIVE CURRENT<br>(mA, max) | Tx POWER SUPPLY<br>(V) |

|---------|--------------|----------------------------|--------------------------------|------------------------|

| AFE4400 | VQFN-40      | Bridge, push-pull          | 50                             | 3 to 5.25              |

| AFE4490 | VQFN-40      | Bridge, push-pull          | 50, 75, 100,<br>150, and 200   | 3 to 5.25              |

| AFE4403 | DSBGA-36     | Bridge, push-pull          | 25, 50, 75, and 100            | 3 to 5.25              |

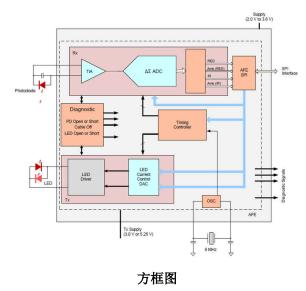

## **6** Pin Configuration and Functions

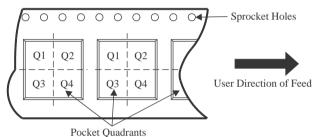

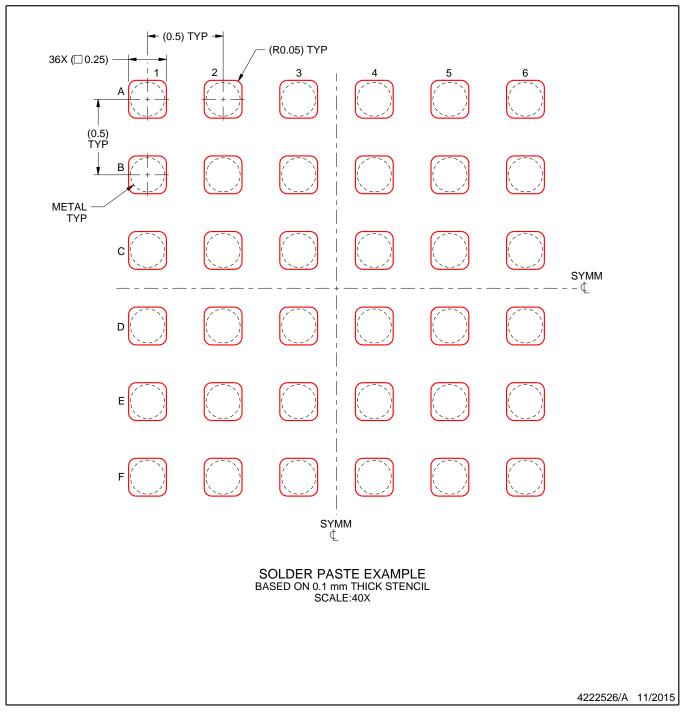

#### 图 6-1. YZP Package, DSBGA-36, (Bottom View)

#### 表 6-1. Pin Functions

| PIN                |                               |           |                                                                                                                                                                                                                                                                                                                                                      |  |

|--------------------|-------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME               | NO.                           | FUNCTION  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                          |  |

| ADC_RDY            | D5                            | Digital   | Output signal that indicates ADC conversion completion.<br>Can be connected to the interrupt input pin of an external microcontroller.                                                                                                                                                                                                               |  |

| AFE_PDN            | C3                            | Digital   | FE-only power-down input; active low.<br>an be connected to the port pin of an external microcontroller.                                                                                                                                                                                                                                             |  |

| BG                 | C2                            | Reference | Decoupling capacitor for internal band-gap voltage to ground.<br>Connect a decoupling capacitor to ground.<br>To achieve the lowest transmitter noise, use a capacitor value of 2.2 μF.<br>To reduce the recovery time from power-down (from 1 s to 0.1 s), use a capacitor value of<br>0.1 μF instead—but with slightly degraded transmitter noise. |  |

| CLKOUT             | E6                            | Digital   | Buffered 4-MHz output clock output.<br>Can be connected to the clock input pin of an external microcontroller.                                                                                                                                                                                                                                       |  |

| DIAG_END           | B4                            | Digital   | Output signal that indicates completion of diagnostics.<br>Can be connected to the port pin of an external microcontroller.                                                                                                                                                                                                                          |  |

| DNC <sup>(1)</sup> | C1, A1, E3, D3,<br>F5, B5, B6 | _         | Do not connect these pins. Leave as open circuit.                                                                                                                                                                                                                                                                                                    |  |

| INN                | F1                            | Analog    | Receiver input pin. Connect to photodiode anode.                                                                                                                                                                                                                                                                                                     |  |

| INP                | E1                            | Analog    | Receiver input pin. Connect to photodiode cathode.                                                                                                                                                                                                                                                                                                   |  |

## 表 6-1. Pin Functions (continued)

| PIN         |        |           |                                                                                                                                                                                                                                                                                                             |  |

|-------------|--------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME        | NO.    | FUNCTION  | DESCRIPTION                                                                                                                                                                                                                                                                                                 |  |

| LED_DRV_GND | A3     | Supply    | LED driver ground pin, H-bridge. Connect to common board ground.                                                                                                                                                                                                                                            |  |

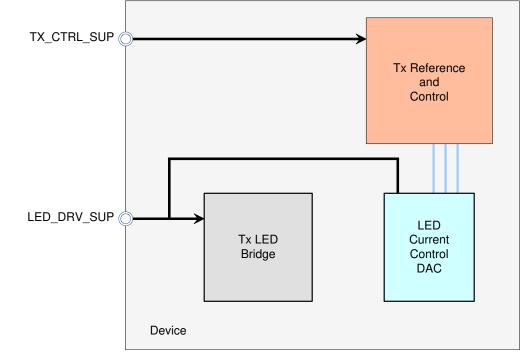

| LED_DRV_SUP | A6     | Supply    | LED driver supply pin, H-bridge. Connect to an external power supply capable of supplying the large LED current, which is drawn by this supply pin.                                                                                                                                                         |  |

| RESET       | D4     | Digital   | AFE-only reset input, active low.<br>Can be connected to the port pin of an external microcontroller                                                                                                                                                                                                        |  |

| RX_ANA_GND  | E2     | Supply    | Rx analog ground pin. Connect to common board ground.                                                                                                                                                                                                                                                       |  |

| RX_ANA_SUP  | F2, E4 | Supply    | Rx analog supply pin; 0.1-µF decoupling capacitor to ground                                                                                                                                                                                                                                                 |  |

| RX_DIG_GND  | B2, F6 | Supply    | Rx digital ground pin. Connect to common board ground.                                                                                                                                                                                                                                                      |  |

| RX_DIG_SUP  | E5     | Supply    | Rx digital supply pin; 0.1-µF decoupling capacitor to ground                                                                                                                                                                                                                                                |  |

| SCLK        | C6     | SPI       | SPI clock pin                                                                                                                                                                                                                                                                                               |  |

| SPISIMO     | C4     | SPI       | SPI serial in master out                                                                                                                                                                                                                                                                                    |  |

| SPISOMI     | C5     | SPI       | SPI serial out master in                                                                                                                                                                                                                                                                                    |  |

| SPISTE      | D6     | SPI       | SPI serial interface enable                                                                                                                                                                                                                                                                                 |  |

| TX_CTRL_SUP | A2     | Supply    | Transmit control supply pin (0.1-µF decoupling capacitor to ground)                                                                                                                                                                                                                                         |  |

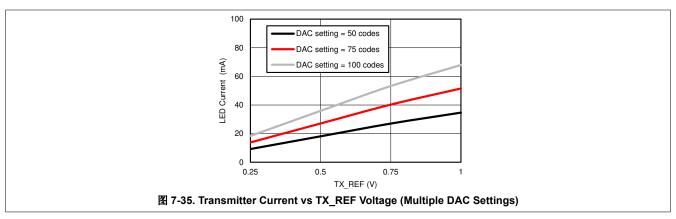

| TX_REF      | B1     | Reference | Transmitter reference voltage, 0.25 V default after reset.<br>Connect a decoupling capacitor to ground.                                                                                                                                                                                                     |  |

| TXN         | A4     | Analog    | LED driver out. Connect to LED in common anode or H-bridge configuration.                                                                                                                                                                                                                                   |  |

| TXP         | A5     | Analog    | LED driver out. Connect to LED in common anode or H-bridge configuration.                                                                                                                                                                                                                                   |  |

| TX3         | В3     | Analog    | LED driver out for third LED. Connect to optional third LED supported in common anode configuration.                                                                                                                                                                                                        |  |

| VCM         | D1     | Reference | Input common-mode voltage output.<br>This signal can be used to shield (guard) the INP, INN traces.<br>If used as a shield, then connect a series resistor (1 k $\Omega$ ) and a decoupling capacitor (10 nF) to ground.<br>If VCM is not used externally, then these external components are not required. |  |

| VSS         | D2     | Supply    | Substrate ground. Connect to common board ground.                                                                                                                                                                                                                                                           |  |

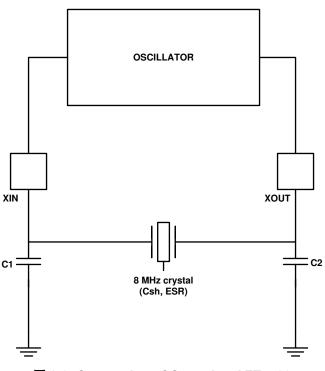

| XOUT        | F4     | Digital   | Crystal oscillator pins.<br>Connect an external crystal between these pins with the correct load capacitor<br>(as specified by vendor) to ground.                                                                                                                                                           |  |

| XIN         | F3     | Digital   | Crystal oscillator pins.<br>Connect an external crystal between these pins with the correct load capacitor<br>(as specified by vendor) to ground.                                                                                                                                                           |  |

(1) Leave pins as open circuit. Do not connect.

## **7** Specifications

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                            |                                   | MIN              | MAX              | UNIT |

|------------------------------------------------------------|-----------------------------------|------------------|------------------|------|

| RX_ANA_SUP, RX_                                            | DIG_SUP to RX_ANA_GND, RX_DIG_GND | - 0.3            | 4                | V    |

| TX_CTRL_SUP, LED_DRV_SUP to LED_DRV_GND                    |                                   | - 0.3            | 6                | V    |

| RX_ANA_GND, RX_                                            | _DIG_GND to LED_DRV_GND           | - 0.3            | 0.3              | V    |

| Analog inputs                                              |                                   | RX_ANA_GND - 0.3 | RX_ANA_SUP + 0.3 | V    |

| Digital inputs                                             |                                   | RX_DIG_GND - 0.3 | RX_DIG_SUP + 0.3 | V    |

| Input current to any pin except supply pins <sup>(2)</sup> |                                   |                  | ±7               | mA   |

| Input current                                              | Momentary                         |                  | ±50              | mA   |

|                                                            | Continuous                        |                  | ±7               | mA   |

| Operating temperatu                                        | ire range                         | 0 – 20           | 70               | °C   |

| Maximum junction temperature, T <sub>J</sub>               |                                   |                  | 125              | °C   |

| Storage temperature                                        | e range, T <sub>stg</sub>         | - 60             | 150              | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Input terminals are diode-clamped to the power-supply rails. Input signals that can swing beyond the supply rails must be currentlimited to 10 mA or less.

### 7.2 ESD Ratings

|                    |                         |                                                                                          | MIN    | MAX  | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------|--------|------|------|

| V                  | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | - 1000 | 1000 | V    |

| V <sub>(ESD)</sub> |                         | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | - 250  | 250  | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|             | PARAMETER                                                   |                            | MIN                                                                        | MAX  | UNIT |

|-------------|-------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------|------|------|

| SUPPLIES    |                                                             |                            |                                                                            | •    |      |

| RX_ANA_SUP  | AFE analog supply                                           |                            | 2.0                                                                        | 3.6  | V    |

| RX_DIG_SUP  | AFE digital supply                                          |                            | 2.0                                                                        | 3.6  | V    |

| TX_CTRL_SUP | Transmit controller supply                                  |                            | 3.0                                                                        | 5.25 | V    |

| LED DRV SUP | Transmit LED driver supply<br>Common anode<br>configuration | H-bridge                   | [3.0 or $(0.75 + V_{LED} + V_{CABLE})^{(1)}$ (2),<br>whichever is greater] | 5.25 | V    |

| LED_DRV_SOP |                                                             | Common anode configuration | [3.0 or $(0.5 + V_{LED} + V_{CABLE})^{(1)}$ (2),<br>whichever is greater]  | 5.25 | V    |

|             | Difference between LED_DRV<br>TX_CTRL_SUP                   | SUP and                    | - 0.3                                                                      | 0.3  | V    |

| TEMPERATURE |                                                             |                            |                                                                            |      |      |

|             | Specified temperature range                                 |                            | - 20                                                                       | 70   | °C   |

|             | Storage temperature range                                   |                            | - 60                                                                       | 150  | °C   |

(1) V<sub>LED</sub> refers to the maximum voltage drop across the external LED (at maximum LED current) connected between the TXP and TXN pins (in H-bridge mode) and from the TXP and TXN pins to LED\_DRV\_SUP (in the common anode configuration).

(2) V<sub>CABLE</sub> refers to voltage drop across any cable, connector, or any other component in series with the LED.

#### 7.4 Thermal Information

|                        |                                              | AFE4403    |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | YZP (WCSP) | UNIT |

|                        |                                              | 36 BALLS   |      |

| R <sub>0 JA</sub>      | Junction-to-ambient thermal resistance       | 49.8       |      |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 0.2        |      |

| R <sub>0 JB</sub>      | Junction-to-board thermal resistance         | 8.5        | °C/W |

| ΨJT                    | Junction-to-top characterization parameter   | 0.8        | C/W  |

| ψ <sub>JB</sub>        | Junction-to-board characterization parameter | 8.5        |      |

| R <sub>0 JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | n/a        |      |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

#### 7.5 Electrical Characteristics

Minimum and maximum specifications are at  $T_A = -20^{\circ}$ C to 70°C, typical specifications are at 25°C. Crystal mode enabled, detector capacitor = 50 pF differential, ADC averaging set to maximum allowed for each PRF, TX\_REF voltage set to 0.5 V, and CLKOUT tri-stated, at RX\_ANA\_SUP = RX\_DIG\_SUP = 3 V, TX\_CTRL\_SUP = LED\_DRV\_SUP = 3.3 V, stage 2 amplifier disabled, and f<sub>CLK</sub> = 8 MHz, unless otherwise noted.

|                     | PARAMETER                                                                 | TEST CONDITIONS                                                                                                          | MIN TYP                                          | MAX    | UNIT             |

|---------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------|------------------|

| PERFOR              | MANCE (Full-Signal Chain)                                                 |                                                                                                                          |                                                  |        |                  |

|                     |                                                                           | R <sub>F</sub> = 10 k Ω                                                                                                  | 50                                               |        | μA               |

|                     |                                                                           | R <sub>F</sub> = 25 k Ω                                                                                                  | 20                                               |        | μA               |

|                     |                                                                           | R <sub>F</sub> = 50 k Ω                                                                                                  | 10                                               |        | μA               |

| I <sub>IN FS</sub>  | Full-scale input current                                                  | R <sub>F</sub> = 100 k Ω                                                                                                 | 5                                                |        | μA               |

| _                   |                                                                           | R <sub>F</sub> = 250 k Ω                                                                                                 | 2                                                |        | μA               |

|                     |                                                                           | R <sub>F</sub> = 500 k Ω                                                                                                 | 1                                                |        | μA               |

|                     |                                                                           | R <sub>F</sub> = 1 MΩ                                                                                                    | 0.5                                              |        | μA               |

| PRF                 | Pulse repetition frequency                                                |                                                                                                                          | 62.5                                             | 2000   | SPS              |

| DC <sub>PRF</sub>   | PRF duty cycle                                                            |                                                                                                                          |                                                  | 25%    |                  |

| CMRR                | Common mode relaction ratio                                               | $f_{CM}$ = 50 Hz and 60 Hz, LED1 and LED2 with $R_{SERIES}$ = 500 k $\Omega$ , $R_{F}$ = 500 k $\Omega$                  | 75                                               |        | dB               |

| UNIKK               | Common-mode rejection ratio                                               | $f_{CM}$ = 50 Hz and 60 Hz, LED1-AMB and LED2-AMB with $R_{SERIES}$ = 500 k $\Omega$ , $R_{F}$ = 500 k $\Omega$          | 95                                               |        | dB               |

| PSRR <sub>LED</sub> | PSRR, transmit LED driver                                                 | With respect to ripple on LED_DRV_SUP                                                                                    | 75                                               |        | dB               |

| PSRR <sub>Tx</sub>  | PSRR, transmit control                                                    | With respect to ripple on TX_CTRL_SUP                                                                                    | 60                                               |        | dB               |

| PSRR <sub>Rx</sub>  | PSRR, receiver                                                            | With respect to ripple on RX_ANA_SUP and RX_DIG_SUP                                                                      | 60                                               |        | dB               |

|                     | Total integrated noise current, input-                                    | $R_F$ = 100 k $\Omega$ , PRF = 600 Hz, duty cycle = 5%                                                                   | 25                                               |        | pA <sub>RM</sub> |

|                     | referred (receiver with transmitter loop back, 0.1-Hz to 20-Hz bandwidth) | R <sub>F</sub> = 500 k Ω , PRF = 600 Hz, duty cycle = 5%                                                                 | 6                                                |        | pA <sub>RM</sub> |

| RECEIVE             | R FUNCTIONAL BLOCK LEVEL SPECIF                                           |                                                                                                                          | I                                                | I      |                  |

|                     | Total integrated noise current, input                                     | $R_{\text{F}}$ = 500 k $_{\Omega}$ , ambient cancellation enabled, stage 2 gain = 4, PRF = 1200 Hz, LED duty cycle = 25% | % 3.2                                            |        | рА <sub>RM</sub> |

|                     | referred (receiver alone) over 0.1-Hz to 20-Hz bandwidth                  | $R_{F}$ = 500 k $\Omega$ , ambient cancellation enabled, stage 2 gain = 4, PRF = 1200 Hz, LED duty cycle = 5%            | 5.3                                              |        | pA <sub>RM</sub> |

| I-V TRAN            | SIMPEDANCE AMPLIFIER                                                      |                                                                                                                          |                                                  |        |                  |

| G                   | Gain                                                                      | $R_F = 10 \text{ k} \Omega \text{ to } 1 \text{ M} \Omega$                                                               | See the <i>Receiver Ch</i><br>section for detail | 1      | V/µA             |

|                     | Gain accuracy                                                             |                                                                                                                          | ±7%                                              |        |                  |

|                     | Feedback resistance                                                       | R <sub>F</sub>                                                                                                           | 10k, 25k, 50k, 100k,<br>500k, and 1M             | 250k,  | Ω                |

|                     | Feedback resistor tolerance                                               | R <sub>F</sub>                                                                                                           | ±20%                                             |        |                  |

|                     | Feedback capacitance                                                      | C <sub>F</sub>                                                                                                           | 5, 10, 25, 50, 100, an                           | id 250 | pF               |

|                     | Feedback capacitor tolerance                                              | C <sub>F</sub>                                                                                                           | ±20%                                             |        |                  |

|                     | Full-scale differential output voltage                                    |                                                                                                                          | 1                                                |        | V                |

|                     | Common-mode voltage on input pins                                         | Set internally                                                                                                           | 0.9                                              |        | V                |

|                     | External differential input capacitance                                   | Includes equivalent capacitance of photodiode, cables,<br>EMI filter, and so forth                                       | 10                                               | 1000   | pF               |

|                     | Shield output voltage, $V_{CM}$                                           | With a 1-k $\Omega$ series resistor and a 10-nF decoupling capacitor to ground                                           | 0.8 0.9                                          | 1      | V                |

## 7.5 Electrical Characteristics (continued)

Minimum and maximum specifications are at  $T_A = -20^{\circ}$ C to 70°C, typical specifications are at 25°C. Crystal mode enabled, detector capacitor = 50 pF differential, ADC averaging set to maximum allowed for each PRF, TX\_REF voltage set to 0.5 V, and CLKOUT tri-stated, at RX\_ANA\_SUP = RX\_DIG\_SUP = 3 V, TX\_CTRL\_SUP = LED\_DRV\_SUP = 3.3 V, stage 2 amplifier disabled, and  $f_{CLK} = 8$  MHz, unless otherwise noted.

|         | PARAMETER                                              | TEST CONDITIONS                                                                                                       | MIN       | TYP                                       | MAX   | UNIT             |

|---------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------|-------------------------------------------|-------|------------------|

|         | T CANCELLATION STAGE                                   |                                                                                                                       |           |                                           |       |                  |

|         | Gain                                                   |                                                                                                                       | 0, 3.5, 6 | 5, 9.5, and <sup>2</sup>                  | 12    | dB               |

|         | Current DAC range                                      |                                                                                                                       | 0         |                                           | 10    | μA               |

|         | Current DAC step size                                  |                                                                                                                       |           | 1                                         |       | μA               |

| LOW-PA  | SS FILTER                                              |                                                                                                                       |           |                                           |       |                  |

|         | Low-pass corner frequency                              | 3-dB attenuation                                                                                                      |           | 500                                       |       | Hz               |

|         |                                                        | Duty cycle = 25%                                                                                                      |           | 0.004                                     |       | dB               |

|         | Pass-band attenuation, 2 Hz to 10 Hz                   | Duty cycle = 10%                                                                                                      |           | 0.041                                     |       | dB               |

|         | Filter settling time                                   | After diagnostics mode                                                                                                |           | 28                                        |       | ms               |

| ANALOG  | -TO-DIGITAL CONVERTER                                  | -                                                                                                                     |           |                                           |       |                  |

|         | Resolution                                             |                                                                                                                       |           |                                           | 22    | Bits             |

|         | Sample rate                                            | See the ADC Operation and Averaging Module section                                                                    |           | 4 × PRF                                   |       | SPS              |

|         | ADC full-scale voltage                                 |                                                                                                                       |           | ±1.2                                      |       | V                |

|         | ADC conversion time                                    | See the ADC Operation and Averaging Module section                                                                    |           |                                           | PRF/4 | μs               |

|         | ADC reset time <sup>(2)</sup>                          |                                                                                                                       | 2         |                                           |       | t <sub>CLK</sub> |

| TRANSM  | IITTER                                                 |                                                                                                                       |           |                                           |       |                  |

|         | Output current range                                   |                                                                                                                       |           | ble, 0 to 10<br>EDCNTRL:<br>gister for de | LED   | mA               |

|         | LED current DAC error                                  |                                                                                                                       |           | ±10%                                      |       |                  |

|         | Output current resolution                              |                                                                                                                       |           | 8                                         |       | Bits             |

|         | Transmitter noise dynamic range,                       | At 25-mA output current                                                                                               |           | 110                                       |       | dB               |

|         | over 0.1-Hz to 20-Hz bandwidth,<br>TX_REF set to 0.5 V | At 50-mA output current                                                                                               |           | 110                                       |       | dB               |

|         | Minimum sample time of LED1 and LED2 pulses            |                                                                                                                       |           | 50                                        |       | μs               |

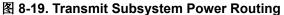

|         |                                                        | LED_ON = 0                                                                                                            |           | 1                                         |       | μA               |

|         | LED current DAC leakage current                        | LED_ON = 1                                                                                                            |           | 50                                        |       | μA               |

|         | LED current DAC linearity                              | Percent of full-scale current                                                                                         |           | 0.50                                      |       | %                |

|         | Output current settling time                           | From zero current to 50 mA                                                                                            |           | 7                                         |       | μs               |

|         | (with resistive load)                                  | From 50 mA to zero current                                                                                            |           | 7                                         |       | μs               |

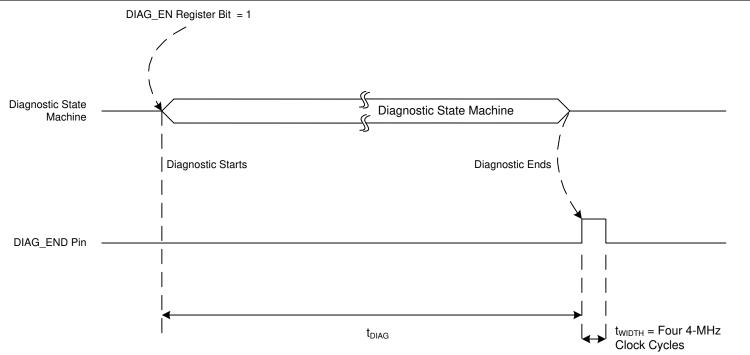

| DIAGNO  | STICS                                                  |                                                                                                                       |           |                                           | I     |                  |

|         | Duration of diagnostics state machine                  | Start of diagnostics after the DIAG_EN register bit is set.<br>End of diagnostic is indicated by DIAG_END going high. |           | 16                                        |       | ms               |

|         | Open fault resistance                                  |                                                                                                                       |           | > 100                                     |       | kΩ               |

|         | Short fault resistance                                 |                                                                                                                       |           | < 10                                      |       | kΩ               |

| INTERNA | AL OSCILLATOR                                          | 1                                                                                                                     | I         |                                           |       |                  |

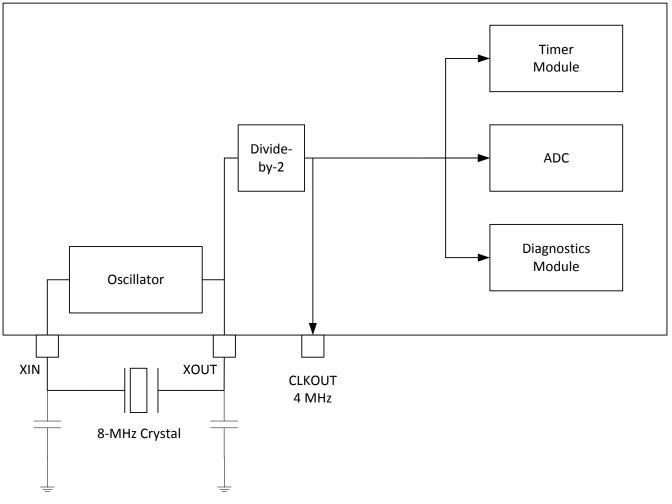

| CLKOUT  | CLKOUT frequency                                       | With an 8-MHz crystal connected to the XIN, XOUT pins                                                                 |           | 4                                         |       | MHz              |

|         | CLKOUT duty cycle                                      |                                                                                                                       |           | 50%                                       |       |                  |

|         | Crystal oscillator start-up time                       | With an 8-MHz crystal connected to the XIN, XOUT pins                                                                 |           | 200                                       |       | μs               |

### 7.5 Electrical Characteristics (continued)

Minimum and maximum specifications are at  $T_A = -20^{\circ}$ C to 70°C, typical specifications are at 25°C. Crystal mode enabled, detector capacitor = 50 pF differential, ADC averaging set to maximum allowed for each PRF, TX\_REF voltage set to 0.5 V, and CLKOUT tri-stated, at RX\_ANA\_SUP = RX\_DIG\_SUP = 3 V, TX\_CTRL\_SUP = LED\_DRV\_SUP = 3.3 V, stage 2 amplifier disabled, and f<sub>CLK</sub> = 8 MHz, unless otherwise noted.

|                      | PARAMETER                                                   | TEST CONDITIONS                                                                           | MIN         | TYP      | MAX               | UNIT            |

|----------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------|----------|-------------------|-----------------|

| EXTERN               | AL CLOCK                                                    |                                                                                           |             |          |                   |                 |

|                      | •• • • • • • • • • •                                        | For SPO2 applications                                                                     |             | 50       |                   | ps              |

|                      | Maximum allowable external clock jitter                     | For optical heart rate only                                                               |             |          | 1000              | ps              |

|                      | External clock input frequency <sup>(1)</sup>               | ±2%                                                                                       | 4           | 8        | 60                | MHz             |

|                      | <b>E 1 1 1 1 1 1</b>                                        | Voltage input high (V <sub>IH</sub> )                                                     | 0.75 × RX_[ | DIG_SUP  |                   | V               |

|                      | External clock input voltage                                | Voltage input low (V <sub>IL</sub> )                                                      | 0.25 × RX_[ | DIG_SUP  |                   | V               |

| TIMING               |                                                             | 1                                                                                         |             |          |                   |                 |

|                      | Wake-up time from complete<br>power-down                    |                                                                                           |             | 1000     |                   | ms              |

|                      | Wake-up time from Rx power-down                             |                                                                                           |             | 100      |                   | μs              |

|                      | Wake-up time from Tx power-down                             |                                                                                           |             | 1000     |                   | ms              |

| t <sub>RESET</sub>   | Active low RESET pulse duration                             |                                                                                           |             | 1        |                   | ms              |

| t <sub>DIAGEND</sub> | DIAG_END pulse duration at the<br>completion of diagnostics |                                                                                           |             | 4        |                   | CLKOU<br>cycles |

| t <sub>ADCRDY</sub>  | ADC_RDY pulse duration                                      |                                                                                           |             | 1        |                   | CLKOU<br>cycle  |

| DIGITAL              | SIGNAL CHARACTERISTICS                                      |                                                                                           |             |          |                   |                 |

| V <sub>IH</sub>      | Logic high input voltage                                    | AFE_ PDN, SCLK, SPISIMO, SPISTE, RESET                                                    | 0.8 DVDD    | > 1.3    | DVDD +<br>0.1     | V               |

| V <sub>IL</sub>      | Logic low input voltage                                     | AFE_ PDN, SCLK, SPISIMO, SPISTE, RESET                                                    | - 0.1       | < 0.4    | 0.2<br>DVDD       | V               |

| I <sub>IN</sub>      | Logic input current                                         | 0 V < V <sub>DigitalInput</sub> < DVDD                                                    | - 10        |          | 10                | μA              |

| V <sub>OH</sub>      | Logic high output voltage                                   | DIAG_END, SPISOMI, ADC_RDY, CLKOUT                                                        | 0.9 DVDD    | > (RX_DI | G_SUP -<br>0.2 V) | V               |

| V <sub>OL</sub>      | Logic low output voltage                                    | DIAG_END, SPISOMI, ADC_RDY, CLKOUT                                                        |             | < 0.4    | 0.1<br>DVDD       | V               |

| SUPPLY               | CURRENT                                                     |                                                                                           | k           |          |                   |                 |

|                      |                                                             | RX_ANA_SUP = 3.0 V, with 8-MHz clock running,<br>Rx stage 2 disabled                      |             | 0.6      |                   | mA              |

|                      | Receiver analog supply current                              | RX_ANA_SUP = 3.0 V, with 8-MHz clock running,<br>Rx stage 2 enabled                       |             | 0.7      |                   | mA              |

|                      |                                                             | RX_ANA_SUP = 3.0 V, with 8-MHz clock running,<br>Rx stage 2 disabled, external clock mode |             | 0.49     |                   | mA              |

|                      | Receiver digital supply current                             | RX_DIG_SUP = 3.0 V                                                                        |             | 0.15     |                   | mA              |

|                      | LED driver supply current                                   | With zero LED current setting                                                             |             | 30       |                   | μA              |

|                      | Transmitter control supply current                          |                                                                                           |             | 15       |                   | μA              |

|                      |                                                             | Receiver current only (RX_ANA_SUP)                                                        |             | 3        |                   | μA              |

|                      | Complete power-down                                         | Receiver current only (RX_DIG_SUP)                                                        |             | 3        |                   | μA              |

|                      | (using the AFE_ PDN pin)                                    | Transmitter current only (LED_DRV_SUP)                                                    |             | 1        |                   | μA              |

|                      |                                                             | Transmitter current only (TX_CTRL_SUP)                                                    |             | 1        |                   | μA              |

|                      | Devuer devue Du eler -                                      | Receiver current only (RX_ANA_SUP)                                                        |             | 200      |                   | μA              |

|                      | Power-down Rx alone                                         | Receiver current only (RX_DIG_SUP)                                                        |             | 150      |                   | μA              |

|                      | Device device Tot also                                      | Transmitter current only (LED_DRV_SUP)                                                    |             | 2        |                   | μA              |

|                      | Power-down Tx alone                                         | Transmitter current only (TX_CTRL_SUP)                                                    |             | 2        |                   | μA              |

## 7.5 Electrical Characteristics (continued)

Minimum and maximum specifications are at  $T_A = -20^{\circ}$ C to 70°C, typical specifications are at 25°C. Crystal mode enabled, detector capacitor = 50 pF differential, ADC averaging set to maximum allowed for each PRF, TX\_REF voltage set to 0.5 V, and CLKOUT tri-stated, at RX\_ANA\_SUP = RX\_DIG\_SUP = 3 V, TX\_CTRL\_SUP = LED\_DRV\_SUP = 3.3 V, stage 2 amplifier disabled, and  $f_{CLK} = 8$  MHz, unless otherwise noted.

| PARAMETER                              | 1           | TEST                          | CONDITIONS                                 | MIN TYP | MAX | UNIT |

|----------------------------------------|-------------|-------------------------------|--------------------------------------------|---------|-----|------|

| POWER DISSIPATION                      |             |                               |                                            |         |     |      |

|                                        | LED_DRV_SUP | Does not include LED cur      | rent.                                      | 1       |     | μA   |

| Power-down with the                    | TX_CTRL_SUP |                               |                                            | 1       |     | μA   |

| AFE_PDN pin                            | RX_ANA_SUP  |                               |                                            | 5       |     | μA   |

|                                        | RX_DIG_SUP  |                               |                                            | 0.1     |     | μA   |

|                                        | LED_DRV_SUP | Does not include LED cur      | rent.                                      | 1       |     | μA   |

| Power-down with the                    | TX_CTRL_SUP |                               |                                            | 1       |     | μA   |

| PDNAFE register bit                    | RX_ANA_SUP  |                               |                                            | 15      |     | μA   |

|                                        | RX_DIG_SUP  |                               |                                            | 20      |     | μA   |

|                                        | LED_DRV_SUP | Does not include LED cur      | rent.                                      | 30      |     | μA   |

| Power-down Rx                          | TX_CTRL_SUP |                               |                                            | 15      |     | μA   |

| F Owel-down TX                         | RX_ANA_SUP  |                               |                                            | 200     |     | μA   |

|                                        | RX_DIG_SUP  |                               |                                            | 150     |     | μA   |

|                                        | LED_DRV_SUP | Does not include LED cur      | rent.                                      | 2       |     | μA   |

| Power-down Tx                          | TX_CTRL_SUP |                               |                                            | 2       |     | μA   |

| T Ower-down TX                         | RX_ANA_SUP  |                               |                                            | 600     |     | μA   |

|                                        | RX_DIG_SUP  |                               |                                            | 150     |     | μA   |

|                                        | LED_DRV_SUP | Does not include LED cur      | rent.                                      | 30      |     | μA   |

| After reset, with 8-                   | TX_CTRL_SUP |                               |                                            | 15      |     | μA   |

| MHz clock running                      | RX_ANA_SUP  |                               |                                            | 600     |     | μA   |

|                                        | RX_DIG_SUP  |                               |                                            | 150     |     | μA   |

|                                        | LED_DRV_SUP | Does not include LED cur      | rent.                                      | 30      |     | μA   |

| With stage 2 mode<br>enabled and 8-MHz | TX_CTRL_SUP |                               |                                            | 15      |     | μA   |

| clock running                          | RX_ANA_SUP  |                               |                                            | 700     |     | μA   |

|                                        | RX_DIG_SUP  |                               |                                            | 150     |     | μA   |

|                                        | LED_DRV_SUP | Does not include LED current. |                                            | 7       |     | μA   |

| Dynamic power-<br>down mode enabled    | TX_CTRL_SUP |                               | PRF = 100 Hz,<br>PDN_CYCLE duration = 8 ms | 5       |     | μA   |

| down mode enabled                      | RX_ANA_SUP  |                               |                                            | 205     |     | μA   |

|                                        | RX_DIG_SUP  |                               |                                            | 150     |     | μA   |

(1) Refer to the CLKDIV[2:0] register bits for a detailed list of input clock frequencies that are supported.

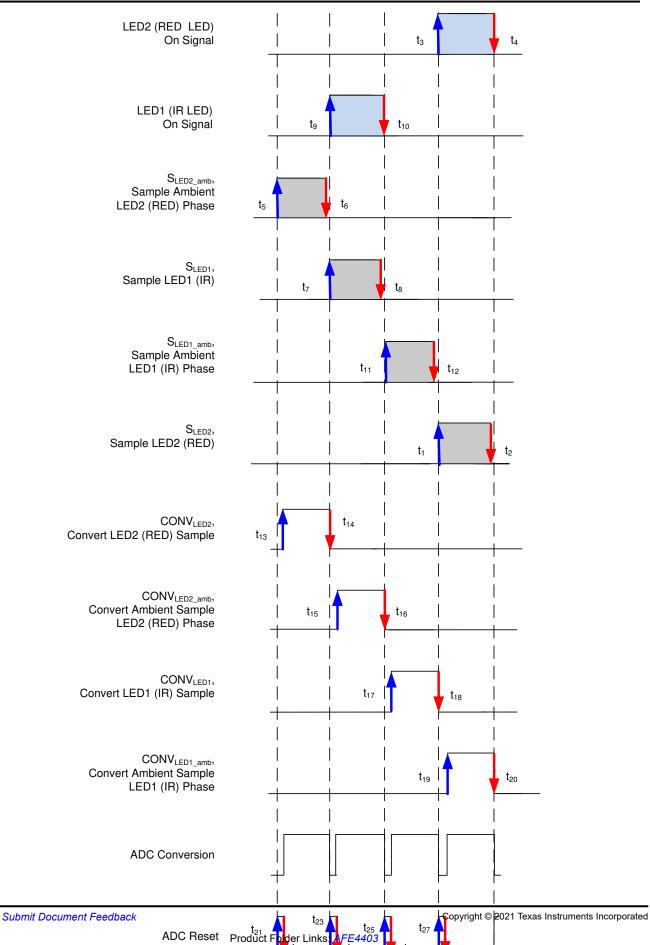

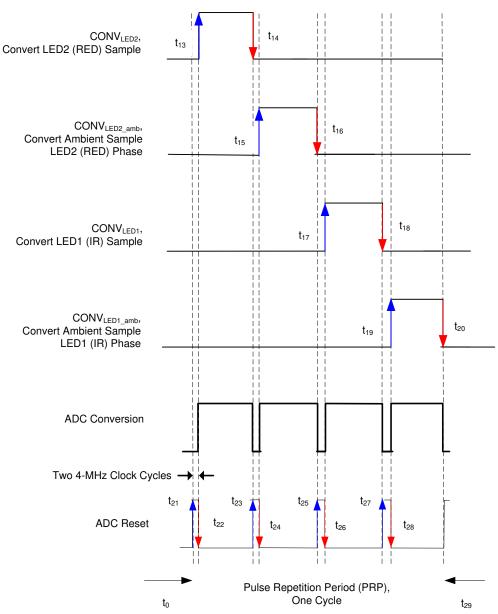

(2) A low ADC reset time can result in a small component of the LED signal leaking into the ambient phase. With an ADC reset of two clock cycles, a - 60-dB leakage is expected. In many cases, this leakage does not affect system performance. However, if this crosstalk must be completely eliminated, a longer ADC reset time of approximately six clock cycles is recommended for t<sub>22</sub>, t<sub>24</sub>, t<sub>26</sub>, and t<sub>28</sub> in <sup>K</sup>/<sub>8</sub> 8-13.

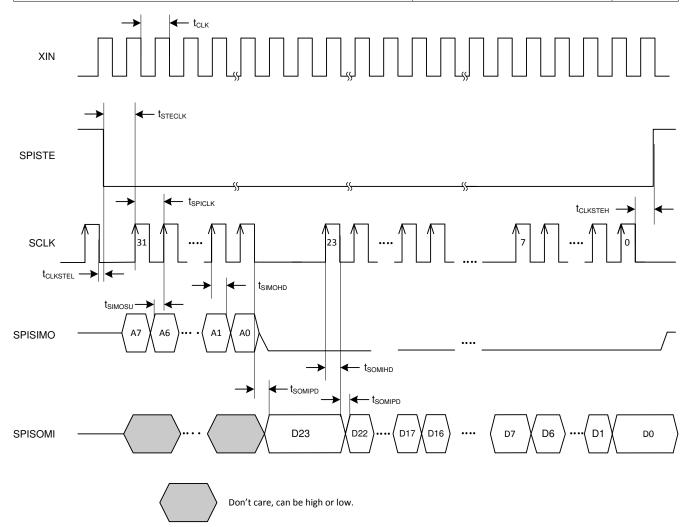

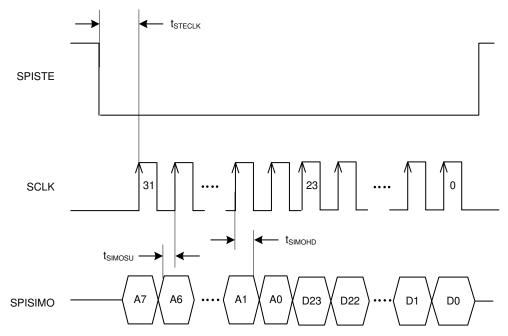

## 7.6 Timing Requirements

|                        | PARAMETER                                         | MIN  | TYP | MAX | UNIT              |

|------------------------|---------------------------------------------------|------|-----|-----|-------------------|

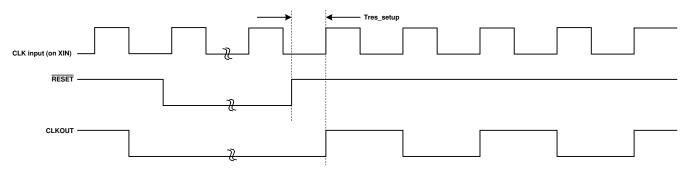

| t <sub>CLK</sub>       | Clock frequency on the XIN pin                    |      | 8   |     | MHz               |

| t <sub>SCLK</sub>      | Serial shift clock period                         | 62.5 |     |     | ns                |

| t <sub>STECLK</sub>    | STE low to SCLK rising edge, setup time           | 10   |     |     | ns                |

| t <sub>CLKSTEH,L</sub> | SCLK transition to SPI STE high or low            | 10   |     |     | ns                |

| t <sub>SIMOSU</sub>    | SIMO data to SCLK rising edge, setup time         | 10   |     |     | ns                |

| t <sub>SIMOHD</sub>    | Valid SIMO data after SCLK rising edge, hold time | 10   |     |     | ns                |

| t <sub>SOMIPD</sub>    | SCLK falling edge to valid SOMI, setup time       | 17   |     |     | ns                |

| t <sub>SOMIHD</sub>    | SCLK rising edge to invalid data, hold time       | 0.5  |     |     | t <sub>SCLK</sub> |

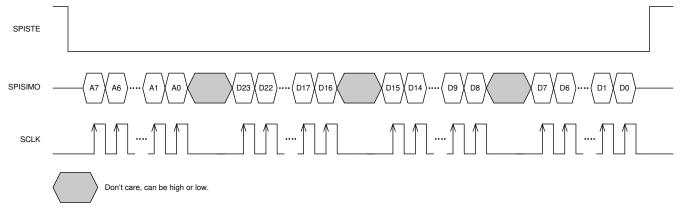

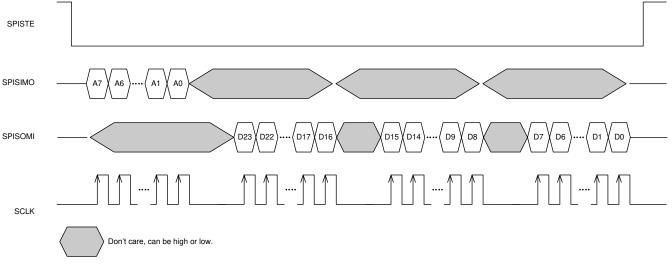

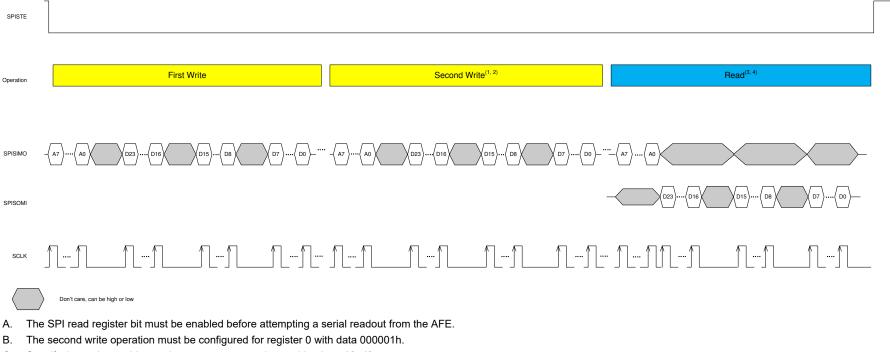

- A. The SPI\_READ register bit must be enabled before attempting a register read.

- B. Specify the register address whose contents must be read back on A[7:0].

- C. The AFE outputs the contents of the specified register on the SPISOMI pin.

#### 图 7-1. Serial Interface Timing Diagram, Read Operation

图 7-2. Serial Interface Timing Diagram, Write Operation

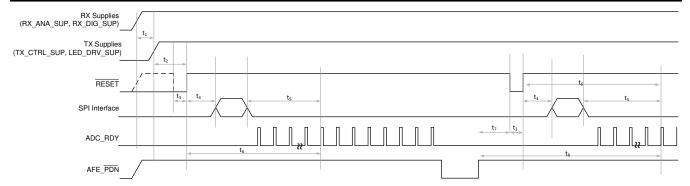

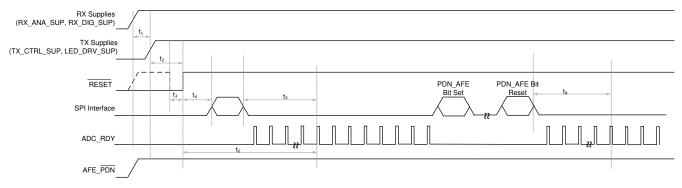

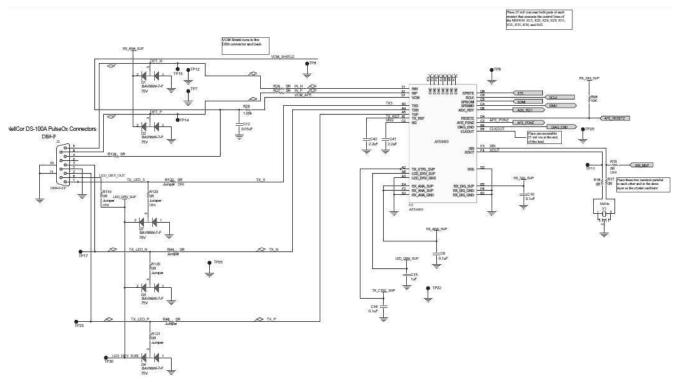

#### 7.7 Timing Requirements: Supply Ramp and Power-Down

|                | PARAMETER                                                                                                          | VALUE                                                                        |

|----------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| t <sub>1</sub> | Time between Rx and Tx supplies ramping up                                                                         | Keep as small as possible (for example, ±10 ms)                              |

| t <sub>2</sub> | Time between both supplies stabilizing and high-going RESET edge                                                   | > 100 ms                                                                     |

| t <sub>3</sub> | RESET pulse duration                                                                                               | > 0.5 ms                                                                     |

| t <sub>4</sub> | Time between RESET and SPI commands                                                                                | > 1 µs                                                                       |

| t <sub>5</sub> | Time between SPI commands and the ADC_RESET which corresponds to valid data                                        | > 3 ms of cumulative sampling time in each phase <sup>(1) (2)</sup> $_{(3)}$ |

| t <sub>6</sub> | Time between RESET pulse and high-accuracy data coming out of the signal chain                                     | > 1 s <sup>(3)</sup>                                                         |

| t <sub>7</sub> | Time from AFE_ PDN high-going edge and RESET pulse <sup>(4)</sup>                                                  | > 100 ms                                                                     |

| t <sub>8</sub> | Time from AFE_ PDN high-going edge (or PDN_AFE bit reset) to high-<br>accuracy data coming out of the signal chain | > 1 s <sup>(3)</sup>                                                         |

(1) This time is required for each of the four switched RC filters to fully settle to the new settings. The same time is applicable whenever there is a change to any of the signal chain controls (for example, LED current setting, TIA gain, and so forth).

(2) If the SPI commands involve a change in the TX\_REF value from its default, then there is additional wait time of approximately 1 s (for a 2.2-µF decoupling capacitor on the TX\_REF pin).

(3) Dependent on the value of the capacitors on the BG and TX\_REF pins. The 1-s wait time is necessary when the capacitors are 2.2 µF and scale down proportionate to the capacitor value. A very low capacitor (for example, 0.1 µF) on these pins causes the transmitter dynamic range to reduce to approximately 100 dB.

(4) After an active power-down from AFE\_PDN, the device should be reset using a low-going RESET pulse.

图 7-3. Supply Ramp and Hardware Power-Down Timing

图 7-4. Supply Ramp and Software Power-Down Timing

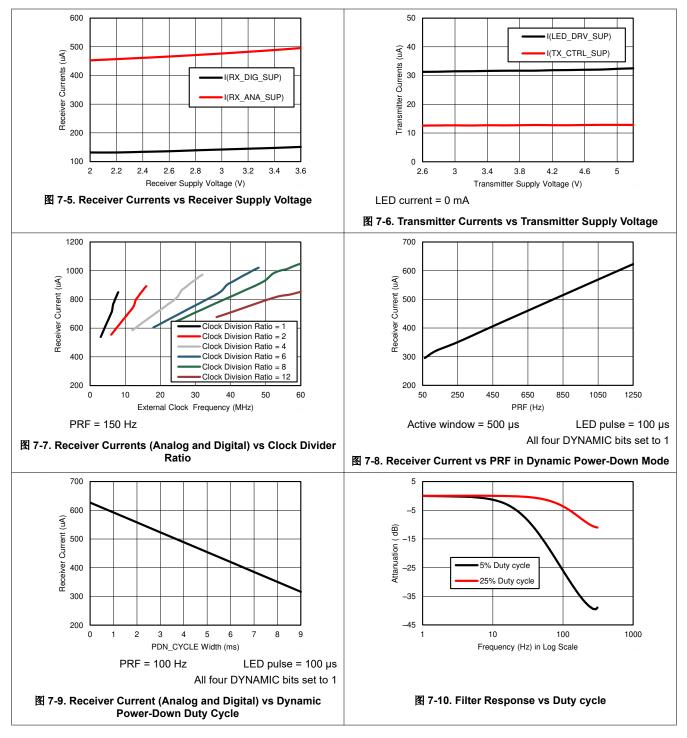

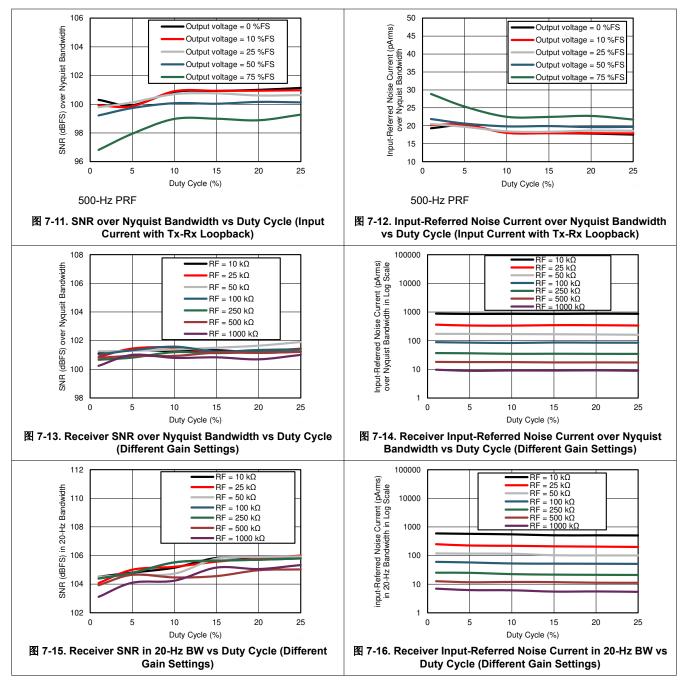

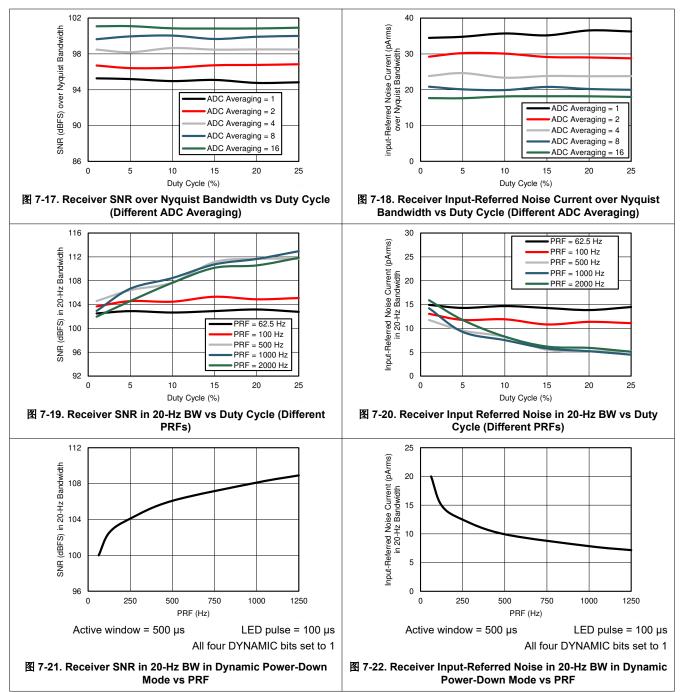

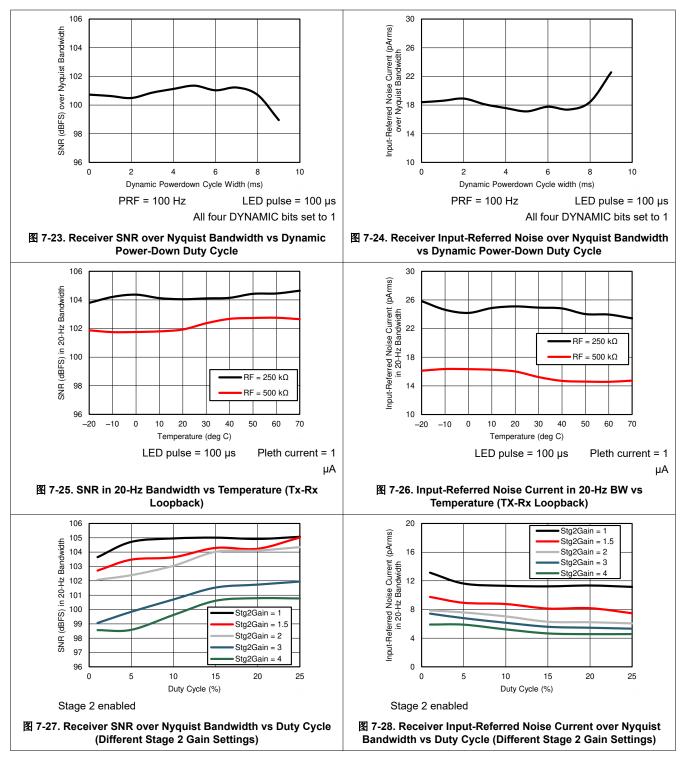

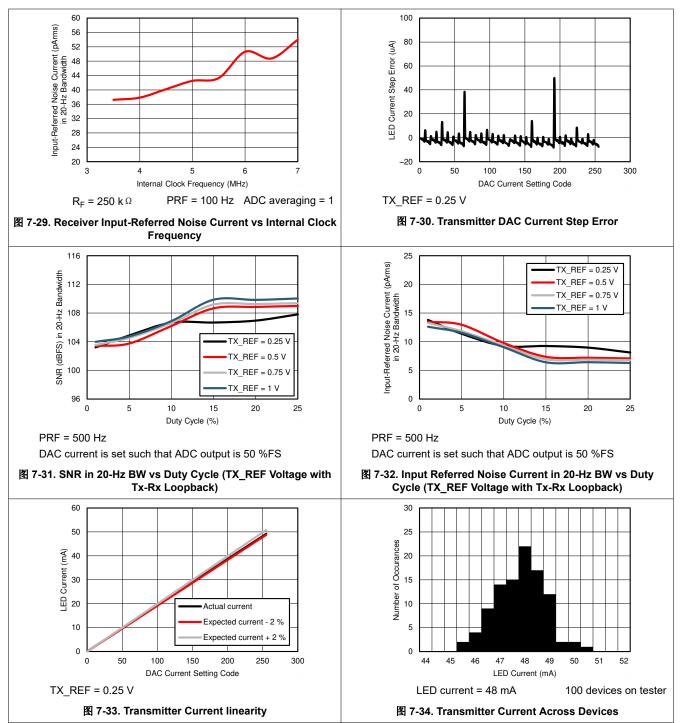

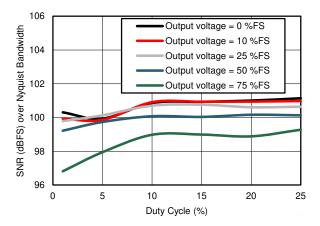

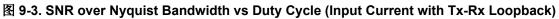

## 7.8 Typical Characteristics

## 8 Detailed Description

### 8.1 Overview

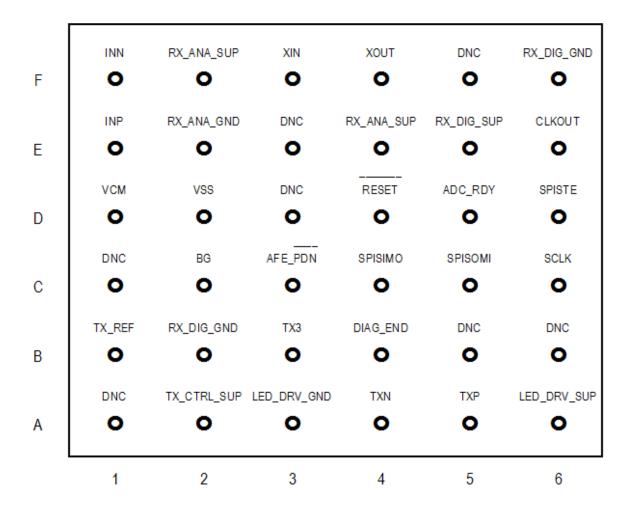

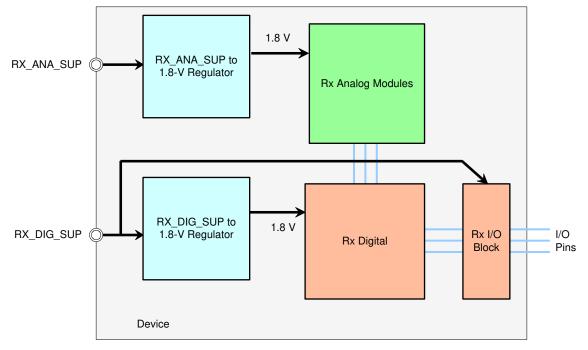

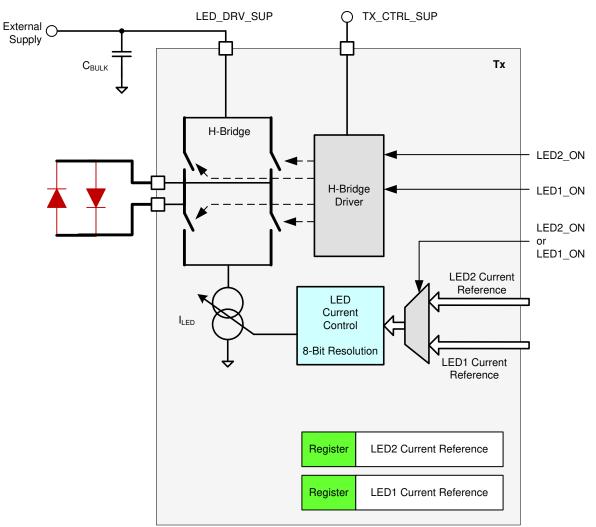

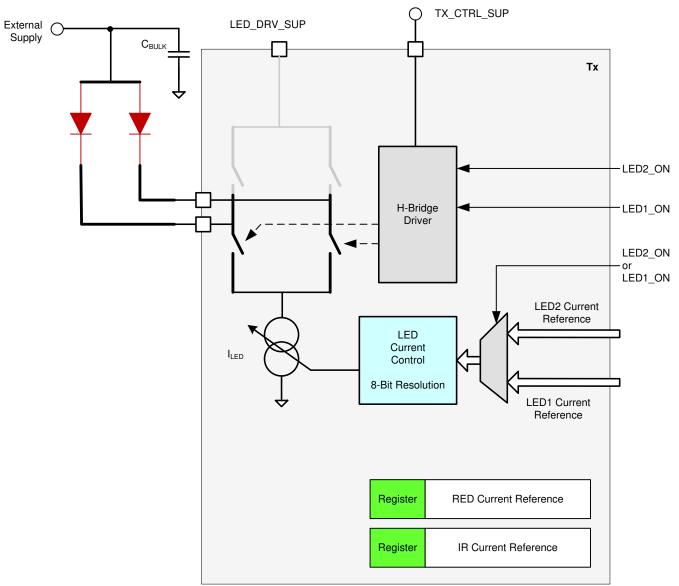

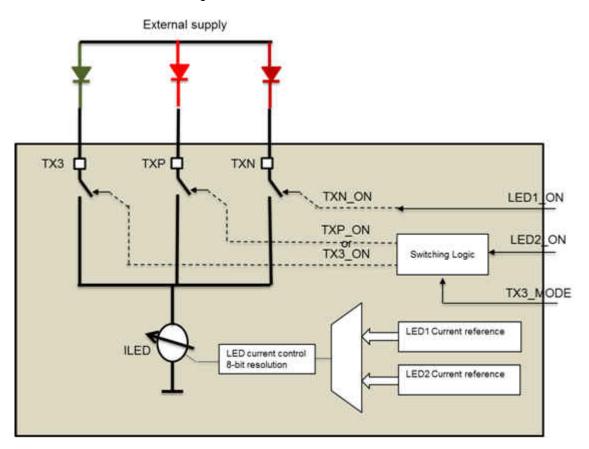

The AFE4403 is a complete analog front-end (AFE) solution targeted for pulse oximeter applications. The device consists of a low-noise receiver channel, an LED transmit section, and diagnostics for sensor and LED fault detection. To ease clocking requirements and provide the low-jitter clock to the AFE, an oscillator is also integrated that functions from an external crystal. The device communicates to an external microcontroller or host processor using an SPI interface. The *Functional Block Diagram* section provides a detailed block diagram for the AFE4403. The blocks are described in more detail in the following sections.

#### 8.2 Functional Block Diagram

### 8.3 Feature Description

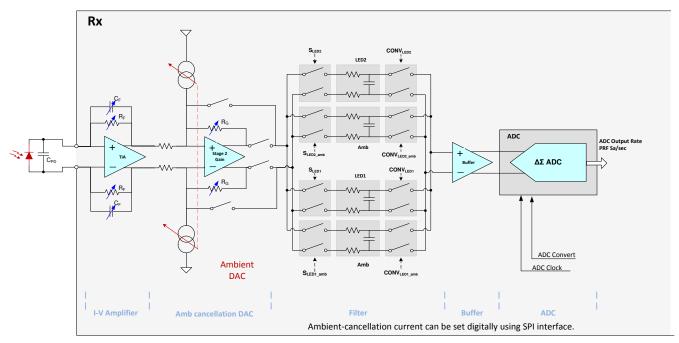

#### 8.3.1 Receiver Channel

This section describes the functionality of the receiver channel.

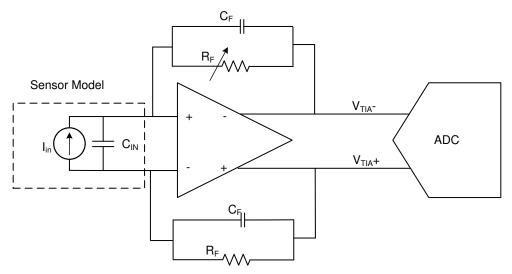

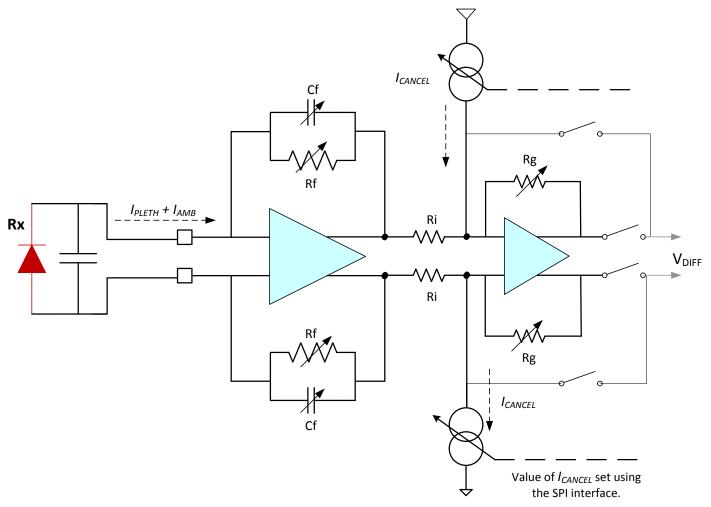

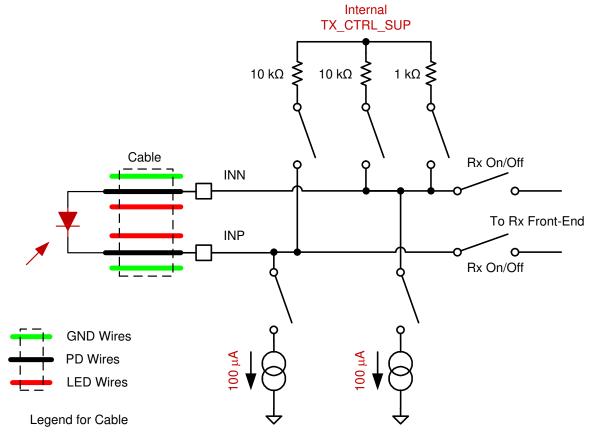

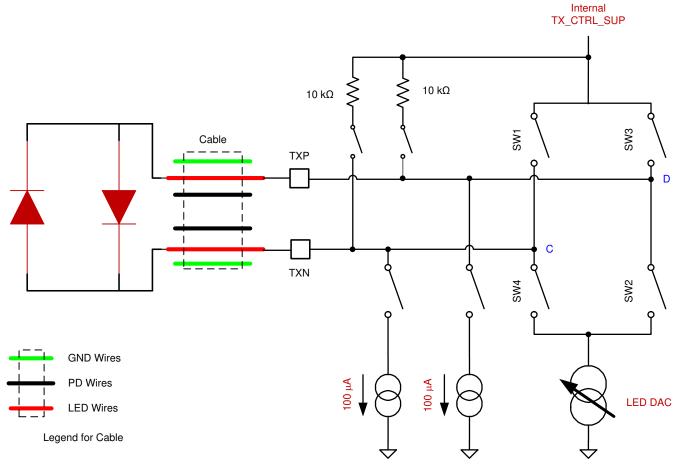

#### 8.3.1.1 Receiver Front-End

The receiver consists of a differential current-to-voltage (I-V) transimpedance amplifier (TIA) that converts the input photodiode current into an appropriate voltage, as shown in  $[\underline{\aleph}]$  8-1. The feedback resistor of the amplifier (R<sub>F</sub>) is programmable to support a wide range of photodiode currents. Available R<sub>F</sub> values include: 1 M  $\Omega$ , 500 k  $\Omega$ , 250 k  $\Omega$ , 100 k  $\Omega$ , 50 k  $\Omega$ , 25 k  $\Omega$ , and 10 k  $\Omega$ .

The device is ideally suited as a front-end for a PPG (photoplethysmography) application. In such an application, the light from the LED is reflected (or transmitted) from (or through) the various components inside the body (such as blood, tissue, and so forth) and are received by the photodiode. The signal received by the photodiode has three distinct components:

- 1. A pulsatile or ac component that arises as a result of the changes in blood volume through the arteries.

- 2. A constant dc signal that is reflected or transmitted from the time invariant components in the path of light. This constant dc component is referred to as the pleth signal.

- 3. Ambient light entering the photodiode.

The ac component is usually a small fraction of the pleth component, with the ratio referred to as the perfusion index (PI). Thus, the allowed signal chain gain is usually determined by the amplitude of the dc component.

#### 图 8-1. Receiver Front-End

The R<sub>F</sub> amplifier and the feedback capacitor (C<sub>F</sub>) form a low-pass filter for the input signal current. Always ensure that the low-pass filter RC time constant has sufficiently high bandwidth (as shown by <math><math><math><math><math>1) because the input current consists of pulses. For this reason, the feedback capacitor is also programmable. Available C<sub>F</sub> values include: 5 pF, 10 pF, 25 pF, 50 pF, 100 pF, and 250 pF. Any combination of these capacitors can also be used.

$$R_{F} \times C_{F} \leq \frac{Rx \text{ Sample Time}}{10}$$

(1)

AFE4403

ZHCSCL7C - MAY 2014 - REVISED APRIL 2021

The output voltage of the I-V amplifier includes the pleth component (the desired signal) and a component resulting from the ambient light leakage. The I-V amplifier is followed by the second stage, which consists of a current digital-to-analog converter (DAC) that sources the cancellation current and an amplifier that gains up the pleth component alone. The amplifier has five programmable gain settings: 0 dB, 3.5 dB, 6 dB, 9.5 dB, and 12 dB. The gained-up pleth signal is then low-pass filtered (500-Hz bandwidth) and buffered before driving a 22-bit ADC. The current DAC has a cancellation current range of 10  $\mu$ A with 10 steps (1  $\mu$ A each). The DAC value can be digitally specified with the SPI interface. Using ambient compensation with the ambient DAC allows the dc-biased signal to be centered to near mid-point of the amplifier (±0.9 V). Using the gain of the second stage allows for more of the available ADC dynamic range to be used.

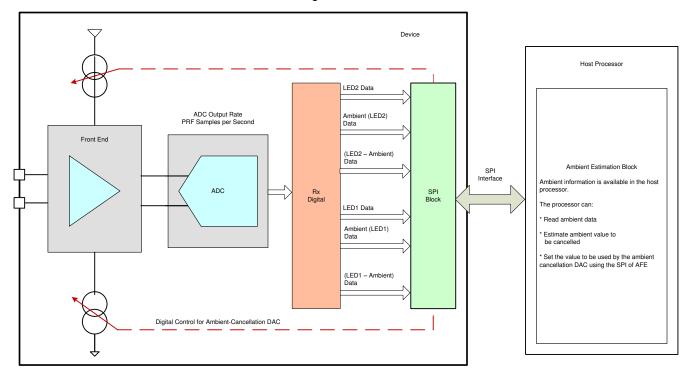

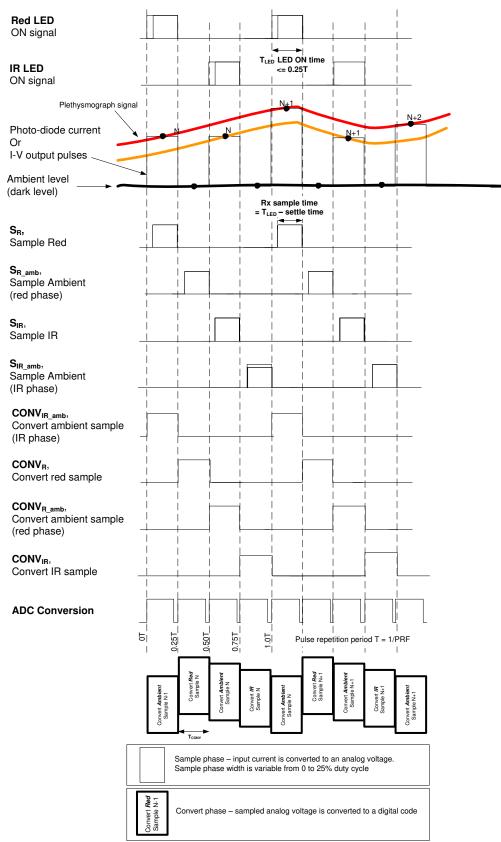

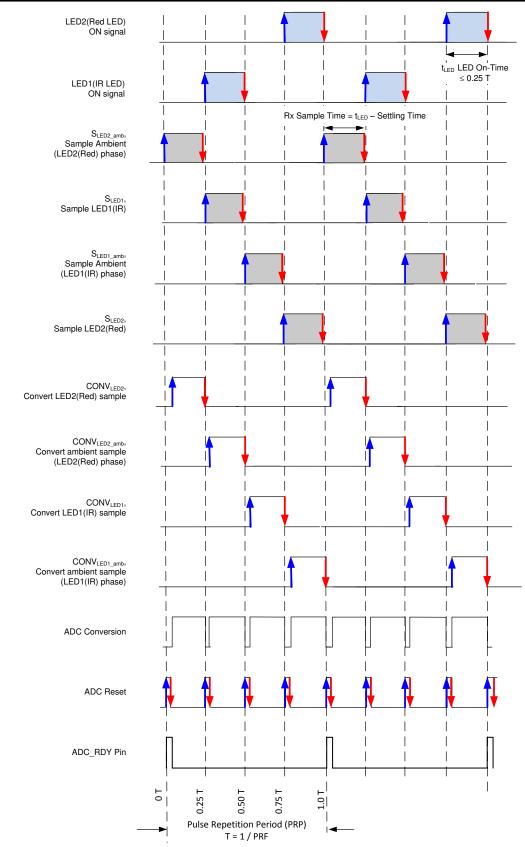

The output of the ambient cancellation amplifier is separated into LED2 and LED1 channels. When LED2 is on, the amplifier output is filtered and sampled on capacitor  $C_{LED2}$ . Similarly, the LED1 signal is sampled on the  $C_{LED1}$  capacitor when LED1 is on. In between the LED2 and LED1 pulses, the idle amplifier output is sampled to estimate the ambient signal on capacitors  $C_{LED2}$  amb and  $C_{LED1}$  amb.

The sampling duration is termed the *Rx* sample time and is programmable for each signal, independently. The sampling can start after the I-V amplifier output is stable (to account for LED and cable settling times). The Rx sample time is used for all dynamic range calculations; the minimum time recommended is 50  $\mu$ s. While the AFE4403 can support pulse widths lower than 50 us, having too low a pulse width could result in a degraded signal and noise from the photodiode.

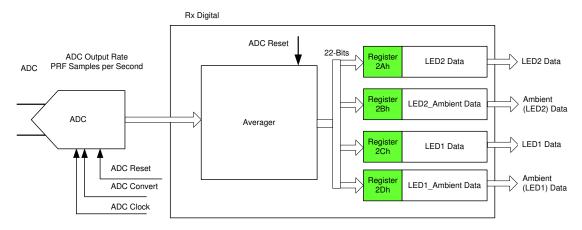

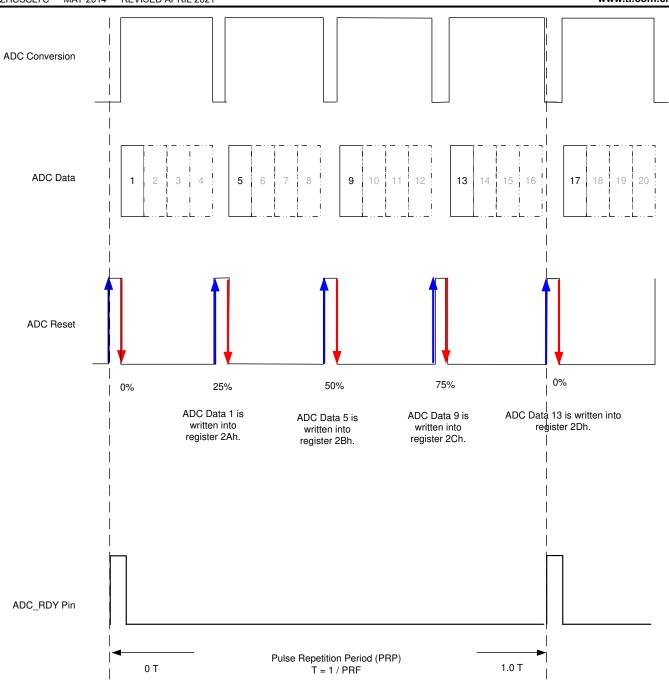

A single, 22-bit ADC converts the sampled LED2, LED1, and ambient signals sequentially. Each conversion provides a single digital code at the ADC output. As discussed in the *Receiver Timing* section, the conversions are meant to be staggered so that the LED2 conversion starts after the end of the LED2 sample phase, and so on.

Note that four data streams are available at the ADC output (LED2, LED1, ambient LED2, and ambient LED1) at the same rate as the pulse repetition frequency. The ADC is followed by a digital ambient subtraction block that additionally outputs the (LED2 – ambient LED2) and (LED1 – ambient LED1) data values.

The model of the photodiode and the connection to the TIA is shown in  $\boxed{8}$  8-2.

图 8-2. TIA Block Diagram

$I_{in}$  is the signal current generated by the photodiode in response to the incident light.  $C_{in}$  is the zero-bias capacitance of the photodiode. The current-to-voltage gain in the TIA is given by 522:

$$V_{TIA}$$

(diff) =  $V_{TIA}^+ - V_{TIA}^- = 2 \times I_{in} \times R_F$

(2)

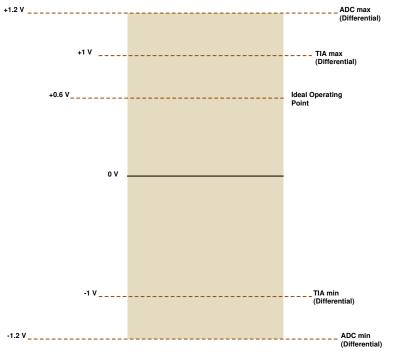

For example, for a photodiode current of  $I_{in} = 1 \ \mu A$  and a TIA gain setting of  $R_F = 100 \ k \Omega$ , the differential output of the TIA is equal to 200 mV. The TIA has an operating range of ±1 V, and the ADC has an input full-scale

range of  $\pm 1.2$  V (the extra margin is to prevent the ADC from saturating while operating the TIA at the fullest output range). Furthermore, because the PPG signal is one-sided, only one half of the full-scale is used. TI recommends operating the device at a dc level that is not more than 50% to 60% of the ADC full-scale. The margin allows for sudden changes in the signal level that might saturate the signal chain if operating too close to full-scale. Signal levels are shown in  $\mathbb{X}$  8-3:

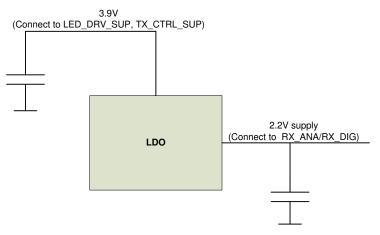

图 8-3. Signal Levels in TIA and ADC