LP8551 SNVS673E -APRIL 2010-REVISED SEPTEMBER 2014

# LP8551 High-Efficiency LED Backlight Driver for Notebooks

#### **Features**

- High-Voltage DC/DC Boost Converter with Integrated FET; Four Switching Frequency Options: 156/312/625/1250 kHz

- 2.7-V to 22-V Input Voltage Range to Support 1x to 5x Cell Li-Ion Batteries

- 50-mA High-Precision LED Current Sinks

- Adaptive LED Current Sink Headroom Control for Maximum System Efficiency

- Programmable PWM Resolution 8 to 13 Bits

- I<sup>2</sup>C and PWM Input Duty Cycle Brightness Control

- PWM Output Frequency and LED Current Set Through Resistors

- 4 LED Outputs with LED Fault (short/open) Detection

- Low Input Voltage, Overtemperature, Overcurrent Detection, and Shutdown

- Minimum Number of External Components

# Applications

- Notebook and Tablet LCD Display LED Backlight

- LED Lighting

# 3 Description

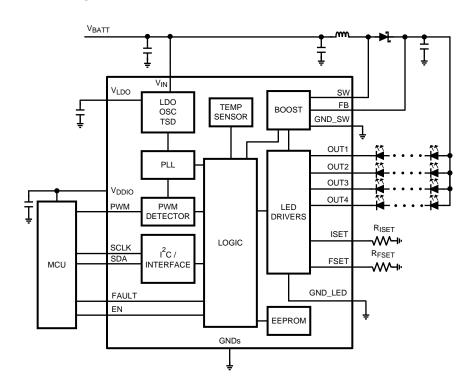

The LP8551 is a white LED driver with integrated boost converter. It has four adjustable current sinks which can be controlled by PWM input or with I<sup>2</sup>Ccompatible serial interface.

The boost converter has adaptive output voltage control based on the LED driver voltages. This feature minimizes the power consumption by adjusting the voltage to lowest sufficient level in all conditions.

LED outputs have 8-bit current resolution and up to 13-bit PWM resolution to achieve smooth and precise brightness control. Proprietary Phase Shift PWM control is used for LED outputs to reduce peak current from the boost converter, thus making the boost capacitors smaller. The Phase Shifting scheme also eliminates audible noise.

Internal EEPROM is used for storing the configuration data. This makes it possible to have minimum external component count and make the solution very small.

The LP8551 has safety features which make it possible to detect LED outputs with open or short fault. As well, low input voltage and boost overcurrent conditions are monitored, and chip is turned off in case of these events. Thermal de-rating function prevents overheating of the device by reducing backlight brightness when set temperature has been reached.

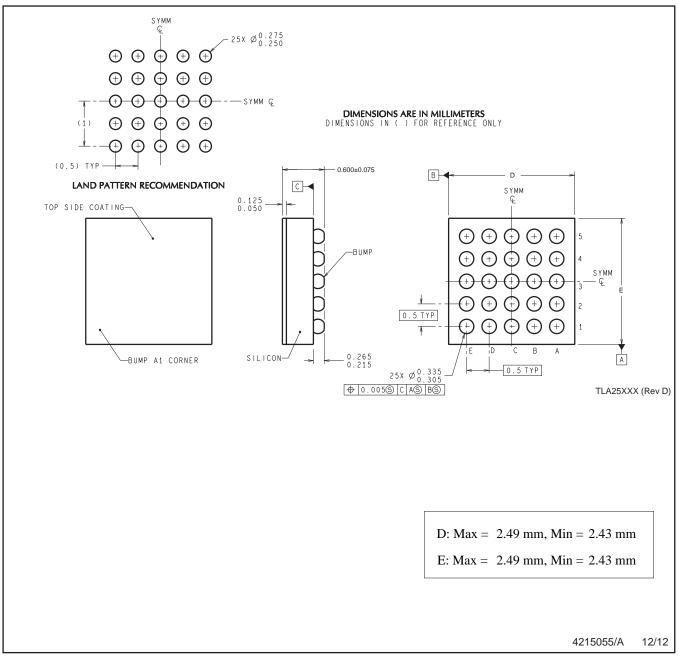

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (MAX)   |

|-------------|------------|-------------------|

| LP8551      | DSBGA (25) | 2.49 mm x 2.49 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

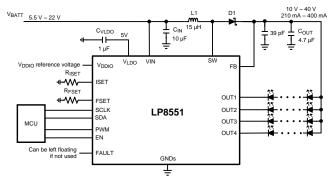

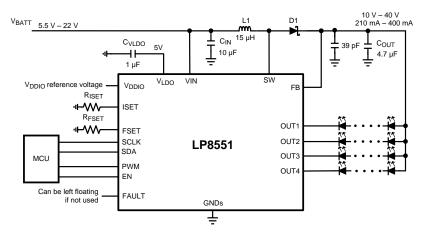

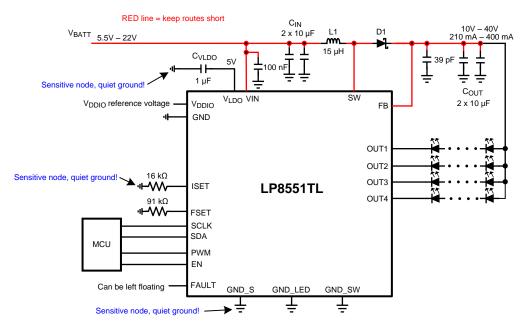

# Simplified Schematic

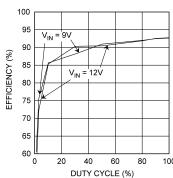

# **LED Drive Efficiency**

#### **Table of Contents**

| 1 | Features 1                                                       | 8  | Detailed Description                             | 11 |

|---|------------------------------------------------------------------|----|--------------------------------------------------|----|

| 2 | Applications 1                                                   |    | 8.1 Overview                                     | 11 |

| 3 | Description 1                                                    |    | 8.2 Functional Block Diagram                     | 11 |

| 4 | Revision History2                                                |    | 8.3 Feature Description                          | 12 |

| 5 | Device Default Values                                            |    | 8.4 Device Functional Modes                      | 20 |

| 6 | Pin Configuration and Functions 4                                |    | 8.5 Programming                                  | 21 |

| 7 | _                                                                |    | 8.6 Register Map                                 | 25 |

| ′ | Specifications                                                   | 9  | Application and Implementation                   | 34 |

|   | 7.1 Absolute Maximum Ratings                                     |    | 9.1 Application Information                      | 34 |

|   | 7.2 Handling Ratings                                             |    | 9.2 Typical Applications                         |    |

|   | 7.3 Recommended Operating Conditions                             | 10 | Power Supply Recommendations                     |    |

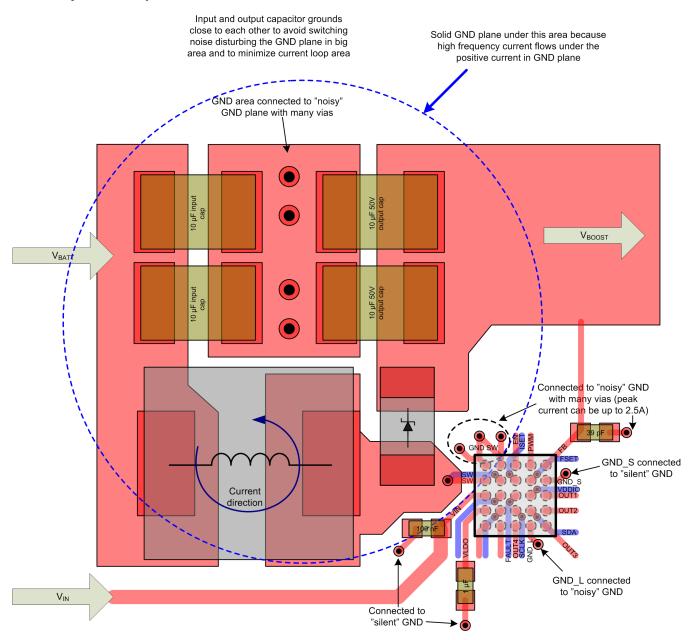

|   | 7.4 Thermal Information 6 7.5 Electrical Characteristics 6       | 11 | Layout                                           |    |

|   |                                                                  |    | 11.1 Layout Guidelines                           |    |

|   | 7.6 Boost Converter Electrical Characteristics                   |    | 11.2 Layout Example                              |    |

|   | 7.7 LED Driver Electrical Characteristics                        | 12 | Device and Documentation Support                 |    |

|   | 7.8 PWM Interface Characteristics                                | 12 | 12.1 Trademarks                                  |    |

|   | 7.9 Undervoltage Protection                                      |    | 12.2 Electrostatic Discharge Caution             |    |

|   | 7.10 Logic Interface Characteristics                             |    | 12.3 Glossary                                    |    |

|   | 7.11 I <sup>2</sup> C Serial Bus Timing Parameters (SDA, SCLK) 9 | 40 |                                                  | 4  |

|   | 7.12 Typical Characteristics                                     | 13 | Mechanical, Packaging, and Orderable Information | 41 |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Revision D (January 2014) to Revision E

**Page**

# Changes from Revision C (April 2013) to Revision D

Page

| Added EEPROM note |  | 24 |

|-------------------|--|----|

|-------------------|--|----|

# 5 Device Default Values

**Table 1. Default EEPROM Memory Values**

| ADDRESS | DEFAULT VALUES LP8551 |

|---------|-----------------------|

| A0H     | 0111 1111             |

| A1H     | 1011 0101             |

| A2H     | 1010 1110             |

| АЗН     | 0111 1011             |

| A4H     | 0010 0000             |

| A5H     | 0000 1001             |

| A6H     | 0000 0000             |

| А7Н     | 0000 0101             |

Copyright © 2010–2014, Texas Instruments Incorporated

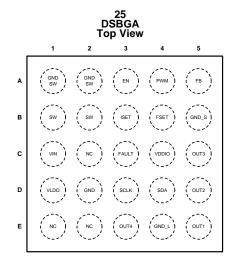

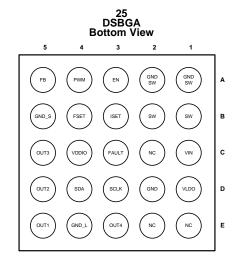

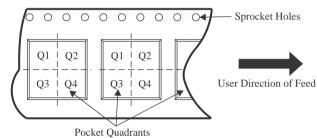

# 6 Pin Configuration and Functions

#### **Pin Functions**

| I      | PIN    | TYPE <sup>(1)</sup> | DECORPTION                                                                                                                                                               |

|--------|--------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUMBER | NAME   | IYPE                | DESCRIPTION                                                                                                                                                              |

| A1     | GND_SW | G                   | Boost switch ground                                                                                                                                                      |

| A2     | GND_SW | G                   | Boost switch ground                                                                                                                                                      |

| A3     | EN     | I                   | Enable input pin                                                                                                                                                         |

| A4     | PWM    | А                   | PWM dimming input. This pin must be connected to GND if not used.                                                                                                        |

| A5     | FB     | Α                   | Boost feedback input                                                                                                                                                     |

| B1     | SW     | Α                   | Boost switch                                                                                                                                                             |

| B2     | SW     | Α                   | Boost switch                                                                                                                                                             |

| В3     | ISET   | Α                   | Set resistor for LED current. This pin can be left floating if not used.                                                                                                 |

| B4     | FSET   | Α                   | PWM frequency set resistor. This pin can be left floating if not used.                                                                                                   |

| B5     | GND_S  | G                   | Signal ground                                                                                                                                                            |

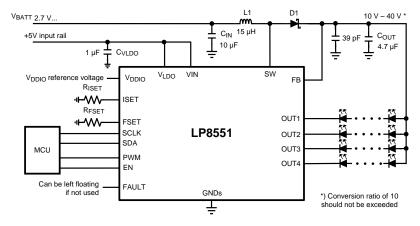

| C1     | VIN    | Р                   | Input power supply up to 22 V. If 2.7 V $\leq$ V <sub>BATT</sub> $<$ 5.5 V (Figure 25) then an external 5-V rail must be used for V <sub>LDO</sub> and V <sub>IN</sub> . |

| C2     | NC     | -                   | Not connected                                                                                                                                                            |

| C3     | FAULT  | OD                  | Fault indication output. If not used, can be left floating.                                                                                                              |

| C4     | VDDIO  | Р                   | Digital IO reference voltage (1.65 V to 5 V) for I <sup>2</sup> C interface. If brightness is controlled with PWM input pin then this pin can be connected to GND.       |

| C5     | OUT3   | А                   | Current sink output                                                                                                                                                      |

| D1     | VLDO   | Р                   | LDO output voltage. External 5-V rail can be connected to this pin in low voltage application.                                                                           |

| D2     | GND    | G                   | Ground                                                                                                                                                                   |

| D3     | SCLK   | I                   | Serial clock. This pin must be connected to GND if not used.                                                                                                             |

| D4     | SDA    | I/O                 | Serial data. This pin must be connected to GND if not used.                                                                                                              |

| D5     | OUT2   | Α                   | Current sink output                                                                                                                                                      |

| E1     | NC     | -                   | Not connected                                                                                                                                                            |

| E2     | NC     | -                   | Not connected                                                                                                                                                            |

| E3     | OUT4   | Α                   | Current sink output                                                                                                                                                      |

| E4     | GND_L  | G                   | LED ground                                                                                                                                                               |

| E5     | OUT1   | Α                   | Current sink output                                                                                                                                                      |

(1) A: Analog Pin, G: Ground Pin, P: Power Pin, I: Input Pin, I/O: Input/Output Pin, O: Output Pin, OD: Open Drain Pin

# 7 Specifications

## 7.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted) (1)

|                                                     | MIN             | MAX             | UNIT |

|-----------------------------------------------------|-----------------|-----------------|------|

| $V_{IN}$                                            | -0.3            | 24              |      |

| $V_{LDO}$                                           | -0.3            | 6               |      |

| Voltage on logic pins (PWM, EN, SCLK, SDA)          | -0.3            | -0.3 6          |      |

| Voltage on logic pin (FAULT)                        | -0.3 to VDDIO + |                 | V    |

| Voltage on analog pins (VDDIO, ISET, FSET)          | -0.3            | 6               |      |

| V (OUT1OUT4, SW, FB)                                | -0.3            | 44              |      |

| Continuous power dissipation (2)                    | Inte            | ernally limited |      |

| Junction temperature (T <sub>J-MAX</sub> )          |                 | 125             | °C   |

| Maximum lead temperature (soldering) <sup>(3)</sup> |                 |                 |      |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at T<sub>J</sub> = 150°C (typ.) and disengages at T<sub>J</sub> = 130°C (typ.).

## 7.2 Handling Ratings

|                                       |                             |                                                                               | MIN             | MAX  | UNIT |

|---------------------------------------|-----------------------------|-------------------------------------------------------------------------------|-----------------|------|------|

| T <sub>stg</sub>                      | Storage temperature rang    | e                                                                             | <del>-</del> 65 | 150  | °C   |

| \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | Electrostatic discharge     | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>   | -2000           | 2000 | V    |

| V <sub>(ESD)</sub>                    | SD) Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | -1000           | 1000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions (1)(2)

Over operating free-air temperature range (unless otherwise noted)

|                                                                | MIN  | NOM MAX | UNIT |  |

|----------------------------------------------------------------|------|---------|------|--|

| Input voltage (V <sub>IN</sub> ) (Figure 22)                   | 5.5  | 22      |      |  |

| Input voltage (V <sub>IN</sub> + V <sub>LDO</sub> )(Figure 25) | 4.5  | 5.5     | \/   |  |

| $V_{DDIO}$                                                     | 1.65 | 5       | V    |  |

| V(OUT1 to OUT4, SW, FB)                                        | 0    | 40      |      |  |

| Junction temperature (T <sub>J</sub> )                         | -30  | 125     | °C   |  |

| Ambient temperature (T <sub>A</sub> ) <sup>(3)</sup>           | -30  | 85      |      |  |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to the potential at the GND pins.

<sup>(3)</sup> For detailed soldering specifications and information, please refer to TI's AN-1112 (SNVA009): DSBGA Wafer Level Chip Scale Package.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = 125°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>), and the junction-to-ambient thermal resistance of the part/package in the application (R<sub>BJA</sub>), as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> - (R<sub>BJA</sub> × P<sub>D-MAX</sub>).

#### 7.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup>                                          | DSBGA (YZR) | UNIT |  |

|------------------------------------------------------------------------|-------------|------|--|

| I TERMAL METRIC                                                        | 25 PINS     | UNII |  |

| R <sub>0JA</sub> Junction-to-ambient thermal resistance <sup>(2)</sup> | 40 to 73    | °C/W |  |

- (1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

- Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

# 7.5 Electrical Characteristics (1)(2)

Limits are for  $T_A$  = 25°C and  $V_{IN}$  = 12 V,  $V_{DDIO}$  = 2.8 V,  $C_{VLDO}$  = 1  $\mu$ F, L1 = 15  $\mu$ H,  $C_{IN}$  = 10  $\mu$ F,  $C_{OUT}$  = 10  $\mu$ F, unless otherwise specified.  $R_{ISET}$  = 16  $k\Omega^{(3)}$

| SYMBOL           | PARAMETER                              | TEST CONDITIONS                                                                  | MIN                       | TYP | MAX                     | UNIT |

|------------------|----------------------------------------|----------------------------------------------------------------------------------|---------------------------|-----|-------------------------|------|

|                  | Standby supply current                 | Internal LDO disabled EN=L and PWM=L                                             |                           |     | 1 (4)                   | μΑ   |

| I <sub>IN</sub>  |                                        | LDO enabled, boost enabled, no current going through LED outputs 5-MHz PLL Clock |                           | 3   |                         |      |

|                  | Normal mode supply current             | 10-MHz PLL Clock                                                                 |                           | 3.7 |                         | mA   |

|                  |                                        | 20-MHz PLL Clock                                                                 |                           | 4.7 |                         |      |

|                  |                                        | 40-MHz PLL Clock                                                                 |                           | 6.7 |                         |      |

| f <sub>OSC</sub> | Internal oscillator frequency accuracy |                                                                                  | -4%<br>-7% <sup>(4)</sup> |     | 4%<br>7% <sup>(4)</sup> |      |

| $V_{LDO}$        | Internal LDO voltage                   |                                                                                  | 4.5 <sup>(4)</sup>        | 5   | 5.5 <sup>(4)</sup>      | V    |

| I <sub>LDO</sub> | Internal LDO external loading          |                                                                                  |                           |     | 5                       | mA   |

- (1) All voltages are with respect to the potential at the GND pins.

- (2) Minimum (Min) and Maximum (Max) limits are specified by design, test, or statistical analysis. Typical numbers are not specified, but do represent the most likely norm.

- (3) Low-ESR surface-mount ceramic capacitors (MLCCs) used in setting electrical characteristics.

- (4) Limits apply over the full operating ambient temperature range (–30°C ≤ T<sub>A</sub> ≤ 85°C).

#### 7.6 Boost Converter Electrical Characteristics

Limits are for  $T_A$  = 25°C and  $V_{IN}$  = 12 V,  $V_{DDIO}$  = 2.8 V,  $C_{VLDO}$  = 1  $\mu$ F, L1 = 15  $\mu$ H,  $C_{IN}$  = 10  $\mu$ F,  $C_{OUT}$  = 10  $\mu$ F, unless otherwise specified.  $R_{ISFT}$  = 16  $k\Omega^{(1)}$

| SYMBOL                            | PARAMETER                       | TEST CONDITIONS                                                          | MIN TYP                   | MAX | UNIT |

|-----------------------------------|---------------------------------|--------------------------------------------------------------------------|---------------------------|-----|------|

| RDS <sub>ON</sub>                 | Switch ON resistance            | I <sub>SW</sub> = 0.5 A                                                  | 0.12                      |     | Ω    |

| $V_{MAX}$                         | Boost maximum output voltage    |                                                                          | 40                        |     | V    |

|                                   |                                 | 9 V ≤ V <sub>BATT</sub> , V <sub>OUT</sub> = 35 V                        | 450                       |     |      |

| $I_{LOAD}$                        | Maximum continuous load current | 6 V ≤ V <sub>BATT</sub> , V <sub>OUT</sub> = 35 V                        | 300                       |     | mA   |

|                                   | Current                         | 3 V ≤ V <sub>BATT</sub> , V <sub>OUT</sub> = 25 V                        | 180                       |     |      |

| V <sub>OUT</sub> /V <sub>IN</sub> | Conversion ratio                | f <sub>SW</sub> = 1.25 MHz                                               |                           | 10  |      |

| f <sub>SW</sub>                   | Switching frequency             | BOOST_FREQ = 00<br>BOOST_FREQ = 01<br>BOOST_FREQ = 10<br>BOOST_FREQ = 11 | 156<br>312<br>625<br>1250 |     | kHz  |

| V <sub>OV</sub>                   | Overvoltage protection voltage  |                                                                          | V <sub>BOOST</sub> + 1.6V |     | V    |

| t <sub>PULSE</sub>                | Switch pulse minimum width      | no load                                                                  | 50                        |     | ns   |

| t <sub>STARTUP</sub>              | Start-up time                   | See (2)                                                                  | 6                         |     | ms   |

| I <sub>MAX</sub>                  | SW pin current limit            | IMAX_SEL = 0<br>IMAX_SEL = 1                                             | 1.4<br>2.5                |     | Α    |

- (1) Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) used in setting electrical characteristics.

- (2) Start-up time is measured from the moment boost is activated until the V<sub>OUT</sub> crosses 90% of its target value.

#### 7.7 LED Driver Electrical Characteristics

Limits are for  $T_A$  = 25°C and  $V_{IN}$  = 12 V,  $V_{DDIO}$  = 2.8 V,  $C_{VLDO}$  = 1  $\mu$ F, L1 = 15  $\mu$ H,  $C_{IN}$  = 10  $\mu$ F,  $C_{OUT}$  = 10  $\mu$ F, unless otherwise specified.  $R_{ISET}$  = 16  $k\Omega^{(1)}$

| SYMBOL               | PARAMETER                              | TEST CONDITIONS                                      | MIN                       | TYP   | MAX                     | UNIT  |

|----------------------|----------------------------------------|------------------------------------------------------|---------------------------|-------|-------------------------|-------|

| I <sub>LEAKAGE</sub> | Leakage current                        | Outputs OUT1OUT4, V <sub>OUT</sub> = 40 V            |                           | 0.1   | 1                       | μA    |

| I <sub>MAX</sub>     | Maximum source current                 | EN_I_RES = 0, CURRENT[7:0] = FFh                     |                           | 30    |                         | Л     |

|                      | OUT1OUT4                               | EN_I_RES = 1, CURRENT[7:0] = FFh                     |                           | 50    |                         | mA    |

| I <sub>OUT</sub>     | Output current accuracy <sup>(2)</sup> | Output current set to 23 mA, EN_I_RES = 1            | -3%<br>-4% <sup>(3)</sup> |       | 3%<br>4% <sup>(3)</sup> |       |

| I <sub>MATCH</sub>   | Matching <sup>(2)</sup>                | Output current set to 23 mA, EN_I_RES = 1            |                           | 0.5%  |                         |       |

|                      | PWM output resolution <sup>(4)</sup>   | f <sub>LED</sub> = 5 kHz, f <sub>PLL</sub> = 5 MHz   |                           | 10    |                         |       |

|                      |                                        | f <sub>LED</sub> = 10 kHz, f <sub>PLL</sub> = 5 MHz  |                           | 9     |                         | bits  |

| D)A/N/               |                                        | $f_{LED} = 20 \text{ kHz}, f_{PLL} = 5 \text{ MHz}$  |                           | 8     |                         |       |

| PWM <sub>RES</sub>   |                                        | $f_{LED} = 5 \text{ kHz}, f_{PLL} = 40 \text{ MHz}$  |                           | 13    |                         |       |

|                      |                                        | $f_{LED} = 10 \text{ kHz}, f_{PLL} = 40 \text{ MHz}$ |                           | 12    |                         |       |

|                      |                                        | f <sub>LED</sub> = 20 kHz, f <sub>PLL</sub> = 40 MHz |                           | 11    |                         |       |

|                      | LED avitabina (na sua sua (4)          | PWM_FREQ[4:0] = 00000b<br>PLL clock 5 MHz            |                           | 600   |                         | 11-   |

| f <sub>LED</sub>     | LED switching frequency <sup>(4)</sup> | PWM_FREQ[4:0] = 111111b<br>PLL clock 5 MHz           |                           | 19.2k |                         | Hz    |

| \/                   | Seturation voltage (5)                 | Output current set to 20 mA                          |                           | 105   | 220 <sup>(3)</sup>      | m)/   |

| $V_{SAT}$            | Saturation voltage <sup>(5)</sup>      | Output current set to 30 mA                          |                           | 160   | 290 <sup>(3)</sup>      | - m\/ |

- (1) Low-ESR surface-mount ceramic capacitors (MLCCs) used in setting electrical characteristics.

- Output Current Accuracy is the difference between the actual value of the output current and programmed value of this current. Matching is the maximum difference from the average. For the constant current sinks on the part (OUT1 to OUT4), the following are determined: the maximum output current (MAX), the minimum output current (MIN), and the average output current of all outputs (AVG). Two matching numbers are calculated: (MAX-AVG)/AVG and (AVG-MIN/AVG). The largest number of the two (worst case) is considered the matching figure. The typical specification provided is the most likely norm of the matching figure for all parts. Note that some manufacturers have different definitions in use.

- (3) Limits apply over the full operating ambient temperature range ( $-30^{\circ}\text{C} \le T_{A} \le 85^{\circ}\text{C}$ ).

- (4) PWM output resolution and frequency depend on the PLL settings. Please see section PWM Frequency Setting for full description.

- (5) Saturation voltage is defined as the voltage when the LED current has dropped 10% from the value measured at 1 V.

### 7.8 PWM Interface Characteristics

Limits are for  $T_A$  = 25°C and  $V_{IN}$  = 12 V,  $V_{DDIO}$  = 2.8 V,  $C_{VLDO}$  = 1  $\mu$ F, L1 = 15  $\mu$ H,  $C_{IN}$  = 10  $\mu$ F,  $C_{OUT}$  = 10  $\mu$ F, unless otherwise specified.  $R_{ISET}$  = 16  $k\Omega^{(1)}$

| SYMBOL               | PARAMETER                                 | TEST CONDITIONS                                                                                    | MIN | TYP                  | MAX | UNIT |

|----------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------|-----|----------------------|-----|------|

| $f_{\sf PWM}$        | PWM frequency range                       |                                                                                                    | 0.1 |                      | 25  | kHz  |

| t <sub>MIN_ON</sub>  | Minimum pulse ON time                     |                                                                                                    |     | 1                    |     |      |

| t <sub>MIN_OFF</sub> | Minimum pulse OFF time                    |                                                                                                    |     | 1                    |     | μs   |

| t <sub>STARTUP</sub> | Turnon delay from standby to backlight on | PWM input active, EN pin rise from low to high                                                     |     | 6                    |     | ms   |

| T <sub>STBY</sub>    | Turnoff Delay                             | PWM input low time for turn off, slope disabled                                                    |     | 50                   |     | ms   |

| PWM <sub>RES</sub>   | PWM Input Resolution                      | $f_{\rm IN}$ < 9 kHz<br>$f_{\rm IN}$ < 4.5 kHz<br>$f_{\rm IN}$ < 2.2 kHz<br>$f_{\rm IN}$ < 1.1 kHz |     | 10<br>11<br>12<br>13 |     | bits |

(1) Low-ESR surface-mount ceramic capacitors (MLCCs) used in setting electrical characteristics.

# 7.9 Undervoltage Protection

Limits are for  $T_A$  = 25°C and  $V_{IN}$  = 12 V,  $V_{DDIO}$  = 2.8 V,  $C_{VLDO}$  = 1  $\mu$ F, L1 = 15  $\mu$ H,  $C_{IN}$  = 10  $\mu$ F,  $C_{OUT}$  = 10  $\mu$ F, unless otherwise specified.  $R_{ISET}$  = 16  $k\Omega^{(1)}$

| SYMBOL            | PARAMETER | TEST CONDITIONS         | MIN  | TYP      | MAX  | UNIT |

|-------------------|-----------|-------------------------|------|----------|------|------|

| V <sub>UVLO</sub> |           | UVLO[1:0] = 00          |      | Disabled |      |      |

|                   |           | UVLO[1:0] = 01, falling | 2.55 | 2.70     | 2.94 |      |

|                   |           | UVLO[1:0] = 01, rising  | 2.62 | 2.76     | 3.00 |      |

|                   |           | UVLO[1:0] = 10, falling | 5.11 | 5.40     | 5.68 |      |

|                   |           | UVLO[1:0] = 10, rising  | 5.38 | 5.70     | 5.98 |      |

|                   |           | UVLO[1:0] = 11, falling | 7.75 | 8.10     | 8.45 |      |

|                   |           | UVLO[1:0] = 11, rising  | 8.36 | 8.73     | 9.20 |      |

<sup>(1)</sup> Low-ESR surface-mount ceramic capacitors (MLCCs) used in setting electrical characteristics.

# 7.10 Logic Interface Characteristics

Limits apply over the full operating ambient temperature range ( $-30^{\circ}\text{C} \le T_{A} \le 85^{\circ}\text{C}$ ), and  $V_{IN} = 12 \text{ V}$ ,  $V_{DDIO} = 2.8 \text{ V}$ ,  $C_{VLDO} = 1 \mu\text{F}$ ,  $L1 = 15 \mu\text{H}$ ,  $C_{IN} = 10 \mu\text{F}$ ,  $C_{OUT} = 10 \mu\text{F}$ , unless otherwise specified.  $C_{ISET} = 16 \text{ k}\Omega^{(1)}$

| SYMBOL          | PARAMETER              | TEST CONDITIONS                          | MIN                   | TYP N              | ΙAΧ  | UNIT |

|-----------------|------------------------|------------------------------------------|-----------------------|--------------------|------|------|

| LOGIC INP       | UT EN                  |                                          |                       |                    |      |      |

| V <sub>IL</sub> | Input low level        |                                          |                       |                    | 0.4  | V    |

| V <sub>IH</sub> | Input high level       |                                          | 1.2                   |                    |      | V    |

| I <sub>I</sub>  | Input current          |                                          | -1                    |                    | 1    | μA   |

| LOGIC INP       | UT PWM                 |                                          |                       |                    |      |      |

| V <sub>IL</sub> | Input low level        |                                          |                       |                    | 0.4  | V    |

| V <sub>IH</sub> | Input high level       |                                          | 2.2                   |                    |      | V    |

| l <sub>l</sub>  | Input current          |                                          | -1                    |                    | 1    | μΑ   |

| LOGIC INP       | UTS SCL, SDA           |                                          | ·                     |                    |      |      |

| V <sub>IL</sub> | Input low level        |                                          |                       | 0.2xV <sub>I</sub> | ODIO | V    |

| V <sub>IH</sub> | Input high level       |                                          | 0.8xV <sub>DDIO</sub> |                    |      | V    |

| I <sub>I</sub>  | Input current          |                                          |                       |                    |      | μΑ   |

| LOGIC OU        | TPUTS SDA, FAULT       |                                          | ·                     |                    |      |      |

| V <sub>OL</sub> | Output low level       | I <sub>OUT</sub> = 3 mA (pullup current) |                       | 0.3 <sup>(2)</sup> | 0.5  | V    |

| ار              | Output leakage current | V <sub>OUT</sub> = 2.8 V                 | -1                    |                    | 1    | μA   |

<sup>(1)</sup> Low-ESR surface-mount ceramic capacitors (MLCCs) used in setting electrical characteristics.

(2) Limits are  $T_A = 25$  °C.

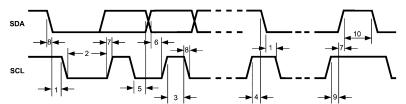

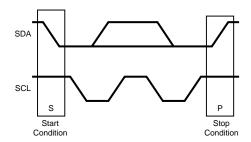

# 7.11 I<sup>2</sup>C Serial Bus Timing Parameters (SDA, SCLK)<sup>(1)</sup>

| SYMBOL         | PARAMETER                                                                     | MIN                  | MAX | UNIT |

|----------------|-------------------------------------------------------------------------------|----------------------|-----|------|

| $f_{\sf SCLK}$ | Clock frequency                                                               |                      | 400 | kHz  |

| 1              | Hold time (repeated) START condition                                          | 0.6                  |     | μs   |

| 2              | Clock low time                                                                | 1.3                  |     | μs   |

| 3              | Clock high time                                                               | 600                  |     | ns   |

| 4              | Setup time for a repeated START condition                                     | 600                  |     | ns   |

| 5              | Data hold time                                                                | 50                   |     | ns   |

| 6              | Data setup time                                                               | 100                  |     | ns   |

| 7              | Rise time of SDA and SCL                                                      | 20+0.1C <sub>b</sub> | 300 | ns   |

| 8              | Fall time of SDA and SCL                                                      | 15+0.1C <sub>b</sub> | 300 | ns   |

| 9              | Setup time for STOP condition                                                 | 600                  |     | ns   |

| 10             | Bus free time between a STOP and a START condition                            | 1.3                  |     | μs   |

| C <sub>b</sub> | Capacitive load parameter for each bus line Load of 1 pF corresponds to 1 ns. | 10                   | 200 | ns   |

(1) Specified by design.  $V_{DDIO}$  = 1.65 V to 5.5 V.

Figure 1. I<sup>2</sup>C Timing Parameters

# TEXAS INSTRUMENTS

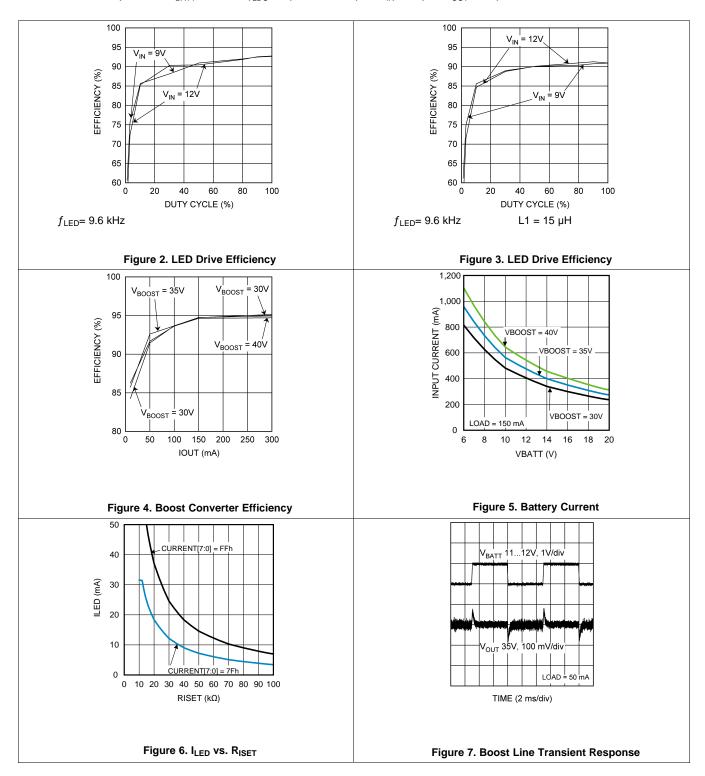

# 7.12 Typical Characteristics

Unless otherwise specified:  $V_{BATT}$ = 12 V,  $C_{VLDO}$ = 1  $\mu$ F, L1 = 33  $\mu$ H,  $C_{IN}$ = 10  $\mu$ F,  $C_{OUT}$ = 10  $\mu$ F.

# 8 Detailed Description

#### 8.1 Overview

The LP8551 is a high-voltage LED driver for medium sized LCD backlight applications. It includes high-voltage boost converter. Boost voltage automatically sets to the correct level needed to drive the LED strings. This is done by monitoring LED output voltage drop in real time.

Four constant current sinks with PWM control are used for driving LEDs. Constant current value is set with EEPROM bits and with  $R_{\rm ISET}$  resistor. Brightness (PWM) is controlled either with I<sup>2</sup>C register or with PWM input. PWM frequencies are set with EEPROM bits and with  $R_{\rm FSET}$  resistor. Special Phase-Shift PWM mode can be used to reduce boost output current peak, thus reducing output ripple, capacitor size, and audible noise.

Safety features include LED fault detection with open and short detection. LED fault detection prevents system overheating in case of open in some of the LED strings. Chip internal temperature is constantly monitored and, based on this, the LP8551 can reduce the brightness of the backlight to reduce thermal loading once certain trip point is reached. Threshold is programmable in EEPROM. If chip internal temperature reaches too high, the boost converter and LED outputs are completely turned off until the internal temperature has reached acceptable level. Boost converter is protected against too high load current and over-voltage. The LP8551 notifies the system about the fault through I<sup>2</sup>C register and with FAULT pin.

EEPROM programmable functions include:

- PWM frequencies

- · Phase shift PWM mode

- LED constant current

- Boost output frequency

- Temperature thresholds

- · Slope for brightness changes

- PWM output resolution

- · Boost control bits

External components R<sub>ISET</sub> and R<sub>FSET</sub> can also be used for selecting the output current and PWM frequencies.

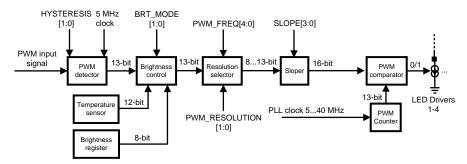

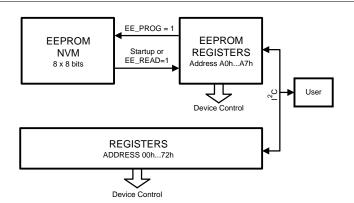

#### 8.2 Functional Block Diagram

## 8.3 Feature Description

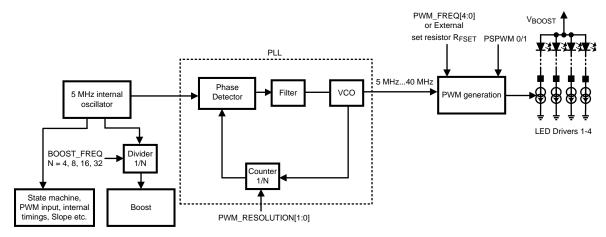

#### 8.3.1 Clock Generation

The LP8551 has internal 5-MHz oscillator which is used for clocking the boost converter, state machine, PWM outputs, PWM input duty cycle measurement, internal timings such as slope time for output brightness changes.

For PWM output generation the 5-MHz clock can be multiplied with the internal PLL to achieve higher resolution. The higher the clock frequency for PWM generation block, the higher the resolution but the tradeoff is higher  $I_Q$  of the part. Clock multiplication is set with <PWM RESOLUTION[1:0]> EEPROM Bits.

Figure 8. Principle of the Clock Generation

#### 8.3.2 Brightness Control Methods

The LP8551 controls the brightness of the backlight with PWM. PWM control is received either from PWM input pin or from I<sup>2</sup>C register bits. The PWM source selection is done with <BRT\_MODE[1:0]> bits as follows:

| BRT_MODE[1] | BRT_MODE[0] | PWM SOURCE                                 |

|-------------|-------------|--------------------------------------------|

| 0           | 0           | PWM input pin duty cycle control. Default. |

| 0           | 1           | PWM input pin duty cycle control.          |

| 1           | 0           | Brightness register                        |

| 1           | 1           | PWM direct control (PWM in = PWM out)      |

#### 8.3.2.1 PWM Input Duty Cycle

With PWM input pin duty cycle control the output PWM is controlled by PWM input duty cycle. PWM detector block measures the duty cycle in the PWM pin and uses this 13-bit value to generate the output PWM. Output PWM can have different frequency than input in this mode and also phase shift PWM mode can be used. Slope is effective in this mode. PWM input resolution is defined by the input PWM clock frequency.

#### 8.3.2.2 Brightness Register Control

With brightness register control the output PWM is controlled with 8-bit resolution <BRT7:0> register bits. Phase shift scheme can be used with this, and the output PWM frequency can be freely selected. Slope is effective in this mode.

#### 8.3.2.3 PWM Direct Control

With PWM direct control the output PWM directly follows the input PWM. Due to the internal logic structure the input is anyway clocked with the 5 MHz clock or the PLL clock. PSPWM mode is not possible in this mode. Slope is not effective in this mode.

#### 8.3.2.4 PWM Calculation Data Flow

Figure 9 shows the PWM calculation data flow. In PWM direct control mode most of the blocks are bypassed, and this flow chart does not apply.

Figure 9. PWM Calculation Data Flow

#### 8.3.2.5 PWM Detector

The PWM detector block measures the duty cycle of the input PWM signal. Resolution depends on the input signal frequency. Hysteresis selection sets the minimum allowable change to the input. If smaller change is detected, it is ignored. With hysteresis the constant changing between two brightness values is avoided if there is small jitter in the input signal.

#### 8.3.2.6 Brightness Control

Brightness control block gets 13-bit value from the PWM detector, 12-bit value from the temperature sensor, and also 8-bit value from the brightness register. <BRT\_MODE[1:0]> selects whether to use PWM input duty cycle value or the brightness register value as described earlier. Based on the temperature sensor value the duty cycle is reduced if the temperature has reached the temperature limit set to the <TEMP LIM[1:0]> EEPROM bits.

#### 8.3.2.7 Resolution Selector

Resolution selector takes the necessary MSB bits from the input data to match the output resolution. For example if 11-bit resolution is used for output, then 11 MSB bits are selected from the input.

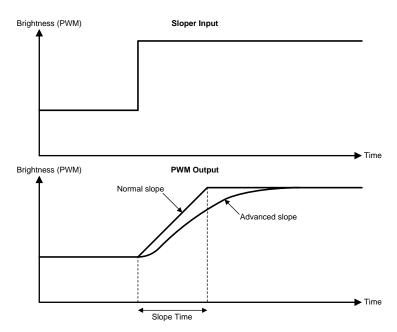

#### 8.3.2.8 Sloper

Sloper makes the smooth transition from one brightness value to another. Slope time can be adjusted from 0 to 500 ms with <SLOPE[3:0]> EEPROM bits. The sloper output is 16-bit value.

#### 8.3.2.9 PWM Comparator

The PWM counter clocks the PWM comparator based on the duty cycle value. Output of the PWM comparator controls directly the LED drivers. If PSPWM mode is used, then the signal to each LED output is delayed certain amount.

#### 8.3.2.10 Current Setting

Maximum current of the LED outputs is controlled with CURRENT[7:0] EEPROM register bits linearly from 0 to 30 mA. If  $\langle EN_I_RES \rangle = 1$  the maximum LED output current can be scaled also with external resistor,  $R_{ISET}$ .  $R_{ISET}$  controls the LED current as follows:

$$I_{LED} = \frac{600 * 1.23V}{R_{ISET}} * \frac{CURRENT [7:0]}{255}$$

(1)

Default value for CURRENT[7:0] = 7Fh (127d). Therefore, the output current can be calculated as follows:

$$R_{ISET} = \frac{600 * 1.23}{I_{LED}} * \frac{1}{2} = \frac{369}{I_{LED}}$$

(2)

For example, if a 16-k $\Omega$  R<sub>ISET</sub> resistor is used, then the LED maximum current is 23 mA.

#### **NOTE**

Formula is only approximation for the actual current.

### 8.3.2.11 PWM Frequency Setting

PWM frequency is selected with PWM\_FREQ[4:0] EEPROM register. If PLL clock frequency multiplication is used, it affects the output PWM frequency as well. <PWM\_RESOLUTION[1:0]> EEPROM bits select the PLL output frequency and hence the PWM frequency and resolution. PWM resolution setting affects the PLL clock frequency (5 MHz to 40 MHz). Highlighted frequencies with boldface can be selected also with external resistor  $R_{\text{FSET}}$ . To activate  $R_{\text{FSET}}$  frequency selection the <EN\_F\_RES> EEPROM bit must be 1.

| PWM_RES[1:0]  | 00    | 01     | 10     | 11     | DECOLUTION (DITC) |  |  |

|---------------|-------|--------|--------|--------|-------------------|--|--|

| PWM_FREQ[4:0] | 5 MHz | 10 MHz | 20 MHz | 40 MHz | RESOLUTION (BITS) |  |  |

| 11111         | 19232 | -      | -      | -      | 8                 |  |  |

| 11110         | 16828 | -      | -      | -      | 8                 |  |  |

| 11101         | 14424 | -      | -      | -      | 8                 |  |  |

| 11100         | 12020 | -      | -      | -      | 8                 |  |  |

| 11011         | 9616  | 19232  | -      | -      | 9                 |  |  |

| 11010         | 7963  | 15927  | -      | -      | 9                 |  |  |

| 11001         | 6386  | 12771  | -      | -      | 9                 |  |  |

| 11000         | 4808  | 9616   | 19232  | -      | 10                |  |  |

| 10111         | 4658  | 9316   | 18631  | -      | 10                |  |  |

| 10110         | 4508  | 9015   | 18030  | -      | 10                |  |  |

| 10101         | 4357  | 8715   | 17429  | -      | 10                |  |  |

| 10100         | 4207  | 8414   | 16828  | -      | 10                |  |  |

| 10011         | 4057  | 8114   | 16227  | -      | 10                |  |  |

| 10010         | 3907  | 7813   | 15626  | -      | 10                |  |  |

| 10001         | 3756  | 7513   | 15025  | -      | 10                |  |  |

| 10000         | 3606  | 7212   | 14424  | -      | 10                |  |  |

| 01111         | 3456  | 6912   | 13823  | -      | 10                |  |  |

| 01110         | 3306  | 6611   | 13222  | -      | 10                |  |  |

| 01101         | 3155  | 6311   | 12621  | -      | 10                |  |  |

| 01100         | 3005  | 6010   | 12020  | -      | 10                |  |  |

| 01011         | 2855  | 5710   | 11419  | -      | 10                |  |  |

| 01010         | 2705  | 5409   | 10818  | -      | 10                |  |  |

| 01001         | 2554  | 5109   | 10217  | -      | 10                |  |  |

| 01000         | 2404  | 4808   | 9616   | 19232  | 11                |  |  |

| 00111         | 2179  | 4357   | 8715   | 17429  | 11                |  |  |

| 00110         | 1953  | 3907   | 7813   | 15626  | 11                |  |  |

| 00101         | 1728  | 3456   | 6912   | 13823  | 11                |  |  |

| 00100         | 1503  | 3005   | 6010   | 12020  | 11                |  |  |

| 00011         | 1202  | 2404   | 4808   | 9616   | 12                |  |  |

| 00010         | 1052  | 2104   | 4207   | 8414   | 12                |  |  |

| 00001         | 826   | 1653   | 3306   | 6611   | 12                |  |  |

| 00000         | 601   | 1202   | 2404   | 4808   | 13                |  |  |

R<sub>FSET</sub> resistance values with corresponding PWM frequencies:

| PWM_RES[1:0] | 00             |            | 01              |            | 10              |            | 11              |            |

|--------------|----------------|------------|-----------------|------------|-----------------|------------|-----------------|------------|

| RFSET (kΩ)   | 5 MHz<br>CLOCK | RESOLUTION | 10 MHz<br>CLOCK | RESOLUTION | 20 MHz<br>CLOCK | RESOLUTION | 40 MHz<br>CLOCK | RESOLUTION |

| 1015         | 19232          | 8          | 19232           | 9          | 19232           | 10         | 19232           | 11         |

| 2629         | 16828          | 8          | 15927           | 9          | 16227           | 10         | 17429           | 11         |

| 3641         | 14424          | 8          | 12771           | 9          | 14424           | 10         | 15626           | 11         |

| 5060         | 12020          | 8          | 9616            | 10         | 12020           | 10         | 12020           | 11         |

| 85100        | 9616           | 9          | 8715            | 10         | 9616            | 11         | 9616            | 12         |

| 135150       | 7963           | 9          | 7813            | 10         | 7813            | 11         | 8414            | 12         |

| 200300       | 6386           | 9          | 6311            | 10         | 6010            | 11         | 6811            | 12         |

| 450          | 4808           | 10         | 4808            | 11         | 4808            | 12         | 4808            | 13         |

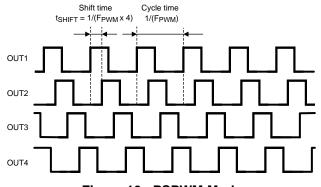

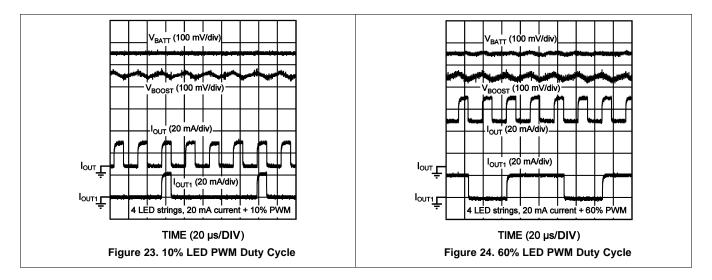

#### 8.3.2.12 Phase Shift PWM (PSPWM) Scheme

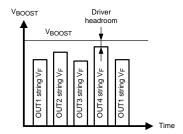

The PSPWM scheme allows delaying the time when each LED output is active. When the LED output are not activated simultaneously, the peak load current from the boost output is greatly decreased. This reduces the ripple seen on the boost output and allows smaller output capacitors. Reduced ripple also reduces the output ceramic capacitor audible ringing. PSPWM scheme also increases the load frequency seen on boost output by x4 and therefore transfers the possible audible noise to so high frequency that human ear cannot hear it.

Description of the PSPWM mode is seen on the following diagram. PSPWM mode is enabled by setting  $\langle EN_PSPWM \rangle$  EEPROM bit to 1. Shift time is the delay between outputs and it is defined as 1 / ( $f_{PWM} \times 4$ ). If the  $\langle EN_PSPWM \rangle$  bit is 0, then the delay is 0 and all outputs are active simultaneously.

Figure 10. PSPWM Mode

# 8.3.2.13 Slope

Slope time can be programmed with EEPROM bits <SLOPE[3:0]> from 0 to 500 ms. The same slope time is used for sloping up and down. Advanced slope makes brightness changes smooth for eye.

Figure 11. Sloper Operation

#### 8.3.2.14 Driver Headroom Control

Driver headroom can be controlled with <DRV\_HEADR[2:0]> EEPROM bits. Driver headroom control sets the minimum threshold for the voltage over the LED output which has the smallest driver headroom and controls the boost output voltage accordingly. Boost output voltage step size is 125 mV. The LED output which has the smallest forward voltage is the one which has highest  $V_F$  across the LEDs. The strings with highest forward voltage is detected automatically. To achieve best possible efficiency smallest possible headroom voltage should be selected. If there is high variation between LED strings, the headroom can be raised slightly to prevent any visual artifacts.

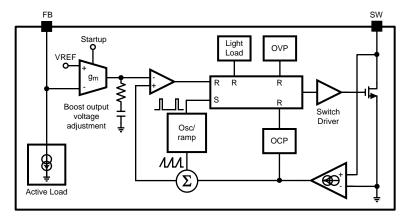

#### 8.3.3 Boost Converter

#### 8.3.3.1 Operation

The LP8551 boost DC/DC converter generates a 10-V to 40-V supply voltage for the LEDs from 2.7-V to 22-V input voltage. The output voltage can be controlled either with EEPROM register bits <VBOOST[4:0]> or automatic adaptive voltage control can be used. The converter is a magnetic switching PWM mode DC/DC converter with a current limit. The topology of the magnetic boost converter is called CPM (current programmed mode) control, where the inductor current is measured and controlled with the feedback. Switching frequency is selectable between 156 kHz and 1.25 MHz with EEPROM bit <BOOST\_FREQ[1:0]>. When <EN\_BOOST> EEPROM register bit is set to 1, then boost activates automatically when backlight is enabled.

In adaptive mode the boost output voltage is adjusted automatically based on LED driver headroom voltage. Boost output voltage control step size is, in this case, 125 mV, to ensure as small as possible driver headroom and high efficiency. Enabling the adaptive mode is done with <EN\_ADAPT> EEPROM bit. If boost is started with adaptive mode enabled, then the initial boost output voltage value is defined with the <VBOOST[4:0]> EEPROM register bits in order to eliminate long output voltage iteration time when boost is started for the first time. Figure 12 shows the boost topology with the protection circuitry:

Figure 12. Boost Topology with Protection Circuitry

#### 8.3.3.2 Protection

Three different protection schemes are implemented:

- 1. Overvoltage protection, limits the maximum output voltage.

- Overvoltage protection limit changes dynamically based on output voltage setting.

- Keeps the output below breakdown voltage.

- Prevents boost operation if battery voltage is much higher than desired output.

- 2. Overcurrent protection, limits the maximum inductor current.

- 3. Duty cycle limiting.

## 8.3.3.3 Manual Output Voltage Control

User can control the boost output voltage with <VBOOST[4:0]> EEPROM register bits when adaptive mode is disabled.

| VBOOST | [4:0] | VOLTAGE (TYPICAL) |

|--------|-------|-------------------|

| BIN    | DEC   | VOLTS             |

| 00000  | 0     | 10                |

| 00001  | 1     | 11                |

| 00010  | 2     | 12                |

| 00011  | 3     | 13                |

| 00100  | 4     | 14                |

|        |       |                   |

| 11101  | 29    | 39                |

| 11110  | 30    | 40                |

| 11111  | 31    | 40                |

#### 8.3.3.4 Adaptive Boost Control

Adaptive boost control function adjusts the boost output voltage to the minimum sufficient voltage for proper LED driver operation. The output with highest  $V_F$  LED string is detected and boost output voltage adjusted accordingly. Driver headroom can be adjusted with <DRIVER\_HEADR[2:0]> EEPROM bits from approximately 300 mV to 1200 mV. Boost adaptive control voltage step size is 125 mV. Boost adaptive control operates similarly with and without PSPWM.

Figure 13. Boost Adaptive Control Principle with PSPWM

#### 8.3.4 Fault Detection

The LP8551 has fault detection for LED fault, low-battery voltage, overcurrent, and thermal shutdown. The open drain output pin (FAULT) can be used to indicate occurred fault. The cause for the fault can be read from status register. Reading the fault register also resets the fault. Setting the EN pin low also resets the faults, even if an external 5-V line is used to power VLDO pin.

#### 8.3.4.1 LED Fault Detection

With LED fault detection, the voltages across the LED drivers are constantly monitored. LED fault detection is enabled with <EN\_LED\_FAULT> EEPROM bit. Shorted or open LED string is detected.

If LED fault is detected:

- The corresponding LED string is taken out of boost adaptive control loop;

- Fault bits are set in the fault register to identify whether the fault has been open/short and how many strings are faulty; and

- Fault open-drain pin is pulled down.

LED fault sensitivity can be adjusted with <LED\_FAULT\_THR> EEPROM bit which sets the allowable variation between LED output voltage to 3.3 V or 5.3 V. Depending on application and how much variation there can be in normal operation between LED string forward voltages this setting can be adjusted.

Fault is cleared by setting EN pin low or by reading the fault register.

#### 8.3.4.2 Undervoltage Detection

The LP8551 has detection for too-low VIN voltage. Threshold level for the voltage is set with EEPROM register bits as seen in Table 2:

Table 2.

| UVLO[1:0] | THRESHOLD (V) |

|-----------|---------------|

| 00        | OFF           |

| 01        | 2.7V          |

| 10        | 5.4V          |

| 11        | 8.1V          |

When undervoltage is detected, the LED outputs and boost shut down, the FAULT pin is pulled down, and corresponding fault bit is set in fault register. LEDs and boost starts again when the voltage has increased above the threshold level. Hysteresis is implemented to threshold level to avoid continuous triggering of fault when threshold is reached.

Fault is cleared by setting EN pin low or by reading the fault register.

#### 8.3.4.3 Overcurrent Protection

The LP8551 has detection for too-high loading on the boost converter. When overcurrent fault is detected, the LP8551 shuts down.

Fault is cleared by setting EN pin low or by reading the fault register.

#### 8.3.4.4 Device Thermal Regulation

The LP8551 has an internal temperature sensor which can be used to measure the junction temperature of the device and protect the device from overheating. During thermal regulation, LED PWM is reduced by 2% of full scale per °C whenever the temperature threshold is reached. Temperature regulation is enabled automatically when chip is enabled. 11-bit temperature value can be read from Temp MSB and Temp LSB registers, MSB should be read first. Temperature limit can be programmed in EEPROM as shown in the following table.

Thermal regulation function does not generate fault signal.

| TEMP_LIM[1:0] | OVER-TEMP LIMIT (°C) |

|---------------|----------------------|

| 00            | OFF                  |

| 01            | 110                  |

| 10            | 120                  |

| 11            | 130                  |

#### 8.3.4.5 Thermal Shutdown

If the LP8551 reaches thermal shutdown temperature (150°C), the LED outputs and boost shut down to protect it from damage. Also the FAULT pin is pulled down to indicate the fault state. The device activates again when temperature drops below 130°C degrees.

Fault is cleared by setting EN pin low or by reading the fault register.

Copyright © 2010-2014, Texas Instruments Incorporated

#### 8.4 Device Functional Modes

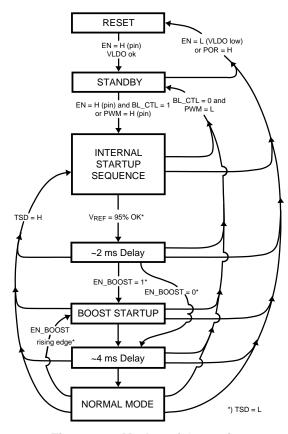

Figure 14. Modes of Operation

#### 8.4.1 Modes of Operation

RESET: In the RESET mode all the internal registers are reset to the default values. Reset is entered always when V<sub>LDO</sub> voltage is low. EN pin is enable for the internal LDO. Power On Reset (POR) activates during the chip startup or when the supply voltage V<sub>LDO</sub> fall below POR level. Once V<sub>LDO</sub> rises above POR level, POR inactivates, and the chip continues to the STANDBY mode.

**STANDBY:** The STANDBY mode is entered if the register bit BL\_CTL is LOW and external PWM input is not active and POR is not active. This is the low power consumption mode, when only internal 5-V LDO is enabled. Registers can be written in this mode and the control bits are effective immediately after start up.

**START-UP:** When BL\_CTL bit is written high or PWM signal is high, the INTERNAL START-UP SEQUENCE powers up all the needed internal blocks (V<sub>REF</sub>, Bias, Oscillator etc.). Internal EPROM and EEPROM are read in this mode. To ensure the correct oscillator initialization etc., a 2-ms delay is generated by the internal state-machine. If the chip temperature rises too high, the Thermal Shutdown (TSD) disables the chip operation and STARTUP mode is entered until no thermal shutdown event is present.

**BOOST START-UP:** Soft start for boost output is generated in the BOOST START-UP mode. The boost output is raised in low current PWM mode during the 4-ms delay generated by the state-machine. All LED outputs are off during the 4-ms delay to ensure smooth startup. The Boost start-up is entered from Internal Start-up Sequence if EN BOOST is HIGH.

**NORMAL:** During NORMAL mode the user controls the chip using the external PWM input or with Control Registers through I<sup>2</sup>C. The registers can be written in any sequence and any number of bits can be altered in a register in one write.

## 8.5 Programming

## 8.5.1 I<sup>2</sup>C-Compatible Serial Bus Interface

#### 8.5.1.1 Interface Bus Overview

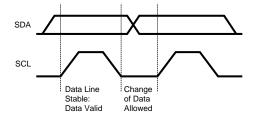

The I<sup>2</sup>C-compatible synchronous serial interface provides access to the programmable functions and registers on the device. This protocol uses a two-wire interface for bidirectional communications between the IC's connected to the bus. The two interface lines are the Serial Data Line (SDA) and the Serial Clock Line (SCLK). These lines should be connected to a positive supply, via a pull-up resistor and remain HIGH even when the bus is idle.

Every device on the bus is assigned a unique address and acts as either a Master or a Slave depending on whether it generates or receives the SCLK. The LP8551 is always a slave device.

#### 8.5.1.2 Data Transactions

One data bit is transferred during each clock pulse. Data is sampled during the high state of the serial clock SCLK. Consequently, throughout the clock's high period, the data should remain stable. Any changes on the SDA line during the high state of the SCLK and in the middle of a transaction, aborts the current transaction. New data should be sent during the low SCLK state. This protocol permits a single data line to transfer both command/control information and data using the synchronous serial clock.

Figure 15. Bit Transfer

Each data transaction is composed of a Start Condition, a number of byte transfers (set by the software) and a Stop Condition to terminate the transaction. Every byte written to the SDA bus must be 8 bits long and is transferred with the most significant bit first. After each byte, an Acknowledge signal must follow. The following sections provide further details of this process.

Figure 16. Start and Stop

The Master device on the bus always generates the Start and Stop Conditions (control codes). After a Start Condition is generated, the bus is considered busy and it retains this status until a certain time after a Stop Condition is generated. A high-to-low transition of the data line (SDA) while the clock (SCLK) is high indicates a Start Condition. A low-to-high transition of the SDA line while the SCLK is high indicates a Stop Condition.

## **Programming (continued)**

Figure 17. Start and Stop Conditions

In addition to the first Start Condition, a repeated Start Condition can be generated in the middle of a transaction. This allows another device to be accessed, or a register read cycle.

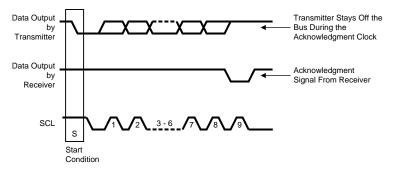

#### 8.5.1.3 Acknowledge Cycle

The Acknowledge Cycle consists of two signals: the acknowledge clock pulse the master sends with each byte transferred, and the acknowledge signal sent by the receiving device.

The master generates the acknowledge clock pulse on the ninth clock pulse of the byte transfer. The transmitter releases the SDA line (permits it to go high) to allow the receiver to send the acknowledge signal. The receiver must pull down the SDA line during the acknowledge clock pulse and ensure that SDA remains low during the high period of the clock pulse, thus signaling the correct reception of the last data byte and its readiness to receive the next byte.

#### 8.5.1.4 "Acknowledge After Every Byte" Rule

The master generates an acknowledge clock pulse after each byte transfer. The receiver sends an acknowledge signal after every byte received.

There is one exception to the "acknowledge after every byte" rule. When the master is the receiver, it must indicate to the transmitter an end of data by not-acknowledging ("negative acknowledge") the last byte clocked out of the slave. This "negative acknowledge" still includes the acknowledge clock pulse (generated by the master), but the SDA line is not pulled down.

#### 8.5.1.5 Addressing Transfer Formats

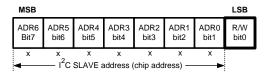

Each device on the bus has a unique slave address. The LP8551 operates as a slave device with 7-bit address combined with data direction bit. Slave address is 2Ch as 7-bit or 58h for write and 59h for read in 8-bit format.

Before any data is transmitted, the master transmits the address of the slave being addressed. The slave device should send an acknowledge signal on the SDA line, once it recognizes its address.

The slave address is the first seven bits after a Start Condition. The direction of the data transfer (R/W) depends on the bit sent after the slave address — the eighth bit.

When the slave address is sent, each device in the system compares this slave address with its own. If there is a match, the device considers itself addressed and sends an acknowledge signal. Depending upon the state of the R/W bit (1:read, 0:write), the device acts as a transmitter or a receiver.

Figure 18. I<sup>2</sup>C Chip Address

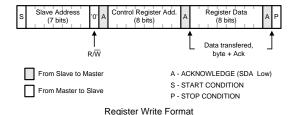

# 8.5.1.6 Control Register Write Cycle

Master device generates start condition.

# **Programming (continued)**

- Master device sends slave address (7 bits) and the data direction bit (r/w = 0).

- Slave device sends acknowledge signal if the slave address is correct.

- Master sends control register address (8 bits).

- · Slave sends acknowledge signal.

- Master sends data byte to be written to the addressed register.

- · Slave sends acknowledge signal.

- If master sends further data bytes the control register address is incremented by one after acknowledge signal.

- Write cycle ends when the master creates stop condition.

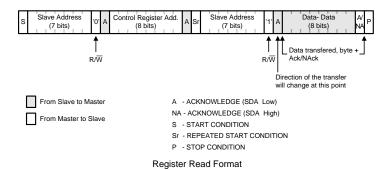

#### 8.5.1.7 Control Register Read Cycle

- · Master device generates a start condition.

- Master device sends slave address (7 bits) and the data direction bit (r/w = 0).

- Slave device sends acknowledge signal if the slave address is correct.

- Master sends control register address (8 bits).

- Slave sends acknowledge signal.

- Master device generates repeated start condition.

- Master sends the slave address (7 bits) and the data direction bit (r/w = 1).

- Slave sends acknowledge signal if the slave address is correct.

- · Slave sends data byte from addressed register.

- If the master device sends acknowledge signal, the control register address is incremented by one. Slave device sends data byte from addressed register.

- Read cycle ends when the master does not generate acknowledge signal after data byte and generates stop condition.

Table 3. Data Read and Write Cycles

|            | ADDRESS MODE                                                                                                                                                                                                                                                                                                                          |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Read  | <start condition=""> <slave address=""><r w="0">[Ack] <register addr.="">[Ack] <repeated condition="" start=""> <slave address=""><r w="1">[Ack] [Register Data]<ack nack="" or=""> additional reads from subsequent register address possible <stop condition=""></stop></ack></r></slave></repeated></register></r></slave></start> |

| Data Write | <start condition=""> <slave address=""><r w="0">[Ack] <register addr.="">[Ack] <register data="">[Ack] additional writes to subsequent register address possible <stop condition=""></stop></register></register></r></slave></start>                                                                                                 |

#### 8.5.1.8 Register Read and Write Detail

Figure 19. LP8551 Register Write Format

Figure 20. LP8551 Register Read Format

#### 8.5.2 **EEPROM**

EEPROM memory stores various parameters for chip control. The 64-bit EEPROM memory is organized as 8 x 8 bits. The EEPROM structure consists of a register front-end and the non-volatile memory (NVM). Register data can be read and written through the serial interface, and data is effective immediately. To read and program NVM, separate commands need to be sent. Erase and program voltages are generated on-chip charge pump, no other voltages than normal input voltage are required. A complete EEPROM memory map is shown in the *Device Default Values* section.

#### **NOTE**

EEPROM NVM can be programmed or read by customer for bench validation. Programming for production devices should be done in TI production test, where appropriate checks are performed to confirm EEPROM validity. Writing to EEPROM Control register of production devices is not recommended. If special EEPROM configuration is required, please contact the TI Sales Office for availability.

Figure 21. EEPROM Control Structure

# 8.6 Register Map

| ADDR | REGISTER           | D7       | D6         | D5         | D4        | D3       | D2       | D1                   | D0        | DEFAULT   |

|------|--------------------|----------|------------|------------|-----------|----------|----------|----------------------|-----------|-----------|

| 00H  | Brightness Control |          | BRT[7:0]   |            |           |          |          |                      | 0000 0000 |           |

| 01H  | Device Control     |          |            |            |           |          |          | BRT_MODE[1:0] BL_CTL |           |           |

| 02H  | Fault              | OPEN     | SHORT      | 2_CHANNELS | 1_CHANNEL | BL_FAULT | OCP      | TSD                  | UVLO      | 0000 0000 |

| 03H  | ID                 | PANEL    |            | MFG        | G[3:0]    |          | REV[2:0] |                      |           | 1111 1100 |

| 04H  | Direct Control     |          |            | OUT[4:1]   |           |          |          |                      | 0000 0000 |           |

| 05H  | Temp MSB           |          | TEMP[10:3] |            |           |          |          |                      | 0000 0000 |           |

| 06H  | Temp LSB           |          | TEMP[2:0]  |            |           |          |          |                      |           | 0000 0000 |

| 72H  | EEPROM_control     | EE_READY |            |            |           |          | EE_INIT  | EE_PROG              | EE_READ   | 0000 0000 |

# 8.6.1 Register Bit Explanations

# 8.6.1.1 Brightness Control

Address 00h

Reset value 0000 0000b

| BRIGHTNESS C | BRIGHTNESS CONTROL REGISTER                     |   |   |   |   |   |   |  |  |  |  |  |

|--------------|-------------------------------------------------|---|---|---|---|---|---|--|--|--|--|--|

| 7            | 6                                               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |  |

|              | BRT[7:0]                                        |   |   |   |   |   |   |  |  |  |  |  |

| Name         | Name Bit Access Description                     |   |   |   |   |   |   |  |  |  |  |  |

| BRT          | BRT 7:0 R/W Backlight PWM 8-bit linear control. |   |   |   |   |   |   |  |  |  |  |  |

#### 8.6.1.2 Device Control

Address 01h

Reset value 0000 0000b

| DEVICE CONTRO | OL REGISTER |        |                                                  |                                         |                                         |                                         |                                |  |  |

|---------------|-------------|--------|--------------------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|--------------------------------|--|--|

| 7             | 6           | 5      | 4 3 2 1 0                                        |                                         |                                         |                                         |                                |  |  |

|               |             |        | BRT_MODE[1:0] BL_CTL                             |                                         |                                         |                                         |                                |  |  |

| Name          | Bit         | Access | Description                                      |                                         |                                         |                                         |                                |  |  |

| BRT_MODE      | 2:1         | R/W    | PWM source m                                     | ode                                     |                                         |                                         |                                |  |  |

|               |             |        | 00b = PWM inp                                    | ut pin duty cycle                       | control (default)                       |                                         |                                |  |  |

|               |             |        | 01b = PWM inp                                    | ut pin duty cycle                       | control                                 |                                         |                                |  |  |

|               |             |        | 10b = Brightnes                                  | s register                              |                                         |                                         |                                |  |  |

|               |             |        | 11b = Direct PV                                  | VM control from F                       | PWM input pin                           |                                         |                                |  |  |

| BL_CTL        | 0           | R/W    | Enable backligh                                  | nt                                      |                                         |                                         |                                |  |  |

|               |             |        |                                                  |                                         |                                         | MODE[1:0] = 10. In PWM pin, and this    |                                |  |  |

|               |             |        | 1 = Backlight er<br>pin control the s<br>effect. | nabled and chip to state of the chip is | urned on if BRT_N<br>s defined with the | MODE[1:0] = 10. Ir<br>PWM pin, and this | n external PWM<br>s bit has no |  |  |

# 8.6.1.3 Fault

Address 02h

Reset value 0000 0000b

| 7          | 6     | 5          | 4                                                                                                                                                                                                                                                                                                | 3                                              | 2                                    | 1                                    | 0                       |  |  |  |  |

|------------|-------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------|--------------------------------------|-------------------------|--|--|--|--|

| OPEN       | SHORT | 2 CHANNELS | 1 CHANNEL                                                                                                                                                                                                                                                                                        | BL FAULT                                       | OCP                                  | TSD                                  | UVLO                    |  |  |  |  |

|            |       | _          | _                                                                                                                                                                                                                                                                                                | 52_17(621                                      | 001                                  | 105                                  | 0.120                   |  |  |  |  |

| Name       | Bit   | Access     | Description                                                                                                                                                                                                                                                                                      |                                                |                                      |                                      |                         |  |  |  |  |

| OPEN       | 7     | R          | LED open fault detect                                                                                                                                                                                                                                                                            | ion                                            |                                      |                                      |                         |  |  |  |  |