# 具有 RSSI 的 11.3 Gbps 限幅互阻抗放大器

查询样品: ONET8521T

# 特性

- 9 GHz 带宽

- · 2.4 kΩ 差分小信号互阻抗

- -20dBm 敏感度

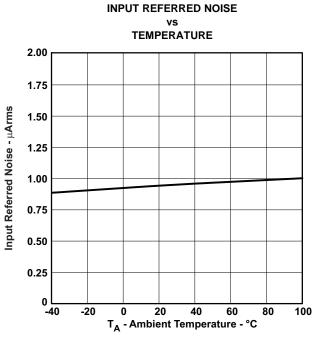

- 0.95 µA<sub>RMS</sub> 输入参考噪音

- 2.5 mA<sub>PP</sub> 输入过载电流

- 接收信号强度指示 (RSSI)

- 90 mW 典型功率耗散

- 支持片载 50 Ω 背向端接的 CML 数据输出

- 片载电源滤波器电容器

- 3.3 V 单电源

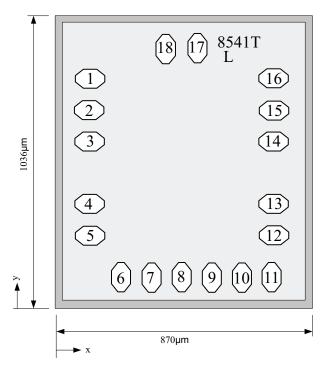

模具尺寸: 870 μm × 1036 μm

# 应用

- 10G 以太网

- 8G 和 10G 光纤通道

- 10G EPON

- SONET OC-192

- 6G CPRI和 OBSAI

- PIN 预放大器接收器

- · APD 预放大器接收器

# 说明

ONET8521T 是一款高速限幅互阻抗放大器,适用于数据传输速率高达 11.3 Gbps 的光电接收器。 它特有低输入 参考噪声、9 GHz 带宽、2.4 kΩ 小信号互阻抗以及接收信号强度指示 (RSSI)。

ONET8541T 采用模具成型方式,包括一个片载 V<sub>CC</sub> 旁路电容器并且非常适合封装在 TO 罐内。

ONET8521T 要求 3.3 V ±10% 单电源供电, 其高功效设计使其典型耗散少于90mW。 该器件可在 −40°C 至 100°C (IC 背面) 环境下平稳工作。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

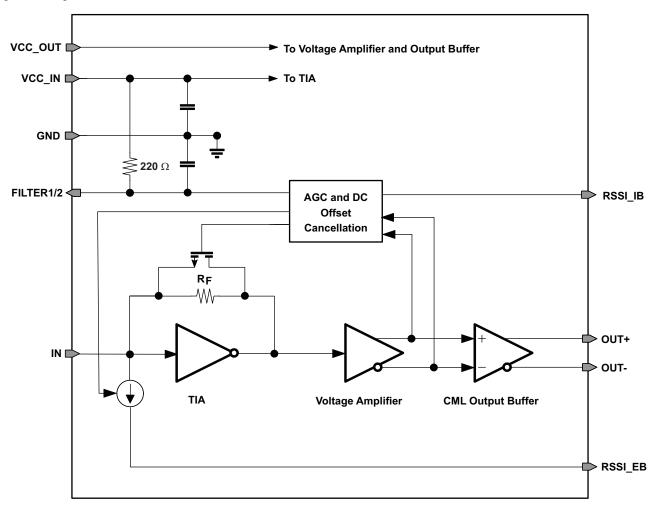

## **BLOCK DIAGRAM**

A simplified block diagram of the ONET8521T is shown in Figure 1.

The ONET8521T consists of the signal path, supply filters, a control block for dc input bias, automatic gain control (AGC) and received signal strength indication (RSSI). The RSSI provides the bias for the TIA stage and the control for the AGC.

The signal path consists of a transimpedance amplifier stage, a voltage amplifier, and a CML output buffer. The on-chip filter circuit provides a filtered  $V_{CC}$  for the PIN photodiode and for the transimpedance amplifier.

The dc input bias circuit and automatic gain control use internal low pass filters to cancel the dc current on the input and to adjust the transimpedance amplifier gain. Furthermore, circuitry is provided to monitor the received signal strength.

Figure 1. Simplified Block Diagram of the ONET8521T

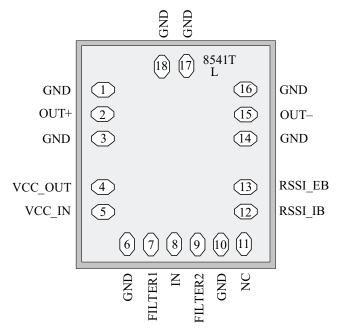

## **BOND PAD ASSIGNMENT**

The ONET8521T is available in die form. The locations of the bondpads are shown in Figure 2.

Figure 2. Bond Pad Assignment of ONET8521T

# **PIN FUNCTIONS**

| PIN     |                            | TVDE             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|---------|----------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME    | NO.                        | TYPE             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| GND     | 1, 3, 6, 10<br>14, 16 – 18 | Supply           | Circuit ground. All GND pads are connected on die. Bonding all pads is optional; however, for optimum performance a good ground connection is mandatory.                                                                                                                                                                                                                                                |  |  |  |  |

| OUT+    | 2                          | Analog<br>output | Non-inverted CML data output. On-chip $50\Omega$ back-terminated to $V_{CC}$ .                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| VCC_OUT | 4                          | Supply           | 2.97V–3.63V supply voltage for the voltage and CML amplifiers.                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| VCC_IN  | 5                          | Supply           | 2.97V–3.63V supply voltage for input TIA stage.                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| FILTER  | 7, 9                       | Analog           | Bias voltage for photodiode cathode. These pads are internally connected to an $220\Omega$ resistor to $V_{CC}$ and a filter capacitor to ground (GND).                                                                                                                                                                                                                                                 |  |  |  |  |

| IN      | 8                          | Analog input     | Data input to TIA (photodiode anode).                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| NC      | 11                         | No Connect       | Do not connect                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| RSSI_IB | 12                         | Analog<br>output | Analog output current proportional to the input data amplitude. Indicates the strength of the received signal (RSSI) if the photo diode is biased from the TIA. Connected to an external resistor to ground (GND). For proper operation, ensure that the voltage at the RSSI pad does not exceed $V_{CC} = 0.65V$ . If the RSSI feature is not used this pad should be left open.                       |  |  |  |  |

| RSSI_EB | 13                         | Analog<br>output | Optional use when operated with external PD bias (e.g. APD). Analog output current proportional to the input data amplitude. Indicates the strength of the received signal (RSSI). Connected to an external resistor to ground (GND). For proper operation, ensure that the voltage at the RSSI pad does not exceed $V_{\rm CC}$ – 0.65V. If the RSSI feature is not used this pad should be left open. |  |  |  |  |

| OUT-    | 15                         | Analog<br>output | Inverted CML data output. On-chip $50\Omega$ back-terminated to $V_{\text{CC}}$ .                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) (1)

|                                                                                                                                               |                                                                          | MIN  | MAX | UNIT     |

|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------|-----|----------|

| V <sub>CC_IN</sub> ,<br>V <sub>CC_OUT</sub>                                                                                                   | Supply voltage (2)                                                       | -0.3 | 4.0 | V        |

| V <sub>FILTER1</sub> ,<br>V <sub>FILTER2</sub> ,<br>V <sub>OUT+</sub> , V <sub>OUT-</sub> ,<br>V <sub>RSSI_IB</sub> ,<br>V <sub>RSSI_EB</sub> | Voltage at FILTER1, FILTER2, OUT+, OUT-, RSSI_IB, RSSI_EB <sup>(2)</sup> | -0.3 | 4.0 | V        |

| I <sub>IN</sub>                                                                                                                               | Current into IN                                                          | -0.7 | 3.5 | mA       |

| I <sub>FILTER</sub>                                                                                                                           | Current into FILTER1, FILTER2                                            | -8   | 8   | mA       |

| I <sub>OUT+</sub> , I <sub>OUT-</sub>                                                                                                         | Continuous current at outputs                                            | -8   | 8   | mA       |

| F0D                                                                                                                                           | ESD rating at all pins except input IN                                   | 2    |     | kV (HBM) |

| ESD                                                                                                                                           | ESD rating at input IN                                                   | 0.5  | ·   | kV(HBM)  |

| $T_{J,max}$                                                                                                                                   | Maximum junction temperature                                             |      | 125 | °C       |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## RECOMMENDED OPERATING CONDITIONS

|                                          | PARAMETER                                | CONDITIONS | MIN  | NOM | MAX                | UNIT |

|------------------------------------------|------------------------------------------|------------|------|-----|--------------------|------|

| $V_{CC}$                                 | Supply voltage                           |            | 2.97 | 3.3 | 3.63               | V    |

| $T_A$                                    | Operating backside die temperature       |            | -40  |     | 100 <sup>(1)</sup> | °C   |

| L <sub>FILTER</sub> ,<br>L <sub>IN</sub> | Wire-bond inductor at pins FILTER and IN |            |      | 0.3 | 0.5                | nΗ   |

| C <sub>PD</sub>                          | Photodiode capacitance                   |            |      | 0.2 |                    | pF   |

<sup>(1) 105°</sup>C maximum junction temperature

# DC ELECTRICAL CHARACTERISTICS

over recommended operating conditions (unless otherwise noted). Typical values are at  $V_{CC} = 3.3 \text{ V}$  and  $T_A = 25^{\circ}\text{C}$

|                     | PARAMETER                    | TEST CONDITIONS                                       | MIN  | TYP  | MAX               | UNIT |

|---------------------|------------------------------|-------------------------------------------------------|------|------|-------------------|------|

| $V_{CC}$            | Supply voltage               |                                                       | 2.97 | 3.3  | 3.63              | V    |

| I <sub>VCC</sub>    | Cupply ourrent               | Input current i <sub>IN</sub> < 1000 μA <sub>PP</sub> |      | 27   | 40 <sup>(1)</sup> | A    |

|                     | Supply current               | Input current i <sub>IN</sub> < 2500 μA <sub>PP</sub> |      |      | 45 <sup>(1)</sup> | mA   |

| V <sub>IN</sub>     | Input bias voltage           |                                                       | 0.75 | 0.85 | 0.98              | V    |

| R <sub>OUT</sub>    | Output resistance            | Single-ended to V <sub>CC</sub>                       | 40   | 50   | 60                | Ω    |

| R <sub>FILTER</sub> | Photodiode filter resistance |                                                       |      | 220  |                   | Ω    |

(1) Including RSSI current

<sup>(2)</sup> All voltage values are with respect to network ground terminal.

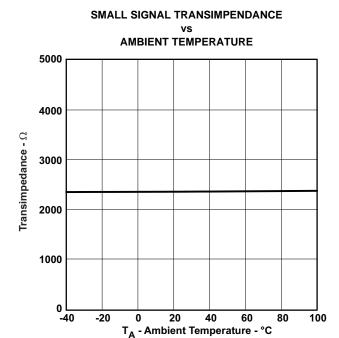

### **AC ELECTRICAL CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted). Typical values are at  $V_{CC} = +3.3$  V and  $T_A = 25$ °C

|                      | PARAMETER                                               | TEST CONDITIONS                                                                              | MIN  | TYP  | MAX  | UNIT             |

|----------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------|------|------|------|------------------|

| Z <sub>21</sub>      | Small signal transimpedance                             | Differential output; Input current $i_{IN} = 20 \mu A_{PP}$                                  | 1500 | 2400 |      | Ω                |

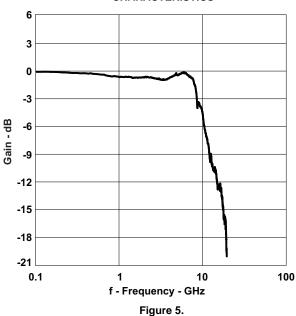

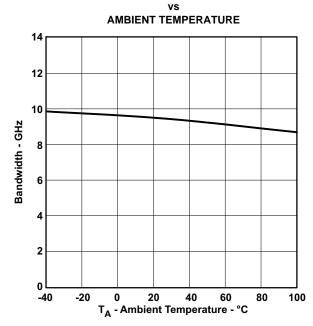

| f <sub>HSS,3dB</sub> | Small signal bandwidth                                  | $i_{IN} = 16 \mu A_{PP}$ (1)                                                                 | 7    | 9    |      | GHz              |

| f <sub>L,3dB</sub>   | Low frequency –3 dB bandwidth                           | 16 μA < i <sub>IN</sub> < 2000 μA <sub>PP</sub>                                              |      | 30   | 100  | kHz              |

| i <sub>N,IN</sub>    | Input referred RMS noise                                | 10 GHz bandwidth (2)                                                                         |      | 0.95 | 1.4  | μΑ               |

| S <sub>US</sub>      | Unstressed sensitivity                                  | 10.3125 Gbps, PRBS31 pattern, 1310 nm, BER 10 <sup>-12</sup>                                 |      | -20  |      | dBm              |

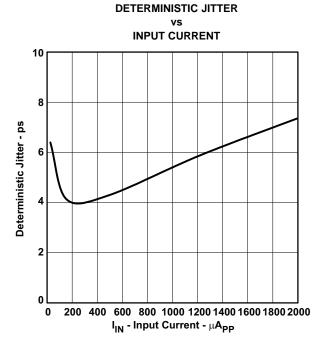

| D.I.                 | Deterministic litter                                    | 25 μA <sub>PP</sub> < i <sub>IN</sub> < 500 μA <sub>PP</sub> (10.3125 Gbps, K28.5 pattern)   |      | 6    | 12   |                  |

| DJ                   | Deterministic jitter                                    | 500 μA <sub>PP</sub> < i <sub>IN</sub> < 2000 μA <sub>PP</sub> (10.3125 Gbps, K28.5 pattern) |      | 6    | 14   | ps <sub>PP</sub> |

| DJ <sub>OL</sub>     | Overload deterministic jitter                           | 2000 μ $A_{PP}$ < $i_{IN}$ < 2500 μ $A_{PP}$ (10.3125 Gbps, K28.5 pattern)                   |      | 7    | 16   | ps <sub>PP</sub> |

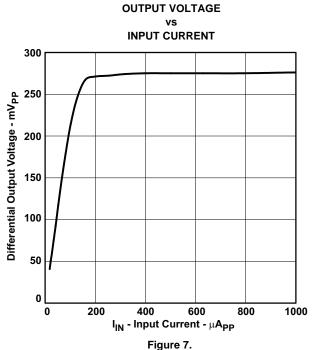

| $V_{OUT,D,MAX}$      | Maximum differential output voltage                     | Input current i <sub>IN</sub> = 500 μA <sub>PP</sub>                                         | 180  | 300  | 420  | $mV_{PP}$        |

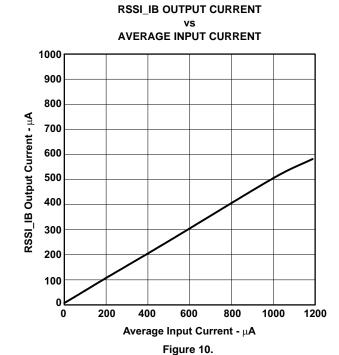

| A <sub>RSSI_IB</sub> | RSSI gain internal bias                                 | Resistive load to GND <sup>(3)</sup>                                                         | 0.48 | 0.5  | 0.52 | A/A              |

|                      | RSSI internal bias output offset current (no light) (4) |                                                                                              | 2    | 7    | 16   | μA               |

| A <sub>RSSI_EB</sub> | RSSI gain external bias                                 | Resistive load to GND <sup>(3)</sup>                                                         | 0.43 |      | 0.6  | A/A              |

|                      | RSSI external bias output offset current (no light)     |                                                                                              |      | 25   |      | μΑ               |

| PSNR                 | Power supply noise rejection                            | F < 10 MHz <sup>(5)</sup> , Supply filtering according to SFF8431                            |      | -15  |      | dB               |

<sup>(1)</sup> The small signal bandwidth is specified over process corners, temperature, and supply voltage variation. The assumed photodiode capacitance is 0.2 pF and the bond-wire inductance is 0.3 nH. The small signal bandwidth strongly depends on environmental parasitics. Careful attention to layout parasitics and external components is necessary to achieve optimal performance.

(2) Input referred RMS noise is (RMS output noise)/ (gain at 100 MHz).

<sup>(3)</sup> The RSSI output is a current output, which requires a resistive load to ground (GND). The voltage gain can be adjusted for the intended application by choosing the external resistor; however, for proper operation, ensure that the voltage at RSSI does not exceed V<sub>CC</sub> – 0.65V.

<sup>(4)</sup> Offset is added to improve accuracy below 5μA. When measured without input current (no light) the offset can be subtracted as a constant offset from RSSI measurements.

<sup>(5)</sup> PSNR is the differential output amplitude divided by the voltage ripple on supply; no input current at IN.

#### DETAILED DESCRIPTION

## **SIGNAL PATH**

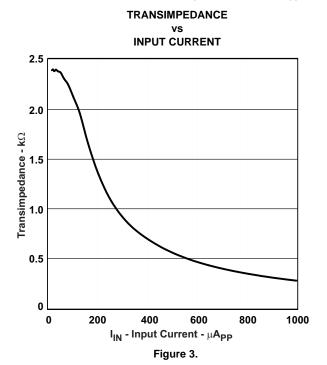

The first stage of the signal path is a transimpedance amplifier which converts the photodiode current into a voltage. If the input signal current exceeds a certain value, the transimpedance gain is reduced by means of a nonlinear AGC circuit to limit the signal amplitude.

The second stage is a limiting voltage amplifier that provides additional limiting gain and converts the single ended input voltage into a differential data signal. The output stage provides CML outputs with an on-chip  $50\Omega$  back-termination to  $V_{CC}$ .

### **FILTER CIRCUITRY**

The FILTER pins provide a filtered  $V_{CC}$  for a PIN photodiode bias. The on-chip low pass filter for the photodiode is implemented using a filter resistor of  $220\Omega$  and a capacitor. The corresponding corner frequency is below 5MHz. The supply voltages for the transimpedance amplifier are filtered by means of on-chip capacitors, thus avoiding the necessity to use an external supply filter capacitor. The input stage has a separate  $V_{CC}$  supply (VCC\_IN) which is not connected on chip to the supply of the limiting and CML stages (VCC\_OUT).

#### **AGC AND RSSI**

The voltage drop across the internal photodiode supply-filter resistor is monitored by the bias and RSSI control circuit block in the case where a PIN diode is biased using the FILTER pins.

If the dc input current exceeds a certain level then it is partially cancelled by means of a controlled current source. This keeps the transimpedance amplifier stage within sufficient operating limits for optimum performance.

The automatic gain control circuitry adjusts the voltage gain of the AGC amplifier to ensure limiting behavior of the complete amplifier.

Finally this circuit block senses the current through the filter resistor and generates a mirrored current that is proportional to the input signal strength. The mirrored current is available at the RSSI\_IB output and can be sunk to ground (GND) using an external resistor. For proper operation, ensure that the voltage at the RSSI\_IB pad does not exceed  $V_{\rm CC} = 0.65V$ .

If an APD or PIN photodiode is used with an external bias then the RSSI\_EB pin should be used. However, for greater accuracy under external photo diode biasing conditions, it is recommended to derive the RSSI from the external bias circuitry.

## TYPICAL OPERATION CHARACTERISTICS

Typical operating condition is at  $V_{CC} = 3.3 \text{ V}$  and  $T_A = 25^{\circ}\text{C}$  (unless otherwise noted)

SMALL SIGNAL BANDWIDTH

Figure 4.

Figure 6.

# **TYPICAL OPERATION CHARACTERISTICS (continued)**

Typical operating condition is at  $V_{CC} = 3.3 \text{ V}$  and  $T_A = 25^{\circ}\text{C}$  (unless otherwise noted)

Figure 8.

Figure 9.

8

# **TYPICAL OPERATION CHARACTERISTICS (continued)**

Typical operating condition is at  $V_{CC} = 3.3 \text{ V}$  and  $T_A = 25^{\circ}\text{C}$  (unless otherwise noted)

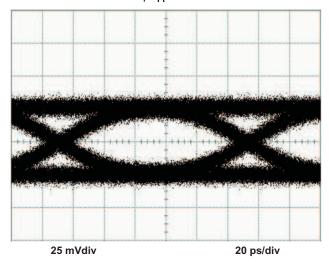

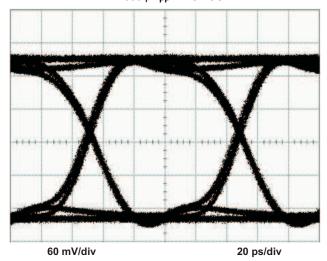

# OUTPUT EYE-DIAGRAM AT 10.3 GBPS AND 20 $\mu A_{PP}$ INPUT CURRENT

Figure 11.

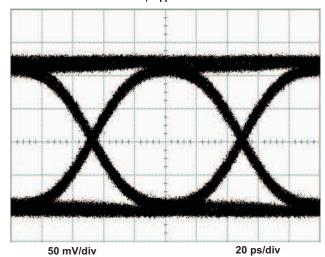

# OUTPUT EYE-DIAGRAM AT 10.3 GBPS AND 100 $\mu$ A<sub>PP</sub> INPUT CURRENT

Figure 12.

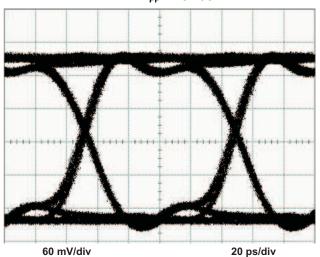

# OUTPUT EYE-DIAGRAM AT 10.3 GBPS AND 500 $\mu A_{PP}$ INPUT CURRENT

Figure 13.

# OUTPUT EYE-DIAGRAM AT 10.3 GBPS AND 2 mA<sub>PP</sub> INPUT CURRENT

Figure 14.

ZHCS364A - JULY 2011 - REVISED AUGUST 2011

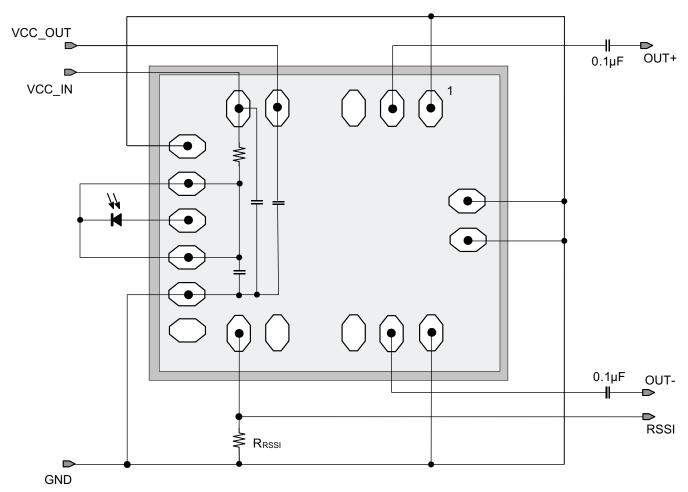

#### **APPLICATION INFORMATION**

Figure 15 shows the ONET8521T used in a typical fiber optic receiver using the internal photodiode bias. The ONET8521T converts the electrical current generated by the PIN photodiode into a differential output voltage. The FILTER inputs provide a dc bias voltage for the PIN that is low pass filtered by the combination of an internal  $220\Omega$  resistor and a capacitor. Because the voltage drop across the  $220\Omega$  resistor is sensed and used by the bias circuit, the photodiode must be connected to the FILTER pads for the bias to function correctly.

The RSSI output is used to mirror the photodiode output current and can be connected via a resistor to GND. The voltage gain can be adjusted for the intended application by choosing the external resistor; however, for proper operation of the ONET8521T, ensure that the voltage at RSSI never exceeds  $V_{CC}$  – 0.65V. If the RSSI output is not used while operating with internal PD bias, it should be left open.

The OUT+ and OUT- pins are internally terminated by  $50\Omega$  pull-up resisters to VCC. The outputs must be ac coupled, for example by using  $0.1\mu\text{F}$  capacitors, to the succeeding device.

Figure 15. Basic Application Circuit for PIN Receivers

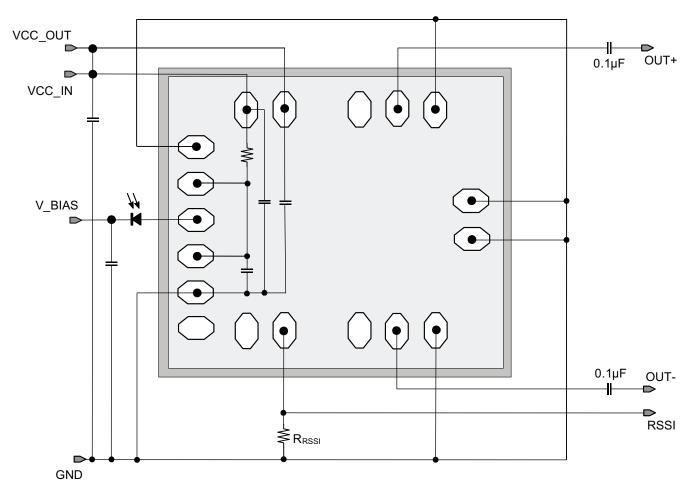

Figure 16 shows the ONET8521T being used in a typical fiber optic receiver using an external photodiode bias for an APD photodiode. This configuration can also be used for a PIN diode if desired. The external bias RSSI signal is based on a dc offset value and is not as accurate as the internal bias RSSI signal which is based upon the photodiode current.

Figure 16. Basic Application Circuit for APD Receivers

## **ASSEMBLY RECOMMENDATIONS**

Careful attention to assembly parasitics and external components is necessary to achieve optimal performance.

Recommendations that optimize performance include:

- 1. Minimize the total capacitance on the IN pad by using a low capacitance photodiode and paying attention to stray capacitances. Place the photodiode close to the ONET8521T die in order to minimize the bond wire length and thus the parasitic inductance.

- 2. Use identical termination and symmetrical transmission lines at the ac coupled differential output pins OUT+ and OUT-.

- 3. Use short bond wire connections for the supply terminals VCC\_IN, VCC\_OUT, and GND. Supply voltage filtering is provided on chip but filtering may be improved by using an additional external capacitor.

# **CHIP DIMENSIONS AND PAD LOCATIONS**

Die Thickness: 203  $\pm$  13  $\mu m$

Pad Dimensions: 105  $\mu$ m  $\times$  65  $\mu$ m Die Size: 870  $\pm$  40  $\mu$ m  $\times$  1036  $\pm$  40  $\mu$ m

| PAD | COORDINATES (referenced to pad 1) |               | SYMBOL  | TYPE          | DESCRIPTION                                        |

|-----|-----------------------------------|---------------|---------|---------------|----------------------------------------------------|

|     | <b>x (μm)</b>                     | <b>y (µm)</b> |         |               |                                                    |

| 1   | 0                                 | 0             | GND     | Supply        | Circuit ground                                     |

| 2   | 0                                 | -115          | OUT+    | Analog output | Non-inverted data output                           |

| 3   | 0                                 | -230          | GND     | Supply        | Circuit ground                                     |

| 4   | 0                                 | -460          | VCC_OUT | Supply        | 3.3V supply voltage                                |

| 5   | 0                                 | -575          | VCC_IN  | Supply        | 3.3V supply voltage                                |

| 6   | 115.5                             | -728          | GND     | Supply        | Circuit ground                                     |

| 7   | 225.5                             | -728          | FILTER1 | Analog        | Bias voltage for photodiode                        |

| 8   | 335.5                             | -728          | IN      | Analog input  | Data input to TIA                                  |

| 9   | 445.5                             | -728          | FILTER2 | Analog        | Bias voltage for photodiode                        |

| 10  | 555.5                             | -728          | GND     | Supply        | Circuit ground                                     |

| 11  | 665.5                             | -728          | NC      | No connect    | Do not connect                                     |

| 12  | 671                               | -575          | RSSI_IB | Analog output | RSSI output signal for internally biased receivers |

| 13  | 671                               | -460          | RSSI_EB | Analog output | RSSI output signal for externally biased receivers |

| 14  | 671                               | -230          | GND     | Supply        | Circuit ground                                     |

| 15  | 671                               | -115          | OUT-    | Analog output | Inverted data output                               |

| 16  | 671                               | 0             | GND     | Supply        | Circuit ground                                     |

| 17  | 393                               | 109           | GND     | Supply        | Circuit ground                                     |

| 18  | 278                               | 109           | GND     | Supply        | Circuit ground                                     |

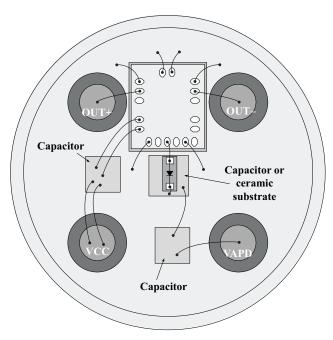

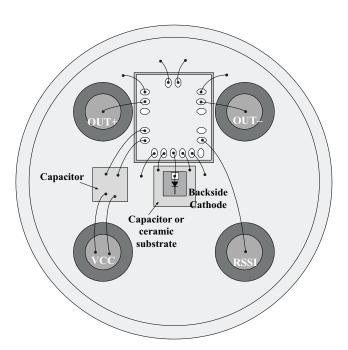

## **TO46 LAYOUT EXAMPLE**

An example for a layout using an external bias voltage for the photodiode in a 5 pin TO46 can is shown in Figure 17. Figure 18 shows an example with a backside cathode contact photodiode using the internal bias voltage.

Figure 17. TO46 5 Pin Layout Using the ONET8521T with an Avalanche Photodiode

Figure 18. TO46 5 Pin Layout Using the Internal Bias Voltage for a Backside Cathode Contact Photodiode

# ZHCS364A – JULY 2011 – REVISED AUGUST 2011

# **REVISION HISTORY**

| CI | Changes from Original (July 2011) to Revision A |    |  |  |  |  |  |

|----|-------------------------------------------------|----|--|--|--|--|--|

| •  | Changed 模具尺寸                                    | 1  |  |  |  |  |  |

| •  | Changed die size                                | 12 |  |  |  |  |  |

www.ti.com 11-Nov-2025

### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|-----------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

| ONET8521TY            | Active | Production    | DIESALE (Y)   0 | 1800   BULK           | -    | Call TI                       | Call TI                    | -40 to 100   |                  |

| ONET8521TY.A          | Active | Production    | DIESALE (Y)   0 | 1800   BULK           | -    | Call TI                       | Call TI                    | -40 to 100   |                  |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,您将全额赔偿,TI 对此概不负责。

TI 提供的产品受 TI 销售条款)、TI 通用质量指南 或 ti.com 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。 除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品,否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025, 德州仪器 (TI) 公司

最后更新日期: 2025 年 10 月