**SN54AHCT573, SN74AHCT573**

ZHCSVW7P OCTOBER 1995 - REVISED APRIL 2024

# SNx4AHCT573 具有三态输出的八路透明 D 类锁存器

# 1 特性

- 输入兼容 TTL 电压

- 闩锁性能超过 250mA, 符合 JESD 17 规范

- 对于符合 MIL-PRF-38535 标准的产品, 所有参数均经过测试,除非另有说明。对于所有其 他产品,生产流程不一定包含对所有参数的测试。

# 2 应用

- 服务器

- PC 和笔记本电脑

- 网络交换机

- 可穿戴保健和健身设备

- 电信基础设施

- 电子销售终端

## 3 说明

SNx4AHCT573 器件是八路透明 D 类锁存器。在锁存 器使能 (LE) 输入为高电平时, Q 输出将跟随数据 (D) 输入。当 LE 为低电平时, Q 输出被锁存在 D 输入端 的逻辑电平上。

器件信息

| 器件型号          | 等级 <sup>(1)</sup> | 封装 <sup>(1)</sup>  |  |  |

|---------------|-------------------|--------------------|--|--|

|               |                   | DB ( SSOP , 20 )   |  |  |

|               |                   | DGV ( TVSOP , 20 ) |  |  |

| SN74AHCT573   | 目录                | DW ( SOIC , 20 )   |  |  |

|               |                   | N ( PDIP , 20 )    |  |  |

|               |                   | PW ( TSSOP , 20 )  |  |  |

| SN54AHCT573   | <b>7</b> II       | J ( CDIP , 20 )    |  |  |

| ONSTALIO 1373 | 军用                | W ( CFP , 20 )     |  |  |

有关更多信息,请参阅节 11。

# **Table of Contents**

Product Folder Links: SN54AHCT573 SN74AHCT573

| 1 特性                                        | 1              |

|---------------------------------------------|----------------|

| 2 应用                                        |                |

| 3 说明                                        |                |

| 4 Pin Configuration and Functions           |                |

| 5 Specifications                            |                |

| 5.1 Absolute Maximum Ratings <sup>(1)</sup> |                |

| 5.2 ESD Ratings                             |                |

| 5.3 Recommended Operating Conditions        | 4              |

| 5.4 Thermal Information                     | 5              |

| 5.5 Electrical Characteristics              | <mark>5</mark> |

| 5.6 Timing Requirements                     | 5              |

| 5.7 Switching Characteristics, SNx4AHCT573  | 6              |

| 5.8 Switching Characteristics, SN54AHCT573  | 6              |

| 5.9 Operating Characteristics               | 6              |

| 5.10 Typical Characteristics                | 7              |

| 6 Parameter Measurement Information         |                |

| 7 Detailed Description                      | 8              |

| 7.1 Overview                                | 8              |

| 7.2 Functional Block Diagram            | 9  |

|-----------------------------------------|----|

| 7.3 Feature Description                 |    |

| 7.4 Device Functional Modes             |    |

| 8 Application and Implementation        | 10 |

| 8.1 Application Information             | 10 |

| 8.2 Typical Application                 | 10 |

| 8.3 Power Supply Recommendations        | 11 |

| 8.4 Layout                              | 11 |

| 9 Device and Documentation Support      | 12 |

| 9.1 接收文档更新通知                            | 12 |

| 9.2 支持资源                                | 12 |

| 9.3 Trademarks                          |    |

| 9.4 静电放电警告                              | 12 |

| 9.5 术语表                                 |    |

| 10 Revision History                     |    |

| 11 Mechanical, Packaging, and Orderable |    |

| Information                             | 13 |

|                                         |    |

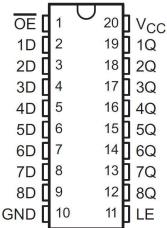

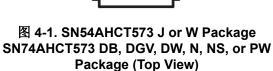

# **4 Pin Configuration and Functions**

图 4-2. SN54AHCT573 FK Package (Top View)

|                         | 表 4-1. Pin Functions |

|-------------------------|----------------------|

| <br>TYPE <sup>(1)</sup> | DE                   |

| PIN |                 | TYPE <sup>(1)</sup> | DESCRIPTION   |

|-----|-----------------|---------------------|---------------|

| NO. | NAME            | ITPE                | DESCRIPTION   |

| 1   | ŌĒ              | I                   | Output Enable |

| 2   | 1D              | I                   | 1D Input      |

| 3   | 2D              | I                   | 2D Input      |

| 4   | 3D              | I                   | 3D Input      |

| 5   | 4D              | I                   | 4D Input      |

| 6   | 5D              | I                   | 5D Input      |

| 7   | 6D              | I                   | 6D Input      |

| 8   | 7D              | I                   | 7D Input      |

| 9   | 8D              | I                   | 8D Input      |

| 10  | GND             | _                   | Ground        |

| 11  | LE              | I                   | Latch Enable  |

| 12  | 8Q              | 0                   | 8Q Output     |

| 13  | 7Q              | 0                   | 7Q Output     |

| 14  | 6Q              | 0                   | 6Q Output     |

| 15  | 5Q              | 0                   | 5Q Output     |

| 16  | 4Q              | 0                   | 4Q Output     |

| 17  | 3Q              | 0                   | 3Q Output     |

| 18  | 2Q              | 0                   | 2Q Output     |

| 19  | 1Q              | 0                   | 1Q Output     |

| 20  | V <sub>CC</sub> | _                   | Power Pin     |

(1) I = input, O = output

# **5 Specifications**

# 5.1 Absolute Maximum Ratings<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                  |                                                   |                             | MIN                   | MAX  | UNIT |

|------------------|---------------------------------------------------|-----------------------------|-----------------------|------|------|

| V <sub>CC</sub>  | Supply voltage range                              |                             | - 0.5                 | 7    | V    |

| VI               | Input voltage range <sup>(2)</sup>                |                             |                       |      | V    |

| Vo               | Output voltage range <sup>(2)</sup>               | - 0.5                       | V <sub>CC</sub> + 0.5 | V    |      |

| I <sub>IK</sub>  | Input clamp current                               | V <sub>I</sub> < 0          |                       | - 20 | mA   |

| I <sub>OK</sub>  | Output clamp current                              | $V_O < 0$ or $V_O > V_{CC}$ |                       | ±20  | mA   |

| Io               | Continuous output current                         | $V_O = 0$ to $V_{CC}$       |                       | ±25  | mA   |

|                  | Continuous current through V <sub>CC</sub> or GND |                             |                       | ±75  | mA   |

| TJ               | Junction temperature                              |                             |                       | 150  | °C   |

| T <sub>stg</sub> | Storage temperature                               |                             | -65                   | 150  | °C   |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 5.2 ESD Ratings

|                    |                          |                                                                       | MIN | MAX   | UNIT |

|--------------------|--------------------------|-----------------------------------------------------------------------|-----|-------|------|

| V                  | Electrostatic discharge  | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     |     | ±2000 | \/   |

| V <sub>(ESD)</sub> | Liectiostatic discriarge | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> |     | ±1000 | V    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 5.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)(1)

|                 |                                    | SN54AHCT573 |                 | SN74AHC | T573            | UNIT |

|-----------------|------------------------------------|-------------|-----------------|---------|-----------------|------|

|                 |                                    | MIN         | MAX             | MIN     | MAX             | UNII |

| V <sub>CC</sub> | Supply voltage                     | 4.5         | 5.5             | 4.5     | 5.5             | V    |

| V <sub>IH</sub> | High-level input voltage           | 2           |                 | 2       |                 | V    |

| V <sub>IL</sub> | Low-level input voltage            |             | 0.8             |         | 0.8             | V    |

| VI              | Input voltage                      | 0           | 5.5             | 0       | 5.5             | V    |

| Vo              | Output voltage                     | 0           | V <sub>CC</sub> | 0       | V <sub>CC</sub> | V    |

| I <sub>OH</sub> | High-level output current          |             | - 8             |         | - 8             | mA   |

| I <sub>OL</sub> | Low-level output current           |             | 8               |         | 8               | mA   |

| Δt/Δν           | Input transition rise or fall rate |             | 20              |         | 20              | ns/V |

| T <sub>A</sub>  | Operating free-air temperature     | - 55        | 125             | - 40    | 125             | °C   |

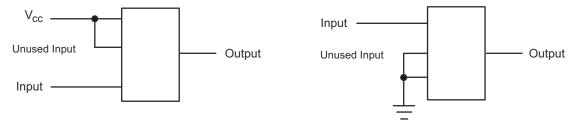

All unused inputs of the device must be held at V<sub>CC</sub> or GND to ensure proper device operation. Refer to the TI application report, Implications of Slow or Floating CMOS Inputs (SCBA004).

Product Folder Links: SN54AHCT573 SN74AHCT573

The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## **5.4 Thermal Information**

|                        |                                              | SN74AHCT573 |      |       |      |      |       |      |  |  |

|------------------------|----------------------------------------------|-------------|------|-------|------|------|-------|------|--|--|

|                        | THERMAL METRIC <sup>(1)</sup>                | DW          | DB   | DGV   | N    | NS   | PW    | UNIT |  |  |

|                        |                                              |             |      | 20 PI | IS   |      |       |      |  |  |

| R <sub>0</sub> JA      | Junction-to-ambient thermal resistance       | 79.4        | 97.9 | 117.2 | 53.3 | 79.2 | 103.3 |      |  |  |

| R <sub>θ JC(top)</sub> | Junction-to-case (top) thermal resistance    | 45.7        | 59.6 | 32.7  | 40.0 | 45.7 | 37.8  | 1    |  |  |

| R <sub>0</sub> JB      | Junction-to-board thermal resistance         | 46.9        | 53.1 | 58.7  | 34.2 | 46.8 | 54.3  | °C/W |  |  |

| ψJT                    | Junction-to-top characterization parameter   | 18.7        | 21.3 | 1.15  | 26.4 | 19.3 | 2.9   | C/VV |  |  |

| ψ ЈВ                   | Junction-to-board characterization parameter | 46.5        | 52.7 | 58.0  | 34.1 | 46.4 | 53.8  | 1    |  |  |

| R <sub>θ JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | n/a         | n/a  | n/a   | n/a  | n/a  | n/a   |      |  |  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report (SPRA953).

### **5.5 Electrical Characteristics**

over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER                        | TEST CONDITIONS                                              | V <sub>cc</sub> | V <sub>CC</sub> T <sub>A</sub> = 25°C |     | - 55°C to 125°C<br>SN54AHCT573 |     | - 40°C to 85°C<br>SN74AHCT573 |     | - 40°C to 125°C<br>SN74AHCT573 |     | UNIT |    |

|----------------------------------|--------------------------------------------------------------|-----------------|---------------------------------------|-----|--------------------------------|-----|-------------------------------|-----|--------------------------------|-----|------|----|

|                                  |                                                              |                 | MIN                                   | TYP | MAX                            | MIN | MAX                           | MIN | MAX                            | MIN | MAX  |    |

| V                                | I <sub>OH</sub> = -50 μA                                     | 4.5V            | 4.4                                   | 4.5 |                                | 4.4 |                               | 4.4 |                                | 4.4 |      | V  |

| V <sub>OH</sub>                  | I <sub>OH</sub> = -8mA                                       | 4.50            | 3.94                                  |     |                                | 3.8 |                               | 3.8 |                                | 3.8 |      | V  |

| V                                | I <sub>OL</sub> = 50 μA                                      | 4.5V            |                                       |     | 0.1                            |     | 0.1                           |     | 0.1                            |     | 0.1  | V  |

| V <sub>OL</sub>                  | I <sub>OL</sub> = 8mA                                        | 4.50            |                                       |     | 0.36                           |     | 0.44                          |     | 0.44                           |     | 0.44 | V  |

| I <sub>I</sub>                   | V <sub>I</sub> = 5.5V or GND                                 | 0V to<br>5.5V   |                                       |     | ±0.1                           |     | ±1 <sup>(1)</sup>             |     | ±1                             |     | ±2   | μA |

| I <sub>OZ</sub>                  | V <sub>O</sub> = V <sub>CC</sub> or GND                      | 5.5V            |                                       |     | ±0.25                          |     | ±2.5                          |     | ±2.5                           |     | ±2.5 | μA |

| Icc                              | $V_I = V_{CC}$ or GND, $I_O = 0$                             | 5.5V            |                                       |     | 4                              |     | 40                            |     | 40                             |     | 40   | μA |

| Δ I <sub>CC</sub> <sup>(2)</sup> | One input at 3.4V,<br>Other inputs at V <sub>CC</sub> or GND | 5.5V            |                                       |     | 1.35                           |     | 1.5                           |     | 1.5                            |     | 1.5  | mA |

| Ci                               | V <sub>I</sub> = V <sub>CC</sub> or GND                      | 5V              |                                       | 2.5 | 10                             |     |                               |     | 10                             |     | 10   | pF |

| Co                               | V <sub>O</sub> = V <sub>CC</sub> or GND                      | 5V              |                                       | 3   |                                |     |                               |     |                                |     |      | pF |

<sup>(1)</sup> On products compliant to MIL-PRF-38535, this parameter is not production tested at  $V_{CC}$  = 0V.

# 5.6 Timing Requirements

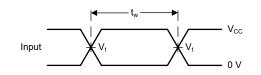

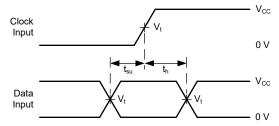

over recommended operating free-air temperature range,  $V_{CC}$  = 5V ± 0.5V (unless otherwise noted) (see  $\ddagger$  6)

| PARAMETER       |                              | T <sub>A</sub> = 2 | 25°C | 125° | - 55°C to<br>125°C<br>SN54AHCT573 |     | - 40°C to 85°C<br>SN74AHCT573 |     | - 40°C to 125°C<br>SN74AHCT573 |    |

|-----------------|------------------------------|--------------------|------|------|-----------------------------------|-----|-------------------------------|-----|--------------------------------|----|

|                 |                              | MIN                | MAX  | MIN  | MAX                               | MIN | MAX                           | MIN | MAX                            |    |

| t <sub>w</sub>  | Pulse duration, LE high      | 5                  |      | 5    |                                   | 5   |                               | 5   |                                | ns |

| t <sub>su</sub> | Setup time, data before LE ↓ | 3.5                |      | 3.5  |                                   | 3.5 |                               | 3.5 |                                | ns |

| t <sub>h</sub>  | Hold time, data after LE ↓   | 1.5                |      | 1.5  |                                   | 1.5 |                               | 1.5 |                                | ns |

提交文档反馈

5

<sup>(2)</sup> This is the increase in supply current for each input at one of the specified TTL voltage levels, rather than 0V or V<sub>CC</sub>.

# 5.7 Switching Characteristics, SNx4AHCT573

over recommended operating free-air temperature range,  $V_{CC}$  = 5V  $\pm$  0.5V (unless otherwise noted) (see  $\ddagger$  6)

| PARAMETER             | FROM    | то       | T <sub>A</sub> = 25°C |     | T <sub>A</sub> = -40°C | to 85°C | T <sub>A</sub> = -40°C | to 125°C | UNIT |

|-----------------------|---------|----------|-----------------------|-----|------------------------|---------|------------------------|----------|------|

| PARAMETER             | (INPUT) | (OUTPUT) | MIN TYP               | MAX | MIN                    | MAX     | MIN                    | MAX      | UNII |

| C <sub>L</sub> = 15pF |         | •        |                       |     |                        |         |                        |          |      |

| t <sub>pd</sub>       | D       | Q        | 5.1                   | 7   | 1                      | 9       | 1                      | 9.5      | ns   |

| t <sub>pd</sub>       | LE      | Q        | 5.6                   | 7.5 | 1                      | 9       | 1                      | 9.5      | ns   |

| t <sub>en</sub>       | ŌĒ      | Q        | 5.5                   | 7.5 | 1                      | 10      | 1                      | 11       | ns   |

| t <sub>dis</sub>      | ŌĒ      | Q        | 5.5                   | 8   | 1                      | 11      | 1                      | 12       | ns   |

| C <sub>L</sub> = 50pF |         |          |                       |     |                        |         |                        |          |      |

| t <sub>pd</sub>       | D       | Q        | 6.1                   | 8   | 1                      | 10      | 1                      | 10.5     | ns   |

| t <sub>pd</sub>       | LE      | Q        | 6.6                   | 8.5 | 1                      | 10      | 1                      | 10.5     | ns   |

| t <sub>en</sub>       | ŌĒ      | Q        | 6.5                   | 8.5 | 1                      | 11      | 1                      | 11.5     | ns   |

| t <sub>dis</sub>      | ŌĒ      | Q        | 6.7                   | 9   | 1                      | 12      | 1                      | 12.5     | ns   |

| t <sub>sk(o)</sub>    |         |          |                       | 1.5 |                        | 1.5     |                        |          | ns   |

<sup>(1)</sup> On products compliant to MIL-PRF-38535, this parameter is not production tested.

## 5.8 Switching Characteristics, SN54AHCT573

over recommended operating free-air temperature range,  $V_{CC}$  = 5V  $\pm$  0.5V (unless otherwise noted) (see  $\ddagger$  6)

| PARAMETER             | FROM    | то       |     | = 25°C             |                    | T <sub>A</sub> = -55°C to | 125°C             | UNIT |

|-----------------------|---------|----------|-----|--------------------|--------------------|---------------------------|-------------------|------|

| PARAMETER             | (INPUT) | (OUTPUT) | MIN | TYP                | MAX                | MIN                       | MAX               | UNII |

| C <sub>L</sub> = 15pF |         |          |     |                    | •                  |                           |                   |      |

| t <sub>pd</sub>       | D       | Q        |     | 5.1 <sup>(1)</sup> | 7 <sup>(1)</sup>   | 1 <sup>(1)</sup>          | 9 <sup>(1)</sup>  | ns   |

| t <sub>pd</sub>       | LE      | Q        |     | 5.6 <sup>(1)</sup> | 7.5 <sup>(1)</sup> | 1 <sup>(1)</sup>          | 9 <sup>(1)</sup>  | ns   |

| t <sub>en</sub>       | ŌĒ      | Q        |     | 5.5 <sup>(1)</sup> | 7.5 <sup>(1)</sup> | 1 <sup>(1)</sup>          | 9 <sup>(1)</sup>  | ns   |

| t <sub>dis</sub>      | ŌĒ      | Q        |     | 5.5 <sup>(1)</sup> | 8 <sup>(1)</sup>   | 1 <sup>(1)</sup>          | 11 <sup>(1)</sup> | ns   |

| C <sub>L</sub> = 50pF |         |          |     | ,                  |                    |                           |                   |      |

| t <sub>pd</sub>       | D       | Q        |     | 6.1                | 8                  | 1                         | 10                | ns   |

| t <sub>pd</sub>       | LE      | Q        |     | 6.6                | 8.5                | 1                         | 10                | ns   |

| t <sub>en</sub>       | ŌĒ      | Q        |     | 6.5                | 8.5                | 1                         | 11                | ns   |

| t <sub>dis</sub>      | ŌĒ      | Q        |     | 6.7                | 9                  | 1                         | 12                | ns   |

| t <sub>sk(o)</sub>    |         |          |     |                    | 1.5 <sup>(2)</sup> |                           |                   | ns   |

# **5.9 Operating Characteristics**

$V_{CC}$  = 5V,  $T_A$  = 25°C

|          | PARAMETER                     | TEST CO  | TYP      | UNIT |    |

|----------|-------------------------------|----------|----------|------|----|

| $C_{pd}$ | Power dissipation capacitance | No load, | f = 1MHz | 16   | рF |

<sup>(2)</sup> On products compliant to MIL-PRF-38535, this parameter does not apply.

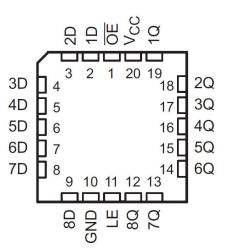

# 5.10 Typical Characteristics

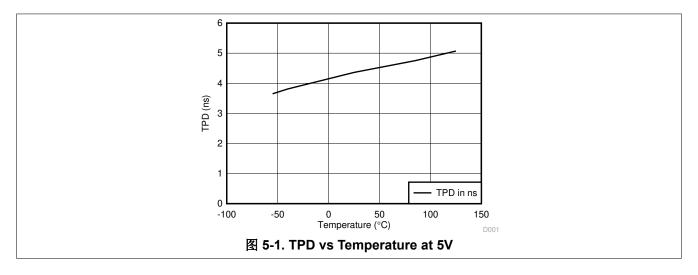

### **6 Parameter Measurement Information**

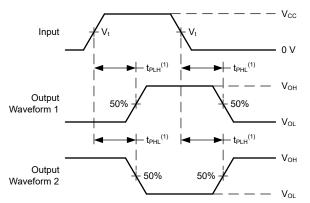

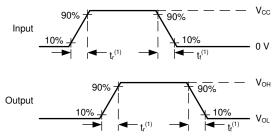

Phase relationships between waveforms were chosen arbitrarily. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  1MHz,  $Z_O$  = 50 $\Omega$ ,  $R_L$  = 1k $\Omega$ ,  $t_t$  < 3ns,  $V_t$  = 1.5V.

For clock inputs,  $f_{max}$  is measured when the input duty cycle is 50%.

The outputs are measured one at a time with one input transition per measurement.

(1)  $C_L$  includes probe and test-fixture capacitance.

图 6-1. Load Circuit for 3-State Outputs

图 6-2. Voltage Waveforms, Pulse Duration

图 6-3. Voltage Waveforms, Setup and Hold Times

(1) The greater between t<sub>PLH</sub> and t<sub>PHL</sub> is the same as t<sub>pd</sub>. 图 **6-4. Voltage Waveforms, Propagation Delays**

$V_{CC}$ Input 0 V Output ≈ V<sub>CC</sub> Waveform 1 50% S1 CLOSED, 10% S2 OPEN  $V_{\text{OH}}$ Output 90% Waveform 2 50% S1 OPEN, S2 CLOSED ≈ 0 V

- (1)  $t_{\text{PLZ}}$  and  $t_{\text{PHZ}}$  are the same as  $t_{\text{dis}}$ .

- (2)  $t_{PZL}$  and  $t_{PZH}$  are the same as  $t_{en}$ .

图 6-5. Voltage Waveforms, Propagation Delays for 3-State Outputs

(1) The greater between t<sub>r</sub> and t<sub>f</sub> is the same as t<sub>t</sub>.

图 6-6. Voltage Waveforms, Input and Output Transition Times

# 7 Detailed Description

#### 7.1 Overview

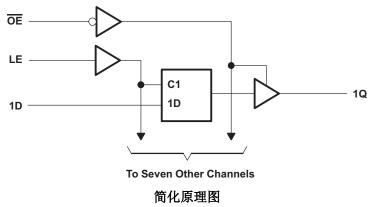

The SNx4AHCT573 devices are octal transparent D-type latches. When the latch-enable (LE) input is high, the Q outputs follow the data (D) inputs. When LE is low, the Q outputs are latched at the logic levels of the D inputs.

A buffered output-enable  $(\overline{OE})$  input can be used to place the eight outputs in either a normal logic state (high or low) or the high-impedance state. In the high-impedance state, the outputs neither load nor drive the bus lines significantly. The high-impedance state and increased drive provide the capability to drive bus lines without interface or pull-up components.

To put the device in the high-impedance state during power up or power down, tie  $\overline{OE}$  to  $V_{CC}$  through a pull-up resistor; the current-sinking capability of the driver determines the minimum value of the resistor.

OE does not affect the internal operations of the latches. Old data can be retained or new data can be entered while the outputs are in the high-impedance state.

English Data Sheet: SCLS243

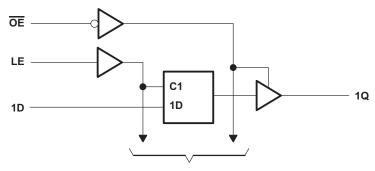

# 7.2 Functional Block Diagram

To Seven Other Channels

# 7.3 Feature Description

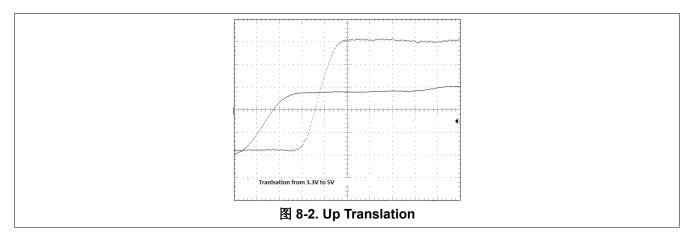

- TTL inputs

- Lowered switching threshold allows up translation 3.3V to 5V

- · Slow edges reduce output ringing

## 7.4 Device Functional Modes

表 7-1. Function Table (Each Latch)

| ı  | INPUTS | OUTPUT |       |

|----|--------|--------|-------|

| ŌĒ | LE     | D      | Q     |

| L  | Н      | Н      | Н     |

| L  | Н      | L      | L     |

| L  | L      | Χ      | $Q_0$ |

| Н  | Χ      | Χ      | Z     |

# 8 Application and Implementation

### 备注

以下应用部分中的信息不属于 TI 器件规格的范围,TI 不担保其准确性和完整性。TI 的客 户应负责确定 器件是否适用于其应用。客户应验证并测试其设计,以确保系统功能。

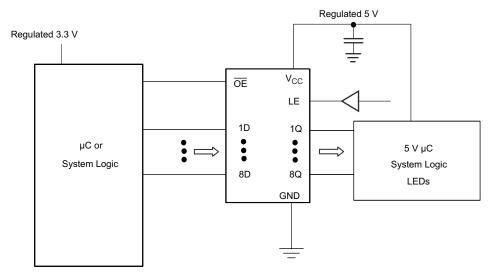

## 8.1 Application Information

The SN74AHCT573 is a low-drive CMOS device that can be used for a multitude of bus interface type applications where output ringing is a concern. The low drive and slow edge rates will minimize overshoot and undershoot on the outputs. The input switching levels have been lowered to accommodate TTL inputs of 0.8V shows this type of translation.

## 8.2 Typical Application

图 8-1. Typical Application Schematic

#### 8.2.1 Design Requirements

This device uses CMOS technology and has balanced output drive. Take care to avoid bus contention because it can drive currents that would exceed maximum limits. The high drive will also create fast edges into light loads; therefore, routing and load conditions should be considered to prevent ringing.

# 8.2.2 Detailed Design Procedure

- 1. Recommended input conditions:

- Rise time and fall time specs: See ( $\triangle t/\triangle V$ ) in the *Recommended Operating Conditions* table.

- Specified High and low levels: See (VIH and VIL) in the Recommended Operating Conditions table.

- Inputs are overvoltage tolerant allowing them to go as high as 5.5V at any valid  $V_{CC}$ .

- 2. Recommend output conditions

- Load currents should not exceed 25mA per output and 75mA total for the part.

- Outputs should not be pulled above V<sub>CC</sub>.

Copyright © 2024 Texas Instruments Incorporated

### 8.2.3 Application Curves

# 8.3 Power Supply Recommendations

The power supply can be any voltage between the MIN and MAX supply voltage rating located in the *Recommended Operating Conditions* table.

Each  $V_{CC}$  pin should have a good bypass capacitor to prevent power disturbance. For devices with a single supply,  $0.1~\mu$  F bypass capacitor is recommended. If there are multiple  $V_{CC}$  pins,  $0.01~\mu$  F or  $0.022~\mu$  F is recommended for each power pin. It is acceptable to parallel multiple bypass capacitors to reject different frequencies of noise. A  $0.1~\mu$  F and  $1~\mu$  F are commonly used in parallel. The bypass capacitor should be installed as close to the power pin as possible for best results.

#### 8.4 Layout

#### 8.4.1 Layout Guidelines

When using multiple bit logic devices inputs should never float.

In many cases, functions or parts of functions of digital logic devices are unused (for example, when only two inputs of a triple-input AND gate are used or only 3 of the 4 buffer gates are used). Such input pins should not be left unconnected because the undefined voltages at the outside connections result in undefined operational states. 8 8-3 specifies the rules that must be observed under all circumstances.

All unused inputs of digital logic devices must be connected to a high or low bias to prevent them from floating. The logic level that should be applied to any particular unused input depends on the function of the device. Generally they will be tied to GND or  $V_{CC}$ ; whichever makes more sense or is more convenient. It is generally acceptable to float outputs unless the part is a transceiver. If the transceiver has an output enable pin, then it will disable the outputs section of the part when asserted. This will not disable the input section of the IOs so they cannot float when disabled.

### 8.4.2 Layout Example

图 8-3. Layout Diagram

11

# 9 Device and Documentation Support

## 9.1 接收文档更新通知

要接收文档更新通知,请导航至 ti.com 上的器件产品文件夹。点击*通知* 进行注册,即可每周接收产品信息更改摘要。有关更改的详细信息,请查看任何已修订文档中包含的修订历史记录。

### 9.2 支持资源

TI E2E™中文支持论坛是工程师的重要参考资料,可直接从专家处获得快速、经过验证的解答和设计帮助。搜索现有解答或提出自己的问题,获得所需的快速设计帮助。

链接的内容由各个贡献者"按原样"提供。这些内容并不构成 TI 技术规范,并且不一定反映 TI 的观点;请参阅 TI 的使用条款。

#### 9.3 Trademarks

TI E2E™ is a trademark of Texas Instruments.

所有商标均为其各自所有者的财产。

### 9.4 静电放电警告

静电放电 (ESD) 会损坏这个集成电路。德州仪器 (TI) 建议通过适当的预防措施处理所有集成电路。如果不遵守正确的处理和安装程序,可能会损坏集成电路。

ESD 的损坏小至导致微小的性能降级,大至整个器件故障。精密的集成电路可能更容易受到损坏,这是因为非常细微的参数更改都可能会导致器件与其发布的规格不相符。

### 9.5 术语表

TI术语表本术语表列出并解释了术语、首字母缩略词和定义。

Changes from Revision N (July 2003) to Revision O (July 2014)

# 10 Revision History

注:以前版本的页码可能与当前版本的页码不同

| С | hanges from Revision O (July 2014) to Revision P (April 2024)                                                                                                                                        | Page           |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| • | Moved storage temperature from Handling Ratings table to Absolute Maximum Ratings table                                                                                                              | 4              |

| • | Changed Handling Ratings table to ESD Ratings table                                                                                                                                                  | 4              |

| • | Added temperature range column labels in Electrical Characteristics table                                                                                                                            | <mark>5</mark> |

| • | Added temperature range column labels in Timing Requirements table                                                                                                                                   | <mark>5</mark> |

| • | Changed t <sub>PLH</sub> and t <sub>PHL</sub> to be t <sub>pd</sub> , t <sub>PZH</sub> and t <sub>PZL</sub> to be t <sub>en</sub> , and t <sub>PLZ</sub> and t <sub>PHZ</sub> to be t <sub>dis</sub> | 6              |

|   | Changed Switching Characteristics table to be two tables separating military and catalog device characteristics                                                                                      |                |

| • | Changed parameter measurement information section images and tables to improve clarity and upda formatting                                                                                           |                |

| _ |                                                                                                                                                                                                      |                |

| _ | goo nom nonon n (out) = ooo, to nononon o (out) = o n,                               |   |

|---|--------------------------------------------------------------------------------------|---|

| • | 将文档更新为新的 TI 数据表格式                                                                    | 1 |

|   | 删除了"订购信息"表                                                                           |   |

|   | 向"特性"列表中添加了"军用免责声明"                                                                  |   |

|   | 添加了"应用"                                                                              |   |

|   | Added Pin Functions table                                                            |   |

|   | Added Handling Ratings table                                                         |   |

|   | Changed MAX operating temperature to 125°C in Recommended Operating Conditions table |   |

|   | Added Thermal Information table                                                      |   |

|   |                                                                                      |   |

Copyright © 2024 Texas Instruments Incorporated

Page

#### www.ti.com.cn

| • | Added - 40°C to 125°C temperature range for SNx4AHCT573 in Electrical Characteristics table | 5 |

|---|---------------------------------------------------------------------------------------------|---|

| • | Added - 40°C to 125°C temperature range for SNx4AHCT573 in Timing Requirements table        | 5 |

| • | Added Typical Characteristics                                                               | 7 |

|   | Added Application and Implementation section                                                |   |

|   | Added Power Supply Recommendations and Layout sections                                      |   |

|   | ,                                                                                           |   |

# 11 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

提交文档反馈

Product Folder Links: SN54AHCT573 SN74AHCT573

13

www.ti.com

16-Apr-2024

#### **PACKAGING INFORMATION**

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan            | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5)              | Samples |

|------------------|------------|--------------|--------------------|------|----------------|---------------------|-------------------------------|--------------------|--------------|--------------------------------------|---------|

| 5962-9685501QRA  | ACTIVE     | CDIP         | J                  | 20   | 20             | Non-RoHS<br>& Green | SNPB                          | N / A for Pkg Type | -55 to 125   | 5962-9685501QR<br>A<br>SNJ54AHCT573J | Samples |

| 5962-9685501QSA  | ACTIVE     | CFP          | W                  | 20   | 25             | Non-RoHS<br>& Green | SNPB                          | N / A for Pkg Type | -55 to 125   | 5962-9685501QS<br>A<br>SNJ54AHCT573W | Samples |

| SN74AHCT573DBR   | ACTIVE     | SSOP         | DB                 | 20   | 2000           | RoHS & Green        | NIPDAU                        | Level-1-260C-UNLIM | -40 to 125   | HB573                                | Samples |

| SN74AHCT573DGVR  | ACTIVE     | TVSOP        | DGV                | 20   | 2000           | RoHS & Green        | NIPDAU                        | Level-1-260C-UNLIM | -40 to 125   | HB573                                | Samples |

| SN74AHCT573DWR   | ACTIVE     | SOIC         | DW                 | 20   | 2000           | RoHS & Green        | NIPDAU                        | Level-1-260C-UNLIM | -40 to 125   | AHCT573                              | Samples |

| SN74AHCT573N     | ACTIVE     | PDIP         | N                  | 20   | 20             | RoHS & Green        | NIPDAU                        | N / A for Pkg Type | -40 to 125   | SN74AHCT573N                         | Samples |

| SN74AHCT573PWR   | ACTIVE     | TSSOP        | PW                 | 20   | 2000           | RoHS & Green        | NIPDAU   SN                   | Level-1-260C-UNLIM | -40 to 125   | HB573                                | Samples |

| SN74AHCT573PWRE4 | ACTIVE     | TSSOP        | PW                 | 20   | 2000           | RoHS & Green        | NIPDAU                        | Level-1-260C-UNLIM | -40 to 125   | HB573                                | Samples |

| SN74AHCT573PWRG4 | ACTIVE     | TSSOP        | PW                 | 20   | 2000           | RoHS & Green        | NIPDAU                        | Level-1-260C-UNLIM | -40 to 125   | HB573                                | Samples |

| SNJ54AHCT573J    | ACTIVE     | CDIP         | J                  | 20   | 20             | Non-RoHS<br>& Green | SNPB                          | N / A for Pkg Type | -55 to 125   | 5962-9685501QR<br>A<br>SNJ54AHCT573J | Samples |

| SNJ54AHCT573W    | ACTIVE     | CFP          | W                  | 20   | 25             | Non-RoHS<br>& Green | SNPB                          | N / A for Pkg Type | -55 to 125   | 5962-9685501QS<br>A<br>SNJ54AHCT573W | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

<sup>(2)</sup> **RoHS**: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

# PACKAGE OPTION ADDENDUM

www.ti.com 16-Apr-2024

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF SN54AHCT573, SN74AHCT573:

Catalog: SN74AHCT573

Military: SN54AHCT573

NOTE: Qualified Version Definitions:

- Catalog TI's standard catalog product

- Military QML certified for Military and Defense Applications

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 16-Apr-2024

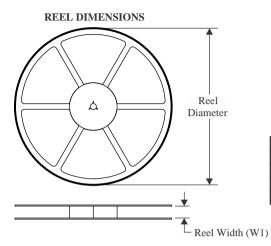

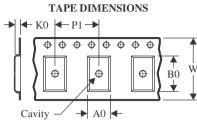

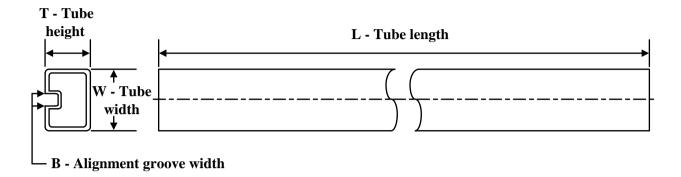

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

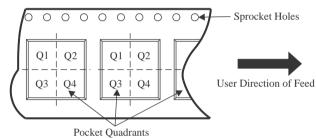

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device           | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| SN74AHCT573DBR   | SSOP            | DB                 | 20 | 2000 | 330.0                    | 16.4                     | 8.2        | 7.5        | 2.5        | 12.0       | 16.0      | Q1               |

| SN74AHCT573DGVR  | TVSOP           | DGV                | 20 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| SN74AHCT573DWR   | SOIC            | DW                 | 20 | 2000 | 330.0                    | 24.4                     | 10.8       | 13.3       | 2.7        | 12.0       | 24.0      | Q1               |

| SN74AHCT573PWR   | TSSOP           | PW                 | 20 | 2000 | 330.0                    | 16.4                     | 6.95       | 7.0        | 1.4        | 8.0        | 16.0      | Q1               |

| SN74AHCT573PWRG4 | TSSOP           | PW                 | 20 | 2000 | 330.0                    | 16.4                     | 6.95       | 7.0        | 1.4        | 8.0        | 16.0      | Q1               |

www.ti.com 16-Apr-2024

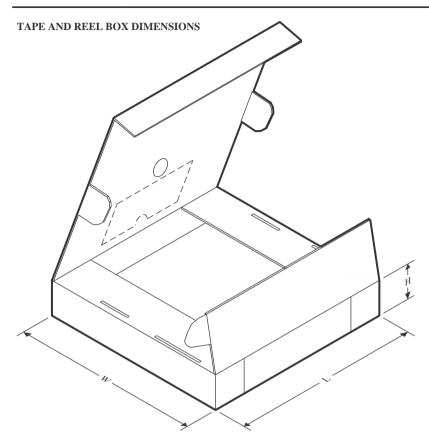

\*All dimensions are nominal

| 7 till dillitoriolorio di o riorinii di |              |                 |      |      |             |            |             |

|-----------------------------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| Device                                  | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

| SN74AHCT573DBR                          | SSOP         | DB              | 20   | 2000 | 356.0       | 356.0      | 35.0        |

| SN74AHCT573DGVR                         | TVSOP        | DGV             | 20   | 2000 | 356.0       | 356.0      | 35.0        |

| SN74AHCT573DWR                          | SOIC         | DW              | 20   | 2000 | 367.0       | 367.0      | 45.0        |

| SN74AHCT573PWR                          | TSSOP        | PW              | 20   | 2000 | 356.0       | 356.0      | 35.0        |

| SN74AHCT573PWRG4                        | TSSOP        | PW              | 20   | 2000 | 356.0       | 356.0      | 35.0        |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 16-Apr-2024

## **TUBE**

### \*All dimensions are nominal

| Device          | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|-----------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| 5962-9685501QSA | W            | CFP          | 20   | 25  | 506.98 | 26.16  | 6220   | NA     |

| SN74AHCT573N    | N            | PDIP         | 20   | 20  | 506    | 13.97  | 11230  | 4.32   |

| SNJ54AHCT573W   | W            | CFP          | 20   | 25  | 506.98 | 26.16  | 6220   | NA     |

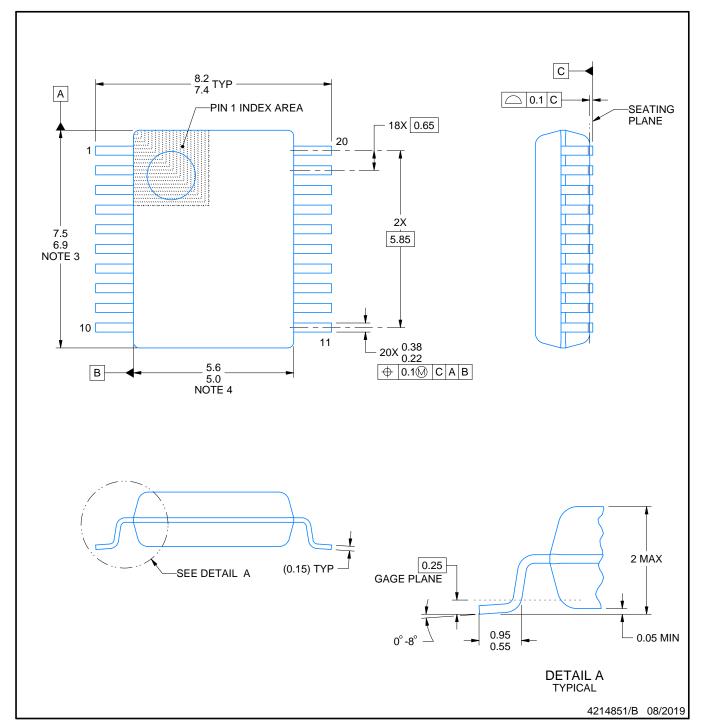

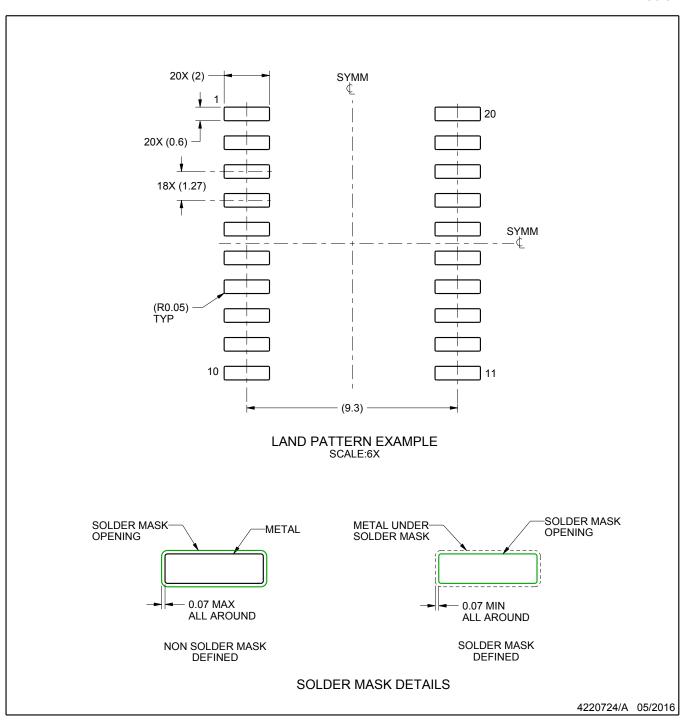

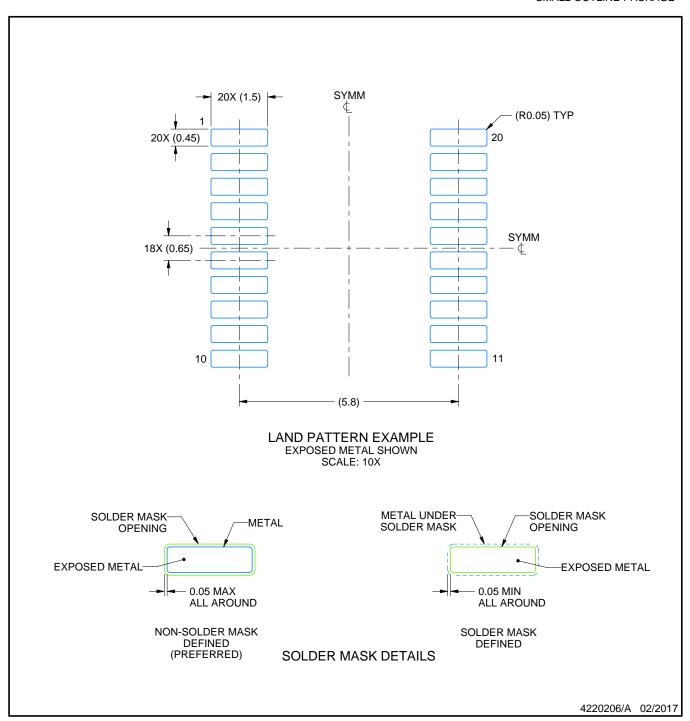

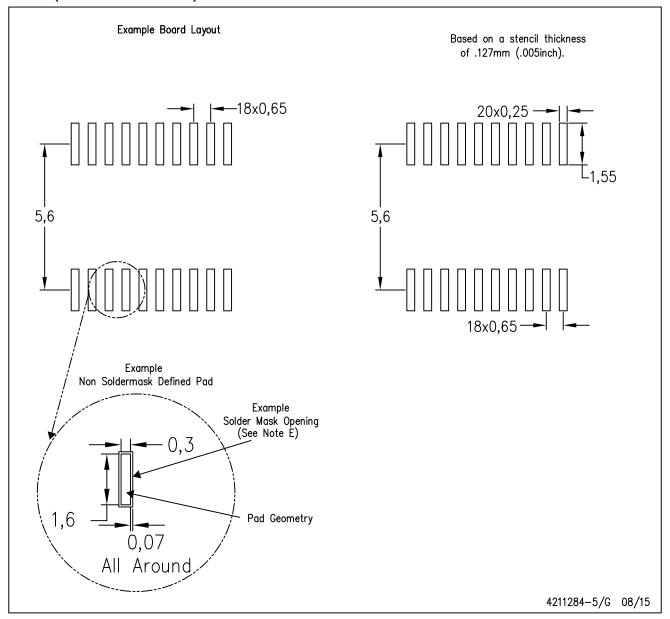

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-150.

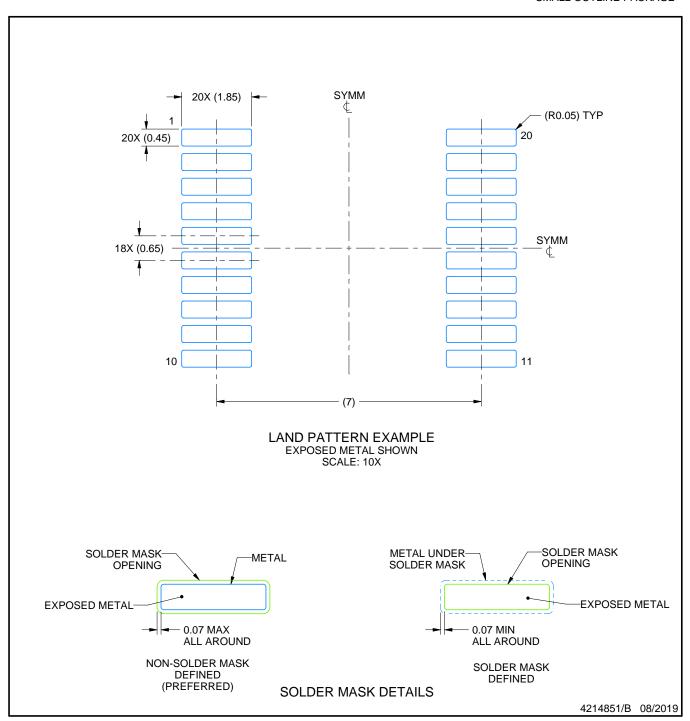

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

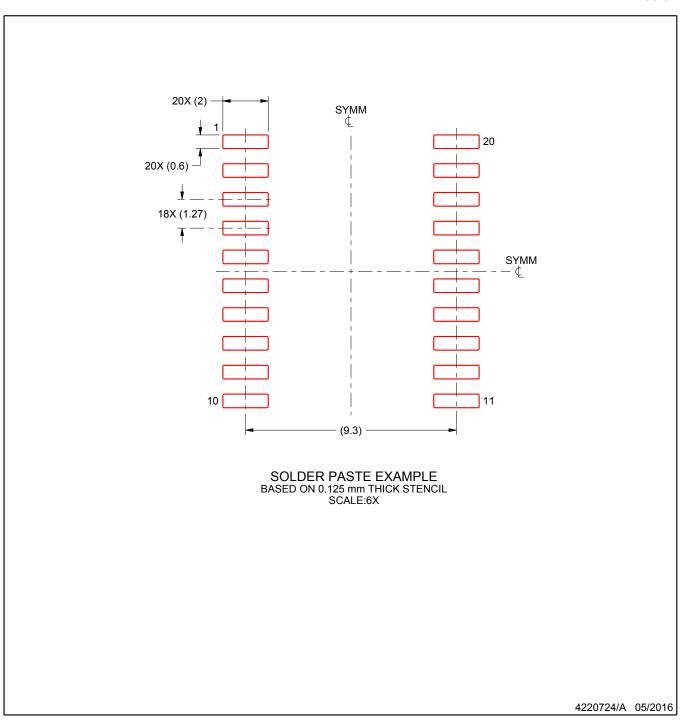

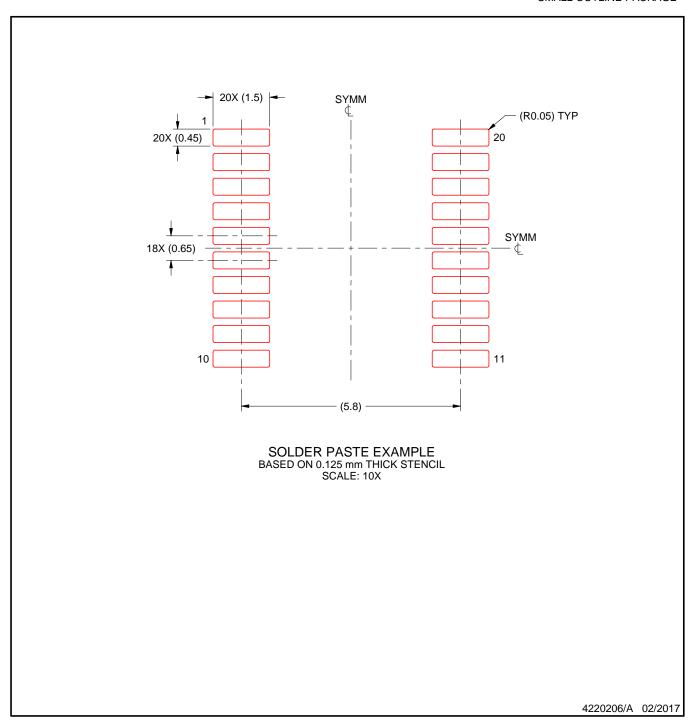

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

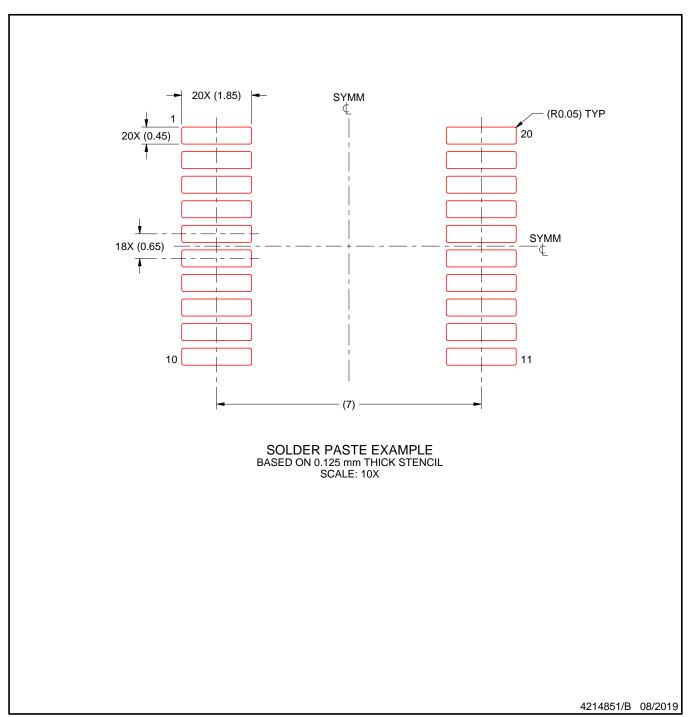

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

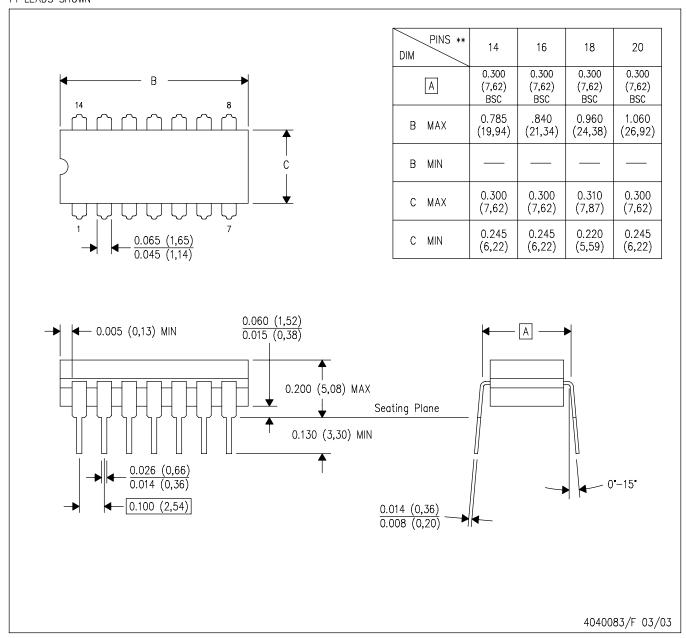

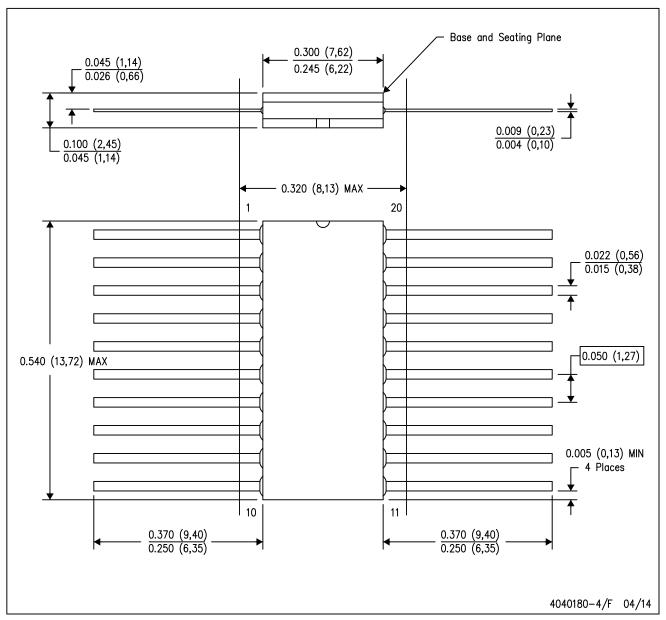

### 14 LEADS SHOWN

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package is hermetically sealed with a ceramic lid using glass frit.

- D. Index point is provided on cap for terminal identification only on press ceramic glass frit seal only.

- E. Falls within MIL STD 1835 GDIP1-T14, GDIP1-T16, GDIP1-T18 and GDIP1-T20.

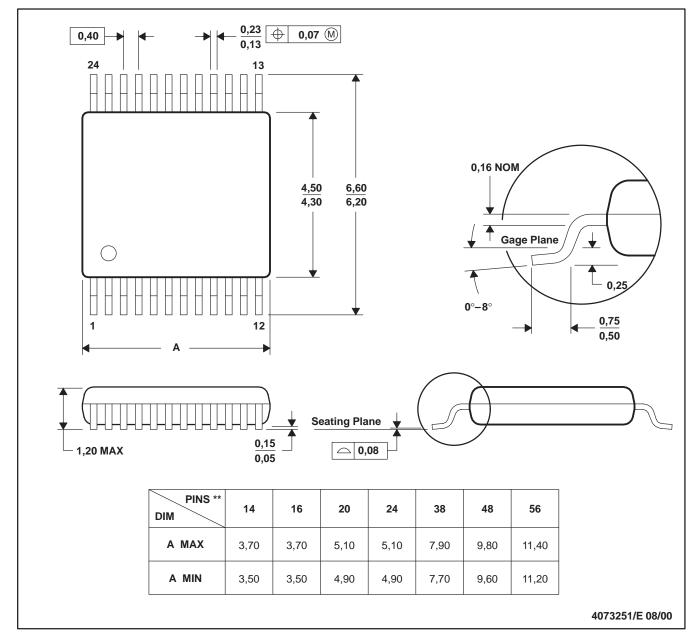

# DGV (R-PDSO-G\*\*)

## 24 PINS SHOWN

#### **PLASTIC SMALL-OUTLINE**

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion, not to exceed 0,15 per side.

D. Falls within JEDEC: 24/48 Pins – MO-153 14/16/20/56 Pins – MO-194

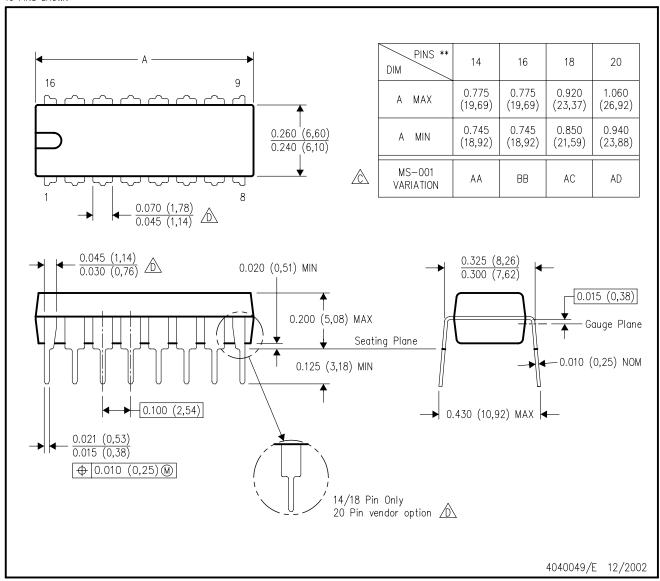

# N (R-PDIP-T\*\*)

# PLASTIC DUAL-IN-LINE PACKAGE

16 PINS SHOWN

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Falls within JEDEC MS-001, except 18 and 20 pin minimum body length (Dim A).

- The 20 pin end lead shoulder width is a vendor option, either half or full width.

SOIC

- 1. All linear dimensions are in millimeters. Dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.43 mm per side.

- 5. Reference JEDEC registration MS-013.

SOIC

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SOIC

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

# W (R-GDFP-F20)

# CERAMIC DUAL FLATPACK

- A. All linear dimensions are in inches (millimeters).

- This drawing is subject to change without notice.

- C. This package can be hermetically sealed with a ceramic lid using glass frit.

D. Index point is provided on cap for terminal identification only.

E. Falls within Mil—Std 1835 GDFP2—F20

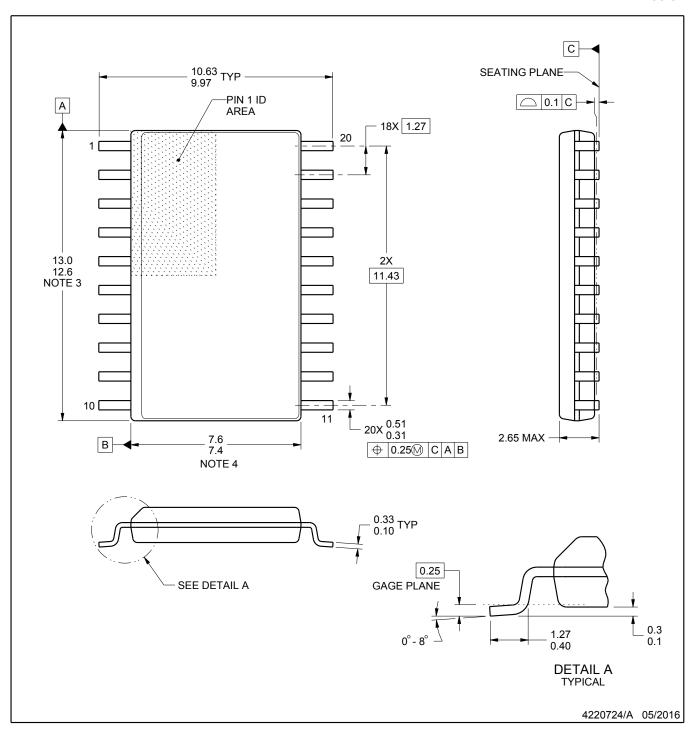

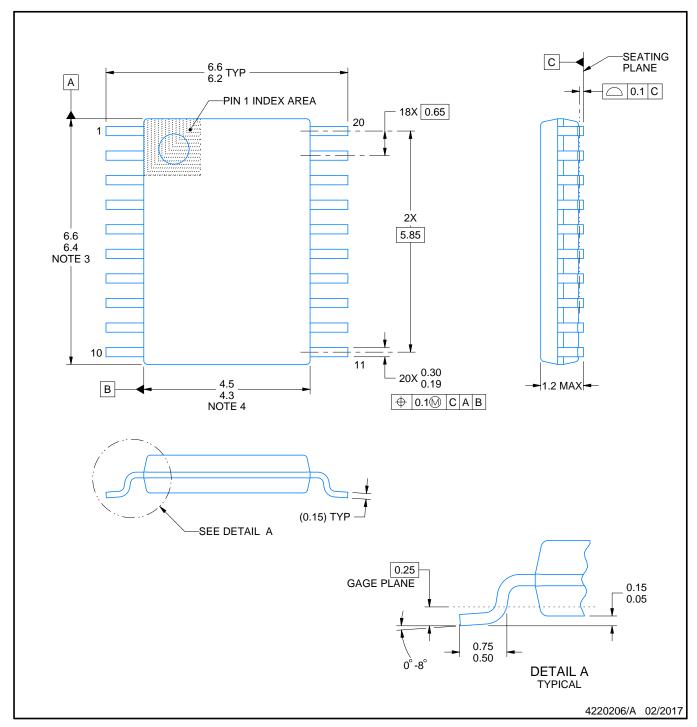

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-153.

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

# PW (R-PDSO-G20)

# PLASTIC SMALL OUTLINE

- All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.C. Publication IPC-7351 is recommended for alternate design.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

# 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024,德州仪器 (TI) 公司