Support & training

#### **TL16C550C**

ZHCSS40I - MARCH 1994 - REVISED MARCH 2021

# TL16C550C 具有自动流控制的异步通信元件

## 1 特性

Texas

INSTRUMENTS

- 可编程自动 RTS 和自动 CTS •

- 在自动 CTS 模式下, CTS 控制发送器

- 在自动 RTS 模式下, RCV FIFO 内容和阈值控制 RTS

- 当设备处于相同的功率降低状态时,串行和调制解 调器控制输出直接驱动 RJ11 线缆

- 能够与所有现有的 TL16C450 软件一起运行

- 复位后,所有寄存器与 TL16C450 寄存器组相同

- 时钟速率高达 16MHz, 支持高达 1Mbaud 的运行

- 在 TL16C450 模式下,保持和移位寄存器无需在 CPU 和串行数据之间进行精确同步

- 可编程波特率发生器可对任何输入参考时钟进行1 至 (2<sup>16</sup>-1) 分频并生成一个内部 16× 时钟

- 向串行数据流添加或从串行数据流中删除的标准异 步通信位(起始位、停止位和奇偶校验位)

- 5V和3.3V运行

- 独立的接收器时钟输入

- 发送、接收、线路状态和数据集中断独立控制

- 完全可编程的串行接口特性:

- 5 位、6 位、7 位或 8 位字符

- 偶校验、奇校验或无奇偶校验位生成与检测

- 可产生 1 个、1 1/2 个或 2 个停止位

- 波特率生成(直流到 1Mbit/s)

- 错误启动位检测

- ٠ 完成状态报告功能

- 双向数据总线和控制总线的三态输出 TTL 驱动能力

- 线路中断生成和检测

- 内部诊断功能:

- 通信链路故障隔离的环回控制

- 中断、奇偶校验、溢出和帧错误仿真

- 完全优先化的中断系统控制

- 调制解调器控制功能(CTS、RTS、DSR、DTR、 RI和 DCD)

## 2 说明

TL16C550C 和 TL16C550CI 是 TL16C550B 异步通信 元件 (ACE) 的功能升级型号,而 TL16C550B 又是 TL16C450 的功能升级型号。TL16C550C 和 TL16C550CI 上电时在功能上与 TL16C450 等效 (字 符模式或 TL16C450 模式),并像 TL16C550B 一样 可以置于备用 FIFO 模式。这通过缓冲接收和发送的字 符来减轻 CPU 的过多软件开销。接收器和发送器 FIFO 能够存储多达 16 个字节,包括接收器 FIFO 每 字节 3 个额外的错误状态位。在 FIFO 模式下,器件具 有一个可选的自动流控制功能,此功能可以通过使用 RTS 输出和 CTS 输入信号自动控制串行数据流来大大 减少软件过载并提高系统效率。

TL16C550C 和 TL16C550CI 对从外设或调制解调器接 收到的数据执行串行至并行转换,并对从 CPU 接收到 的数据执行并行至串行转换。CPU 可以随时读取 ACE 状态。ACE 包括完整的调制解调器控制功能和一个处 理器中断系统,该系统可以进行定制以更大限度地减少 通信链路的软件管理。

TL16C550C 和 TL16C550CI ACE 都包含一个可编程 波特率发生器,能够对参考时钟进行1至65535分 频,并为内部发送器逻辑生成一个 16× 参考时钟。所 含的配置可以将此 16× 时钟用于接收器逻辑。ACE 支 持 1Mbaud 的串行速率(16MHz 输入时钟),因此位 时间为 1 µs, 典型字符时间为 10 µs( 起始位、8 个 数据位、停止位)。

TL16C550C 和 TL16C550CI 上的其中两个 TL16C450 端子功能已更改为  $\overline{\mathsf{TXRDY}}$  和  $\overline{\mathsf{RXRDY}}$ , 它们用于为 DMA 控制器提供信号。

# **Table of Contents**

| 1 特性                                                 | 1              |

|------------------------------------------------------|----------------|

| 2 说明                                                 |                |

| 3 Revision History                                   |                |

| 4 Pin Configuration and Functions                    |                |

| 5 Specifications                                     |                |

| 5.1 Absolute Maximum Ratings                         |                |

| 5.2 Recommended Operating Conditions (Low            |                |

| Voltage - 3.3 nominal)                               | <mark>6</mark> |

| 5.3 Recommended Operating Conditions (Standard       |                |

| Voltage - 5 V nominal)                               | 7              |

| 5.4 Thermal Information                              | 7              |

| 5.5 Electrical Characteristics (Low Voltage - 3.3 V  |                |

| nominal)                                             | 8              |

| 5.6 Electrical Characteristics (Standard Voltage - 5 |                |

| V nominal)                                           |                |

| 5.7 System Timing Requirements                       | 9              |

| 5.8 System Switching Characteristics                 |                |

| 5.9 Baud Generator Switching Characteristics         |                |

| 5.10 Receiver Switching Characteristics              |                |

| 5.11 Transmitter Switching Characteristics           | 11             |

|    | 5.12 Modem Control Switching Characteristics | 11   |

|----|----------------------------------------------|------|

| 6  | Parameter Measurement Information            |      |

|    | Detailed Description                         |      |

| '  | 7.1 Autoflow Control (see 图 7-1)             |      |

|    |                                              |      |

|    | 7.2 Auto-RTS (see 图 7-1)                     |      |

|    | 7.3 Auto-CTS (see 图 7-1)                     |      |

|    | 7.4 Enabling Autoflow Control and Auto-CTS   | 20   |

|    | 7.5 Auto-CTS and Auto-RTS Functional Timing  | . 21 |

|    | 7.6 Functional Block Diagram                 |      |

|    | 7.7 Principles of Operation                  | .22  |

| 8  | Application Information                      | 34   |

|    | Device and Documentation Support             |      |

| •  | 9.1 接收文档更新通知                                 |      |

|    | 9.2 支持资源                                     |      |

|    | 9.3 Trademarks                               | .36  |

|    | 9.4 静电放电警告                                   |      |

|    | 9.5 术语表                                      |      |

| 1( | 0 Mechanical, Packaging, and Orderable       |      |

|    | Information                                  | . 37 |

**3 Revision History** 注:以前版本的页码可能与当前版本的页码不同

| C | hanges from Revision H (January 2006) to Revision I (March 2021) | Page |

|---|------------------------------------------------------------------|------|

| • | 更新了数据表格式                                                         | 1    |

| • | Added the Pin Configuration and Functions section                | 3    |

| • | Added the Thermal Information table.                             | 7    |

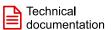

## **4 Pin Configuration and Functions**

#### NC - No internal connection

#### 表 4-1. Pin Functions

|      | TERMIN              | AL    |       | I/O | DESCRIPTION                                                                                                  |  |  |  |  |

|------|---------------------|-------|-------|-----|--------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME | NO.N <sup>(1)</sup> | NO.FN | NO.PT | 1/0 | DESCRIPTION                                                                                                  |  |  |  |  |

| A0   | 28                  | 31    | 28    |     | Register select. A0 -A2 are used during read and write operations to select the                              |  |  |  |  |

| A1   | 27                  | 30    | 27    |     | ACE register to read from or write to. Refer to Table 1 for register addresses and refer to ADS description. |  |  |  |  |

| A2   | 26                  | 29    | 26    |     |                                                                                                              |  |  |  |  |

|         | TEDMIN                        |       |       | 表 4-1. Ⅰ | Pin Functions (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|---------|-------------------------------|-------|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME    | TERMIN<br>NO.N <sup>(1)</sup> | NO.FN | NO.PT | I/O      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

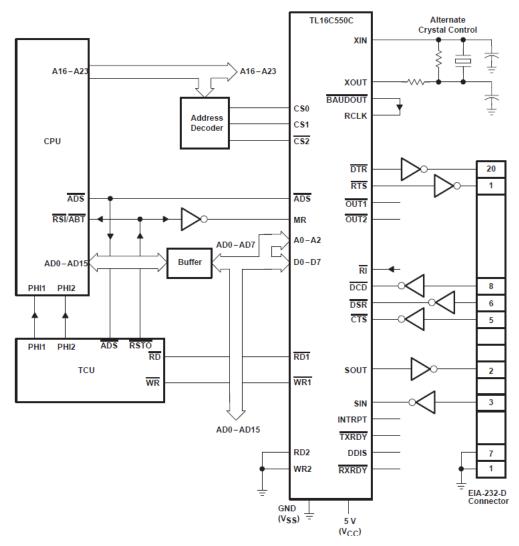

| ADS     | 25                            | 28    | 24    | I        | Address strobe. When ADS is active (low), A0, A1, and A2 and CS0, CS1, and CS2 drive the internal select logic directly; when ADS is high, the register select and chip select signals are held at the logic levels they were in when the low-to-                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

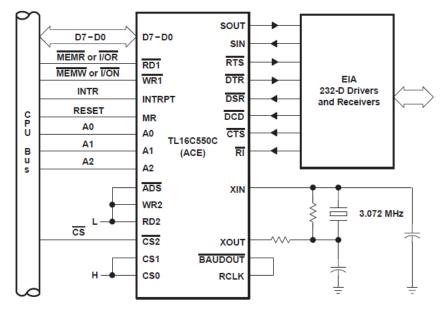

| BAUDOUT | 15                            | 17    | 12    | 0        | high transition of ADS occurred         Baud out. BAUDOUT is a 16 x clock signal for the transmitter section of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|         |                               |       |       |          | ACE. The clock rate is established by the reference oscillator frequency divided by a divisor specified by the baud generator divisor latches. BAUDOUT may also be used for the receiver section by tying this output to RCLK.                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| CS0     | 12                            | 14    | 9     | I        | Chip select. When CS0 and CS1 are high and $\overline{CS2}$ is low, these three inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| CS1     | 13                            | 15    | 10    |          | select the ACE. When any of these inputs are inactive, the ACE remains inactive (refer to $\overline{\text{ADS}}$ description).                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| CS2     | 14                            | 16    | 11    |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| СТS     | 36                            | 40    | 38    | 1        | Clear to send. $\overline{\text{CTS}}$ is a modem status signal. Its condition can be checked by reading bit 4 (CTS) of the modem status register. Bit 0 ( $\triangle$ CTS) of the modem status register indicates that $\overline{\text{CTS}}$ has changed states since the last read from the modem status register. If the modem status interrupt is enabled when $\overline{\text{CTS}}$ changes levels and the auto- $\overline{\text{CTS}}$ mode is not enabled, an interrupt is generated. $\overline{\text{CTS}}$ is also used in the auto- $\overline{\text{CTS}}$ mode to control the transmitter |  |  |  |

| D0      | 1                             | 2     | 43    | I/O      | Data bus. Eight data lines with 3-state outputs provide a bidirectional path for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| D1      | 2                             | 3     | 44    |          | data, control, and status information between the ACE and the CPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| D2      | 3                             | 4     | 45    |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| D3      | 4                             | 5     | 46    |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| D4      | 5                             | 6     | 47    |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| D5      | 6                             | 7     | 2     |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| D6      | 7                             | 8     | 3     |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| D7      | 8                             | 9     | 4     |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| DCD     | 38                            | 42    | 40    | 1        | Data carrier detect. DCD is a modem status signal. Its condition can be checked by reading bit 7 (DCD) of the modem status register. Bit 3 ( $\triangle$ DCD) of the modem status register indicates that DCD has changed states since the last read from the modem status register. If the modem status interrupt is enabled when DCD changes levels, an interrupt is generated                                                                                                                                                                                                                            |  |  |  |

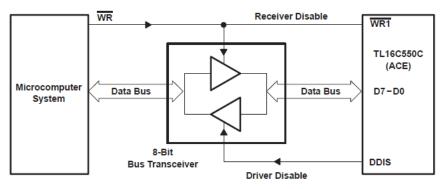

| DDIS    | 23                            | 26    | 22    | 0        | Driver disable. DDIS is active (high) when the CPU is not reading data. When active, DDIS can disable an external transceiver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| DSR     | 37                            | 41    | 39    | I        | Data set ready. $\overline{\text{DSR}}$ is a modem status signal. Its condition can be checked by reading bit 5 (DSR) of the modem status register. Bit 1 ( $\triangle$ DSR) of the modem status register indicates $\overline{\text{DSR}}$ has changed levels since the last read from the modem status register. If the modem status interrupt is enabled when $\overline{\text{DSR}}$ changes levels, an interrupt is generated.                                                                                                                                                                         |  |  |  |

| DTR     | 33                            | 37    | 33    | 0        | Data terminal ready. When active (low), $\overline{\text{DTR}}$ informs a modem or data set that the ACE is ready to establish comunication. $\overline{\text{DTR}}$ is placed in the active level by setting the DTR bit of the modem control register. $\overline{\text{DTR}}$ is placed in the inactive level either as a result of a master reset, during loop mode operation, or clearing the DTR bit.                                                                                                                                                                                                 |  |  |  |

| INTRPT  | 30                            | 33    | 30    | 0        | Interrupt.When active (high), INTRPT informs the CPU that the ACE has an interrupt to be serviced. Four conditions that cause an interrupt to be issued are: a receiver error, received data that is available or timed out (FIFO mode only), an empty transmitter holding register, or an enabled modem status interrupt. INTRPT is reset (deactivated) either when the interrupt is serviced or as a result of a master reset.                                                                                                                                                                            |  |  |  |

| MR      | 35                            | 39    | 35    | I        | Master reset. When active (high), MR clears most ACE registers and sets the levels of various output signals (refer to Table 2).                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| OUT1    | 34                            | 38    | 34    | 0        | Outputs 1 and 2. These are user-designated output terminals that are set to the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| OUT2    | 31                            | 35    | 31    |          | active (low) level by setting respective modem control register (MCR) bits (OUT1 and OUT2). OUT1 and OUT2 are set to inactive the (high) level as a result of master reset, during loop mode operations, or by clearing bit 2 (OUT1) or bit 3 (OUT2) of the MCR.                                                                                                                                                                                                                                                                                                                                            |  |  |  |

## 表 4-1. Pin Functions (continued)

|                 | TERMIN              | IAL      |          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|-----------------|---------------------|----------|----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME            | NO.N <sup>(1)</sup> | NO.FN    | NO.PT    | - I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| RCLK            | 9                   | 10       | 5        | I     | Receiver clock. RCLK is the 16 x baud rate clock for the receiver section of the ACE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| RD1<br>RD2      | 21<br>22            | 24<br>25 | 19<br>20 | I     | Read inputs. When either RD1 or RD2 is active (low or high respectively) while<br>the ACE is selected, the CPU is allowed to read status information or data from<br>a selected ACE register. Only one of these inputs is required for the transfer of<br>data during a read operation; the other input should be tied to its inactive level<br>(i.e., RD2 tied low or RD1 tied high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| RI              | 39                  | 43       | 41       | I     | Ring indicator. $\overline{RI}$ is a modem status signal. Its condition can be checked by reading bit 6 (RI) of the modem status register. Bit 2 (TERI) of the modem status register indicates that $\overline{RI}$ has transitioned from a low to a high level since the last read from the modem status register. If the modem status interrupt is enabled when this transition occurs, an interrupt is generated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| RTS             | 32                  | 36       | 32       | 0     | Request to send. When active, RTS informs the modem or data set that the ACE is ready to receive data. RTS is set to the active level by setting the RTS modem control register bit and is set to the inactive (high) level either as a result of a master reset or during loop mode operations or by clearing bit 1 (RTS) ofthe MCR. In the auto-RTS mode, RTS is set to the inactive level by the receiver threshold control logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

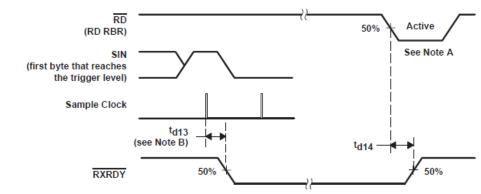

| RXRDY           | 29                  | 32       | 29       | 0     | Receiver ready. Receiver direct memory access (DMA) signalling is available with RXRDY. When operating in the FIFO mode, one of two types of DMA signalling can be selected using the FIFO control register bit 3 (FCR3). When operating in the TL16C450 mode, only DMA mode 0 is allowed. Mode 0 supports single-transfer DMA in which a transfer is made between CPU bus cycles. Mode 1 supports multitransfer DMA in which multiple transfers are made continuously until the receiver FIFO has been emptied. In DMA mode 0 (FCR0 = 0 or FCR0 = 1, FCR3 = 0), when there is at least one character in the receiver FIFO or receiver holding register, RXRDY is active (low). When RXRDY has been active but there are no characters in the FIFO or holding register, RXRDY goes inactive (high).In DMA mode 1 (FCR0 = 1, FCR3 = 1), when the trigger level or the time-out has been reached, RXRDY goes active (low); when it has been active but there are no more characters in the FIFO or holding register, it goes inactive (high). |  |  |  |

| SIN             | 10                  | 11       | 7        | I     | Serial data input. SIN is serial data input from a connected communications device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| SOUT            | 11                  | 13       | 8        | 0     | Serial data output. SOUT is composite serial data output to a connected communication device. SOUT is set to the marking (high) level as a result of master reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| TXRDY           | 24                  | 27       | 23       | 0     | Transmitter ready. Transmitter DMA signalling is available with TXRDY. When operating in the FIFO mode, one of two types of DMA signalling can be selected using FCR3. When operating in the TL16C450 mode, only DMA mode 0 is allowed. Mode 0 supports single-transfer DMA in which a transfer is made between CPU bus cycles. Mode 1 supports multitransfer DMA in which multiple transfers are made continuously until the transmit FIFO has been filled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| V <sub>CC</sub> | 40                  | 44       | 42       |       | 5-V supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| V <sub>SS</sub> | 20                  | 22       | 18       |       | Supply common                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| WR1<br>WR2      | 18<br>19            | 20<br>21 | 16<br>17 | I     | Write inputs. When either $\overline{WR1}$ or WR2 is active (low or high respectively) and while the ACE is selected, the CPU is allowed to write control words or data into a selected ACE register. Only one of these inputs is required to transfer data during a write operation; the other input should be tied to its inactive level (i.e., WR2 tied low or $\overline{WR1}$ tied high).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

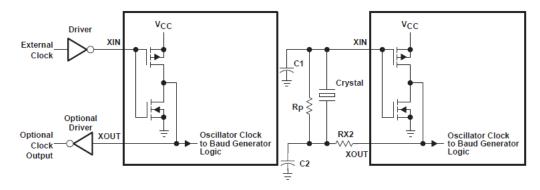

| XIN<br>XOUT     | 16<br>17            | 18<br>19 | 14<br>15 | I/O   | External clock. XIN and XOUT connect the ACE to the main timing reference (clock or crystal).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

(1) The N package is **Not Recommended for New Designs**.

## **5** Specifications

## 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                                                              |                                    | MIN   | MAX | UNIT |

|------------------|--------------------------------------------------------------|------------------------------------|-------|-----|------|

| V <sub>CC</sub>  | Supply voltage range <sup>(3)</sup>                          |                                    | - 0.5 | 7   | V    |

| VI               | Input voltage range at any input                             | - 0.5                              | 7     | V   |      |

| Vo               | Output voltage range                                         |                                    | - 0.5 | 7   | V    |

| -                | Operating free-air temperature range                         | TL16C550C                          | 0     | 70  | °C   |

| T <sub>A</sub>   |                                                              | TL16C550CI                         | - 40  | 85  | °C   |

| T <sub>stg</sub> | Storage temperature                                          |                                    | - 65  | 150 | °C   |

| Т <sub>С</sub>   | Case temperature for 10 seconds                              | FN package                         |       | 260 | °C   |

|                  | Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds | N <sup>(1) (2)</sup> or PT package |       | 260 | °C   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) The N package is Not Recommended for New Designs.

(3) All voltage values are with respect to  $V_{SS}$ .

## 5.2 Recommended Operating Conditions (Low Voltage - 3.3 nominal)

|                                                           | MIN                 | NOM | MAX                 | UNIT |

|-----------------------------------------------------------|---------------------|-----|---------------------|------|

| Supply voltage, V <sub>CC</sub>                           | 3                   | 3.3 | 3.6                 | V    |

| Input voltage, V <sub>I</sub>                             | 0                   |     | V <sub>CC</sub>     | V    |

| High-level input voltage, V <sub>IH</sub> <sup>(1)</sup>  | 0.7 V <sub>CC</sub> |     |                     | V    |

| Low-level input voltage, V <sub>IL</sub> <sup>(1)</sup>   |                     |     | 0.3 V <sub>CC</sub> | V    |

| Output voltage, V <sub>O</sub> <sup>(2)</sup>             | 0                   |     | V <sub>CC</sub>     | V    |

| High-level output current, I <sub>OH</sub> (all outputs)  |                     |     | 1.8                 | mA   |

| Low-level output current, I <sub>OL</sub> (all outputs)   |                     |     | 3.2                 | mA   |

| Input capacitance                                         |                     |     | 1                   | pF   |

| Operating free-air temperature, T <sub>A</sub>            | 0                   | 25  | 70                  | °C   |

| Junction temperature range, T <sub>J</sub> <sup>(3)</sup> | 0                   | 25  | 115                 | °C   |

| Oscillator/clock speed                                    |                     |     | 14.9                | MHz  |

(1) Meets TTL levels,  $V_{IHmin}$  = 2 V and  $V_{ILmax}$  = 0.8 V on nonhysteresis inputs.

(2) Applies for external output buffers.

(3) These junction temperatures reflect simulated conditions. Absolute maximum junction temperature is 150°C. The customer is responsible for verifying junction temperature.

## 5.3 Recommended Operating Conditions (Standard Voltage - 5 V nominal)

|                                                        | <u> </u>   | MIN                 | NOM | MAX                 | UNIT |  |

|--------------------------------------------------------|------------|---------------------|-----|---------------------|------|--|

| Supply voltage, V <sub>CC</sub>                        |            | 4.75                | 5   | 5.25                | V    |  |

| Input voltage, V <sub>I</sub>                          |            | 0                   |     | V <sub>CC</sub>     | V    |  |

| ligh-level input voltage, V <sub>IH</sub>              | Except XIN | 2                   |     |                     | V    |  |

|                                                        | XIN        | 0.7 V <sub>CC</sub> |     |                     | v    |  |

| Low-level input voltage, V <sub>IL</sub>               | Except XIN |                     |     | 0.8                 | V    |  |

|                                                        | XIN        |                     |     | 0.3 V <sub>CC</sub> | v    |  |

| Output voltage, V <sub>O</sub> <sup>(1)</sup>          |            | 0                   |     | V <sub>CC</sub>     | V    |  |

| High-level output current, I <sub>OH</sub> (all output | ts)        |                     |     | 4                   | mA   |  |

| Low-level output current, I <sub>OL</sub> (all output  | s)         |                     |     | 4                   | mA   |  |

| Input capacitance                                      |            |                     |     | 1                   | pF   |  |

| Operating free-air temperature, T <sub>A</sub>         |            | 0                   | 25  | 70                  | °C   |  |

| Junction temperature range, $T_{J}^{(2)}$              |            | 0                   | 25  | 115                 | °C   |  |

| Oscillator/clock speed                                 |            |                     |     | 16                  | MHz  |  |

Applies for external output buffers.

(1) (2) These junction temperatures reflect simulated conditions. Absolute maximum junction temperature is 150°C. The customer is responsible for verifying junction temperature.

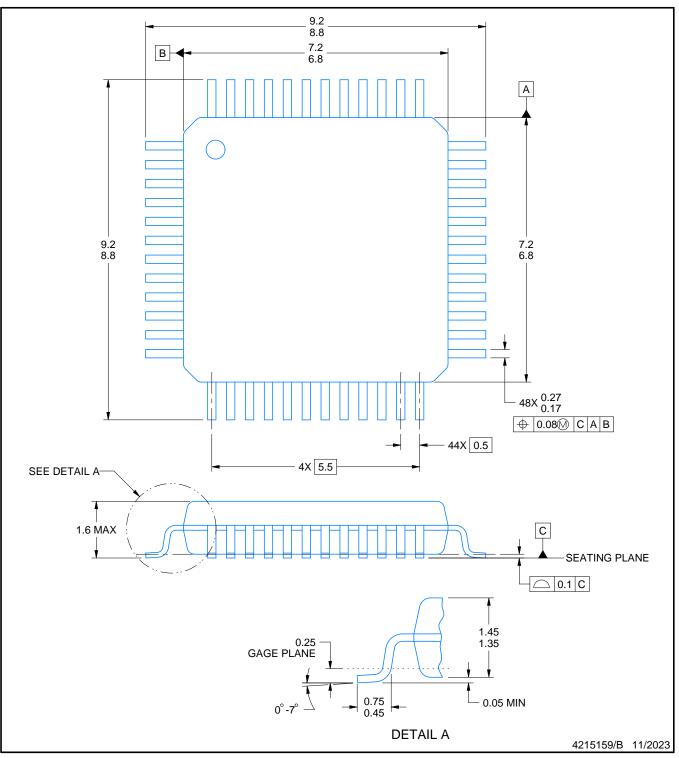

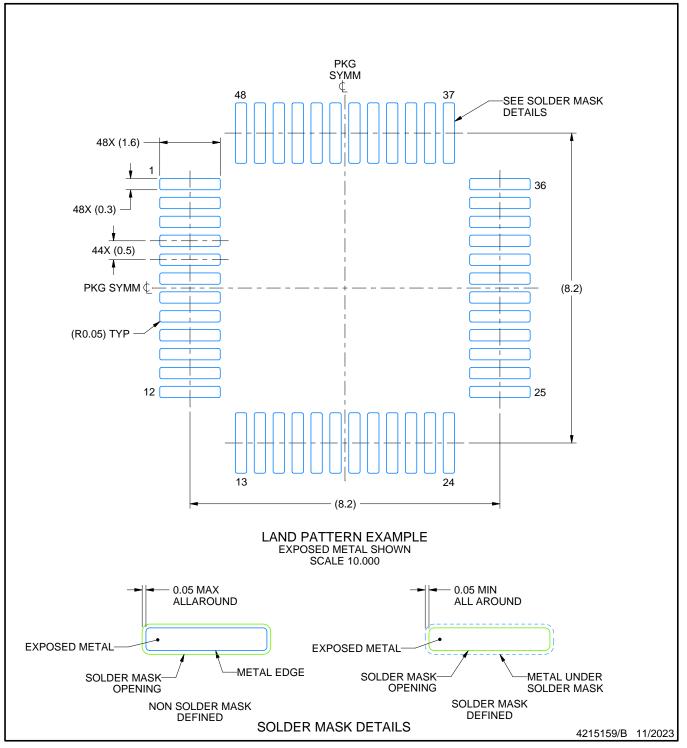

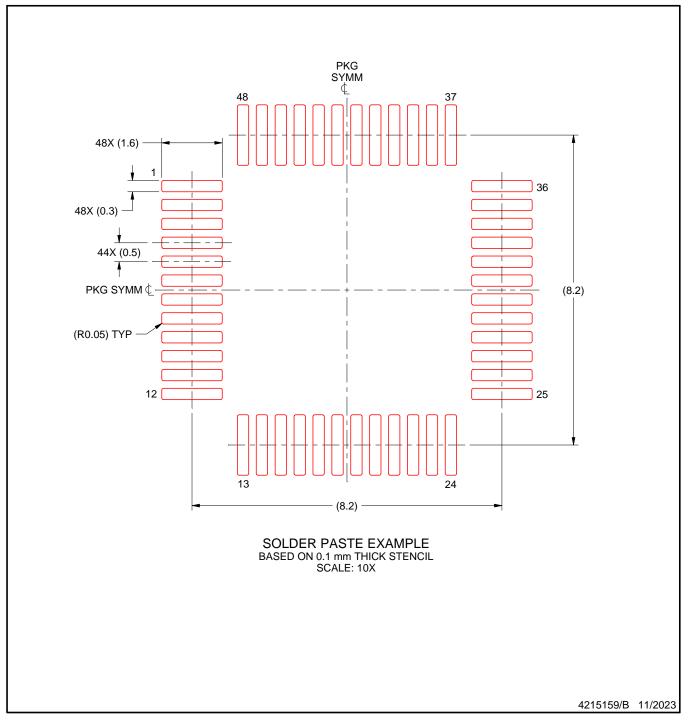

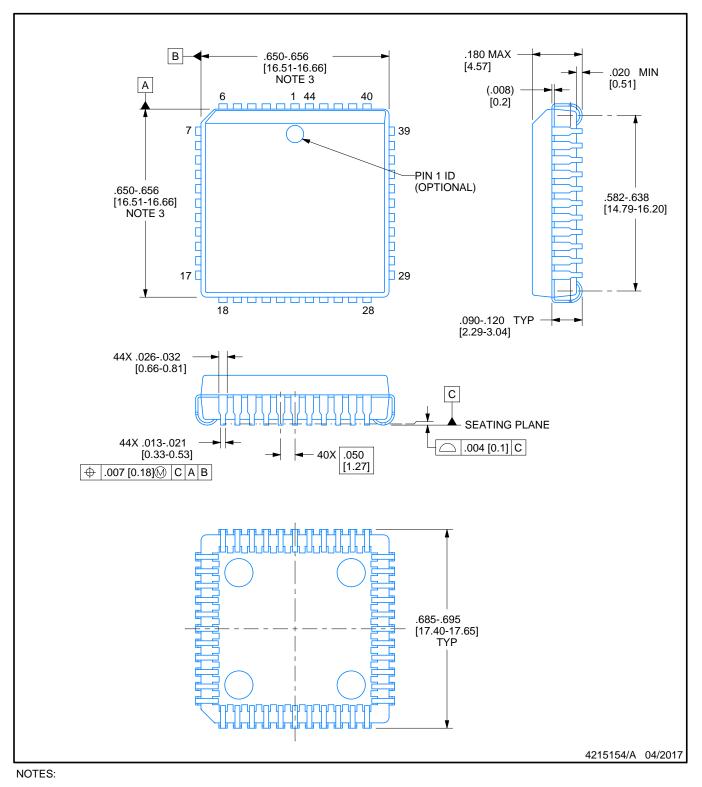

### **5.4 Thermal Information**

|                        |                                              | TL16C550C | TL16C550C | TL16C550C |      |

|------------------------|----------------------------------------------|-----------|-----------|-----------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | РТ        | PFB       | FN        | UNIT |

|                        |                                              | 48 PINS   | 48 PINS   | 44 PINS   |      |

| R <sub>0 JA</sub>      | Junction-to-ambient thermal resistance       | 72.5      | 73.6      | 62.4      | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 31.0      | 26.3      | 37.2      | °C/W |

| R <sub>0 JB</sub>      | Junction-to-board thermal resistance         | 36.2      | 37.2      | 39.1      | °C/W |

| ΨJT                    | Junction-to-top characterization parameter   | 4.4       | 1.9       | 19.4      | °C/W |

| <sup>ψ</sup> JB        | Junction-to-board characterization parameter | 36.0      | 37.0      | 38.7      | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 5.5 Electrical Characteristics (Low Voltage - 3.3 V nominal)

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                                | PARAMETER                              | TEST CO                                                                                                                                       | NDITIONS                                                          | MIN | TYP <sup>(1)</sup> | MAX  | UNIT |

|--------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----|--------------------|------|------|

| V <sub>OH</sub> <sup>(2)</sup> | High-level output voltage              | I <sub>OH</sub> = - 1 mA                                                                                                                      |                                                                   | 2.4 |                    |      | V    |

| V <sub>OL</sub> <sup>(2)</sup> | Low-level output voltage               | I <sub>OL</sub> = 1.6 mA                                                                                                                      |                                                                   |     |                    | 0.5  | V    |

| I                              | Input current                          | $V_{CC} = 3.6 V,$<br>$V_{I} = 0 \text{ to } 3.6 V,$                                                                                           | V <sub>SS</sub> = 0,<br>All other terminals floating              |     |                    | 10   | μA   |

| I <sub>OZ</sub>                | High-impedance-state output<br>current | $V_{CC}$ = 3.6 V,<br>$V_{O}$ = 0 to 3.6 V<br>Chip selected in write mode                                                                      | $V_{SS} = 0,$<br>or chip deselect                                 |     |                    | ± 20 | μA   |

| I <sub>CC</sub>                | Supply current                         | V <sub>CC</sub> = 3.6 V,<br>SIN, <u>DSR</u> , <u>DCD</u> , <u>CTS</u> , and<br>RI at 2V,<br>All other inputs at 0.8 V,<br>No load on outputs, | T <sub>A</sub> = 25°C<br>XTAL1 at 4 MHz,<br>Baud rate = 50 kbit/s |     |                    | 8    | mA   |

| C <sub>i(CLK)</sub>            | Clock input capacitance                | V <sub>CC</sub> = 0,                                                                                                                          | V <sub>SS</sub> = 0,                                              |     | 15                 | 20   | pF   |

| C <sub>o(CLK)</sub>            | Clock output capacitance               | f =1 MHz,                                                                                                                                     | T <sub>A</sub> = 25°C                                             |     | 20                 | 30   | pF   |

| Ci                             | Input capacitance                      | All other terminals ground                                                                                                                    | ed                                                                |     | 6                  | 10   | pF   |

| Co                             | Output capacitance                     |                                                                                                                                               |                                                                   |     | 10                 | 20   | pF   |

(1) All typical values are at  $V_{CC}$  = 3.3 V and  $T_A$  = 25°C.

(2) These parameters apply for all outputs except XOUT.

## 5.6 Electrical Characteristics (Standard Voltage - 5 V nominal)

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                                | PARAMETER                              | TEST CO                                                                                                               | NDITIONS                                                          | MIN  | TYP <sup>(1)</sup> | MAX | UNIT |

|--------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------|--------------------|-----|------|

| V <sub>OH</sub> <sup>(2)</sup> | High-level output voltage              | I <sub>OH</sub> = - 1 mA                                                                                              |                                                                   | 2.4  |                    |     | V    |

| V <sub>OL</sub> <sup>(2)</sup> | Low-level output voltage               | I <sub>OL</sub> = 1.6 mA                                                                                              |                                                                   | 0.4  |                    |     | V    |

| lı                             | Input current                          | $V_{CC} = 5.25 V,$<br>$V_{I} = 0 \text{ to } 5.25 V,$                                                                 | V <sub>SS</sub> = 0,<br>All other terminals floating              | 10   |                    |     | μA   |

| I <sub>OZ</sub>                | High-impedance-state output<br>current | $V_{CC}$ = 5.25 V,<br>$V_{O}$ = 0 to 5.25 V,<br>Chip selected in write mode                                           | $V_{SS} = 0,$ or chip deselect                                    | ± 20 |                    |     | μA   |

| I <sub>CC</sub>                | Supply current                         | V <sub>CC</sub> = 5.25 V,<br>SIN, DSR, DCD, CTS, and<br>RI at 2V,<br>All other inputs at0.8 V,<br>No load on outputs, | T <sub>A</sub> = 25°C<br>XTAL1 at 4 MHz,<br>Baud rate = 50 kbit/s | 10   |                    |     | mA   |

| C <sub>i(CLK)</sub>            | Clock input capacitance                | V <sub>CC</sub> = 0,                                                                                                  |                                                                   |      | 15                 | 20  | pF   |

| C <sub>o(CLK)</sub>            | Clock output capacitance               | f =1 MHz,                                                                                                             | V <sub>SS</sub> = 0,                                              |      | 20                 | 30  | pF   |

| Ci                             | Input capacitance                      | All other terminals                                                                                                   | T <sub>A</sub> = 25°C,                                            |      | 6                  | 10  | pF   |

| Co                             | Output capacitance                     | grounded                                                                                                              |                                                                   |      | 10                 | 20  | pF   |

(1) All typical values are at  $V_{CC}$  = 5 V and  $T_A$  = 25°C.

(2) These parameters apply for all outputs except XOUT.

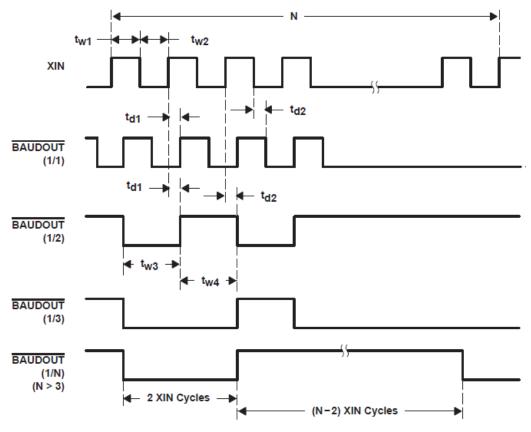

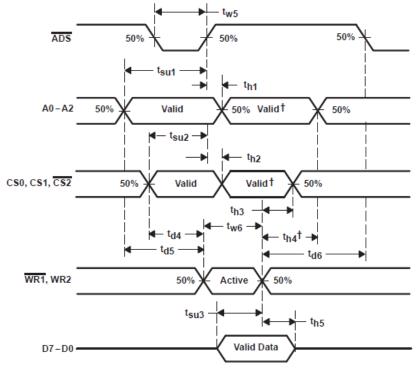

## 5.7 System Timing Requirements

over recommended ranges of supply voltage and operating free-air temperature

|                     |                                                                              | ALT. SYMBOL      | FIGURE          | TEST CONDITIONS        | MIN M | MAX | UNIT |

|---------------------|------------------------------------------------------------------------------|------------------|-----------------|------------------------|-------|-----|------|

| t <sub>cR</sub>     | Cycle time, read (tw7 + td8 + td9)                                           | RC               |                 |                        | 87    |     | ns   |

| t <sub>cW</sub>     | Cycle time, write (tw6 + td5 + td6)                                          | WC               |                 |                        | 87    |     | ns   |

| t <sub>w1</sub>     | Pulse duration, clock high                                                   | t <sub>XH</sub>  | 5               | f = 16 MHz Max,        | 25    |     | ns   |

| t <sub>w2</sub>     | Pulse duration, clock low                                                    | t <sub>XL</sub>  | 5               | $V_{CC} = 5 V$         | 25    |     | 115  |

| t <sub>w5</sub>     | Pulse duration, ADS low                                                      | t <sub>ADS</sub> | 6.7             |                        | 9     |     | ns   |

| t <sub>w6</sub>     | Pulse duration, WR                                                           | t <sub>WR</sub>  | 6               |                        | 40    |     | ns   |

| t <sub>w7</sub>     | Pulse duration, RD                                                           | t <sub>RD</sub>  | 7               |                        | 40    |     | ns   |

| t <sub>w8</sub>     | Pulse duration, MR                                                           | t <sub>MR</sub>  |                 |                        | 1     |     | ns   |

| t <sub>su1</sub>    | Setup time, address valid before ADS †                                       | t <sub>AS</sub>  | 6.7             |                        | 8     |     | ns   |

| t <sub>su2</sub>    | Setup time, CS valid before ADS ↑                                            | t <sub>CS</sub>  | 0.7             |                        | 0     |     | 115  |

| t <sub>su3</sub>    | Setup time, data valid before $\overline{WR1}$ † or $WR2$ ↓                  | t <sub>DS</sub>  | 6               |                        | 15    |     | ns   |

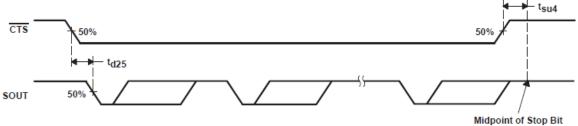

| t <sub>su4</sub>    | Setup time, CTS † before midpoint of stop bit                                |                  | 17              |                        | 10    |     | ns   |

| t <sub>h1</sub>     | Hold time, address low after ADS †                                           | t <sub>AH</sub>  | t <sub>AH</sub> |                        | 0     |     |      |

| t <sub>h2</sub>     | Hold time, CS valid after ADS †                                              | t <sub>CH</sub>  | 6.7             |                        | 0     |     | ns   |

| t <sub>h3</sub>     | Hold time, CS valid after WR1 ↑ or WR2 ↓                                     | t <sub>WCS</sub> | 0               |                        | 10    |     |      |

| t <sub>h4</sub>     | Hold time, address valid after $\overline{WR1}$ † or $WR2$ ↓                 | t <sub>WA</sub>  | - 6             |                        | 10    |     | ns   |

| t <sub>h5</sub>     | Hold time, data valid after WR1 ↑ or WR2 ↓                                   | t <sub>DH</sub>  | 6               |                        | 5     |     | ns   |

| t <sub>h6</sub>     | Hold time, chip select valid after $\overline{\text{RD1}}$ † or RD2 ↓        | t <sub>RCS</sub> | 7               |                        | 10    |     | ns   |

| t <sub>h7</sub>     | Hold time, address valid after $\overline{\text{RD1}}$ † or RD2 $\downarrow$ | t <sub>RA</sub>  | 7               |                        | 20    |     | ns   |

| t <sub>d4</sub> (1) | Delay time, CS valid before WR1 ↓ or WR2 ↑                                   | t <sub>CSW</sub> |                 |                        |       |     |      |

| t <sub>d5</sub> (1) | Delay time, address valid before WR1 ↓ or WR2<br>↑                           | t <sub>AW</sub>  | 6               |                        | 7     |     | ns   |

| t <sub>d6</sub> (1) | Delay time, write cycle, $\overline{WR1}$ † or WR2 ↓ to $\overline{ADS}$ ↓   | t <sub>WC</sub>  | 6               |                        | 40    |     | ns   |

| t <sub>d7</sub> (1) | Delay time, CS valid to RD1 ↓ or RD2 ↑                                       | t <sub>CSR</sub> | 7               |                        | 7     |     |      |

| t <sub>d8</sub> (1) | Delay time, address valid to $\overline{\text{RD1}} \downarrow$ or RD2 †     | t <sub>AR</sub>  | 7               |                        | 7     |     | ns   |

| t <sub>d9</sub>     | Delay time, read cycle, RD1 ↑ or RD2 ↓ to ADS<br>↓                           | t <sub>RC</sub>  | 7               |                        | 40    |     | ns   |

| t <sub>d10</sub>    | Delay time, RD1 ↓ or RD2 ↑ to data valid                                     | t <sub>RVD</sub> | 7               | C <sub>L</sub> = 75 pF |       | 45  | ns   |

| t <sub>d11</sub>    | Delay time, $\overline{RD1}$ ↑ or RD2 ↓ to floating data                     | t <sub>HZ</sub>  | 7               | C <sub>L</sub> = 75 pF |       | 20  | ns   |

(1) Only applies when ADS is low.

## 5.8 System Switching Characteristics

over recommended ranges of supply voltage and operating free-air temperature<sup>(1)</sup>

| PARAMETER           |                                                                                                               | ALT. SYMBOL      | FIGURE | TEST CONDITIONS        | MIN | MAX | UNIT |

|---------------------|---------------------------------------------------------------------------------------------------------------|------------------|--------|------------------------|-----|-----|------|

| t <sub>dis(R)</sub> | Disable time, $\overline{RD1} \downarrow \uparrow$ or $RD2 \uparrow \downarrow$ to DDIS $\uparrow \downarrow$ | t <sub>RDD</sub> | 7      | C <sub>L</sub> = 75 pF | 20  |     | ns   |

(1) Charge and discharge times are determined by  $V_{OL}$ ,  $V_{OH}$ , and external loading.

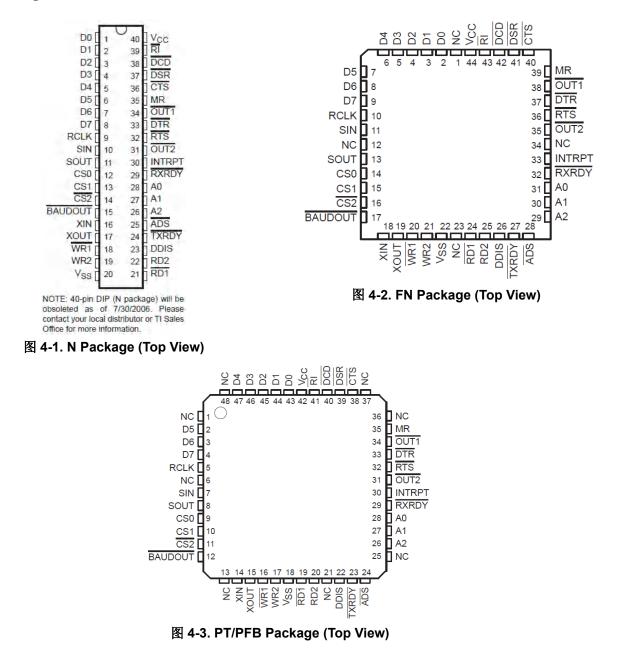

## **5.9 Baud Generator Switching Characteristics**

over recommended ranges of supply voltage and operating free-air temperature,  $C_L$  = 75 pF

|                 | PARAMETER                        | ALT. SYMBOL      | FIGURE | TEST CONDITIONS       | MIN | MAX | UNIT |

|-----------------|----------------------------------|------------------|--------|-----------------------|-----|-----|------|

| t <sub>w3</sub> | Pulse duration, BAUDOUT low      | t <sub>LW</sub>  | 5      | f = 16 MHz, CLK ÷ 2,  | 50  |     | ns   |

| t <sub>w4</sub> | Pulse duration, BAUDOUT high     | t <sub>HW</sub>  | 5      | V <sub>CC</sub> = 5 V | 50  |     | 115  |

| t <sub>d1</sub> | Delay time, XIN ↑ to BAUDOUT ↑   | t <sub>BLD</sub> | 5      |                       |     | 45  | ns   |

| t <sub>d2</sub> | Delay time, XIN ↑ ↓ to BAUDOUT ↓ | t <sub>BHD</sub> | 5      |                       |     | 45  | ns   |

### 5.10 Receiver Switching Characteristics

over recommended ranges of supply voltage and operating free-air temperature<sup>(1)</sup>

|                  | PARAMETER                                                                      | ALT. SYMBOL       | FIGURE           | TEST CONDITIONS        | MIN | MAX | UNIT          |

|------------------|--------------------------------------------------------------------------------|-------------------|------------------|------------------------|-----|-----|---------------|

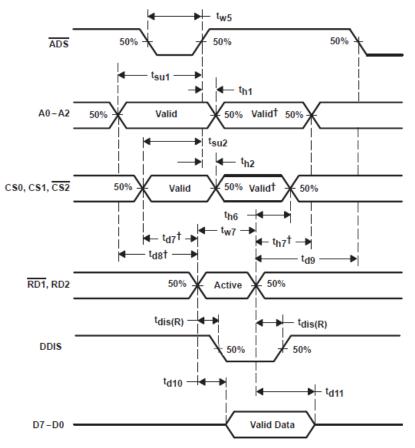

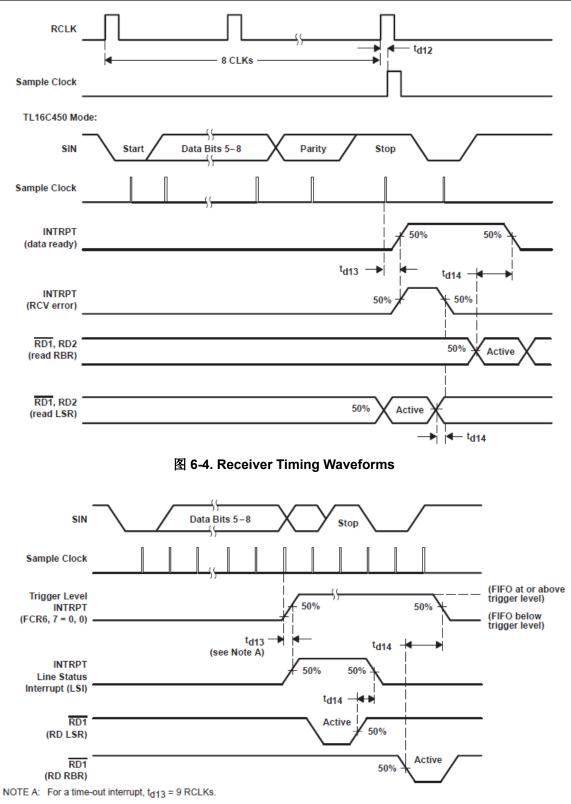

| t <sub>d12</sub> | Delay time, RCLK to sample                                                     | t <sub>SCD</sub>  | 8                |                        |     | 10  | ns            |

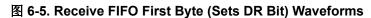

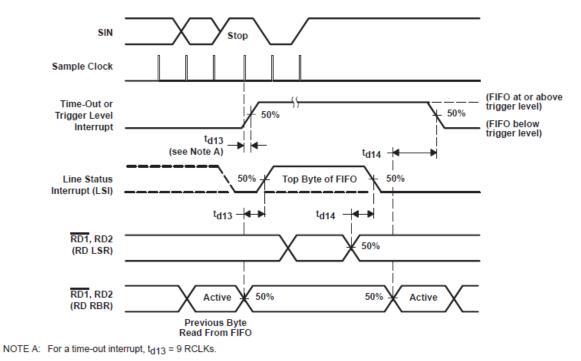

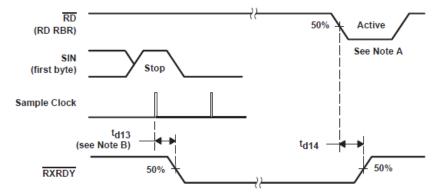

| t <sub>d13</sub> | Delay time, stop to set INTRPT or read RBR to LSI interrupt or stop to RXRDY ↓ | t <sub>SINT</sub> | 8, 9, 10, 11, 12 |                        |     | 1   | RCLK<br>cycle |

| t <sub>d14</sub> | Delay time, read RBR/LSR to reset INTRPT                                       | t <sub>RINT</sub> | 8, 9, 10, 11, 12 | C <sub>L</sub> = 75 pF |     | 70  | ns            |

(1) In the FIFO mode, the read cycle (RC) = 425 ns (min) between reads of the receive FIFO and the status registers (interrupt identification register or line status register).

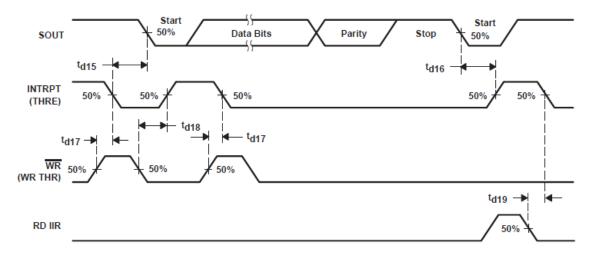

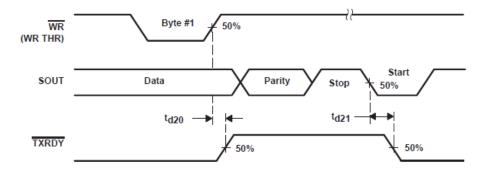

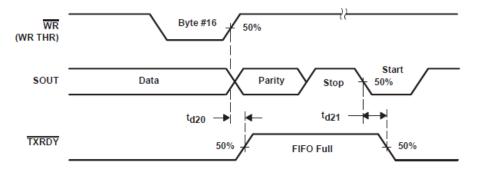

## 5.11 Transmitter Switching Characteristics

over recommended ranges of supply voltage and operating free-air temperature

|                  | PARAMETER                                                                  | ALT. SYMBOL      | FIGURE | TEST CONDITIONS        | MIN | MAX | UNIT              |

|------------------|----------------------------------------------------------------------------|------------------|--------|------------------------|-----|-----|-------------------|

| t <sub>d15</sub> | Delay time, initial write to transmit start                                | t <sub>IRS</sub> | 13     |                        | 8   | 24  | baudout<br>cycles |

| t <sub>d16</sub> | t <sub>d16</sub> Delay time, start to INTRPT                               |                  | 13     |                        | 8   | 10  | baudout<br>cycles |

| t <sub>d17</sub> | Delay time, $\overline{WR}$ (WR THR) to reset INTRPT                       | t <sub>HR</sub>  | 13     | C <sub>L</sub> = 75 pF |     | 50  | ns                |

| t <sub>d18</sub> | Delay time, initial write to INTRPT (THRE <sup>(1)</sup> )                 | t <sub>SI</sub>  | 13     |                        | 16  | 34  | baudout<br>cycles |

| t <sub>d19</sub> | Delay time, read IIR <sup>(1)</sup> to reset INTRPT (THRE <sup>(1)</sup> ) | t <sub>IR</sub>  | 13     | C <sub>L</sub> = 75 pF |     | 35  | ns                |

| t <sub>d20</sub> | Delay time, write to TXRDY inactive                                        | t <sub>WXI</sub> | 14, 15 | C <sub>L</sub> = 75 pF |     | 35  | ns                |

| t <sub>21</sub>  | Delay time, start to TXRDY active                                          | t <sub>SXA</sub> | 14, 15 | C <sub>L</sub> = 75 pF |     | 9   | baudout<br>cycles |

(1) THRE = transmitter holding register empty; IIR = interrupt identification register.

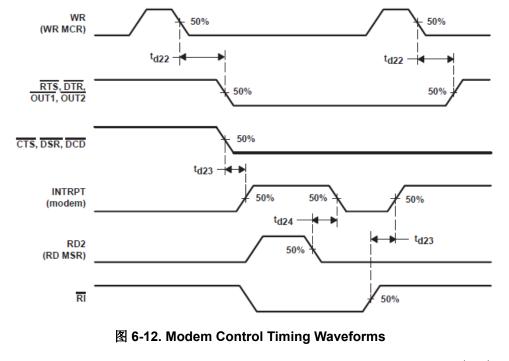

## 5.12 Modem Control Switching Characteristics

|                  | PARAMETER                                                                          | ALT. SYMBOL      | FIGURE | MIN | MAX | UNIT              |

|------------------|------------------------------------------------------------------------------------|------------------|--------|-----|-----|-------------------|

| t <sub>d22</sub> | Delay time, WR MCR to output                                                       | t <sub>MDO</sub> | 16     |     | 50  | ns                |

| t <sub>d23</sub> | Delay time, modem interrupt to set INTRPT                                          | t <sub>SIM</sub> | 16     |     | 35  | ns                |

| t <sub>d24</sub> | Delay time, RD MSR to reset INTRPT                                                 | t <sub>RIM</sub> | 16     |     | 40  | ns                |

| t <sub>d25</sub> | Delay time, CTS low to SOUT ↓                                                      |                  | 17     |     | 24  | baudout<br>cycles |

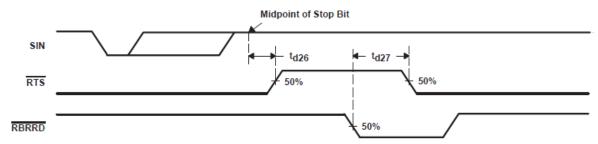

| t <sub>d26</sub> | Delay time, RCV threshold byte to $\overline{RTS}$ †                               |                  | 18     |     | 2   | baudout<br>cycles |

| t <sub>d27</sub> | Delay time, read of last byte in receive FIFO to $\overline{\text{RTS}}\downarrow$ |                  | 18     |     | 2   | baudout<br>cycles |

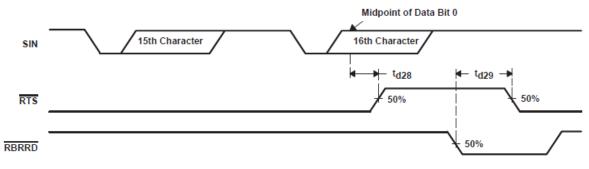

| t <sub>d28</sub> | Delay time, first data bit of 16th character to $\overline{RTS}$ †                 |                  | 19     |     | 2   | baudout<br>cycles |

| t <sub>d29</sub> | Delay time, RBRRD low to RTS↓                                                      |                  | 19     |     | 2   | baudout<br>cycles |

over recommended ranges of supply voltage and operating free-air temperature,  $C_1 = 75 \text{ pF}$

## **6** Parameter Measurement Information

图 6-1. Baud Generator Timing Waveforms

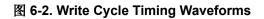

<sup>†</sup> Applicable only when  $\overline{\text{ADS}}$  is low

<sup>†</sup> Applicable only when ADS is low

### 图 6-3. Read Cycle Timing Waveforms

# 图 6-6. Receive FIFO Bytes Other Than the First Byte (DR Internal Bit Already Set) Waveforms

NOTE A: This is the reading of the last byte in the FIFO.

#### 图 6-7. Receiver Ready (RXRDY) Waveforms, FCR0 = 0 or FCR0 = 1 and FCR3 = 0 (Mode 0)

NOTES: A. This is the reading of the last byte in the FIFO. B. For a time-out interrupt,  $t_{d13}$  = 9 RCLKs.

图 6-9. Transmitter Timing Waveforms

图 6-10. Transmitter Ready (TXRDY) Waveforms, FCR0 = 0 or FCR0 = 1 and FCR3 = 0 (Mode 0)

图 6-13. CTS and SOUT Autoflow Control Timing (Start and Stop) Waveforms

图 6-15. Auto-RTS Timing for RCV Threshold of 14 Waveforms

## 7 Detailed Description

## 7.1 Autoflow Control (see 7-1)

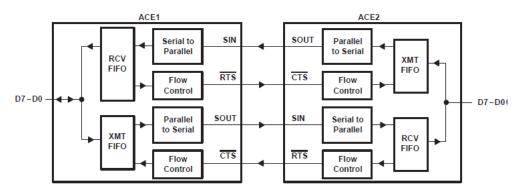

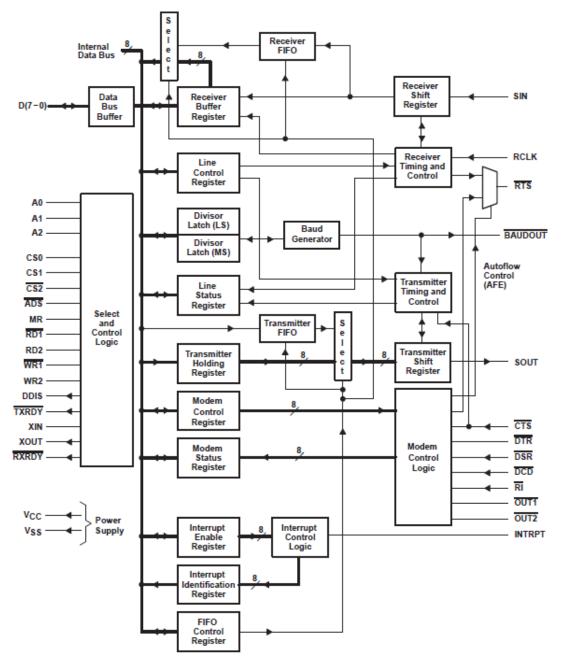

Autoflow control is comprised of auto-CTS and auto-RTS. With auto-CTS, the CTS input must be active before the transmitter FIFO can emit data. With auto-RTS, RTS becomes active when the receiver needs more data and notifies the sending serial device. When RTS is connected to CTS, data transmission does not occur unless the receiver FIFO has space for the data; thus, overrun errors are eliminated using ACE1 and ACE2 from a TLC16C550C with the autoflow control enabled. If not, overrun errors occur when the transmit data rate exceeds the receiver FIFO read latency.

图 7-1. Autoflow Control (Auto-RTS and Auto-CTS) Example

## 7.2 Auto-RTS (see 🖄 7-1)

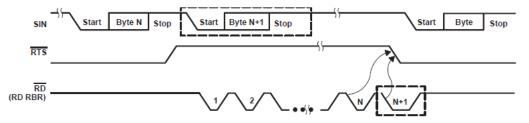

Auto- $\overline{\text{RTS}}$  data flow control originates in the receiver timing and control block (see  $\ddagger$  7.6) and is linked to the programmed receiver FIFO trigger level. When the receiver FIFO level reaches a trigger level of 1, 4, or 8 (see  $\boxed{8}$  7-3),  $\overline{\text{RTS}}$  is deasserted. With trigger levels of 1, 4, and 8, the sending ACE may send an additional byte after the trigger level is reached (assuming the sending ACE has another byte to send) because it may not recognize the deassertion of  $\overline{\text{RTS}}$  until after it has begun sending the additional byte.  $\overline{\text{RTS}}$  is automatically reasserted once the RCV FIFO is emptied by reading the receiver buffer register.

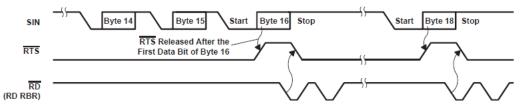

When the trigger level is 14 (see Figure 4), RTS is deasserted after the first data bit of the 16th character is present on the SIN line. RTS is reasserted when the RCV FIFO has at least one available byte space.

## 7.3 Auto-CTS (see 🖄 7-1)

The transmitter circuitry checks  $\overline{\text{CTS}}$  before sending the next data byte. When  $\overline{\text{CTS}}$  is active, it sends the next byte. To stop the transmitter from sending the following byte,  $\overline{\text{CTS}}$  must be released before the middle of the last stop bit that is currently being sent (see  $\boxed{8}$  7-2). The auto- $\overline{\text{CTS}}$  function reduces interrupts to the host system. When flow control is enabled,  $\overline{\text{CTS}}$  level changes do not trigger host interrupts because the device automatically controls its own transmitter. Without auto- $\overline{\text{CTS}}$ , the transmitter sends any data present in the transmit FIFO and a receiver overrun error may result

## 7.4 Enabling Autoflow Control and Auto-CTS

Autoflow control is enabled by setting modem control register bits 5 (autoflow enable or AFE) and 1 (RTS) to a 1. Autoflow incorporates both auto- $\overline{\text{RTS}}$  and auto- $\overline{\text{CTS}}$ . When only auto- $\overline{\text{CTS}}$  is desired, bit 1 in the modem control register should be cleared (this assumes that a control signal is driving  $\overline{\text{CTS}}$ ).

## 7.5 Auto-CTS and Auto-RTS Functional Timing

图 7-2. CTS Functional Timing Waveforms

#### NOTES:

- 1. When  $\overline{\text{CTS}}$  is low, the transmitter keeps sending serial data out.

- 2. If CTS goes high before the middle of the last stop bit of the current byte, the transmitter finishes sending the current byte but it does not send the next byte.

- 3. When CTS goes from high to low, the transmitter begins sending data again.

The receiver FIFO trigger level can be set to 1, 4, 8, or 14 bytes. These are described in 🛽 7-3 and 🖉 7-4.

图 7-3. RTS Functional Timing Waveforms, RCV FIFO Trigger Level = 1, 4, or 8 Bytes

#### NOTES:

- 1. N = RCV FIFO trigger level (1, 4, or 8 bytes)

- 2. The two blocks in dashed lines cover the case where an additional byte is sent as described in the preceding auto-RTS section.

图 7-4. RTS Functional Timing Waveforms, RCV FIFO Trigger Level = 14 Bytes

#### NOTES:

- 1. RTS is deasserted when the receiver receives the first data bit of the sixteenth byte. The receive FIFO is full after finishing the sixteenth byte.

- 2. RTS is asserted again when there is at least one byte of space available and no incoming byte is in processing or there is more than one byte of space available.

- 3. When the receive FIFO is full, the first receive buffer register read reasserts RTS.

## 7.6 Functional Block Diagram

#### 7.7 Principles of Operation

#### 表 7-1. Register Selection

| DLAB <sup>(1)</sup> | A2 | A1 | A0                                              | REGISTER                                                     |

|---------------------|----|----|-------------------------------------------------|--------------------------------------------------------------|

| 0                   | L  | L  | L                                               | Receiver buffer (read), transmitter holding register (write) |

| 0                   | L  | L  | H Interrupt enable register                     |                                                              |

| X                   | L  | Н  | L Interrupt identification register (read only) |                                                              |

| X                   | L  | Н  | L FIFO control register (write)                 |                                                              |

| X                   | L  | Н  | Н                                               | Line control register                                        |

| Х                   | Н  | L  | L                                               | Modem control register                                       |

| Х                   | Н  | L  | Н                                               | Line status register                                         |

Copyright © 2023 Texas Instruments Incorporated

|                     |    | 1  | c /-I. Regis |                       |

|---------------------|----|----|--------------|-----------------------|

| DLAB <sup>(1)</sup> | A2 | A1 | A0           | REGISTER              |

| Х                   | Н  | Н  | L            | Modem status register |

| Х                   | Н  | Н  | Н            | Scratch register      |

| 1                   | L  | L  | L            | Divisor latch (LSB)   |

| 1                   | L  | L  | Н            | Divisor latch (MSB)   |

## 表 7-1 Register Selection (continued)

The divisor latch access bit (DLAB) is the most significant bit of the line control register. The DLAB signal is controlled by writing to this (1) bit location (see Table 4).

| REGISTER/SIGNAL                             | RESET CONTROL         | RESET STATE                                                                              |  |  |  |

|---------------------------------------------|-----------------------|------------------------------------------------------------------------------------------|--|--|--|

| Interrupt enable register                   | Master reset          | All bits cleared (0 - 3 forced and 4 - 7 permanent)                                      |  |  |  |

| Interrupt identification register           | Master reset          | Bit 0 is set, bits 1, 2, 3, 6, and 7 are cleared, and bits 4 – 5 are permanently cleared |  |  |  |

| FIFO control register                       | Master reset          | All bits cleared                                                                         |  |  |  |

| Line control register                       | Master reset          | All bits cleared                                                                         |  |  |  |

| Modem control register                      | Master reset          | All bits cleared (6 - 7 permanent)                                                       |  |  |  |

| Line status register                        | Master reset          | Bits 5 and 6 are set; all other bits are cleared                                         |  |  |  |

| Modem status register                       | Master reset          | Bits 0 – 3 are cleared; bits 4 – 7 are input signals                                     |  |  |  |

| SOUT                                        | Master reset          | High                                                                                     |  |  |  |

| INTRPT (receiver error flag)                | Read LSR/MR           | Low                                                                                      |  |  |  |

| INTRPT (received data available)            | Read RBR/MR           | Low                                                                                      |  |  |  |

| INTRPT (transmitter holding register empty) | Read IR/write THR/MR  | Low                                                                                      |  |  |  |

| INTRPT (modem status changes)               | Read MSR/MR           | Low                                                                                      |  |  |  |

| OUT2                                        | Master reset          | High                                                                                     |  |  |  |

| RTS                                         | Master reset          | High                                                                                     |  |  |  |

| DTR                                         | Master reset          | High                                                                                     |  |  |  |

| OUT1                                        | Master reset          | High                                                                                     |  |  |  |

| Scratch register                            | Master reset          | No effect                                                                                |  |  |  |