- ST16C654 Pin Compatible With Additional Enhancements

- Supports Up To 24-MHz Crystal Input Clock (1.5 Mbps)

- Supports Up To 48-MHz Oscillator Input Clock (3 Mbps) for 5-V Operation

- Supports Up To 32-MHz Oscillator Input Clock ( 2 Mbps) for 3.3-V Operation

- 64-Byte Transmit FIFO

- 64-Byte Receive FIFO With Error Flags

- Programmable and Selectable Transmit and Receive FIFO Trigger Levels for DMA and Interrupt Generation

- Programmable Receive FIFO Trigger Levels for Software/Hardware Flow Control

- Software/Hardware Flow Control

- Programmable Xon/Xoff Characters

- Programmable Auto-RTS and Auto-CTS

- Optional Data Flow Resume by Xon Any Character

- DMA Signalling Capability for Both Received and Transmitted Data

- Supports 3.3-V or 5-V Supply

- Characterized for Operation From –40°C to 85°C

- Software Selectable Baud Rate Generator

- Prescalable Provides Additional Divide by 4 Function

- Fast Access 2 Clock Cycle IOR/IOW Pulse Width

- Programmable Sleep Mode

- Programmable Serial Interface Characteristics

- 5. 6. 7. or 8-Bit Characters

- Even, Odd, or No Parity Bit Generation and Detection

- 1, 1.5, or 2 Stop Bit Generation

- False Start Bit Detection

- Complete Status Reporting Capabilities in Both Normal and Sleep Mode

- Line Break Generation and Detection

- Internal Test and Loopback Capabilities

- Fully Prioritized Interrupt System Controls

- Modem Control Functions (CTS, RTS, DSR, DTR, RI, and CD)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

TEXAS INSTRUMENTS

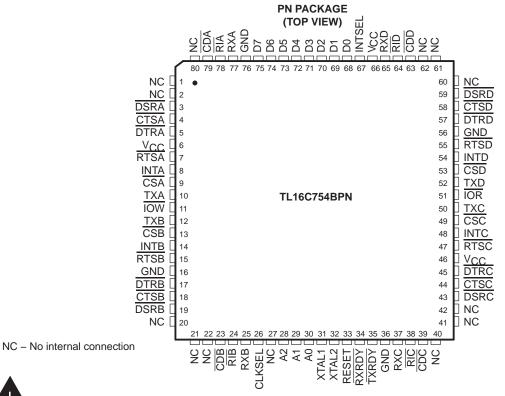

NC - No internal connection

#### description

The TL16C754B is a quad universal asynchronous receiver/transmitter (UART) with 64-byte FIFOs, automatic hardware/software flow control, and data rates up to 3 Mbps. The TL16C754B offers enhanced features. It has a transmission control register (TCR) that stores received FIFO threshold level to start/stop transmission during hardware and software flow control. With the FIFO RDY register, the software gets the status of TXRDY/RXRDY for all four ports in one access. On-chip status registers provide the user with error indications, operational status, and modem interface control. System interrupts may be tailored to meet user requirements. An internal loopback capability allows onboard diagnostics.

The UART transmits data sent to it from the peripheral 8-bit bus on the TX signal and receives characters on the RX signal. Characters can be programmed to be 5, 6, 7, or 8 bits. The UART has a 64-byte receive FIFO and transmit FIFO and can be programmed to interrupt at different trigger levels. The UART generates its own desired baud rate based upon a programmable divisor and its input clock. It can transmit even, odd, or no parity and 1, 1.5, or 2 stop bits. The receiver can detect break, idle or framing errors, FIFO overflow, and parity errors. The transmitter can detect FIFO underflow. The UART also contains a software interface for modem control operations, and software flow control and hardware flow control capabilities.

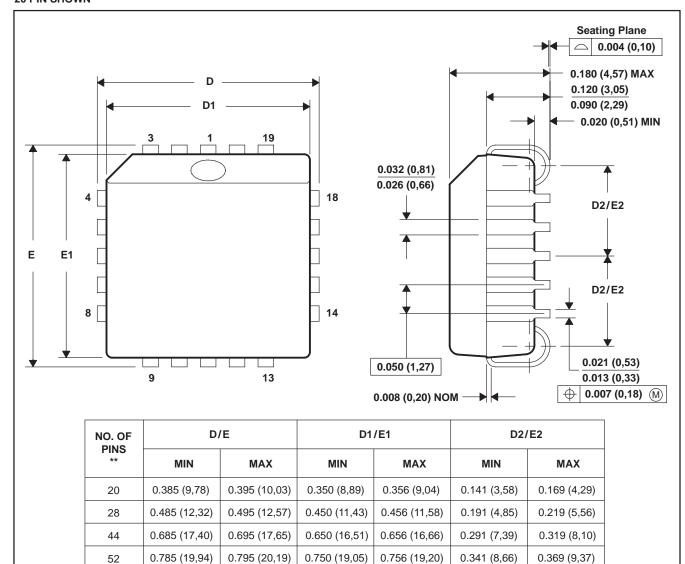

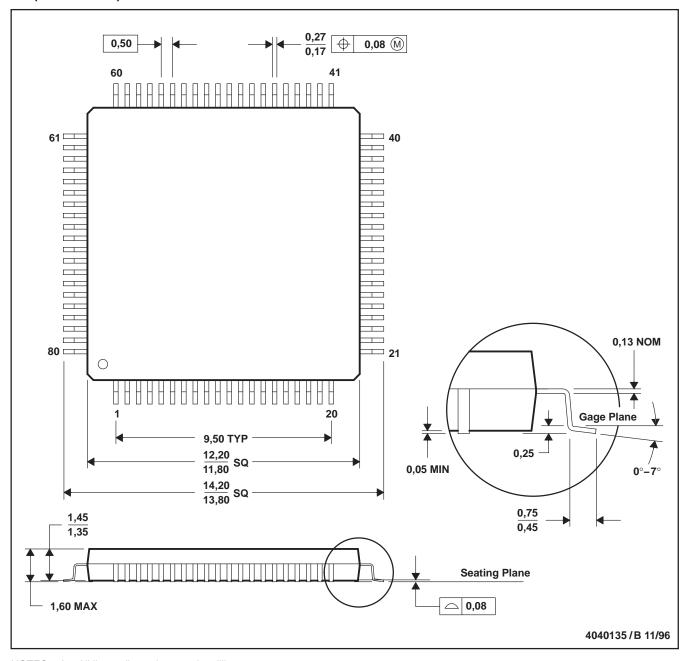

The TL16C754B is available in 80-pin TQFP and 68-pin PLCC packages.

# **Terminal Functions**

| TER                      | MINAL             |                   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------|-------------------|-------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | N                 | 0.                | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| NAME                     | PN                | FN                | 1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A0                       | 30                | 34                | ı   | Address bit 0 select. Internal registers address selection. Refer to Table 7 for Register Address Map.                                                                                                                                                                                                                                                                                                                                                                                                     |

| A1                       | 29                | 33                | ı   | Address bit 1 select. Internal registers address selection. Refer to Table 7 for Register Address Map                                                                                                                                                                                                                                                                                                                                                                                                      |

| A2                       | 28                | 32                | ı   | Address bit 2 select. Internal registers address selection. Refer to Table 7 for Register Address Map                                                                                                                                                                                                                                                                                                                                                                                                      |

| CDA, CDB<br>CDC, CDD     | 79, 23<br>39, 63  | 9, 27<br>43, 61   | I   | Carrier detect (active low). These inputs are associated with individual UART channels A through D. A low on these pins indicates that a carrier has been detected by the modem for that channel.                                                                                                                                                                                                                                                                                                          |

| CLKSEL                   | 26                | 30                | I   | Clock select. CLKSEL selects the divide-by-1 or divide-by-4 prescalable clock. During the reset, a logic 1 (V <sub>CC</sub> ) on CLKSEL selects the divide-by-1 prescaler. A logic 0 (GND) on CLKSEL selects the divide-by-4 prescaler. The value of CLKSEL is latched into MCR[7] at the trailing edge of RESET. A logic 1 (V <sub>CC</sub> ) on CLKSEL will latch a 0 into MCR[7]. A logic 0 (GND) on CLKSEL will latch a 1 into MCR[7]. MCR[7] can be changed after RESET to alter the prescaler value. |

| CSA, CSB<br>CSC, CSD     | 9, 13,<br>49, 53  | 16, 20,<br>50, 54 | I   | Chip select A, B, C, and D (active low). These pins enable data transfers between the user CPU and the TL16C754B for the channel(s) addressed. Individual UART sections (A, B, C, D) are addressed by providing a low on the respective CSA through CSD pin.                                                                                                                                                                                                                                               |

| CTSA, CTSB<br>CTSC, CTSD | 4, 18<br>44, 58   | 11, 25<br>45, 59  | ı   | Clear to send (active low). These inputs are associated with individual UART channels A through D. A low on the CTS pins indicates the modem or data set is ready to accept transmit data from the 754A. Status can be checked by reading MSR bit 4. These pins only affect the transmit and receive operations when auto CTS function is enabled through the enhanced feature register (EFR) bit 7, for hardware flow control operation.                                                                  |

| D0-D2<br>D3-D7           | 68–70,<br>71–75   | 66–68,<br>1–5     | I/O | Data bus (bidirectional). These pins are the eight bit, 3-state data bus for transferring information to or from the controlling CPU. D0 is the least significant bit and the first data bit in a transmit or receive serial data stream.                                                                                                                                                                                                                                                                  |

| DSRA, DSRB<br>DSRC, DSRD | 3, 19<br>43, 59   | 10, 26<br>44, 60  | I   | Data set ready (active low). These inputs are associated with individual UART channels A through D. A low on these pins indicates the modem or data set is powered on and is ready for data exchange with the UART.                                                                                                                                                                                                                                                                                        |

| DTRA, DTRB<br>DTRC, DTRD | 5, 17<br>45, 57   | 12, 24<br>46, 58  | 0   | Data terminal ready (active low). These outputs are associated with individual UART channels A through D. A low on these pins indicates that the 754A is powered on and ready. These pins can be controlled through the modem control register. Writing a 1 to MCR bit 0 sets the DTR output to low, enabling the modem. The output of these pins is high after writing a 0 to MCR bit 0, or after a reset.                                                                                                |

| GND                      | 16, 36,<br>56, 76 | 6, 23,<br>40, 57  | Pwr | Signal and power ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| INTA, INTB<br>INTC, INTD | 8, 14,<br>48, 54  | 15, 21,<br>49, 55 | 0   | Interrupt A, B, C, and D (active high). These pins provide individual channel interrupts, INTA-D. INTA-D are enabled when MCR bit 3 is set to a 1, interrupts are enabled in the interrupt enable register (IER) and when an interrupt condition exists. Interrupt conditions include: receiver errors, available receiver buffer data, transmit buffer empty, or when a modem status flag is detected. INTA-D are in the high-impedance state after reset.                                                |

| INTSEL                   | 67                | 65                | ı   | Interrupt select (active high with internal pulldown). INTSEL can be used in conjunction with MCR bit 3 to enable or disable the 3-state interrupts INTA-D or override MCR bit 3 and force continuous interrupts. Interrupt outputs are enabled continuously by making this pin a 1. Driving this pin low allows MCR bit 3 to control the 3-state interrupt output. In this mode, MCR bit 3 is set to a 1 to enable the 3-state outputs.                                                                   |

| ĪŌR                      | 51                | 52                | I   | Read input (active low strobe). A valid low level on IOR will load the contents of an internal register defined by address bits A0–A2 onto the TL16C754B data bus (D0–D7) for access by an external CPU.                                                                                                                                                                                                                                                                                                   |

| ĪOW                      | 11                | 18                | I   | Write input (active low strobe). A valid low level on $\overline{\text{IOW}}$ will transfer the contents of the data bus (D0–D7) from the external CPU to an internal register that is defined by address bits A0–A2.                                                                                                                                                                                                                                                                                      |

# **Terminal Functions (Continued)**

| TERM                     | INAL             |                  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------|------------------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                     | N(               | 0.               | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| NAME                     | PN               | FN               |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RESET                    | 33               | 37               | _   | Reset. RESET will reset the internal registers and all the outputs. The UART transmitter output and the receiver input will be disabled during reset time. See TL16C754B external reset conditions for initialization details. RESET is an active high input.                                                                                                                                                                                                                                                                      |

| RIA, RIB<br>RIC, RID     | 78, 24<br>38, 64 | 8, 28<br>42, 62  | _   | Ring indicator (active low). These inputs are associated with individual UART channels A through D. A low on these pins indicates the modem has received a ringing signal from the telephone line. A low to high transition on these input pins generates a modem status interrupt, if it is enabled.                                                                                                                                                                                                                              |

| RTSA, RTSB<br>RTSC, RTSD | 7, 15<br>47, 55  | 14, 22<br>48, 56 | 0   | Request to send (active low). These outputs are associated with individual UART channels A through D. A low on the RTS pins indicates the transmitter has data ready and waiting to send. Writing a 1 in the modem control register (MCR bit 1) sets these pins to low, indicating data is available. After a reset, these pins are set to 1. These pins only affects the transmit and receive operation when auto RTS function is enabled through the enhanced feature register (EFR) bit 6, for hardware flow control operation. |

| RXA, RXB<br>RXC, RXD     | 77, 25<br>37, 65 | 7, 29<br>41, 63  | _   | Receive data input. These inputs are associated with individual serial channel data to the 754A. During the local loopback mode, these RX input pins are disabled and TX data is internally connected to the UART RX input internally.                                                                                                                                                                                                                                                                                             |

| RXRDY                    | 34               | 38               | 0   | Receive ready (active low). RXRDY contains the wire-ORed status of all four receive channel FIFOs, RXRDY A–D. It goes low when the trigger level has been reached or a timeout interrupt occurs. It goes high when all RX FIFOs are empty and there is an error in RX FIFO.                                                                                                                                                                                                                                                        |

| TXA, TXB<br>TXC, TXD     | 10, 12<br>50, 52 | 17, 19<br>51, 53 | 0   | Transmit data. These outputs are associated with individual serial transmit channel data from the 754A. During the local loopback mode, the TX input pin is disabled and TX data is internally connected to the UART RX input.                                                                                                                                                                                                                                                                                                     |

| TXRDY                    | 35               | 39               | 0   | Transmit ready (active low). TXRDY contains the wire-ORed status of all four transmit channel FIFOs, TXRDY A–D. It goes low when there are a trigger level number of spares available. It goes high when all four TX buffers are full.                                                                                                                                                                                                                                                                                             |

| VCC                      | 6, 46,<br>66     | 13, 47,<br>64    | Pwr | Power supply inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

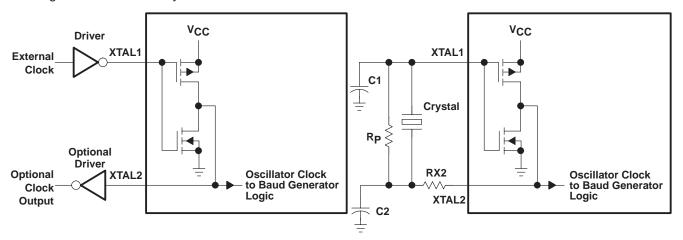

| XTAL1                    | 31               | 35               | I   | Crystal or external clock input. XTAL1 functions as a crystal input or as an external clock input. A crystal can be connected between XTAL1 and XTAL2 to form an internal oscillator circuit (see Figure 10). Alternatively, an external clock can be connected to XTAL1 to provide custom data rates.                                                                                                                                                                                                                             |

| XTAL2                    | 32               | 36               | 0   | Output of the crystal oscillator or buffered clock. See also XTAL1. XTAL2 is used as a crystal oscillator output or buffered clock output.                                                                                                                                                                                                                                                                                                                                                                                         |

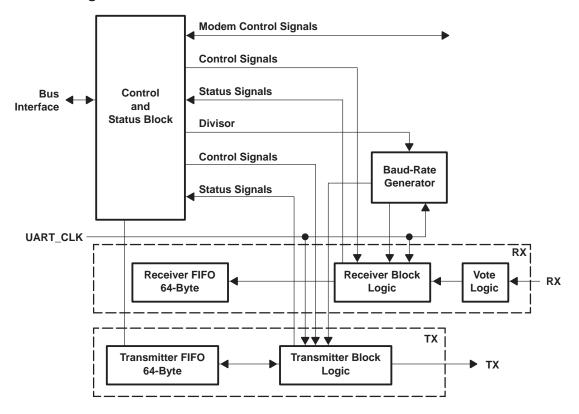

# functional block diagram

NOTE: The Vote logic determines whether the RX data is a logic 1 or 0. It takes three samples of the RX line and uses a majority vote to determine the logic level received. The Vote logic operates on all bits received.

#### functional description

The TL16C754B UART is pin compatible with the TL16C554 and ST16C654 UARTs. It provides more enhanced features. All additional features are provided through a special enhanced feature register.

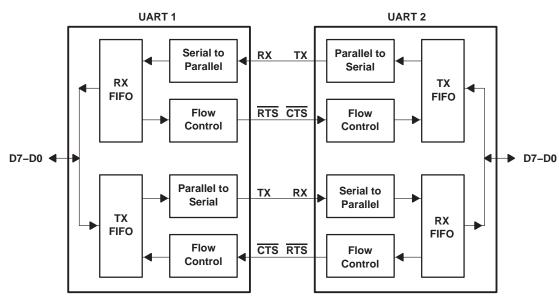

The UART will perform serial-to-parallel conversion on data characters received from peripheral devices or modems and parallel-to-parallel conversion on data characters transmitted by the processor. The complete status of each channel of the TL16C754B UART can be read at any time during functional operation by the processor.

The TL16C754B UART can be placed in an alternate mode (FIFO mode) relieving the processor of excessive software overhead by buffering received/transmitted characters. Both the receiver and transmitter FIFOs can store up to 64 bytes (including three additional bits of error status per byte for the receiver FIFO) and have selectable or programmable trigger levels. Primary outputs RXRDY and TXRDY allow signalling of DMA transfers.

The TL16C754B UART has selectable hardware flow control and software flow control. Both schemes significantly reduce software overhead and increase system efficiency by automatically controlling serial data flow. Hardware flow control uses the  $\overline{\text{RTS}}$  output and  $\overline{\text{CTS}}$  input signals. Software flow control uses programmable Xon/Xoff characters.

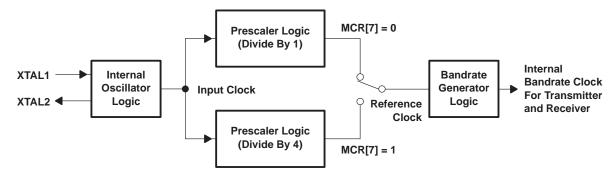

The UART will include a programmable baud rate generator that can divide the timing reference clock input by a divisor between 1 and (2<sup>16</sup>–1). The CLKSEL pin can be used to divide the input clock by 4 or by 1 to generate the reference clock during the reset. The divide-by-4 clock is selected when CLKSEL pin is a logic 0 or the divide-by-1 is selected when CLKSEL is a logic 1.

SLLS397A - NOVEMBER 1999 - REVISED JUNE 2004

# functional description (continued)

#### trigger levels

The TL16C754B UART provides independent selectable and programmable trigger levels for both receiver and transmitter DMA and interrupt generation. After reset, both transmitter and receiver FIFOs are disabled and so, in effect, the trigger level is the default value of one byte. The selectable trigger levels are available via the FCR. The programmable trigger levels are available via the TLR.

#### hardware flow control

Hardware flow control is composed of auto- $\overline{\text{CTS}}$  and auto- $\overline{\text{RTS}}$ . Auto- $\overline{\text{CTS}}$  and auto- $\overline{\text{RTS}}$  can be enabled/disabled independently by programming EFR[7:6].

With auto-CTS, CTS must be active before the UART can transmit data.

Auto-RTS only activates the RTS output when there is enough room in the FIFO to receive data and deactivates the RTS output when the RX FIFO is sufficiently full. The HALT and RESTORE trigger levels in the TCR determine the levels at which RTS is activated/deactivated.

If both auto- $\overline{\text{CTS}}$  and auto- $\overline{\text{RTS}}$  are enabled, when  $\overline{\text{RTS}}$  is connected to  $\overline{\text{CTS}}$ , data transmission does not occur unless the receiver FIFO has empty space. Thus, overrun errors are eliminated during hardware flow control. If not enabled, overrun errors occur if the transmit data rate exceeds the receive FIFO servicing latency.

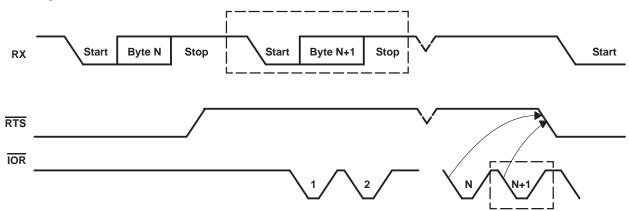

#### auto-RTS

Auto-RTS data flow control originates in the receiver block (see functional block diagram). Figure 1 shows RTS functional timing. The receiver FIFO trigger levels used in Auto-RTS are stored in the TCR. RTS is active if the RX FIFO level is below the HALT trigger level in TCR[3:0]. When the receiver FIFO HALT trigger level is reached, RTS is deasserted. The sending device (e.g., another UART) may send an additional byte after the trigger level is reached (assuming the sending UART has another byte to send) because it may not recognize the deassertion of RTS until it has begun sending the additional byte. RTS is automatically reasserted once the receiver FIFO reaches the RESUME trigger level programmed via TCR[7:4]. This reassertion allows the sending device to resume transmission.

NOTES: A. N = receiver FIFO trigger level

B. The two blocks in dashed lines cover the case where an additional byte is sent as described in Auto-RTS.

Figure 1. RTS Functional Timing

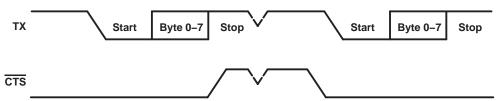

#### auto-CTS

The transmitter circuitry checks  $\overline{CTS}$  before sending the next data byte. When  $\overline{CTS}$  is active, the transmitter sends the next byte. To stop the transmitter from sending the following byte,  $\overline{CTS}$  must be deasserted before the middle of the last stop bit that is currently being sent. The auto- $\overline{CTS}$  function reduces interrupts to the host system. When flow control is enabled, the  $\overline{CTS}$  state changes and need not trigger host interrupts because the device automatically controls its own transmitter. Without auto- $\overline{CTS}$ , the transmitter sends any data present in the transmit FIFO and a receiver overrun error can result. Figure 2 shows  $\overline{CTS}$  functional timing, and Figure 3 shows an example of autoflow control.

NOTES: A. When CTS is low, the transmitter keeps sending serial data out.

- B. When CTS goes high before the middle of the last stop bit of the current byte, the transmitter finishes sending the current byte, but it does not send the next byte.

- C. When CTS goes from high to low, the transmitter begins sending data again.

Figure 2. CTS Functional Timing

Figure 3. Autoflow Control (Auto-RTS and Auto-CTS) Example

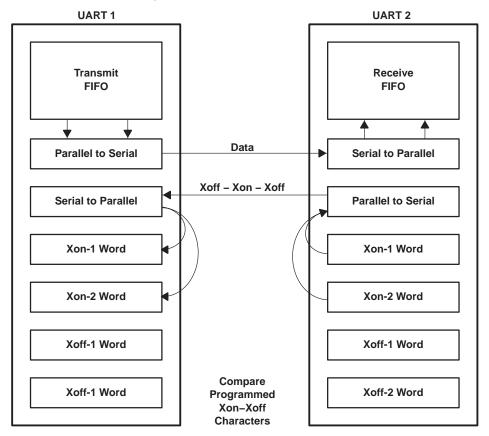

#### software flow control

Software flow control is enabled through the enhanced feature register and the modem control register. Different combinations of software flow control can be enabled by setting different combinations of EFR[3–0]. Table 1 shows software flow control options.

Two other enhanced features relate to S/W flow control:

Xon Any Function [MCR(5): Operation will resume after receiving any character after recognizing the Xoff character.

#### NOTE:

It is possible that an Xon1 character is recognized as an Xon Any character, which could cause an Xon2 character to be written to the RX FIFO.

Special Character [EFR(5)]: Incoming data is compared to Xoff2. Detection of the special character sets the Xoff interrupt {IIR(4)] but does not halt transmission. The Xoff interrupt is cleared by a read of the IIR. The special character is transferred to the RX FIFO.

| BIT 3 | BIT 2 | BIT 1 | BIT 0 | Tx, Rx SOFTWARE FLOW CONTROLS                                                      |

|-------|-------|-------|-------|------------------------------------------------------------------------------------|

| 0     | 0     | Х     | Х     | No transmit flow control                                                           |

| 1     | 0     | Х     | Х     | Transmit Xon1, Xoff1                                                               |

| 0     | 1     | Х     | Х     | Transmit Xon2, Xoff2                                                               |

| 1     | 1     | Х     | Х     | Transmit Xon1, Xon2: Xoff1, Xoff2                                                  |

| Х     | Х     | 0     | 0     | No receive flow control                                                            |

| Х     | Х     | 1     | 0     | Receiver compares Xon1, Xoff1                                                      |

| Х     | Х     | 0     | 1     | Receiver compares Xon2, Xoff2                                                      |

| 1     | 0     | 1     | 1     | Transmit Xon1, Xoff1 Receiver compares Xon1 or Xon2, Xoff1 or Xoff2                |

| 0     | 1     | 1     | 1     | Transmit Xon2, Xoff2 Receiver compares Xon1 or Xon2, Xoff1 or Xoff2                |

| 1     | 1     | 1     | 1     | Transmit Xon1, Xon2: Xoff1, Xoff2 Receiver compares Xon1 and Xon2: Xoff1 and Xoff2 |

| 0     | 0     | 1     | 1     | No transmit flow control<br>Receiver compares Xon1 and Xon2: Xoff1 and Xoff2       |

Table 1. Software Flow Control Options EFR[3:0]

When software flow control operation is enabled, the TL16C754B will compare incoming data with Xoff1/2 programmed characters (in certain cases Xoff1 and Xoff2 must be received sequentially¹). When an Xoff character is received, transmission is halted after completing transmission of the current character. Xoff character detection also sets IIR[4] and causes INT to go high (if enabled via IER[5]).

To resume transmission an Xon1/2 character must be received (in certain cases Xon1 and Xon2 must be received sequentially). When the correct Xon characters are received IIR[4] is cleared and the Xoff interrupt disappears.

#### NOTE:

If a parity, framing or break error occurs while receiving a software flow control character, this character will be treated as normal data and will be written to the RCV FIFO.

Xoff1/2 characters are transmitted when the RX FIFO has passed the programmed trigger level TCR[3:0].

Xon1/2 characters are transmitted when the RX FIFO reaches the trigger level programmed via TCR[7:4].

An important note here is that if, after an Xoff character has been sent, software flow control is disabled, the UART will transmit Xon characters automatically to enable normal transmission to proceed. A feature of the TL16C754B UART design is that if the software flow combination (EFR[3:0]) changes after an Xoff has been sent, the originally programmed Xon is automatically sent. If the RX FIFO is still above the trigger level the newly programmed Xoff1/2 will be transmitted.

<sup>1.</sup> When pairs of Xon/Xoff characters are programmed to occur sequentially, received Xon1/Xoff1 characters will be written to the Rx FIFO if the subsequent character is not Xon2/Xoff2.

The transmission of Xoff/Xon(s) follows the exact same protocol as transmission of an ordinary byte from the FIFO. This means that even if the word length is set to be 5, 6, or 7 characters then the 5, 6, or 7 least significant bits of Xoff1,2/Xon1,2 will be transmitted. The transmission of 5, 6, or 7 bits of a character is seldom done, but this functionality is included to maintain compatibility with earlier designs.

It is assumed that software flow control and hardware flow control will never be enabled simultaneously. Figure 4 shows a software flow control example.

Figure 4. Software Flow Control Example

#### software flow control example

Assumptions: UART1 is transmitting a large text file to UART2. Both UARTs are using software flow control with single character Xoff (0F) and Xon (0D) tokens. Both have Xoff threshold (TCR [3:0]=F) set to 60 and Xon threshold (TCR[7:4]=8) set to 32. Both have the interrupt receive threshold (TLR[7:4]=D) set to 52.

UART1 begins transmission and sends 52 characters, at which point UART2 will generate an interrupt to its processor to service the RCV FIFO, but assume the interrupt latency is fairly long. UART1 will continue sending characters until a total of 60 characters have been sent. At this time UART2 will transmit a 0F to UART1, informing UART1 to halt transmission. UART1 will likely send the 61st character while UART2 is sending the Xoff character. Now UART2 is serviced and the processor reads enough data out of the RCV FIFO that the level drops to 32. UART2 will now send a 0D to UART1, informing UART1 to resume transmission.

SLLS397A - NOVEMBER 1999 - REVISED JUNE 2004

# functional description (continued)

#### reset

Table 2 summarizes the state of registers after reset.

**Table 2. Register Reset Functions**

| REGISTER                          | RESET<br>CONTROL | RESET STATE                                                               |

|-----------------------------------|------------------|---------------------------------------------------------------------------|

| Interrupt enable register         | RESET            | All bits cleared                                                          |

| Interrupt identification register | RESET            | Bit 0 is set. All other bits cleared.                                     |

| FIFO control register             | RESET            | All bits cleared                                                          |

| Line control register             | RESET            | Reset to 00011101 (1D hex).                                               |

| Modem control register            | RESET            | Bit 6–0 cleared. Bit 7 reflects the inverse of the CLKSEL pin value.      |

| Line status register              | RESET            | Bits 5 and 6 set. All other bits cleared.                                 |

| Modem status register             | RESET            | Bits 0-3 cleared. Bits 4-7 input signals.                                 |

| Enhanced feature register         | RESET            | Bit 6 – 0 is cleared. Bit 7 reflects the inverse of the CLKSEL pin value. |

| Receiver holding register         | RESET            | Pointer logic cleared                                                     |

| Transmitter holding register      | RESET            | Pointer logic cleared                                                     |

| Transmission control register     | RESET            | All bits cleared                                                          |

| Trigger level register            | RESET            | All bits cleared                                                          |

NOTE: Registers DLL, DLH, SPR, Xon1, Xon2, Xoff1, Xoff2 are not reset by the top-level reset signal RESET, i.e., they hold their initialization values during reset.

Table 3 summarizes the state of some signals after reset.

Table 3. Signal Reset Functions

| SIGNAL | RESET<br>CONTROL | RESET STATE |

|--------|------------------|-------------|

| TX     | RESET            | High        |

| RTS    | RESET            | High        |

| DTR    | RESET            | High        |

| RXRDY  | RESET            | High        |

| TXRDY  | RESET            | Low         |

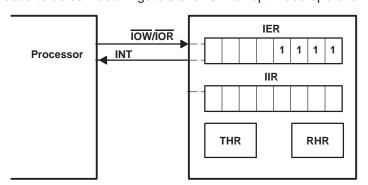

#### interrupts

The TL16C754B UART has interrupt generation and prioritization (6 prioritized levels of interrupts) capability. The interrupt enable register (IER) enables each of the 6 types of interrupts and the INT signal in response to an interrupt generation. The IER can also disable the interrupt system by clearing bits 0-3, 5-7. When an interrupt is generated, the interrupt identification register(IIR) indicates that an interrupt is pending and provides the type of interrupt through IIR[5-0]. Table 4 summarizes the interrupt control functions.

**Table 4. Interrupt Control Functions**

| IIR[5-0] | PRIORITY<br>LEVEL | INTERRUPT<br>TYPE    | INTERRUPT SOURCE                                                                | INTERRUPT RESET METHOD                                                       |

|----------|-------------------|----------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| 000001   | None              | None                 | None                                                                            | None                                                                         |

| 000110   | 1                 | Receiver line status | OE, FE, PE, or BI errors occur in characters in the RX FIFO                     | FE< PE< BI: All erroneous characters are read from the RX FIFO. OE: Read LSR |

| 001100   | 2                 | RX timeout           | Stale data in RX FIFO                                                           | Read RHR                                                                     |

| 000100   | 2                 | RHR interrupt        | DRDY (data ready) (FIFO disable) RX FIFO above trigger level (FIFO enable)      | Read RHR                                                                     |

| 000010   | 3                 | THR interrupt        | TFE (THR empty) (FIFO disable) TX FIFO passes above trigger level (FIFO enable) | Read IIR OR a write to the THR                                               |

| 000000   | 4                 | Modem status         | MSR[3:0]= 0                                                                     | Read MSR                                                                     |

| 010000   | 5                 | Xoff interrupt       | Receive Xoff character(s)/special character                                     | Receive Xon character(s)/Read of IIR                                         |

| 100000   | 6                 | CTS, RTS             | RTS pin or CTS pin change state from active (low) to inactive (high)            | Read IIR                                                                     |

It is important to note that for the framing error, parity error, and break conditions, LSR[7] generates the interrupt. LSR[7] is set when there is an error anywhere in the RX FIFO and is cleared only when there are no more errors remaining in the FIFO. LSR[4–2] always represent the error status for the received character at the top of the Rx FIFO. Reading the Rx FIFO updates LSR[4–2] to the appropriate status for the new character at the top of the FIFO. If the Rx FIFO is empty, then LSR[4–2] is all zeros.

For the Xoff interrupt, if an Xoff flow character detection caused the interrupt, the interrupt is cleared by an Xon flow character detection. If a special character detection caused the interrupt, the interrupt is cleared by a read of the ISR.

#### interrupt mode operation

In interrupt mode (if any bit of IER[3:0] is1), the processor is informed of the status of the receiver and transmitter by an interrupt signal, INT. Therefore, it is not necessary to continuously poll the line status register (LSR) to see if any interrupt needs to be serviced. Figure 5 shows interrupt mode operation.

**Figure 5. Interrupt Mode Operation**

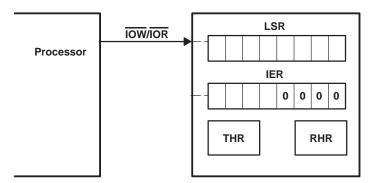

#### polled mode operation

In polled mode (IER[3:0] = 0000), the status of the receiver and transmitter can then be checked by polling the line status register (LSR). This mode is an alternative to the interrupt mode of operation where the status of the receiver and transmitter is automatically known by means of interrupts sent to the CPU. Figure 6 shows polled mode operation.

Figure 6. FIFO Polled Mode Operation

## **DMA** signalling

There are two modes of DMA operation, DMA mode 0 or 1, selected by FCR[3].

In DMA mode 0 or FIFO disable (FCR[0]=0) DMA occurs in single character transfers. In DMA mode 1 multicharacter (or block) DMA transfers are managed to relieve the processor for longer periods of time.

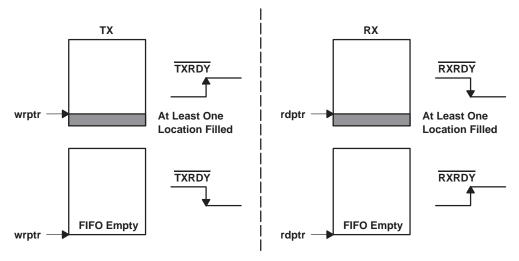

#### single DMA transfers (DMA mode0/FIFO disable)

Transmitter: When empty, the TXRDY signal becomes active. TXRDY will go inactive after one character has been loaded into it

Receiver: RXRDY is active when there is at least one character in the FIFO. It becomes inactive when the receiver is empty.

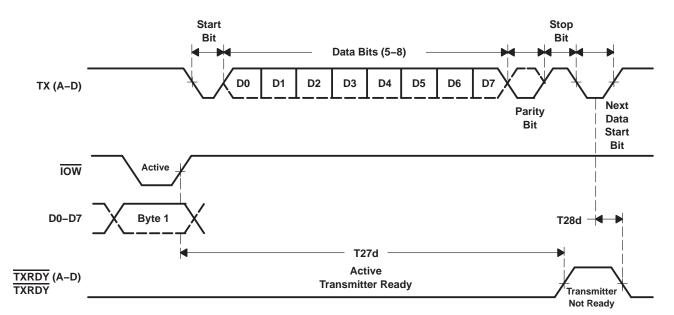

Figure 7 shows TXRDY and RXRDY in DMA mode 0/FIFO disable.

Figure 7. TXRDY and RXRDY in DMA Mode 0/FIFO Disable

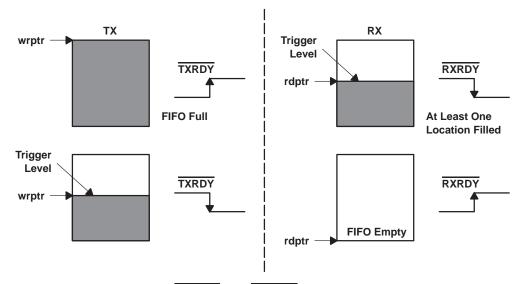

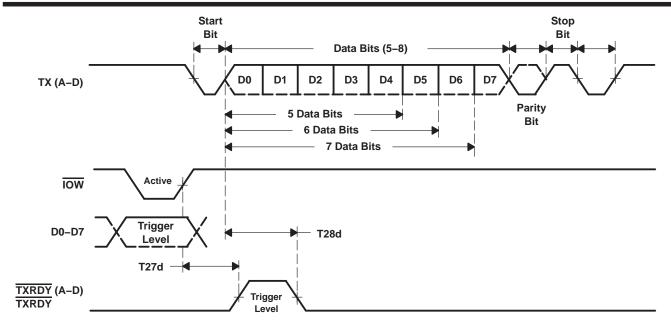

## block DMA transfers (DMA mode 1)

Transmitter: TXRDY is active when a trigger level number of spaces are available. It becomes inactive when the FIFO is full.

Receiver: RXRDY becomes active when the trigger level has been reached or when a timeout interrupt occurs. It will go inactive when the FIFO is empty or an error in the RX FIFO is flagged by LSR(7)

Figure 8 shows TXRDY and RXRDY in DMA mode 1.

Figure 8. TXRDY and RXRDY in DMA Mode 1

#### sleep mode

Sleep mode is an enhanced feature of the TL16C754B UART. It is enabled when EFR[4], the enhanced functions bit, is set and when IER[4] is set. Sleep mode is entered when:

- The serial data input line, RX, is idle (see break and time-out conditions).

- The TX FIFO and TX shift register are empty.

- There are no interrupts pending except THR and timeout interrupts.

Sleep mode will not be entered if there is data in the RX FIFO.

In sleep mode the UART clock and baud rate clock are stopped. Since most registers are clocked using these clocks the power consumption is greatly reduced. The UART will wake up when any change is detected on the RX line, when there is any change in the state of the modem input pins or if data is written to the TX FIFO.

#### NOTE:

Writing to the divisor latches, DLL and DLH, to set the baud clock, **must not** be done during sleep mode. Therefore it is advisable to disable sleep mode using IER[4] before writing to DLL or DLH.

#### break and timeout conditions

An RX timeout condition is detected when the receiver line, RX, has been high for a time equivalent to (4X programmed word length)+12 bits and there is at least one byte stored in the Rx FIFO.

When a break condition occurs, the TX line is pulled low. A break condition is activated by setting LCR[6].

#### programmable baud rate generator

The TL16C754B UART contains a programmable baud generator that divides reference clock by a divisor in the range between 1 and (2<sup>16</sup>–1). The output frequency of the baud rate generator is 16x the baud rate. An additional divide-by-4 prescaler is also available and can be selected by the CLKSEL pin or MCR[7], as shown in the following. The formula for the divisor is:

Divisor =  $(XTAL1 \text{ crystal input frequency / prescaler}) / (desired baud rate <math>\times$  16)

Where

$$prescaler = \begin{cases} 1 \text{ when CLKSEL } = \text{ high during reset, or MCR[7] is set to 0 after reset} \\ 4 \text{ when CLKSEL } = \text{ low during reset, or MCR[7] is set to 1 after reset} \end{cases}$$

Figure 9 shows the internal prescaler and baud rate generator circuitry.

Figure 9. Prescaler and Baud Rate Generator Block Diagram

DLL and DLH must be written to in order to program the baud rate. DLL and DLH are the least significant and most significant byte of the baud rate divisor.

If DLL and DLH are both zero, the UART is effectively disabled, as no baud clock will be generated.

The programmable baud rate generator is provided to select both the transmit and receive clock rates.

Table 5 and Table 6 show the baud rate and divisor correlation for the crystal with frequency 1.8432 MHz and 3.072 MHz, respectively.

# programmable baud rate generator (continued)

Table 5. Baud Rates Using a 1.8432-MHz Crystal

| DESIRED<br>BAUD RATE | DIVISOR USED<br>TO GENERATE<br>16 × CLOCK | PERCENT ERROR<br>DIFFERENCE BETWEEN<br>DESIRED AND ACTUAL |

|----------------------|-------------------------------------------|-----------------------------------------------------------|

| 50                   | 2304                                      |                                                           |

| 75                   | 1536                                      |                                                           |

| 110                  | 1047                                      | 0.026                                                     |

| 134.5                | 857                                       | 0.058                                                     |

| 150                  | 768                                       |                                                           |

| 300                  | 384                                       |                                                           |

| 600                  | 192                                       |                                                           |

| 1200                 | 96                                        |                                                           |

| 1800                 | 64                                        |                                                           |

| 2000                 | 58                                        | 0.69                                                      |

| 2400                 | 48                                        |                                                           |

| 3600                 | 32                                        |                                                           |

| 4800                 | 24                                        |                                                           |

| 7200                 | 16                                        |                                                           |

| 9600                 | 12                                        |                                                           |

| 19200                | 6                                         |                                                           |

| 38400                | 3                                         |                                                           |

| 56000                | 2                                         | 2.86                                                      |

Table 6. Baud Rates Using a 3.072-MHz Crystal

| DESIRED<br>BAUD RATE | DIVISOR USED<br>TO GENERATE<br>16 × CLOCK | PERCENT ERROR<br>DIFFERENCE BETWEEN<br>DESIRED AND ACTUAL |

|----------------------|-------------------------------------------|-----------------------------------------------------------|

| 50                   | 3840                                      |                                                           |

| 75                   | 2560                                      |                                                           |

| 110                  | 1745                                      | 0.026                                                     |

| 134.5                | 1428                                      | 0.034                                                     |

| 150                  | 1280                                      |                                                           |

| 300                  | 640                                       |                                                           |

| 600                  | 320                                       |                                                           |

| 1200                 | 160                                       |                                                           |

| 1800                 | 107                                       | 0.312                                                     |

| 2000                 | 96                                        |                                                           |

| 2400                 | 80                                        |                                                           |

| 3600                 | 53                                        | 0.628                                                     |

| 4800                 | 40                                        |                                                           |

| 7200                 | 27                                        | 1.23                                                      |

| 9600                 | 20                                        |                                                           |

| 19200                | 10                                        |                                                           |

| 38400                | 5                                         |                                                           |

SLLS397A - NOVEMBER 1999 - REVISED JUNE 2004

# programmable baud generator (continued)

Figure 10 shows the crystal clock circuit reference.

#### TYPICAL CRYSTAL OSCILLATOR NETWORK

| CRYSTAL    | RP   | RX2    | C1       | C2       |

|------------|------|--------|----------|----------|

| 3.072 MHz  | 1 ΜΩ | 1.5 kΩ | 10-30 pF | 40-60 pF |

| 1.8432 MHz | 1 ΜΩ | 1.5 kΩ | 10-30 pF | 40-60 pF |

Figure 10. Typical Crystal Clock Circuits<sup>†</sup>

<sup>†</sup> For crystal with fundamental frequency from 1 MHz to 24 MHz

NOTE: For input clock frequency higher then 24 MHz, the crystal is not allowed and the oscillator must be used, since the TL16C754B internal oscillator cell can only support the crystal frequency up to 24 MHz.

# absolute maximum ratings over operating free-air temperature (unless otherwise noted)†

## recommended operating conditions

# low voltage (3.3 V nominal)

|                                              |                                     | MIN                  | NOM | MAX                | UNIT |

|----------------------------------------------|-------------------------------------|----------------------|-----|--------------------|------|

| Supply voltage, V <sub>CC</sub>              |                                     | 2.7                  | 3.3 | 3.6                | V    |

| Input voltage, V <sub>I</sub>                |                                     | 0                    |     | Vcc                | V    |

| High-level input voltage, VIH (se            | e Note 1)                           | 0.7V <sub>CC</sub>   |     |                    | V    |

| Low-level input voltage, VIL (see            | Note 1)                             |                      |     | 0.3V <sub>CC</sub> | V    |

| Output voltage, VO (see Note 2)              |                                     | 0                    |     | Vcc                | V    |

| LPale lavel autout avenue at M               | $I_{OH} = -8$ mA, See Note 4        | V <sub>CC</sub> -0.8 |     |                    |      |

| High-level output current, VOH               | I <sub>OH</sub> = -4 mA, See Note 5 | V <sub>CC</sub> -0.8 |     |                    | V    |

|                                              | I <sub>OL</sub> = 8 mA, See Note 4  |                      |     | 0.5                | V    |

| Low-level output current, VOL                | I <sub>OL</sub> = 4 mA, See Note 5  |                      |     | 0.5                |      |

| Input capacitance, CI                        |                                     |                      |     | 18                 | pF   |

| Operating free-air temperature,              | ГА                                  | -40                  | 25  | 85                 | °C   |

| Virtual junction temperature range           | ge, TJ (see Note 3)                 | 0                    | 25  | 125                | °C   |

| Oscillator/clock speed                       |                                     |                      |     | 35                 | MHz  |

| Clock duty cycle                             |                                     |                      | 50% |                    |      |

| Jitter specification                         |                                     |                      |     | ±100               | ppm  |

| Supply current, I <sub>CC</sub> (see Note 6) | 1.8 MHz, 3.6 V                      |                      | 12  |                    |      |

|                                              | 25 MHz, 3.6 V                       |                      | 25  |                    | mA   |

| (300 14010 0)                                | Sleep Mode, 3.6 V                   |                      | 1.5 |                    |      |

NOTES: 1. Meets TTL levels,  $V_{IH(min)} = 2 \text{ V}$  and  $V_{IL(max)} = 0.8 \text{ V}$  on nonhysteresis inputs.

- Applies for external output buffers.

- 3. These junction temperatures reflect simulated conditions. Absolute maximum junction temperature is 150°C. The customer is responsible for verifying junction temperature.

- 4. These parameters apply for D7-D0.

- 5. These parameters apply for DTRA, DTRB, DTRC, DTRD, INTA, INTB, INTC, INTD, RTS\_A, RTS\_B, RTS\_C, RTS\_D, RSRDY, TXRDY, TX\_A, TX\_B, TX\_C, TX\_D.

- 6. Measurement condition:

- a) Normal operation other than sleep mode

$V_{CC} = 3.3 \text{ V}, T_A = 25^{\circ}\text{C}.$

Full duplex serial activity on all four serial (UART) channels at the clock frequency specified in above table with divisior of one.

b) Sleep mode

$V_{CC} = 3.3 \text{ V}, T_A = 25^{\circ}\text{C}.$

After enabling the sleep mode for all four channels, all serial and host activity is kept idle.

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

SLLS397A - NOVEMBER 1999 - REVISED JUNE 2004

# recommended operating conditions (continued)

#### standard voltage

|                                          |                                           | MIN     | NOM | MAX                | UNIT |  |

|------------------------------------------|-------------------------------------------|---------|-----|--------------------|------|--|

| Supply voltage, V <sub>CC</sub>          |                                           | 4.5     | 5   | 5.5                | V    |  |

| Input voltage, V <sub>I</sub>            | voltage, V <sub>I</sub> 0 V <sub>CC</sub> |         | V   |                    |      |  |

| High-level input voltage, VIH            |                                           |         | V   |                    |      |  |

| Low-level input voltage, V <sub>IL</sub> |                                           |         |     | 0.3V <sub>CC</sub> | V    |  |

| Output voltage, VO                       |                                           | 0       |     | VCC                | V    |  |

| Habitanal autout assess at M             | I <sub>OH</sub> = -8 mA, See Note 8       | VCC-0.8 |     |                    |      |  |

| High-level output current, VOH           | I <sub>OH</sub> = -4 mA, See Note 9       | VCC-0.8 |     |                    | V    |  |

| Law lavel autout aumant Mar              | I <sub>OL</sub> = 8 mA, See Note 8        |         |     | 0.5                | V    |  |

| Low-level output current, VOL            | I <sub>OL</sub> = 4 mA, See Note 9        |         |     | 0.5                |      |  |

| Input capacitance, CI                    |                                           |         |     | 18                 | pF   |  |

| Operating free-air temperature,          | ГА                                        | -40     | 25  | 85                 | °C   |  |

| Virtual junction temperature rang        | ge, T <sub>J</sub> (see Note 7)           | 0       | 25  | 125                | °C   |  |

| Oscillator/clock speed                   |                                           |         |     | 50                 | MHz  |  |

| Clock duty cycle                         |                                           |         | 50% |                    |      |  |

|                                          | 50 MHz, 5.5 V                             |         | 50  |                    |      |  |

| Supply current, I <sub>CC</sub>          | 25 MHz, 5.5 V                             |         | 42  |                    | mA   |  |

| (see Note 12)                            | 1.8 MHz, 5.5 V                            |         | 21  |                    |      |  |

|                                          | Sleep mode, 5.5 V                         |         | 2.5 |                    |      |  |

NOTES: 7. Applies for external output buffers

- 8. These junction temperatures reflect simulated conditions. Absolute maximum junction temperature is 150°C. The customer is responsible for verifying junction temperature.

- 9. These parameters apply for D7–D0, IRQ3–IRQ15, DRO0, DRO1, and DRO3.

- 10. These parameters apply for GPIO0–GPIO7, XSOUT, XRTS, XDTR, XIR–TXD.

- 11. These parameters apply for XOUT.

- 12. Measurement condition:

- a) Normal operation other than sleep mode

$$V_{CC} = 5 \text{ V}, \quad T_A = 25^{\circ}\text{C}.$$

Full duplex serial activity on all four serial (UART) channels at the clock frequency specified in above table with divisior of one.

b) Sleep mode

$$V_{CC} = 5 \text{ V}, T_{A} = 25^{\circ}\text{C}.$$

After enabling the sleep mode for all four channels, all serial and host activity is kept idle.

SLLS397A - NOVEMBER 1999 - REVISED JUNE 2004

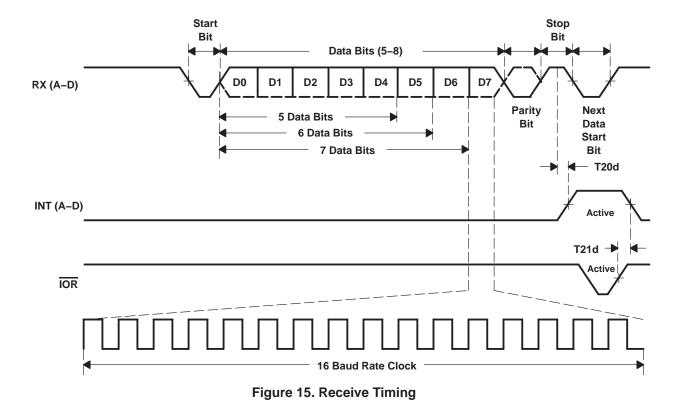

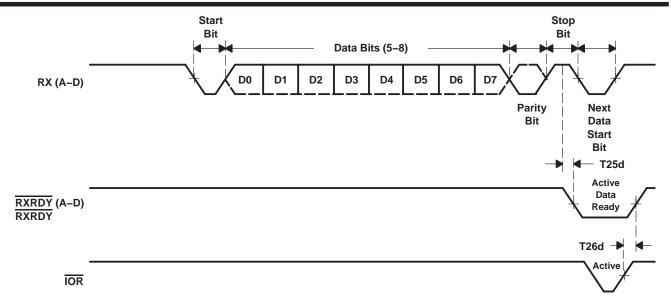

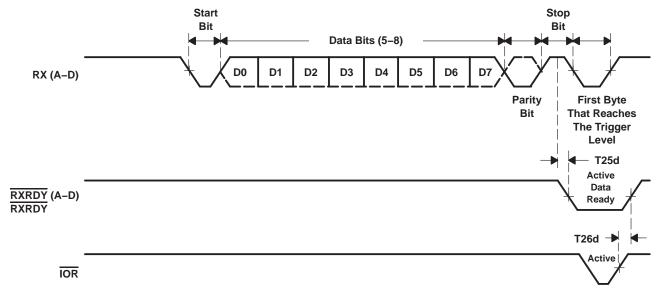

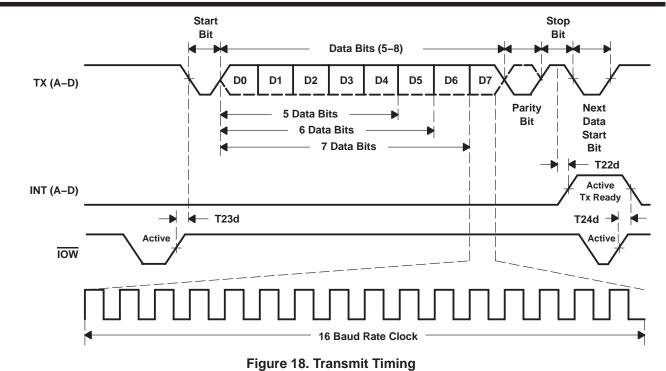

# timing requirements $T_A = -40^{\circ}\text{C}$ to 85°C, $V_{CC} = 3.3 \text{ V}$ to 5 V $\pm$ 10% (unless otherwise noted)(see Figures 9–16)

|                    |                                                                                           |                         | LIM             | TS                |         |

|--------------------|-------------------------------------------------------------------------------------------|-------------------------|-----------------|-------------------|---------|

|                    | PARAMETER                                                                                 | TEST CONDITIONS         | MIN             | MAX               | UNIT    |

| C <sub>P</sub>     | Clock period                                                                              |                         | 20              |                   | ns      |

| T <sub>RESET</sub> | Reset pulse width                                                                         |                         | 200             |                   | ns      |

| _                  | One Water/Oland arread                                                                    | V <sub>CC</sub> = 4.5 V |                 | 50                | N 41 1- |

| T <sub>3w</sub>    | Oscillator/Clock speed                                                                    | V <sub>CC</sub> = 3 V   |                 | 45                | MHz     |

| T <sub>6s</sub>    | Address setup time                                                                        |                         | 0               |                   | ns      |

| T <sub>6h</sub>    | Address hold time                                                                         |                         | 0               |                   | ns      |

| T <sub>7d</sub>    | IOR delay from chip select                                                                |                         | 10              |                   | ns      |

| $T_{7w}$           | IOR strobe width                                                                          |                         | 2P‡             |                   |         |

| T <sub>7h</sub>    | Chip select hold time from IOR                                                            |                         | 0               |                   | ns      |

| T <sub>8d</sub>    | Delay time between successive assertion of IOW and IOR                                    |                         | 4P‡             |                   | ns      |

| T <sub>8s</sub>    | Setup time from IOW or IOR assertion to XTAL1 clock↑                                      |                         | 20              |                   | ns      |

| T <sub>8h</sub>    | Hold time from XTAL1 clock↓ to $\overline{\text{IOW}}$ or $\overline{\text{IOR}}$ release |                         | 20              |                   | ns      |

| T <sub>9d</sub>    | Read cycle delay                                                                          |                         | 2P <sup>‡</sup> |                   |         |

| _                  | Delegation IOD to date                                                                    | V <sub>CC</sub> = 4.5 V |                 | 30                |         |

| T <sub>12d</sub>   | Delay from IOR to data                                                                    | V <sub>CC</sub> = 3 V   |                 | 47                | ns      |

| T <sub>12h</sub>   | Data disable time                                                                         |                         |                 | 15                | ns      |

| T <sub>13d</sub>   | IOW delay from chip select                                                                |                         | 10              |                   | ns      |

| T <sub>13w</sub>   | IOW strobe width                                                                          |                         | 2P‡             |                   |         |

| T <sub>13h</sub>   | Chip select hold time from IOW                                                            |                         | 0               |                   | ns      |

| T <sub>15d</sub>   | Write cycle delay                                                                         |                         | 2P‡             |                   |         |

| T <sub>16s</sub>   | Data setup time                                                                           |                         | 16              |                   | ns      |

| T <sub>16h</sub>   | Data hold time                                                                            |                         | 15              |                   | ns      |

| T <sub>17d</sub>   | Delay from IOW to output                                                                  | 50 pF load              |                 | 50                | ns      |

| T <sub>18d</sub>   | Delay to set interrupt from MODEM input                                                   | 50 pF load              |                 | 70                | ns      |

| T <sub>19d</sub>   | Delay to reset interrupt from IOR                                                         | 50 pF load              |                 | 70                | ns      |

| T <sub>20d</sub>   | Delay from stop to set interrupt                                                          |                         |                 | 1 <sub>Rclk</sub> | †       |

| T <sub>21d</sub>   | Delay from IOR to reset interrupt                                                         | 50 pF load              |                 | 70                | ns      |

| T <sub>22d</sub>   | Delay from stop to interrupt                                                              |                         |                 | 100               | ns      |

| T <sub>23d</sub>   | Delay from initial IOW reset to transmit start                                            |                         | 8               | 24                | †       |

| T <sub>24d</sub>   | Delay from IOW to reset interrupt                                                         |                         |                 | 70                | ns      |

| T <sub>25d</sub>   | Delay from stop to set RXRDY                                                              |                         |                 | 1                 | Clk     |

| T <sub>26d</sub>   | Delay from IOR to reset RXRDY                                                             |                         |                 | 1                 | μs      |

| T <sub>27d</sub>   | Delay from IOW to set TXRDY                                                               |                         |                 | 70                | ns      |

| T <sub>28d</sub>   | Delay from start to reset TXRDY                                                           |                         |                 | 16                | †       |

| T <sub>30s</sub>   | Address setup time                                                                        |                         | 10              |                   | ns      |

<sup>†</sup> Baudrate

<sup>‡</sup>P= Input clock period

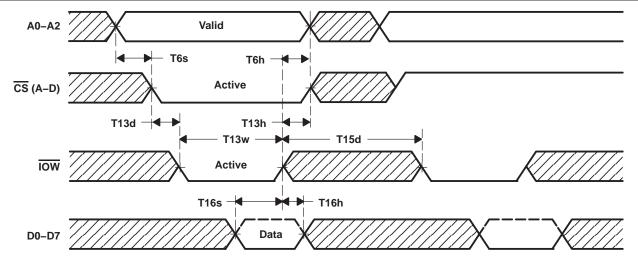

Figure 11. General Write Timing

<sup>&</sup>lt;sup>†</sup> The shadow area means in a shared bus environment, the UART is not driving the data bus.

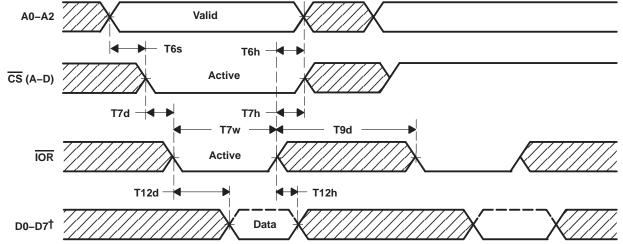

Figure 12. General Read Timing

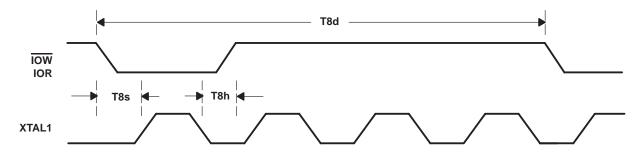

Figure 13. Alternate Read/Write Strobe Timing

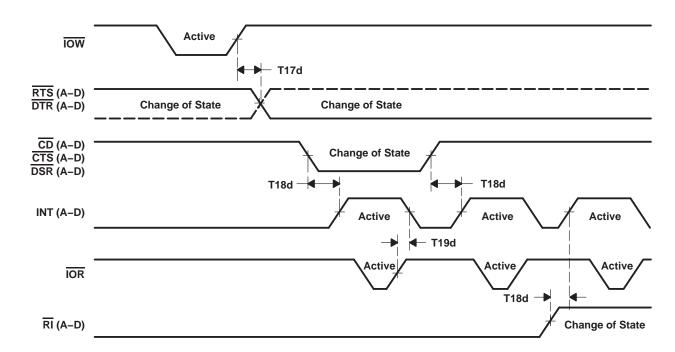

Figure 14. Modem Input/Output Timing

Figure 16. Receive Ready Timing in None FIFO Mode

Figure 17. Receive Timing in FIFO Mode

Figure 19. Transmit Ready Timing in None FIFO Mode

Figure 20. Transmit Ready Timing in FIFO Mode

# register map†

Each register is selected using address lines A[0], A[1], A[2] and, in some cases, bits from other registers. The programming combinations for register selection are shown in Table 7.

Table 7. Register Map - Read/Write Properties

| A[2] | A[1] | A[0] | READ MODE                               | WRITE MODE                      |

|------|------|------|-----------------------------------------|---------------------------------|

| 0    | 0    | 0    | Receive holding register (RHR)          | Transmit holding register (THR) |

| 0    | 0    | 1    | Interrupt enable register (IER)         | Interrupt enable register       |

| 0    | 1    | 0    | Interrupt identification register (IIR) | FIFO control register (FCR)     |

| 0    | 1    | 1    | Line control register (LCR)             | Line control register           |

| 1    | 0    | 0    | Modem control register (MCR)            | Modem control register          |

| 1    | 0    | 1    | Line status register (LSR)              |                                 |

| 1    | 1    | 0    | Modem status register (MSR)             |                                 |

| 1    | 1    | 1    | Scratch register (SPR)                  | Scratch register (SPR)          |

| 0    | 0    | 0    | Divisor latch LSB (DLL)                 | Divisor latch LSB (DLL)         |

| 0    | 0    | 1    | Divisor latch MSB (DLH)                 | Divisor latch MSB (DLH          |

| 0    | 1    | 0    | Enhanced feature register (EFR)         | Enhanced feature register       |

| 1    | 0    | 0    | Xon-1 word                              | Xon-1 word                      |

| 1    | 0    | 1    | Xon-2 word                              | Xon-2 word                      |

| 1    | 1    | 0    | Xoff-1 word                             | Xoff-1 word                     |

| 1    | 1    | 1    | Xoff-2 word                             | Xoff-2 word                     |

| 1    | 1    | 0    | Transmission control register (TCR)     | Transmission control register   |

| 1    | 1    | 1    | Trigger level register (TLR)            | Trigger level register          |

| 1    | 1    | 1    | FIFO ready register                     |                                 |

<sup>†</sup>DLL and DLH are accessible only when LCR bit-7 is 1.

Enhanced feature register, Xon1, 2 and Xoff1, 2 are accessible only when LCR is set to 10111111 (8hBF).

Transmission control register and trigger level register are accessible only when EFR[4] = 1 and MCR[6] = 1, i.e., EFR[4] and MCR[6] are read/write enables.

FCR FIFORdy register is accessible when any CS A-D = 0, MCR [2] = 1 and loopback MCR [4] = 0 is disabled.

MCR[7] can only be modified when EFR[4] is set.

# register map (continued)

Table 8 lists and describes the TL16C754B internal registers.

# Table 8. TL16C754B Internal Registers

| Addr | REGISTER | BIT 7                                     | BIT 6                                     | BIT 5                          | BIT 4                            | BIT 3                          | BIT 2                          | BIT 1                          | BIT 0                             | READ/<br>WRITE |

|------|----------|-------------------------------------------|-------------------------------------------|--------------------------------|----------------------------------|--------------------------------|--------------------------------|--------------------------------|-----------------------------------|----------------|

| 000  | RHR      | bit 7                                     | bit 6                                     | bit 5                          | bit 4                            | bit 3                          | bit 2                          | bit 1                          | bit 0                             | Read           |

| 000  | THR      | bit 7                                     | bit 6                                     | bit 5                          | bit 4                            | bit 3                          | bit 2                          | bit 1                          | bit 0                             | Write          |

| 001  | IER      | 0/CTS<br>interrupt<br>enable <sup>†</sup> | 0/RTS<br>interrupt<br>enable <sup>†</sup> | 0/Xoff<br>interrupt<br>enable† | 0/X Sleep<br>modeT               | Modem<br>status<br>interrupt   | Rx line<br>status<br>interrupt | THR<br>empty<br>interrupt      | Rx data<br>available<br>interrupt | Read/<br>Write |

| 010  | FCR      | Rx trigger<br>level                       | Rx trigger<br>level                       | 0/TX<br>trigger<br>level†      | 0/TX<br>trigger<br>levelT        | DMA<br>mode<br>select          | Resets<br>Tx FIFO              | Resets<br>Rx FIFO              | Enables<br>FIFOs                  | Write          |

| 010  | IIR      | FCR(0)                                    | FCR(0)                                    | 0 <u>/CT</u> S,<br>RTST        | 0/Xoff†                          | Interrupt<br>priority<br>Bit 2 | Interrupt<br>priority<br>Bit 1 | Interrupt<br>priority<br>Bit 0 | Interrupt<br>status               | Read           |

| 011  | LCR      | DLAB and<br>EFR<br>enable                 | Break<br>control bit                      | Sets parity                    | Parity type select               | Parity<br>enable               | No. of stop<br>bits            | Word<br>length                 | Word<br>length                    | Read/<br>Write |

| 100  | MCR      | 1x or<br>4X clock                         | TCR and<br>TLR<br>enable                  | 0/Xon Any                      | 0/Enable<br>loopback             | IRQ<br>Enable                  | FIFOrdy<br>Enable              | RTS                            | DTR                               | Read/<br>Write |

| 101  | LSR      | 0/Error in<br>Rx FIFO                     | THR and<br>TSR<br>empty                   | THR<br>empty                   | Break<br>interrupt               | Framing<br>error               | Parity<br>error                | Over-run<br>error              | Data in receiver                  | Read           |

| 110  | MSR      | CD                                        | RI                                        | DSR                            | CTS                              | ΔCD                            | ΔRI                            | ΔDSR                           | ΔCTS                              | Read           |

| 111  | SPR      | bit 7                                     | bit 6                                     | bit 5                          | bit 4                            | bit 3                          | bit 2                          | bit 1                          | bit 0                             | Read/<br>Write |

| 000  | DLL      | bit 7                                     | bit 6                                     | bit 5                          | bit 4                            | bit 3                          | bit 2                          | bit 1                          | bit 0                             | Read/<br>Write |

| 001  | DLH      | bit 15                                    | bit 14                                    | bit 13                         | bit 12                           | bit 11                         | bit 10                         | bit 9                          | bit 8                             | Read/<br>Write |

| 010  | EFR      | Auto-CTS                                  | Auto-RTS                                  | Special<br>character<br>detect | Enable<br>enhanced-<br>functions | S/W flow<br>control<br>Bit 3   | S/W flow<br>control<br>Bit 2   | S/W flow<br>control<br>Bit 1   | S/W flow<br>control<br>Bit 0      | Read/<br>Write |

| 100  | Xon1     | bit 7                                     | bit 6                                     | bit 5                          | bit 4                            | bit 3                          | bit 2                          | bit 1                          | bit 0                             | Read/<br>Write |

| 101  | Xon2     | bit 7                                     | bit 6                                     | bit 5                          | bit 4                            | bit 3                          | bit 2                          | bit 1                          | bit 0                             | Read/<br>Write |

| 110  | Xoff1    | bit 7                                     | bit 6                                     | bit 5                          | bit 4                            | bit 3                          | bit 2                          | bit 1                          | bit 0                             | Read/<br>Write |

| 111  | Xoff2    | bit 7                                     | bit 6                                     | bit 5                          | bit 4                            | bit 3                          | bit 2                          | bit 1                          | bit 0                             | Read/<br>Write |

| 110  | TCR      | bit 7                                     | bit 6                                     | bit 5                          | bit 4                            | bit 3                          | bit 2                          | bit 1                          | bit 0                             | Read/<br>Write |

| 111  | TLR      | bit 7                                     | bit 6                                     | bit 5                          | bit 4                            | bit 3                          | bit 2                          | bit 1                          | bit 0                             | Read/<br>Write |

| 111  | FIFORdy  | RX FIFO<br>D status                       | RX FIFO<br>C status                       | RX FIFO<br>B status            | RX FIFO<br>A status              | TX FIFO<br>D status            | TX FIFO<br>C status            | TX FIFO<br>B status            | TX FIFO<br>A status               | Read           |

<sup>†</sup> The shaded bits in the above table can only be modified if EFR[4] is enabled, i.e., if enhanced functions are enabled.

NOTE: Refer to the notes under Table 7 for more register access information.

#### receiver holding register (RHR)

The receiver section consists of the receiver holding register (RHR) and the receiver shift register (RSR). The RHR is actually a 64-byte FIFO. The RSR receives serial data from RX terminal. The data is converted to parallel data and moved to the RHR. The receiver section is controlled by the line control register. If the FIFO is disabled, location zero of the FIFO is used to store the characters. If overflow occurs, characters are lost. The RHR also stores the error status bits associated with each character.

## transmit holding register (THR)