ZHCSFO5-NOVEMBER 2016

# TPS25810-Q1 具有负载检测功能的 USB Type-C DFP 控制器和电源开关

Technical

Documents

🕳 Sample &

🖥 Buy

# 1 特性

- 兼容 USB Type-C 版本 1.2 的下行数据端口 (DFP) 控制器

- 连接器连接或断开检测

- 配置通道 (CC) STD、1.5A、3A 电流能力通告

- 超高速极性确定

- V<sub>BUS</sub> 应用和放电

- V<sub>CONN</sub>应用于电子标记电缆

- 音频和调试附件识别

- 端口未连接时, IDDQ 的典型值为 0.7µA

- 三个输入电源选项

- IN1: USB 充电电源

- IN2: V<sub>CONN</sub> 电源

- AUX: 器件电源

- 电源唤醒可保证系统冬眠 (S4) 和关闭 (S5) 功耗状态下的低功耗

- 34mΩ(典型值)高侧金属氧化物半导体场效应晶 体管 (MOSFET)

- 1.7A 或 3.4A 可编程 ILIM (±7.1%)

- 端口功率管理可实现多端口功率资源优化

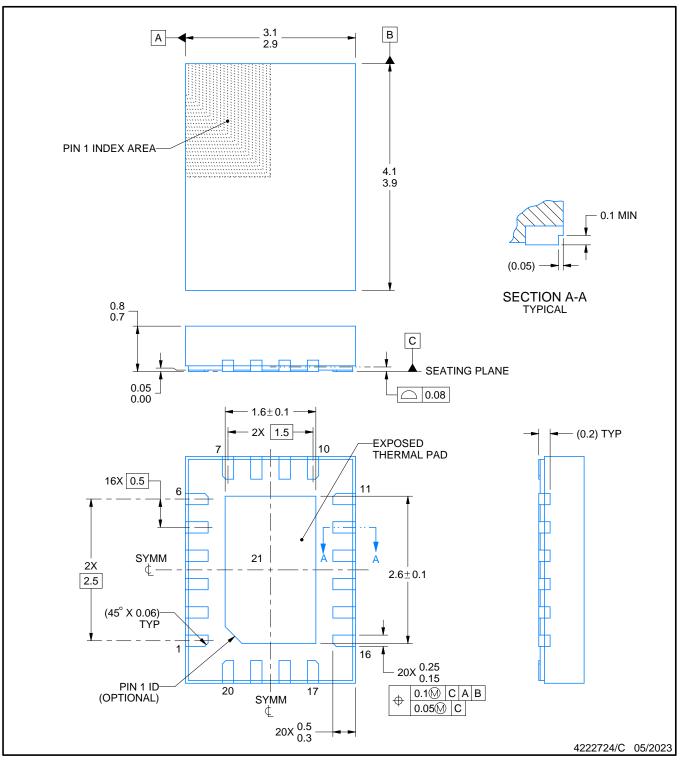

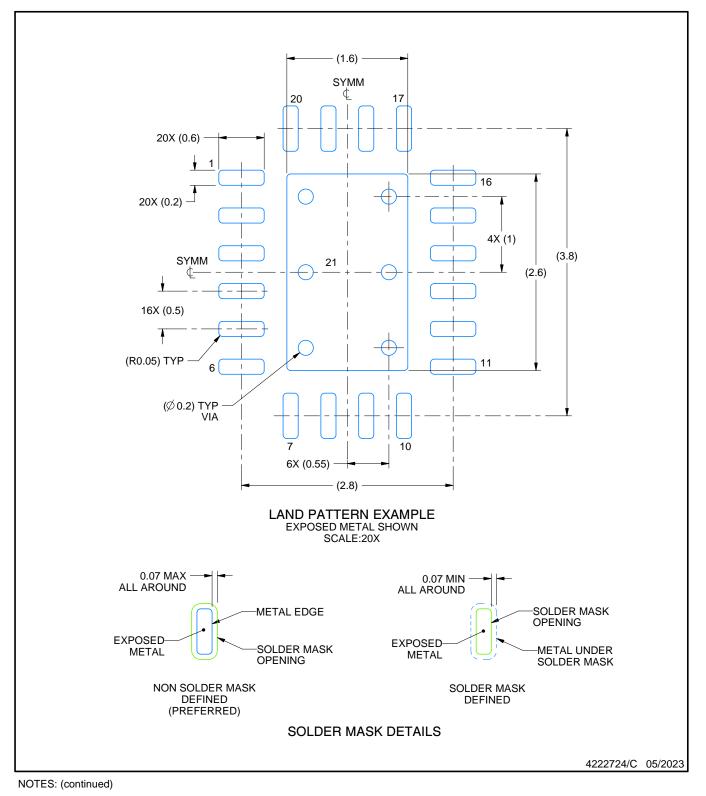

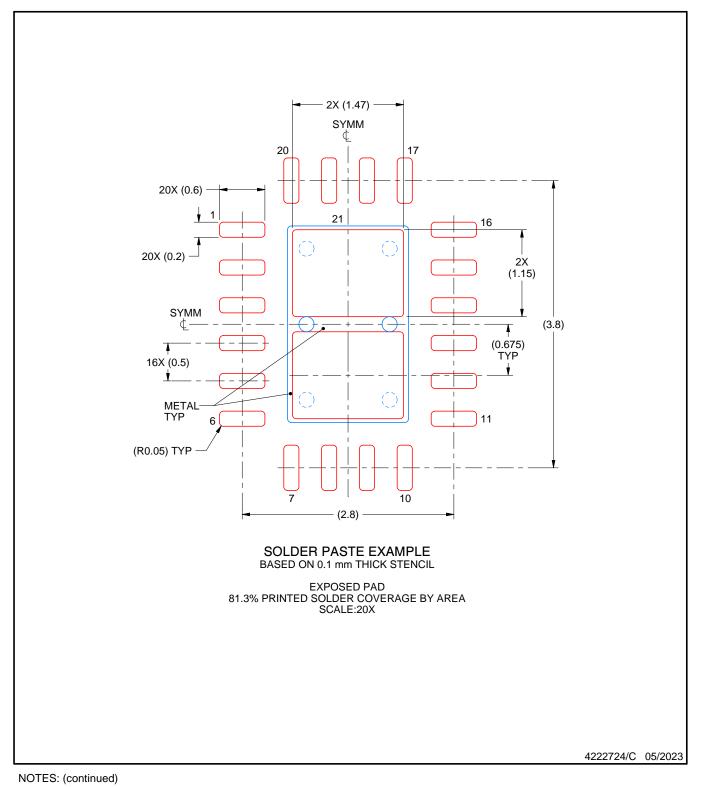

- 封装: 20 引脚晶圆级四方扁平无引线 (WQFN) 封装 (3mm x 4mm)<sup>(1)</sup>

- 2 应用

- 汽车信息娱乐系统

- 汽车后座 USB 充电

- (1) CC 引脚符合 IEC-61000-4-2 标准

3 说明

Tools &

Software

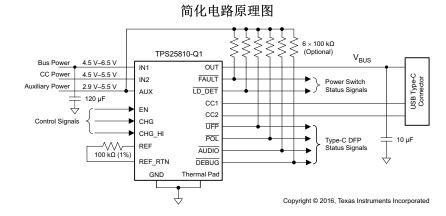

TPS25810-Q1 是一款 USB Type-C 下行数据端口 (DFP) 控制器,集成了一个额定电流为 3A 的 USB 电 源开关。TPS25810-Q1 器件监测 Type-C 配置通道 (CC) 线路,确定 USB 设备何时与其相连。如果连接 与上行数据端口 (UFP) 器件 相连,TPS25810-Q1 可 将电源应用于 V<sub>BUS</sub> 并将可选 V<sub>BUS</sub> 拉电流能力通过 CC 线路传输至 UFP。如果使用以电气方式标记的电 缆连接 UFP,TPS25810-Q1 器件也可以将 V<sub>CONN</sub> 电 源应用于电缆的 CC 引脚。TPS25810-Q1 器件还会识 别何时连接了 Type-C 音频或调试附件。

Support &

Community

2.2

**TPS25810-Q1** 器件在未连接器件时的电流消耗低于 0.7μA(典型值)。在未连接 UFP 时, S4 和 S5 系统 电源使用 UFP 输出禁用 5V 高功率电源,从而进一步 实现系统节能。在此模式下,器件能够由电压较低 (3.3V)的辅助电源 (AUX) 供电运行,该电源通常在低 功耗状态 (S4 和 S5)下为系统微控制器供电。

**TPS25810-Q1 34m**Ω 电源开关具备两种固定电流限值 可供选择,对应于 **Type-C** 电流水平。**FAULT** 输出在 开关处于过流和过热条件时发出信号。在所有端口无法 同时提供高电流 (3A) 的环境下,**LD\_DET** 输出可针对 多个高电流 **Type-C** 端口的功率管理进行控制。

器件信息(1)

| 器件型号        | 封装                       | 封装尺寸(标称值)       |

|-------------|--------------------------|-----------------|

| TPS25810-Q1 | 超薄四方扁平无引线<br>(WQFN) (20) | 3.00mm x 4.00mm |

(1) 要了解所有可用封装,请参见数据表末尾的可订购产品附录。

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

Texas Instruments

# 目录

| 1 | 特性   |                                    |

|---|------|------------------------------------|

| 2 | 应用   |                                    |

| 3 | 说明   | 1                                  |

| 4 | 修订   | 历史记录 2                             |

| 5 | Pin  | Configuration and Functions 3      |

| 6 | Spe  | cifications5                       |

|   | 6.1  | Absolute Maximum Ratings 5         |

|   | 6.2  | ESD Ratings 5                      |

|   | 6.3  | Recommended Operating Conditions 5 |

|   | 6.4  | Thermal Information 6              |

|   | 6.5  | Electrical Characteristics 6       |

|   | 6.6  | Switching Characteristics 8        |

|   | 6.7  | Typical Characteristics 10         |

| 7 | Deta | ailed Description 12               |

|   | 7.1  | Overview 12                        |

|   | 7.2  | Functional Block Diagram 14        |

|   | 7.3  | Feature Description 14             |

|    | 7.4  | Device Functional Modes    | <mark>23</mark> |

|----|------|----------------------------|-----------------|

| 8  | Appl | ication and Implementation | 25              |

|    | 8.1  | Application Information    | 25              |

|    | 8.2  | Typical Applications       | 25              |

| 9  | Powe | er Supply Recommendations  | 30              |

| 10 | Layo | out                        | 31              |

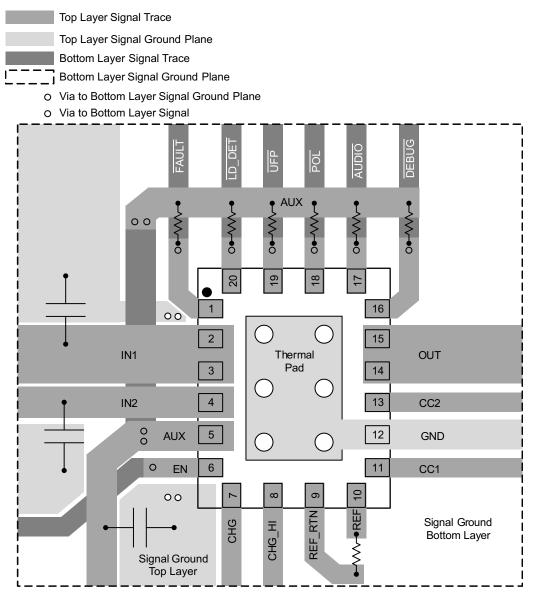

|    | 10.1 | Layout Guidelines          | 31              |

|    | 10.2 | Layout Example             | 32              |

| 11 | 器件   | 和文档支持                      | 33              |

|    | 11.1 | 器件支持                       |                 |

|    | 11.2 | 文档支持                       | 33              |

|    | 11.3 | 接收文档更新通知                   | 33              |

|    | 11.4 | 社区资源                       | <mark>33</mark> |

|    | 11.5 | 商标                         | <mark>33</mark> |

|    | 11.6 | 静电放电警告                     | <mark>33</mark> |

|    | 11.7 | Glossary                   | <mark>33</mark> |

| 12 | 机械   | 、封装和可订购信息                  | 33              |

|    |      |                            |                 |

# 4 修订历史记录

| 日期          | 修订版本 | 注      |  |  |

|-------------|------|--------|--|--|

| 2016 年 11 月 | *    | 最初发布版本 |  |  |

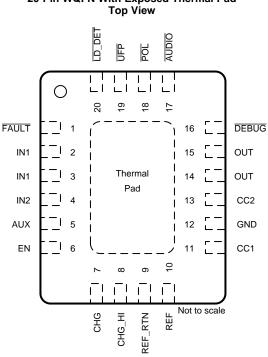

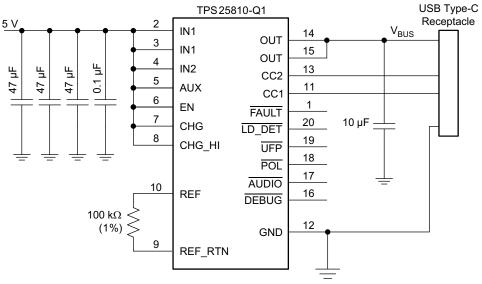

# 5 Pin Configuration and Functions

# **Pin Functions**

| PIN I/O |         | 1/0 | DESCRIPTION                                                                                                                                                                                      |  |

|---------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO.     | NAME    | 1/0 | DESCRIPTION                                                                                                                                                                                      |  |

| 1       | FAULT   | 0   | Fault event indicator. Open-drain logic output that asserts low to indicate a current-limit or thermal-<br>shutdown event due to overtemperature.                                                |  |

| 2       | IN1     | Ι   | V <sub>BUS</sub> input supply. Internal power switch connects IN1 to OUT.                                                                                                                        |  |

| 3       | IN1     | Ι   | V <sub>BUS</sub> input supply. Internal power switch connects IN1 to OUT.                                                                                                                        |  |

| 4       | IN2     | I   | $V_{\rm CONN}$ input supply. Internal power switch connects IN2 to CC1 or CC2. Short to IN1 if only one supply is used.                                                                          |  |

| 5       | AUX     | I   | Auxiliary input supply. Connect to an always-alive system rail to use the power-wake feature. Short to IN1 and IN2 if only one supply is used.                                                   |  |

| 6       | EN      | I   | Enable logic input. Turns the device on and off                                                                                                                                                  |  |

| 7       | CHG     | I   | Charge-logic input to select between standard USB (500 mA for a Type-C receptacle supporting only USB 2.0, and 900 mA for Type-C receptacle supporting USB 3.1) or a Type-C current-sour bility. |  |

| 8       | CHG_HI  | I   | High-charge logic input to select between 1.5-A and 3-A Type-C current sourcing capability. Valid when CHG is set to Type-C current.                                                             |  |

| 9       | REF_RTN | I   | Precision signal-reference return. Connect to the REF pin via a 100-kΩ, 1% resistor.                                                                                                             |  |

| 10      | REF     | I   | Analog input used to generate the internal current reference. Connect a 1% or better, 100-ppm, $100-k\Omega$ resistor between this pin and REF_RTN.                                              |  |

| 11      | CC1     | I/O | Analog input/output that connects to the Type-C receptacle CC1 pin                                                                                                                               |  |

| 12      | GND     | _   | Power ground                                                                                                                                                                                     |  |

| 13      | CC2     | I/O | Analog input/output that connects to the Type-C receptacle CC2 pin.                                                                                                                              |  |

| 14      | OUT     | 0   | Power switch output                                                                                                                                                                              |  |

| 15      | OUT     | 0   | Power switch output                                                                                                                                                                              |  |

| 16      | DEBUG   | 0   | Open-drain logic output that asserts when a Type-C debug accessory is identified on the CC lines.                                                                                                |  |

| 17      | AUDIO   | 0   | Open-drain logic output that asserts when a Type-C audio accessory is identified on the CC lines.                                                                                                |  |

RVC Package 20-Pin WQFN With Exposed Thermal Pad Top View

Texas Instruments

www.ti.com.cn

# Pin Functions (continued)

| Р   | IN          | I/O                                                                                                                                                                                                                                      | DESCRIPTION                                                                                                                                                                                  |

|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME        | 1/0                                                                                                                                                                                                                                      | DESCRIPTION                                                                                                                                                                                  |

|     |             | Polarity open-drain logic output that signals which Type-C CC pin is connected to the CC line. This gives the information needed to multiplex the super-speed lines. Asserted when the CC2 pin is connected to the CC line in the cable. |                                                                                                                                                                                              |

| 19  | UFP         | 0                                                                                                                                                                                                                                        | Open-drain logic output that asserts when a Type-C UFP is identified on the CC lines.                                                                                                        |

| 20  | LD_DET      | 0                                                                                                                                                                                                                                        | Load-detect open-drain logic output that signals when a device set to source Type-C 3-A current is sourcing over 1.95 A, nominal.                                                            |

| _   | Thermal pad | _                                                                                                                                                                                                                                        | Thermal pad on the bottom of the package. The thermal pad is internally connected to GND and is used to heat-sink the device to the circuit board. Connect the thermal pad to the GND plane. |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range, voltages are respect to GND (unless otherwise noted) <sup>(1)</sup>

|                                               |                                                                                           | MIN  | MAX                               | UNIT |

|-----------------------------------------------|-------------------------------------------------------------------------------------------|------|-----------------------------------|------|

|                                               | IN1, IN2, AUX, EN, CHG, CHG_HI, REF, OUT, LD_DET, FAULT, CC1, CC2, UFP, POL, AUDIO, DEBUG | -0.3 | 7                                 | V    |

| Pin voltage, V                                | REF_RTN                                                                                   |      | Internally<br>connected<br>to GND | V    |

| Pin positive source current, I <sub>SRC</sub> | OUT, REF, CC1, CC2                                                                        |      | Internally<br>limited             | А    |

|                                               | OUT (while applying V <sub>BUS</sub> )                                                    |      | 5                                 | А    |

| Pin positive sink current, I <sub>SNK</sub>   | CC1, CC2 (while applying V <sub>CONN</sub> )                                              |      | 1                                 | А    |

| THE POSITIVE ON INCOMONA, ISNK                | LD_DET, FAULT, UFP, POL, AUDIO, DEBUG                                                     |      | Internally<br>limited             | mA   |

| Operating junction temperature, $T_J$         |                                                                                           | -40  | 180                               | °C   |

| Storage temperature range, T <sub>stg</sub>   |                                                                                           | -65  | 150                               | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                   |               |                                                             | VALUE   | UNIT |

|-------------------|---------------|-------------------------------------------------------------|---------|------|

|                   |               | Human-body model (HBM), per per AEC Q100-002 <sup>(2)</sup> | ±2 000  |      |

| V (1)             | Electrostatic | Charged-device model (CDM), per per AEC Q100-011            | ±500    | V    |

| $V_{(ESD)}^{(1)}$ | discharge     | 61000-4-2 contact discharge, CC1 and CC2 <sup>(3)</sup> IEC | ±8 000  | v    |

|                   |               | IEC 61000-4-2 air discharge, CC1 and CC2 <sup>(3)</sup>     | ±15 000 |      |

(1) Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges into the device.

(2) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

(3) Surges per IEC61000-402, 1999 applied between CC1/CC2 and output ground of the TPS25810EVM-745.

# 6.3 Recommended Operating Conditions

Voltages are with respect to GND (unless otherwise noted)

|                        |                                              |                                               | MIN  | NOM | MAX             | UNIT |

|------------------------|----------------------------------------------|-----------------------------------------------|------|-----|-----------------|------|

|                        |                                              | IN1                                           | 4.5  |     | 6.5             |      |

| V <sub>IN</sub>        | Supply voltage                               | IN2                                           | 4.5  |     | 5.5             | V    |

|                        |                                              | AUX                                           | 2.9  |     | 5.5             |      |

| VI                     | Input voltage                                | EN, CHG, CHG_HI                               | 0    |     | 5.5             | V    |

| VIH                    | High-level input voltage                     | EN, CHG, CHG_HI                               | 1.17 |     |                 | V    |

| VIL                    | Low-level voltage                            | EN, CHG, CHG_HI                               |      |     | 0.63            | V    |

| V <sub>PU</sub>        | Pullup voltage                               | Used on LD_DET, FAULT, UFP, POL, AUDIO, DEBUG | 0    |     | 5.5             | V    |

|                        |                                              | OUT                                           |      |     | 3               | А    |

| I <sub>SRC</sub>       | Positive source current                      | CC1 or CC2 when supplying VCONN               |      |     | 250             | mA   |

| I <sub>SNK</sub>       | Positive sink current (10 ms moving average) | LD_DET, FAULT, UFP, POL, AUDIO, DEBUG         |      |     | 10              | mA   |

| I <sub>SNK_PULSE</sub> | Positive repetitive pulse sink current       | LD_DET, FAULT, UFP, POL, AUDIO, DEBUG         |      |     | rnally<br>mited | mA   |

| R <sub>REF</sub>       | Reference resistor                           |                                               | 98   | 100 | 102             | kΩ   |

| TJ                     | Operating junction temperature               |                                               | -40  |     | 125             | °C   |

TEXAS INSTRUMENTS

www.ti.com.cn

# 6.4 Thermal Information

|                       | THERMAL METRIC <sup>(1)</sup> Junction-to-ambient thermal resistance | TPS25810-Q1 |      |

|-----------------------|----------------------------------------------------------------------|-------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                                        | RVC (WQFN)  | UNIT |

|                       |                                                                      | 20 PINS     |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance                               | 39.3        | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance                            | 43.4        | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance                                 | 13          | °C/W |

| ΨJT                   | Junction-to-top characterization parameter                           | 0.7         | °C/W |

| Ψјв                   | Junction-to-board characterization parameter                         | 13          | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance                         | 4.2         | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

# 6.5 Electrical Characteristics

$-40^{\circ}C \le T_{J} \le 125^{\circ}C$ ,  $4.5 \ V \le V_{IN1} \le 6.5 \ V$ ,  $4.5 \ V \le V_{IN2} \le 5.5 \ V$ ,  $2.9 \ V \le V_{AUX} \le 5.5 \ V$ ;  $V_{EN} = V_{CHG} = V_{CHG_{-HI}} = V_{AUX}$ ,  $R_{REF} = 100 \ k\Omega$ . Typical values are at 25°C. All voltages are with respect to GND.  $I_{OUT}$  and  $I_{OS}$  defined positive out of the indicated pin (unless otherwise noted)

|                     | PARAMETER                                                 | TEST CONDITIONS                                                                                                                                                                                                                      | MIN  | TYP  | MAX  | UNIT |

|---------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| OUT – PO            | WER SWITCH                                                |                                                                                                                                                                                                                                      |      |      |      |      |

|                     |                                                           | $T_{J} = 25^{\circ}C, I_{OUT} = 3 A$                                                                                                                                                                                                 |      | 34   | 37   |      |

| r <sub>DS(on)</sub> | On-resistance <sup>(1)</sup>                              | $-40^{\circ}C \le T_J \le 85^{\circ}C$ , $I_{OUT} = 3 \text{ A}$                                                                                                                                                                     |      | 34   | 46   | mΩ   |

|                     |                                                           | $-40^{\circ}C \le T_J \le 125^{\circ}C$ , $I_{OUT} = 3 A$                                                                                                                                                                            |      | 34   | 55   |      |

| I <sub>REV</sub>    | OUT to IN reverse leakage current                         | $ \begin{split} &V_{OUT} = 6.5 \text{ V}, V_{\text{IN1}} = V_{\text{EN}} = 0 \text{ V}, \\ &-40^{\circ}\text{C} \leq \text{T}_{\text{J}} \leq 85^{\circ}\text{C}, \\ &I_{\text{REV}} \text{ is current out of IN1 pin} \end{split} $ |      | 0    | 3    | μA   |

| OUT – CU            | IRRENT LIMIT                                              |                                                                                                                                                                                                                                      |      |      |      |      |

|                     | (4)                                                       | $V_{CHG}$ = 0 V or $V_{CHG}$ = $V_{AUX}$ and $V_{CHG\_HI}$ = 0 V                                                                                                                                                                     | 1.58 | 1.7  | 1.82 |      |

| los                 | Short circuit current limit <sup>(1)</sup>                |                                                                                                                                                                                                                                      | 3.16 | 3.4  | 3.64 | A    |

|                     |                                                           | R <sub>REF</sub> = 10 Ω                                                                                                                                                                                                              |      |      | 7    |      |

| OUT – DIS           | SCHARGE                                                   |                                                                                                                                                                                                                                      |      |      |      |      |

|                     | Discharge resistance                                      | $V_{OUT}$ = 4 V, UFP signature removed from<br>CC lines, time < $t_{w_DCHG}$                                                                                                                                                         | 400  | 500  | 600  | Ω    |

|                     | Bleed discharge resistance                                | $V_{OUT}$ = 4 V, No UFP signature on CC lines,<br>time > t <sub>w_DCHG</sub>                                                                                                                                                         | 100  | 150  | 250  | kΩ   |

| REF                 |                                                           | +                                                                                                                                                                                                                                    |      |      |      |      |

| Vo                  | Output voltage                                            |                                                                                                                                                                                                                                      | 0.78 | 0.8  | 0.82 | V    |

| I <sub>OS</sub>     | Short circuit current                                     | R <sub>REF</sub> = 10 Ω                                                                                                                                                                                                              | 9.5  |      | 15.3 | μA   |

| FAULT               |                                                           |                                                                                                                                                                                                                                      |      |      |      |      |

| V <sub>OL</sub>     | Output low voltage                                        | $I_{FAULT} = 1 \text{ mA}$                                                                                                                                                                                                           |      |      | 350  | mV   |

| I <sub>OFF</sub>    | Off-state leakage                                         | $V_{FAULT} = 5.5 V$                                                                                                                                                                                                                  |      |      | 1    | μA   |

| LD_DET              |                                                           |                                                                                                                                                                                                                                      |      |      |      |      |

| V <sub>OL</sub>     | Output low voltage                                        | $I_{LD_DET} = 1 \text{ mA}$                                                                                                                                                                                                          |      |      | 350  | mV   |

| I <sub>OFF</sub>    | Off-state leakage                                         | $V_{LD_DET} = 5.5 V$                                                                                                                                                                                                                 |      |      | 1    | μA   |

| I <sub>TH</sub>     | OUT sourcing, rising threshold<br>current for load detect |                                                                                                                                                                                                                                      | 1.8  | 1.95 | 2.1  | А    |

|                     | Hysteresis <sup>(2)</sup>                                 |                                                                                                                                                                                                                                      |      | 125  |      | mA   |

(1) Pulse-testing techniques maintain junction temperature close to ambient temperature; thermal effects must be taken into account separately.

(2) These parameters are provided for reference only and do not constitute part of TI's published specifications for purposes of TI's product warranty.

# **Electrical Characteristics (continued)**

$-40^{\circ}C \le T_{J} \le 125^{\circ}C$ ,  $4.5 \text{ V} \le V_{IN1} \le 6.5 \text{ V}$ ,  $4.5 \text{ V} \le V_{IN2} \le 5.5 \text{ V}$ ,  $2.9 \text{ V} \le V_{AUX} \le 5.5 \text{ V}$ ;  $V_{EN} = V_{CHG} = V_{CHG_{HI}} = V_{AUX}$ ,  $R_{REF} = 100 \text{ k}\Omega$ . Typical values are at 25°C. All voltages are with respect to GND.  $I_{OUT}$  and  $I_{OS}$  defined positive out of the indicated pin (unless otherwise noted)

|                                                    | PARAMETER                                                                         | TEST CONDITIONS                                                                                                                                 | MIN  | TYP   | MAX         | UNIT     |

|----------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------------|----------|

| CC1, CC2 – \                                       | / <sub>CONN</sub> POWER SWITCH                                                    |                                                                                                                                                 |      |       |             |          |

|                                                    |                                                                                   | T <sub>J</sub> = 25°C, I <sub>OUT</sub> = 250 mA                                                                                                |      | 365   | 420         |          |

| r <sub>DS(on)</sub>                                | On-resistance                                                                     | –40°C ≤ T <sub>J</sub> ≤ 85°C, I <sub>OUT</sub> = 250 mA                                                                                        |      | 365   | 530         | mΩ       |

| . ,                                                |                                                                                   | –40°C ≤ T <sub>J</sub> ≤ 125°C, I <sub>OUT</sub> = 250 mA                                                                                       |      | 365   | 600         |          |

| CC1, CC2 – \                                       | / <sub>CONN</sub> POWER SWITCH – CURREN                                           | T LIMIT                                                                                                                                         |      |       |             |          |

|                                                    |                                                                                   |                                                                                                                                                 | 300  | 355   | 410         |          |

| l <sub>OS</sub>                                    | Short-circuit current limit <sup>(1)</sup>                                        | R <sub>REF</sub> = 10 Ω                                                                                                                         |      |       | 800         | mA       |

| CC1, CC2 – C                                       | CONNECT MANAGEMENT – DANGI                                                        | LING ELECTRONICALLY MARKED CABLE N                                                                                                              | IODE |       |             |          |

|                                                    | Sourcing current on the pass-<br>through CC Line                                  | $0 \text{ V} \leq \text{V}_{\text{CCx}} \leq 1.5 \text{ V}$                                                                                     | 64   | 80    | 96          |          |

| I <sub>SRC</sub>                                   | Sourcing current on the Ra CC line                                                | $0 \text{ V} \leq \text{V}_{\text{CCx}} \leq 1.5 \text{ V}$                                                                                     | 64   | 80    | 96          | μA       |

| CC1, CC2 – C                                       | CONNECT MANAGEMENT - ACCES                                                        | SSORY MODE                                                                                                                                      |      |       | ù           |          |

| I                                                  | CCx sourcing current<br>(CC2 – audio, CC1-debug)                                  | $0 \text{ V} \leq \text{V}_{\text{CCx}} \leq 1.5 \text{ V}$                                                                                     | 64   | 80    | 96          |          |

| I <sub>SRC</sub>                                   | CCx sourcing current<br>(CC1 – audio, CC2-debug) <sup>(2)</sup>                   | $0 \text{ V} \leq \text{V}_{\text{CCx}} \leq 1.5 \text{ V}$                                                                                     |      | 0     |             | μA       |

| CC1, CC2 – C                                       | CONNECT MANAGEMENT – UFP M                                                        | ODE                                                                                                                                             |      |       |             |          |

| I <sub>SRC</sub>                                   | Sourcing current with either IN1 or IN2 in UVLO                                   | 0 V $\leq$ V <sub>CCx</sub> $\leq$ 1.5 V<br>V <sub>IN1</sub> $<$ V <sub>TH_UVLO_IN1</sub> or V <sub>IN2</sub> $<$ V <sub>TH_UVLO_IN2</sub>      | 64   | 80    | 96          | μA       |

|                                                    |                                                                                   | $V_{CHG} = 0 V$ and $V_{CHG_HI} = 0 V$<br>0 V $\leq V_{CCx} \leq 1.5 V$                                                                         | 75   | 80    | 85          | -        |

| I <sub>SRC</sub>                                   | Sourcing current                                                                  | $V_{CHG} = V_{AUX}$ and $V_{CHG_HI} = 0 V$<br>0 V $\leq V_{CCX} \leq 1.5 V$                                                                     | 170  | 180   | 190         | μA       |

|                                                    |                                                                                   | $V_{CHG} = V_{AUX}$ and $V_{CHG_{HI}} = V_{AUX}$<br>0 V $\leq V_{CCX} \leq 2.45$ V                                                              | 312  | 330   | 348         |          |

| UFP, POL, A                                        | UDIO, DEBUG                                                                       |                                                                                                                                                 |      |       | <u>r</u>    |          |

| V <sub>OL</sub>                                    | Output low voltage                                                                | I <sub>SNK_PIN</sub> = 1 mA                                                                                                                     |      |       | 250         | mV       |

| I <sub>OFF</sub>                                   | Off-state leakage                                                                 | V <sub>PIN</sub> = 5.5 V                                                                                                                        |      |       | 1           | μA       |

| EN, CHG, CH                                        | IG_HI – LOGIC INPUTS                                                              |                                                                                                                                                 |      |       | ·           |          |

| V <sub>TH</sub>                                    | Rising threshold voltage                                                          |                                                                                                                                                 |      | 0.925 | 1.15        | V        |

| V <sub>TH</sub>                                    | Falling threshold voltage                                                         |                                                                                                                                                 | 0.65 | 0.875 |             | V        |

|                                                    | Hysteresis <sup>(2)</sup>                                                         |                                                                                                                                                 |      | 50    |             | mV       |

| I <sub>IN</sub>                                    | Input current                                                                     | V <sub>EN</sub> = 0 V or 6.5 V                                                                                                                  | -0.5 |       | 0.5         | μA       |

|                                                    | RATURE SHUTDOWN                                                                   |                                                                                                                                                 |      |       | ł           |          |

| T <sub>TH_OTSD2</sub>                              | Rising threshold temperature for device shutdown                                  |                                                                                                                                                 | 155  |       |             | °C       |

|                                                    | Hysteresis <sup>(2)</sup>                                                         |                                                                                                                                                 |      | 20    |             | °C       |

| T <sub>TH_OTSD1</sub>                              | Rising threshold temperature for OUT/ $V_{CONN}$ switch shutdown in current limit |                                                                                                                                                 | 135  |       |             | °C       |

|                                                    | Hysteresis <sup>(2)</sup>                                                         |                                                                                                                                                 |      | 20    |             | °C       |

| IN1                                                | 1900000                                                                           | <u> </u>                                                                                                                                        |      | 20    |             | U        |

| V <sub>TH_UVLO_IN1</sub>                           | Rising threshold voltage for UVLO                                                 |                                                                                                                                                 | 3.9  | 4.1   | 4.3         | V        |

| • TH_UVLU_IN1                                      | Hysteresis <sup>(2)</sup>                                                         |                                                                                                                                                 | 0.0  | 100   | т. <b>उ</b> | mV       |

|                                                    | Disabled supply current                                                           | V <sub>EN</sub> = 0 V, −40°C ≤ T <sub>J</sub> ≤ 85°C                                                                                            |      | 100   | 1           | μA       |

| I <sub>IN1(DIS)</sub><br>I <sub>IN1(CC_OPEN)</sub> | Enabled supply current with CC lines open                                         | $v_{\text{EN}} = 0 \ \text{v}, -40 \ \text{C} \le T_{\text{J}} \le 85 \ \text{C}$ $-40^{\circ}\text{C} \le T_{\text{J}} \le 85^{\circ}\text{C}$ |      |       | 1           | μΑ<br>μΑ |

# **Electrical Characteristics (continued)**

$-40^{\circ}C \le T_{J} \le 125^{\circ}C$ ,  $4.5 \text{ V} \le V_{IN1} \le 6.5 \text{ V}$ ,  $4.5 \text{ V} \le V_{IN2} \le 5.5 \text{ V}$ ,  $2.9 \text{ V} \le V_{AUX} \le 5.5 \text{ V}$ ;  $V_{EN} = V_{CHG} = V_{CHG\_HI} = V_{AUX}$ ,  $R_{REF} = 100 \text{ k}\Omega$ . Typical values are at 25°C. All voltages are with respect to GND.  $I_{OUT}$  and  $I_{OS}$  defined positive out of the indicated pin (unless otherwise noted)

|                           | PARAMETER                                                                                                                          | TEST CONDITIONS                                                                            | MIN  | TYP  | MAX  | UNIT |  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------|------|------|------|--|

| I <sub>IN1(Ra)</sub>      | Enabled supply current with<br>accessory or dangling<br>electronically marked cable<br>signature on CC lines                       |                                                                                            |      |      | 2    | μA   |  |

| I <sub>IN1(Rd)</sub>      | Enabled supply current with UFP attached                                                                                           | $V_{CHG}$ = 0 V, or $V_{CHG}$ = $V_{AUX}$ and $V_{CHG\_HI}$ = 0 V                          |      | 75   | 100  | μA   |  |

| . ,                       | allacheu                                                                                                                           |                                                                                            |      | 85   | 110  |      |  |

| IN2                       |                                                                                                                                    |                                                                                            |      |      |      |      |  |

| V <sub>TH_UVLO_IN2</sub>  | Rising threshold voltage for UVLO                                                                                                  |                                                                                            | 3.9  | 4.1  | 4.3  | V    |  |

|                           | Hysteresis <sup>(2)</sup>                                                                                                          |                                                                                            |      | 100  |      | mV   |  |

| I <sub>IN2(DIS)</sub>     | Disabled supply current                                                                                                            | $V_{EN} = 0 \text{ V}, -40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 85^{\circ}\text{C}$ |      |      | 1    | μA   |  |

| I <sub>IN2(CC_OPEN)</sub> | Enabled supply current with CC lines open                                                                                          | $-40^{\circ}C \le T_{J} \le 85^{\circ}C$                                                   |      |      | 1    | μA   |  |

| I <sub>IN2(Ra)</sub>      | Enabled supply current with<br>accessory or dangling<br>electronically marked cable<br>signature on CC lines                       |                                                                                            |      |      | 2    | μA   |  |

| I <sub>IN2(Rd)</sub>      | Enabled supply current with UFP<br>signature on CC lines<br>(Includes IN current that provides<br>the CC output current to the UFP | $V_{CHG} = 0 \text{ V}, 0 \text{ V} \le V_{CCx} \le 1.5 \text{ V}$                         |      | 98   | 110  | 5 μΑ |  |

|                           |                                                                                                                                    | $V_{CHG}$ = $V_{IN}$ and $V_{CHG\_HI}$ = 0 V, 0 V $\leq$ $V_{CCx}$ $\leq$ 1.5 V            |      | 198  | 215  |      |  |

|                           | Rd resistor)                                                                                                                       | $0 \vee \leq V_{CCx} \leq 2.45 \vee$                                                       |      | 348  | 373  |      |  |

| AUX                       |                                                                                                                                    |                                                                                            |      |      | k    |      |  |

| V <sub>TH_UVLO_AUX</sub>  | Rising threshold voltage for UVLO                                                                                                  |                                                                                            | 2.65 | 2.75 | 2.85 | V    |  |

|                           | Hysteresis <sup>(2)</sup>                                                                                                          |                                                                                            |      | 100  |      | mV   |  |

| I <sub>AUX(DIS)</sub>     | Disabled supply current                                                                                                            | $V_{EN} = 0 \text{ V}, -40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 85^{\circ}\text{C}$ |      |      | 1    | μA   |  |

| I <sub>AUX(CC_OPEN)</sub> | Enabled internal supply current with CC lines open                                                                                 | 40°C ≤ T <sub>J</sub> ≤ 85°C                                                               |      | 0.7  | 3    | μA   |  |

| I <sub>AUX(Ra)</sub>      | Enabled supply current with<br>accessory or dangling active cable<br>signature on CC lines                                         |                                                                                            |      | 140  | 185  | μA   |  |

| I <sub>AUX(Rd_noIN)</sub> | Enabled supply current with UFP<br>termination on CC lines and with<br>either IN1 or IN2 in UVLO                                   | $V_{IN1} < V_{TH_UVLO_IN1}$ or $V_{IN2} < V_{TH_UVLO_IN2}$                                 |      | 145  | 190  | μA   |  |

| I <sub>AUX(Rd)</sub>      | Enabled supply current with UFP termination on CC lines                                                                            |                                                                                            |      | 55   | 82   | μA   |  |

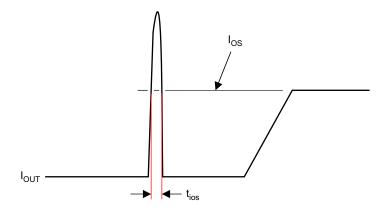

# 6.6 Switching Characteristics

$-40^{\circ}C \le T_{J} \le 125^{\circ}C$ , 4.5 V  $\le V_{IN1} \le 6.5$  V, 4.5 V  $\le V_{IN2} \le 5.5$  V, 2.9 V  $\le V_{AUX} \le 5.5$  V;  $V_{EN} = V_{CHG} = V_{CHG}$  =  $V_{AUX}$ ,  $R_{REF} = 100 \text{ k}\Omega$ . Typical values are at 25°C. All voltages are with respect to GND.  $I_{OUT}$  and  $I_{OS}$  defined positive out of the indicated pin (unless otherwise noted)

|                  | PARAMETER                                    | TEST CONDITIONS                                                                        | MIN  | TYP  | MAX  | UNIT |  |  |  |  |  |

|------------------|----------------------------------------------|----------------------------------------------------------------------------------------|------|------|------|------|--|--|--|--|--|

| OUT – I          | OUT – POWER SWITCH                           |                                                                                        |      |      |      |      |  |  |  |  |  |

| t <sub>r</sub>   | Output-voltage rise time                     | $V_{IN1} = 5 \text{ V}, \text{ C}_{L} = 1 \ \mu\text{F}, \text{ R}_{L} = 100 \ \Omega$ | 1.2  | 1.8  | 2.5  | ms   |  |  |  |  |  |

| t <sub>f</sub>   | Output-voltage fall time                     | (measured from 10% to 90% of final value)                                              | 0.35 | 0.55 | 0.75 | ms   |  |  |  |  |  |

| t <sub>on</sub>  | Output-voltage turnon time                   |                                                                                        | 2.5  | 3.5  | 5    | ms   |  |  |  |  |  |

| t <sub>off</sub> | Output-voltage turnoff time                  | $V_{IN1} = 5 V, C_L = 1 \mu F, R_L = 100 \Omega$                                       | 2    | 3    | 4.5  | ms   |  |  |  |  |  |

| OUT – O          | OUT – CURRENT LIMIT                          |                                                                                        |      |      |      |      |  |  |  |  |  |

| t <sub>ios</sub> | Current-limit response time to short circuit | $V_{\text{IN1}}-V_{\text{OUT}}$ = 1 V, RL = 10 m\Omega, see Figure 1                   |      | 1.5  | 4    | μs   |  |  |  |  |  |

# **Switching Characteristics (continued)**

$-40^{\circ}C \le T_{J} \le 125^{\circ}C$ , 4.5 V  $\le V_{IN1} \le 6.5$  V, 4.5 V  $\le V_{IN2} \le 5.5$  V, 2.9 V  $\le V_{AUX} \le 5.5$  V;  $V_{EN} = V_{CHG} = V_{CHG_{HI}} = V_{AUX}$ ,  $R_{REF} = 100 \text{ k}\Omega$ . Typical values are at 25°C. All voltages are with respect to GND.  $I_{OUT}$  and  $I_{OS}$  defined positive out of the indicated pin (unless otherwise noted)

|                       | PARAMETER                                                                 | TEST CONDITIONS                                                                                          | MIN  | TYP  | MAX  | UNIT |

|-----------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------|------|------|------|

| FAULT                 |                                                                           | · · · · · ·                                                                                              |      |      |      |      |

| t <sub>DEGA</sub>     | Asserting deglitch due to overcurrent                                     |                                                                                                          | 5.5  | 8.2  | 10.7 | ms   |

| t <sub>DEGA(OC)</sub> | Asserting deglitch due to overtemperature in current limit <sup>(1)</sup> |                                                                                                          |      | 0    |      | ms   |

| t <sub>DEGA(OT)</sub> | Deasserting deglitch                                                      |                                                                                                          | 5.5  | 8.2  | 10.7 | ms   |

| LD_DET                |                                                                           |                                                                                                          |      |      | ·    |      |

| t <sub>DEGA</sub>     | Asserting deglitch                                                        |                                                                                                          | 45   | 65   | 85   | ms   |

| t <sub>DEGD</sub>     | Deasserting deglitch                                                      |                                                                                                          | 1.45 | 2.15 | 2.9  | s    |

| OUT – DIS             | CHARGE                                                                    |                                                                                                          |      |      |      |      |

|                       | R <sub>DCHG</sub> discharge time                                          | V <sub>OUT</sub> = 1 V, time I <sub>SNK_OUT</sub> > 1 mA<br>after UFP signature removed from<br>CC lines | 39   | 65   | 96   | ms   |

| CC1, CC2              | - V <sub>CONN</sub> POWER SWITCH                                          |                                                                                                          |      |      | ·    |      |

| t <sub>r</sub>        | Output voltage rise time                                                  | $V_{IN2} = 5 V, C_L = 1 \mu F, R_L = 100 \Omega$                                                         | 0.15 | 0.25 | 0.35 | ms   |

| t <sub>f</sub>        | Output voltage fall time                                                  | (measured from 10% to 90% of final value)                                                                | 0.18 | 0.22 | 0.26 | ms   |

| t <sub>on</sub>       | Output voltage turnon time                                                | $V_{IN2} = 5 V, C_I = 1 \mu F, R_I = 100 \Omega$                                                         | 1    | 1.5  | 2    | ms   |

| t <sub>off</sub>      | Output voltage turnoff time                                               | $v_{IN2} = 5 v, C_L = 1 \mu F, R_L = 100 \Omega$                                                         | 0.3  | 0.4  | 0.55 | ms   |

| CC1, CC2              | - V <sub>CONN</sub> POWER SWITCH - CURREN                                 | T LIMIT                                                                                                  |      |      |      |      |

| t <sub>res</sub>      | Current limit response time to short circuit                              | $V_{\text{IN2}}-V_{\text{CONN}}$ = 1 V, R = 10 m $\Omega,$ see Figure 1                                  |      | 1    | 3    | μs   |

| UFP, POL              | , AUDIO, DEBUG                                                            |                                                                                                          |      |      |      |      |

| t <sub>DEGR</sub>     | Asserting deglitch                                                        |                                                                                                          | 100  | 150  | 200  | ms   |

| t <sub>DEGF</sub>     | Deasserting deglitch                                                      |                                                                                                          | 7.9  | 12.5 | 17.7 | ms   |

(1) These parameters are provided for reference only and do not constitute part of TI's published specifications for purposes of TI's product warranty.

#### TPS25810-Q1 ZHCSF05 – NOVEMBER 2016

www.ti.com.cn

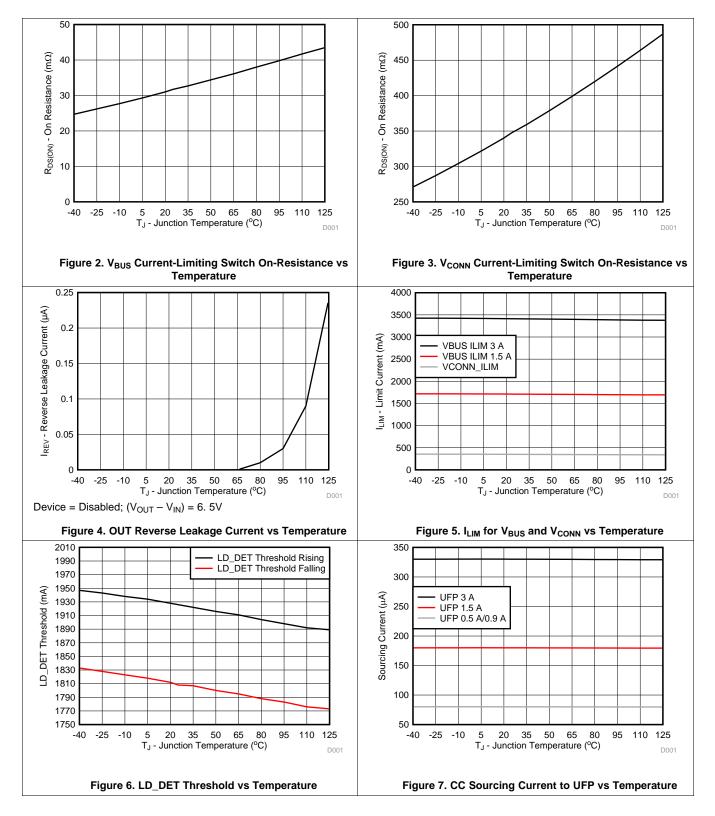

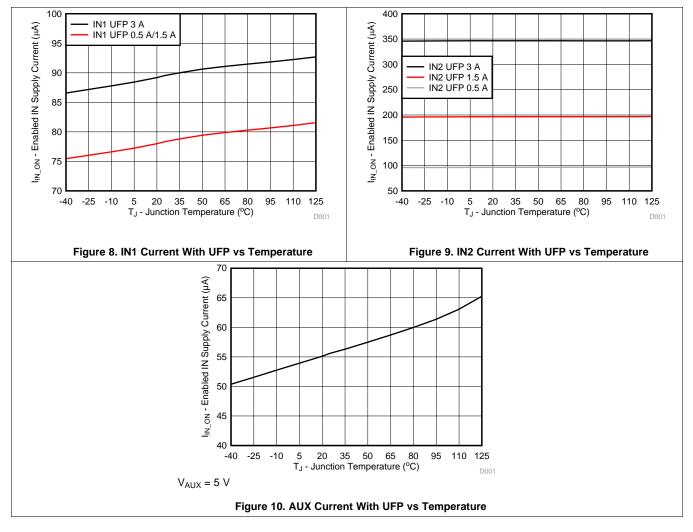

# **Typical Characteristics (continued)**

# 7 Detailed Description

# 7.1 Overview

The TPS25810-Q1 device is a highly integrated USB Type-C<sup>TM</sup> downstream-facing port (DFP) controller with built-in power switch developed for the new USB Type-C connector and cable. The device provides all of the functionality needed to support a USB Type-C DFP in a system where USB power delivery (PD) source capabilities (for example,  $V_{BUS} > 5$  V) are not implemented. The device is designed to be compliant with the Type-C specification, revision 1.1.

### 7.1.1 USB Type-C Basic

For a detailed description of the Type-C specification, see the USB-IF Web site to download the latest released version. Some of the basic concepts of the Type-C specification that pertain to understanding the operation of the TPS25810-Q1 device (a DFP device) are described as follows.

USB Type-C removes the need for different plug and receptacle types for host and device functionality. The Type-C receptacle replaces both Type-A and Type-B receptacles because the Type-C cable is pluggable in either direction between host and device. A host-to-device logical relationship is maintained via the configuration channel (CC). Optionally, hosts and devices can be either providers or consumers of power when USB PD communication is used to swap roles.

All USB Type-C ports operate in one of the following three data modes:

- Host mode: the port can only be host (provider of power).

- Device mode: the port can only be device (consumer of power).

- Dual-role mode: the port can be either host or device.

Port types:

- DFP (downstream facing port): Host

- UFP (upstream facing port): Device

- DRP (dual-role port): Host or device

Valid DFP-to-UFP connections:

- Table 1 describes valid DFP-to-UFP connections.

- Host-to-host and device-to-device have no functions.

#### Table 1. DFP-to-UFP Connections

|                  | HOST-MODE PORT | DEVICE-MODE<br>PORT | DUAL-ROLE PORT       |

|------------------|----------------|---------------------|----------------------|

| Host-mode port   | No function    | Works               | Works                |

| Device-mode port | Works          | No function         | Works                |

| Dual-role port   | Works          | Works               | Works <sup>(1)</sup> |

(1) This may be automatic or manually driven.

### 7.1.2 Configuration Channel

The function of the configuration channel (CC) is to detect connections and configure the interface across the USB Type-C cables and connectors.

Functionally, the configuration channel serves the following purposes:

- Detect connection to the USB ports

- Resolve cable orientation and twist connections to establish USB data bus routing

- Establish DFP and UFP roles between two connected ports

- Discover and configure power: USB Type-C current modes or USB power delivery

- Discover and configure optional alternate and accessory modes

- Enhance flexibility and ease of use

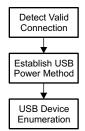

Typical flow of DFP to UFP configuration is shown in Figure 11:

Figure 11. Flow of DFP to UFP Configuration

#### 7.1.3 Detecting a Connection

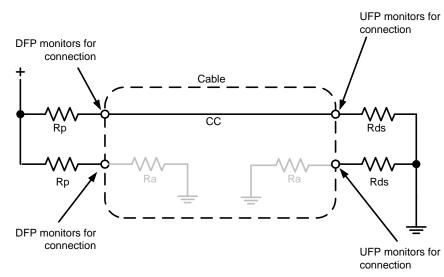

DFPs and DRPs fulfill the role of detecting a valid connection over USB Type-C. Figure 12 shows a DFP-to-UFP connection made with Type-C cable. As shown in Figure 12, the detection concept is based on being able to detect terminations in the product that has been attached. A pullup and pulldown termination model is used. A pullup termination can be replaced by a current source.

- In the DFP-UFP connection, the DFP monitors both CC pins for a voltage lower than the unterminated voltage.

- A UFP advertises Rd on both its CC pins (CC1 and CC2).

- A powered cable advertises Ra on only one of the CC pins of the plug. Ra is used to inform the source to apply  $V_{\text{CONN}}$ .

- An analog audio device advertises Ra on both CC pins of the plug, which identifies it as an analog audio device. V<sub>CONN</sub> is not applied on either CC pin in this case.

Figure 12. DFP-UFP Connection

TPS25810-Q1 ZHCSF05-NOVEMBER 2016 Texas Instruments

www.ti.com.cn

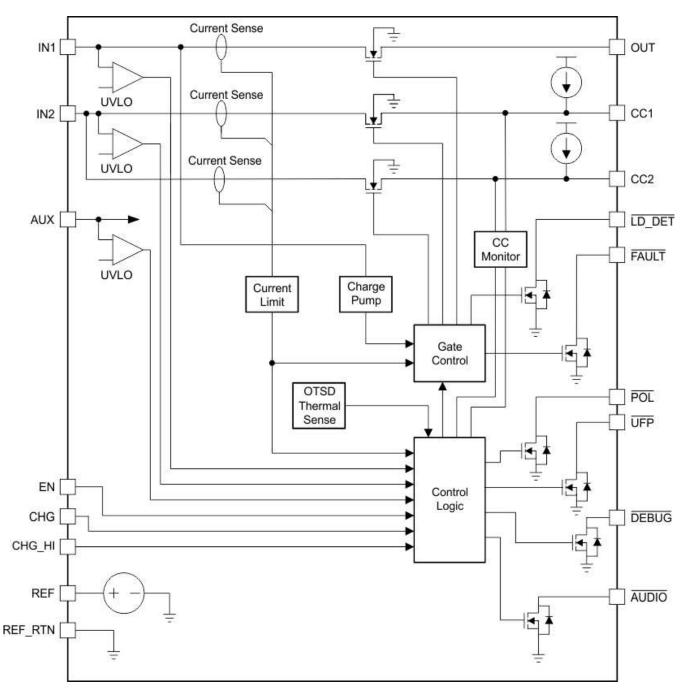

# 7.2 Functional Block Diagram

# 7.3 Feature Description

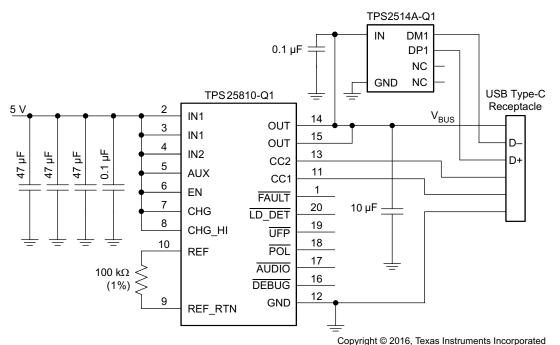

The TPS25810-Q1 device is a DFP Type-C port controller with integrated power switches for  $V_{CONN}$  and  $V_{BUS}$ . The TPS25810-Q1 device does not support BC1.2 charging modes, because it does not interact with USB D+ and D- data lines. The TPS25810-Q1 device can be used in conjunction with a BC 1.2 device like the TPS2514A-Q1 to support BC1.2 and Type-C charging modes in a single Type-C DFP port. See the TPS25810 EVM user's guide (SLVUAI0) and *Application and Implementation* section of this data sheet for more details. The TPS25810-Q1 device can be used in a USB 2.0 only or in a USB 3.1 port implementation. When used in a USB 3.1 port, the TPS25810-Q1 device can control an external super-speed MUX to handle the Type-C flippable feature.

#### **Feature Description (continued)**

#### 7.3.1 Configuration Channel Pins CC1 and CC2

The TPS25810-Q1 device has two pins, CC1 and CC2, that serve to detect an attachment to the port and to resolve cable orientation. These pins are also used to establish the current broadcast to a valid UFP, configure  $V_{\text{CONN}}$ , and detect attachment of a debug or audio-adapter accessory.

Table 2 lists the TPS25810-Q1 response to various attachments to its port.

|                                   |      |      | TPS25810-Q1 RESPONSE <sup>(1)</sup> |                                       |      |      |       |       |  |  |

|-----------------------------------|------|------|-------------------------------------|---------------------------------------|------|------|-------|-------|--|--|

| TPS25810-Q1 TYPE-C PORT           | CC1  | CC2  | Ουτ                                 | V <sub>CONN</sub><br>on CC1 or<br>CC2 | POL  | UFP  | AUDIO | DEBUG |  |  |

| Nothing attached                  | OPEN | OPEN | OPEN                                | NO                                    | Hi-Z | Hi-Z | Hi-Z  | Hi-Z  |  |  |

| UFP connected                     | Rd   | OPEN | IN1                                 | NO                                    | Hi-Z | LOW  | Hi-Z  | Hi-Z  |  |  |

| UFP connected                     | OPEN | Rd   | IN1                                 | NO                                    | LOW  | LOW  | Hi-Z  | Hi-Z  |  |  |

| Powered cable, no UFP connected   | OPEN | Ra   | OPEN                                | NO                                    | Hi-Z | Hi-Z | Hi-Z  | Hi-Z  |  |  |

| Powered cable, no UFP connected   | Ra   | OPEN | OPEN                                | NO                                    | Hi-Z | Hi-Z | Hi-Z  | Hi-Z  |  |  |

| Powered cable, UFP connected      | Rd   | Ra   | IN1                                 | CC2                                   | Hi-Z | LOW  | Hi-Z  | Hi-Z  |  |  |

| Powered cable, UFP connected      | Ra   | Rd   | IN1                                 | CC1                                   | LOW  | LOW  | Hi-Z  | Hi-Z  |  |  |

| Debug accessory connected         | Rd   | Rd   | OPEN                                | NO                                    | Hi-Z | Hi-Z | Hi-Z  | LOW   |  |  |

| Audio-adapter accessory connected | Ra   | Ra   | OPEN                                | NO                                    | Hi-Z | Hi-Z | LOW   | Hi-Z  |  |  |

Table 2. TPS25810-Q1 Response

(1) POL, UFP, AUDIO, and DEBUG are open-drain outputs; pull high with 100 kΩ to AUX when used. Tie to GND or leave open when not used.

#### 7.3.2 Current Capability Advertisement and Overload Protection

The TPS25810-Q1 device supports all three Type-C current advertisements as defined by the USB Type-C standard. Current broadcast to a connected UFP is controlled by the CHG and CHG\_HI pins. For each broadcast level, the device protects itself from a UFP that draws current in excess of the USB Type-C current advertisement of that port by setting the current limit as shown in Table 3.

| CHG | CHG_HI | CC CAPABILITY<br>BROADCAST | CURRENT LIMIT (TYP) | LOAD DETECT<br>THRESHOLD (TYP) |

|-----|--------|----------------------------|---------------------|--------------------------------|

| 0   | 0      | STD                        | 1.7 A               | NA                             |

| 0   | 1      | STD                        | 1.7 A               | NA                             |

| 1   | 0      | 1.5 A                      | 1.7 A               | NA                             |

| 1   | 1      | 3 A                        | 3.4 A               | 1.95 A                         |

#### Table 3. USB Type-C Current Advertisement

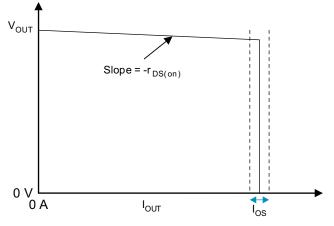

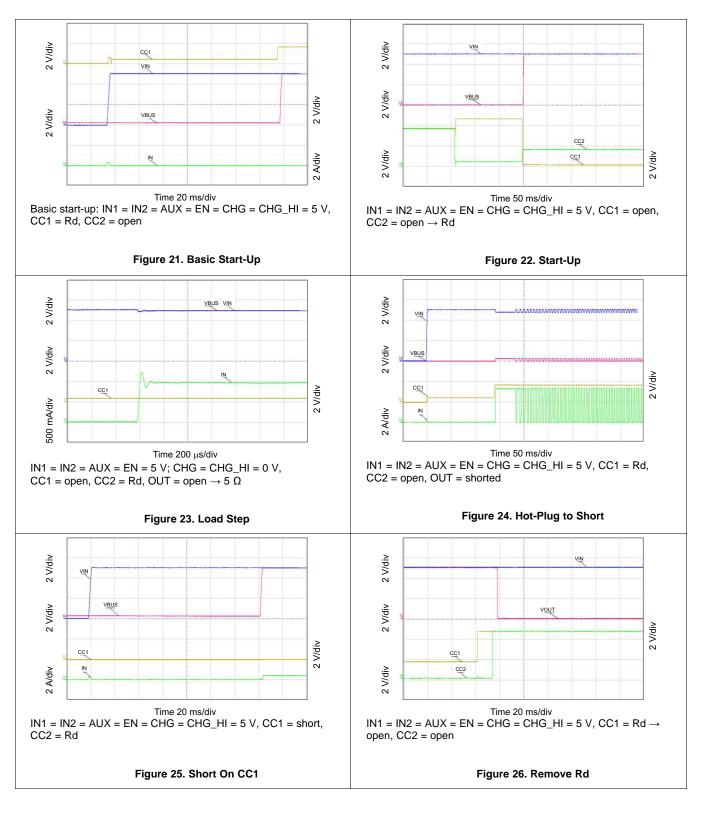

Under OUT overload conditions, an internal OUT current-limit regulator limits the output current to the selected  $I_{LIM}$  based on CHG and CHG\_HI selection. In applications where  $V_{CONN}$  is supplied via CC1 or CC2, separate fixed current-limit regulators protect these pins from overload at the level indicated in the *Electrical Characteristics* table. When an overload condition is present, the device maintains a constant output current, with the output voltage determined by ( $I_{OS} \times R_{LOAD}$ ). Two possible overload conditions can occur. The first overload condition occurs when either: 1) input voltage is first applied, enable is true, and a short circuit is present (load which draws  $I_{OUT} > I_{OS}$ ), or 2) input voltage is present and the TPS25810-Q1 device is enabled into a short circuit. The output voltage is held near zero potential with respect to ground and the TPS25810-Q1 device ramps the output current to  $I_{OS}$ . The TPS25810-Q1 device limits the current to  $I_{OS}$  until the overload condition is removed or the device begins to thermal cycle. This is demonstrated in Figure 24 where the device was enabled into a short, and subsequently cycles current off and on as the thermal protection engages.

The second condition is when an overload occurs while the device is enabled and fully turned on. The device responds to the overload condition within time  $t_{ios}$  (see Figure 1) when the specified overload (per *Electrical Characteristics*) is applied. The response speed and shape vary with the overload level, input circuit, and rate of application. The current-limit response varies between simply settling to  $I_{OS}$  or turnoff and controlled return to  $I_{OS}$ . Similar to the previous case, the TPS25810-Q1 device limits the current to  $I_{OS}$  until the overload condition is removed or the device begins to thermal cycle.

The TPS25810-Q1 device thermal cycles if an overload condition is present long enough to activate thermal limiting in any of the above cases. This is due to the relatively large power dissipation  $[(V_{IN} - V_{OUT}) \times I_{OS}]$  driving the junction temperature up. The device turns off when the junction temperature exceeds 135°C (min) while in current limit. The device remains off until the junction temperature cools 20°C and then restarts. The TPS25810-Q1 current-limit profile is shown in Figure 13.

Figure 13. Current Limit Profile

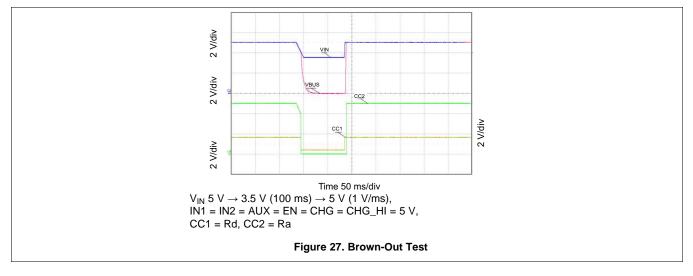

### 7.3.3 Undervoltage Lockout (UVLO)

The undervoltage lockout (UVLO) circuit disables the power switch until the input voltage reaches the UVLO turnon threshold. Built-in hysteresis prevents unwanted on-off cycling due to input voltage droop during turnon.

### 7.3.3.1 Device Power Pins (IN1, IN2, AUX, OUT, and GND)

The device has multiple input power pins: IN1, IN2 and AUX. IN1 is connected to OUT by the internal power FET and serves the supply for the Type-C charging current. IN2 is the supply for  $V_{CONN}$  and ties directly between the  $V_{CONN}$  power switch on its input and CC1 or CC2 on its output. AUX, the auxiliary input supply, provides power to the device. See the *Functional Block Diagram*.

In the simplest implementation where multiple supplies are not available; IN1, IN2, and AUX can be tied together. However, in mobile systems (battery powered) where system power savings is paramount, IN1 and IN2 can be powered by the high-power dc-dc supply (>3-A capability), and AUX can be connected to the low-power supply that typically powers the system microcontroller when the system is in the hibernate or sleep power state. Unlike IN1 and IN2, AUX can operate directly from a 3.3-V supply commonly used to power the microcontroller when the system is put in low-power mode. Ceramic bypass capacitors close to the device from the INx and AUX pins to GND are recommended to alleviate bus transients.

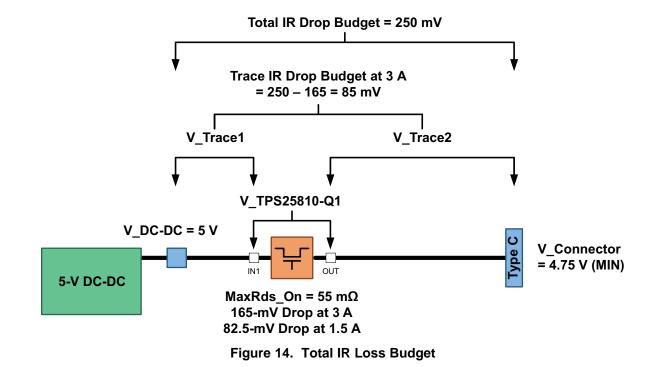

The recommended operating voltage range for IN1 and IN2 is 4.5 V to 5.5 V, whereas AUX can be operated from 2.9 V to 5.5 V. However IN1, the high-power supply, can operate up to 6.5 V. This higher input voltage affords a larger IR loss budget in systems where a long cable harness is used, and results in high IR losses with 3-A charging current. Increasing IN1 beyond 5.5 V enables longer cable and board trace lengths between the device and the Type-C receptacle while meeting the USB specification for  $V_{BUS} \ge 4.75$  V at the connector.

Figure 14 illustrates the point. In this example IN1 is at 5 V, which restricts the IR loss budget from the dc-dc converter to the connector to 250 mV.

#### 7.3.3.2 FAULT Response

The FAULT pin is an open-drain output asserted low when the device OUT current exceeds its programmed value and the overtemperature threshold ( $T_{TH_OTSD1}$ ) is crossed. See the *Electrical Characteristics* for overcurrent and overtemperature values. The FAULT signal remains asserted until the fault condition is removed and the device resumes normal operation. The TPS25810-Q1 device is designed to eliminate false overcurrent fault reporting by using an internal deglitch circuit.

Connect FAULT with a pullup resistor to AUX. FAULT can be left open or tied to GND when not used.

#### 7.3.3.3 Thermal Shutdown

The device has two internal overtemperature shutdown thresholds,  $T_{TH_OTSD1}$  and  $T_{TH_OTSD2}$ , to protect the internal FET from damage and assist with overall safety of the system.  $T_{TH_OTSD2}$  is greater than  $T_{TH_OTSD1}$ . FAULT is asserted low to signal a fault condition when the device temperature exceeds  $T_{TH_OTSD1}$  and the current-limit switch is disabled. However when  $T_{TH_OTSD2}$  is exceeded, all open-drain outputs are left open and the device is disabled such that minimum power and heat are dissipated. The device attempts to power up when the die temperature decreases by 20°C.

#### 7.3.3.4 REF

A 100-k $\Omega$  (1% or better recommended) resistor is connected from this pin to REF\_RTN. The REF pin sets the reference current required to bias the internal circuitry of the device. The overload current-limit tolerance and CC currents depend upon the accuracy of this resistor. Using a ±1% or better low-temperature-coefficient resistor yields the best current-limit accuracy and overall device performance.

#### 7.3.3.5 Audio Accessory Detection

The USB Type-C specification defines an audio-adapter decode state which allows implementation of an analog USB Type-C to 3.5-mm headset adapter. The TPS25810-Q1 device detects an audio accessory device when both CC1 and CC2 pins detect  $V_{Ra}$  voltage (when pulled to ground by an Ra resistor). The device asserts the open-drain AUDIO pin low to indicate the detection of such a device.

Texas Instruments

www.ti.com.cn

#### Table 4. Audio Accessory Detection

| CC1 | CC2 | AUDIO                 | STATE                             |

|-----|-----|-----------------------|-----------------------------------|

| Ra  | Ra  | Asserted (pulled low) | Audio-adapter accessory connected |

Platforms supporting the audio accessory function can be triggered by the AUDIO pin to enable accessory mode circuits to support the audio function. When the Ra pulldown is removed from the CC2 pin, AUDIO is deasserted or pulled high. The TPS25810-Q1 device monitors the CC2 pin for audio device detach. When this function is not needed (for example in a data-less port), AUDIO can be tied to GND or left open.

#### 7.3.3.6 Debug Accessory Detection

The Type-C spec supports an optional debug-accessory mode, used for debug only and not to be used for communicating with commercial products. When the TPS25810-Q1 device detects  $V_{Rd}$  voltage on both CC1 and CC2 pins (when pulled to ground by an Rd resistor), it asserts DEBUG low. With DEBUG asserted, the system can enter debug mode for factory testing or a similar functional mode. DEBUG deasserts or pulls high when Rd is removed from CC1. The TPS25810-Q1 device monitors the CC1 pin for debug-accessory detach.

If the debug-accessory mode is not used, tie DEBUG to GND or leave it open.

#### Table 5. Debug Accessory Detection

| CC1 | CC2 | POL                   | STATE                     |

|-----|-----|-----------------------|---------------------------|

| Rd  | Rd  | Asserted (pulled low) | Debug accessory connected |

#### 7.3.3.7 Plug Polarity Detection

Reversible Type-<u>C plug</u> orientation is reported by the  $\overline{POL}$  pin when a UFP is connected. However, when no UFP is attached POL remains deasserted, irrespective of cable plug orientation. Table 6 describes the POL state based on which of the device CC pins detects V<sub>Rd</sub> from an attached UFP pulldown.

#### Table 6. Plug Polarity Detection

| CC1  | CC2  | POL                   | STATE                                       |

|------|------|-----------------------|---------------------------------------------|

| Rd   | Open | Hi-Z                  | UFP connected                               |

| Open | Rd   | Asserted (pulled low) | UFP connected with reverse plug orientation |

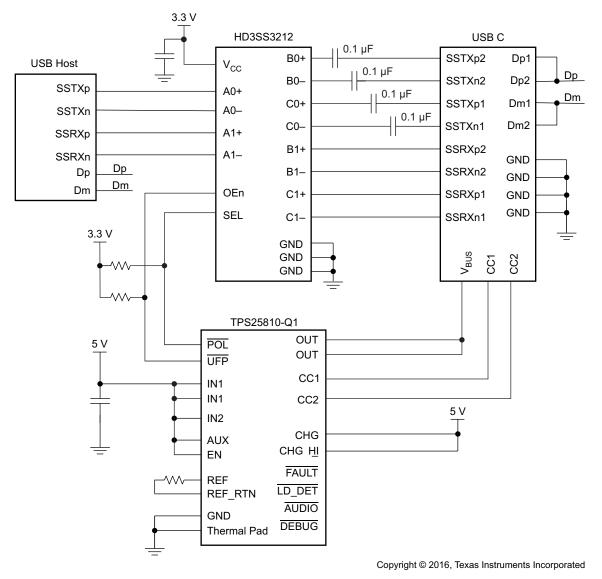

Figure 15 shows an example implementation which uses the POL terminal to control the SEL terminal on the HD3SS3212 device. The HD3SS3212 device provides switching on the differential channels between Port B and Port C to Port A, depending on cable orientation. For details on the HD3SS3212 device, see the HD3SS3212 data sheet (SLASE74).

Figure 15. Example Implementation

#### 7.3.3.8 Device Enable Control

The logic enable pin (EN) controls the power switch and device supply current. The supply current is reduced to less than 1  $\mu$ A when a logic low is present on EN. The EN pin provides a convenient way to turn on or turn off the device while it is powered. The enable input threshold has built-in hysteresis. When this pin is pulled high, the device is turned on or enabled. When the device is disabled (EN pulled low) the internal FETs tied to IN1 and IN2 are disconnected, all open-drain outputs are left open (Hi-Z), and the monitor block for CC1 and CC2 is turned off. The EN terminal should not be left floating.

#### 7.3.3.9 Load Detect

The load-detect function in the device is enabled when the device is set to broadcast high-current V<sub>BUS</sub> charging (CHG = CHG\_HI = High) on the <u>CC</u> pin. In this mode, the device monitors the OUT current to a UFP; if the current exceeds 1.95 A (typ), the <u>LD\_DET</u> pin asserts. Because <u>LD\_DET</u> is an open-drain output, pull it high with 100 k $\Omega$  to AUX when used; tie it to GND or leave it open when not used.

#### 7.3.3.10 Power Wake

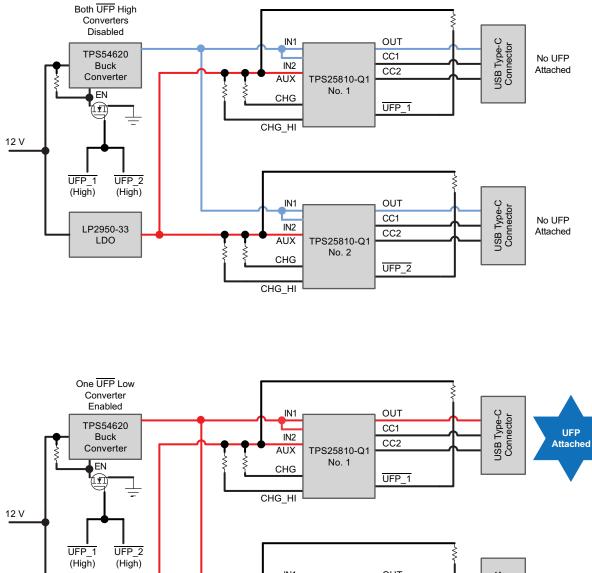

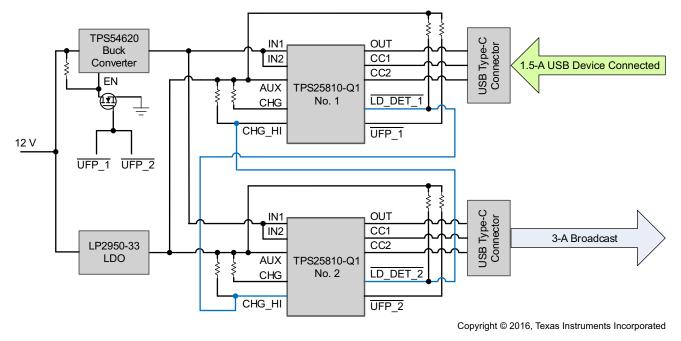

The power-wake feature supported in the TPS25810-Q1 device offers the mobile-systems designer a way to save on system power when no UFP is attached to the Type-C port. See Figure 16. To enable power wake, the UFP pins from device No. 1 and No. 2 are tied together (each with its own 100-k $\Omega$  pullup) to the enable pin of a 5-V, 6-A dc-dc buck converter. When no UFP is detected on both Type-C ports, the EN pin of the dc-dc converter is pulled high, thereby disabling it. Because both TPS25810-Q1 devices are powered by an always-on 3.3-V LDO, turning off the supply to IN1 and IN2 does not affect its operation in detach state. Anytime a UFP is detected on either port, the corresponding TPS25810-Q1 UFP pin is pulled low, enabling the dc-dc converter to provide charging current to the attached UFP. Turning off the high-power dc-dc converter when ports are unattached saves on system power. This method can save a significant amount of power, because the TPS25810-Q1 device only requires < 5  $\mu$ A when no UFP device is connected.

Figure 16. Power-Wake Implementation

### 7.3.3.11 Port Power Management (PPM)

PPM is the intelligent and dynamic allocation of power made possible with the use of the LD\_DET pin. PPM is for systems that have multiple charging ports but cannot power them all at their maximum charging current simultaneously.

Goals of PPM are:

- Enhanced user experience, because the user needs not to search for a high-current charging port.

- Lowered cost and size of the power supply needed for implementing high-current charging in a multiport system.

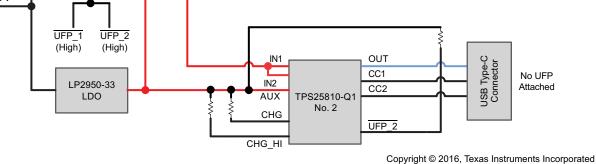

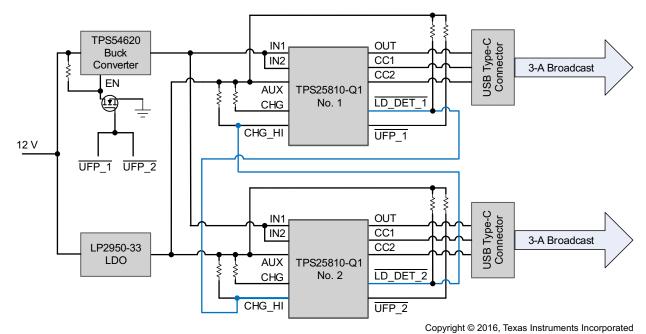

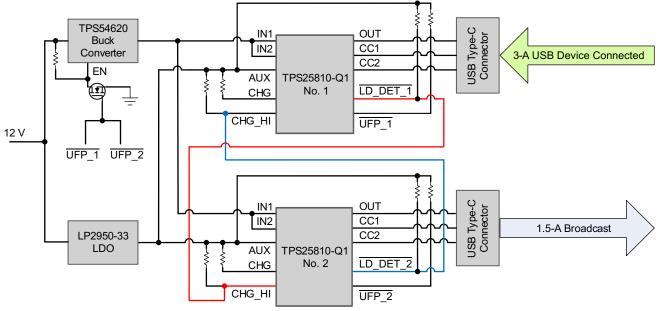

#### 7.3.3.12 Implementing PPM in a System With Two Type-C Ports

Figure 17 shows PPM and power wake implemented in a system with two Type-C ports, both initially set to broadcast high-current charging (3 A, CHG and CHG\_HI pulled high via 100-k $\Omega$  resistors to AUX). To enable PPM, tie the LD\_DET pin from TPS25810-Q1 device No. 1 to CHG\_HI of TPS25810-Q1 device No. 2 and vice versa, as shown in Figure 17. Each device independently monitors the charging current drawn by its attached UFP.