**TUSB1002A**

ZHCSHW9B - MARCH 2018 - REVISED OCTOBER 2023

# TUSB1002A USB3.2 10Gbps 双通道线性转接驱动器

### 1 特性

- 支持 USB3.2 x1 SuperSpeed (5Gbps) 和 SuperSpeedPlus (10Gbps)

- 支持 PCI Express Gen3、SATA Express 和 SATA Gen3

- 超低功耗架构:

- 断开 U2、U3:<1.9mW

- 关断: < 700µW

- 可调节电压输出摆幅线性范围高达 1200mVpp

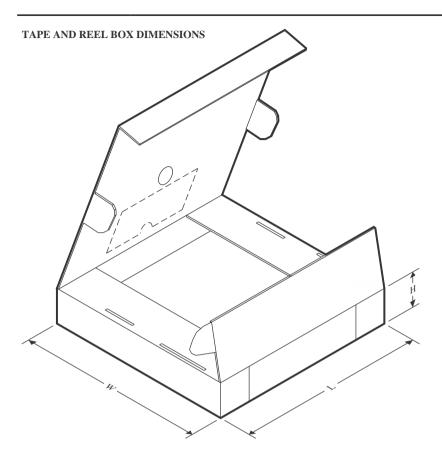

- 无主机或器件端要求

- 16 种线性均衡设置, 高达 16dB (10Gbps 时)

- 可调节直流均衡增益

- 支持热插拔

- 与 LVPE502A 和 LVPE512 USB 3.0 转接驱动器引 脚对引脚兼容

- 与 TUSB1002 转接驱动器引脚对引脚兼容

- 温度范围:0°C 至 70°C (商业级)和 40°C 至 85°C(工业级)

- ±5kV HBM ESD

- 由 3.3V 单电源供电。

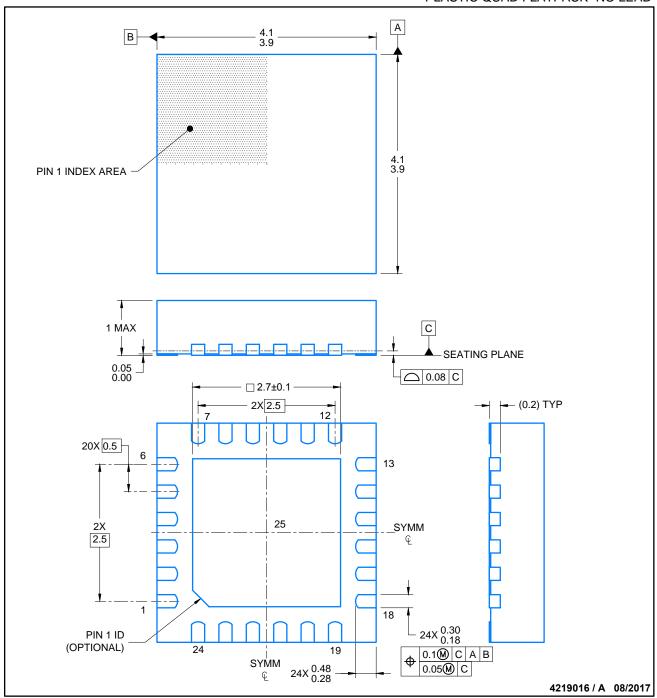

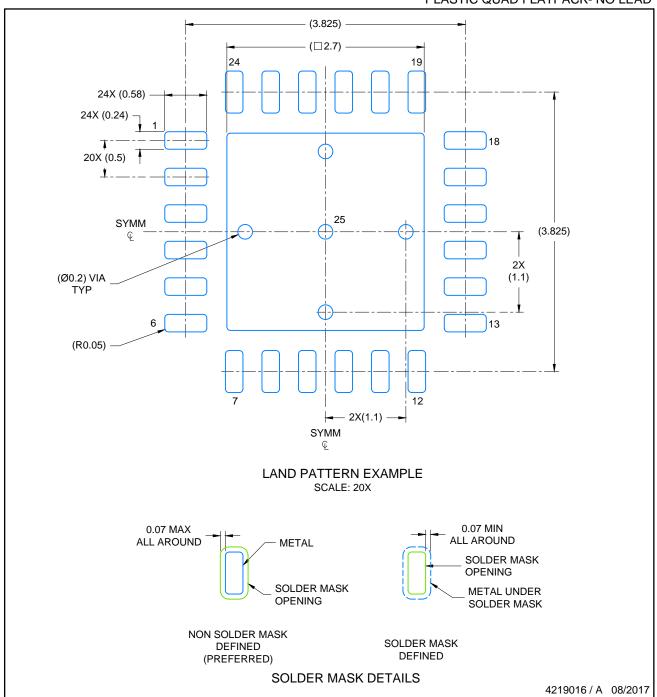

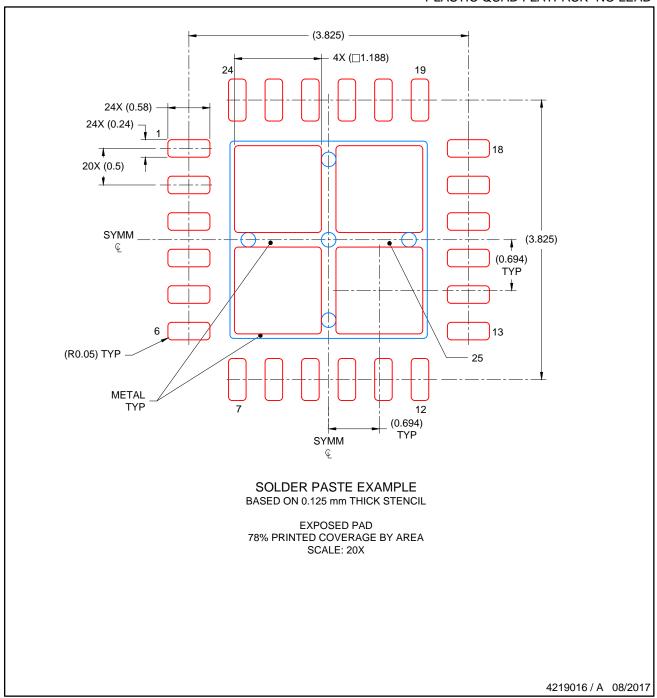

- 采用 4mm×4mm VQFN 封装

### 2 应用

- 笔记本和台式机

- 电视

- 平板电脑

- 手机

- 有源电缆

- 扩展坞

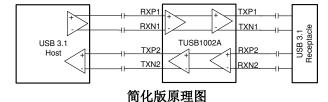

### 3 说明

是业内首款双通道 USB 3.2 x1 TUSB1002A SuperSpeedPlus (SSP) 转接驱动器和信号调节器。该 器件采用超低功耗架构,由 3.3V 电源供电,具有很低 的功耗。它支持 USB3.2 低功耗模式,可进一步降低空 闲状态下的功耗。

TUSB1002A 实现了一款线性均衡器,最高可容许码间 串扰 (ISI) 引入 16dB 的损耗。当 USB 信号在印刷电路 板 (PCB) 或电缆上传输时,其完整性会在通道损耗和 码间串扰的影响下有所降低。线性均衡器可对通道损失 进行补偿,进而延长通道传输距离,从而使系统符合 USB 规范。凭借双通道和小型封装, TUSB1002A 可 在 USB3.2 路径中灵活放置。

TUSB1002A 采用 24 引脚 4mm × 4mm VQFN 封装。 它还具有商业级 (TUSB1002A) 和工业级 (TUSB1002AI) 两个版本。

#### 器件信息

| AA 11 1A .C.        |                               |                    |  |  |  |  |  |

|---------------------|-------------------------------|--------------------|--|--|--|--|--|

| 器件型号 <sup>(1)</sup> | 温度                            | 封装                 |  |  |  |  |  |

| TUSB1002A           | T <sub>A</sub> = 0°C 至 70°C   | RGE ( VQFN , 24 )  |  |  |  |  |  |

| TUSB1002AI          | T <sub>A</sub> = -40°C 至 85°C | NOL ( VQI N , 24 ) |  |  |  |  |  |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

### **Table of Contents**

| 1 特性                                 | 1  | 7.5 U0 Mode                             | 18              |

|--------------------------------------|----|-----------------------------------------|-----------------|

| 2 应用                                 |    | 7.6 U1 Mode                             | 18              |

| 3 说明                                 |    | 7.7 U2/U3 Mode                          | 18              |

| 4 Revision History                   |    | 8 Application and Implementation        | 19              |

| 5 Pin Configuration and Functions    |    | 8.1 Application Information             | 19              |

| 6 Specifications                     |    | 8.2 Typical USB3.2 Application          | 19              |

| 6.1 Absolute Maximum Ratings         |    | 8.3 Typical SATA, PCIe and SATA Express |                 |

| 6.2 ESD Ratings                      |    | Application                             | 23              |

| 6.3 Recommended Operating Conditions |    | 8.4 Power Supply Recommendations        | 26              |

| 6.4 Thermal Information              |    | 8.5 Layout                              | 26              |

| 6.5 Electrical Characteristics       |    | 9 Device and Documentation Support      | <mark>28</mark> |

| 6.6 Timing Requirements              |    | 9.1 接收文档更新通知                            | 28              |

| 6.7 Switching Characteristics        |    | 9.2 支持资源                                | 28              |

| 6.8 Typical Characteristics          |    | 9.3 Trademarks                          |                 |

| 7 Detailed Description               |    | 9.4 静电放电警告                              | 28              |

| 7.1 Overview                         |    | 9.5 术语表                                 |                 |

| 7.2 Functional Block Diagram         | 14 | 10 Mechanical, Packaging, and Orderable |                 |

| 7.3 Feature Description              | 15 | Information                             | 28              |

| 7.4 Device Functional Modes          |    |                                         |                 |

|                                      |    |                                         |                 |

**4 Revision History** 注:以前版本的页码可能与当前版本的页码不同

| С | hanges from Revision A (November 2018) to Revision B (October 2023)                                      | Page            |

|---|----------------------------------------------------------------------------------------------------------|-----------------|

| • | 更新了整个文档中的表格、图和交叉参考的编号格式                                                                                  | 1               |

| • | 更新了器件信息表以包含环境温度                                                                                          | <mark>1</mark>  |

| • | Updated the TUSB1002A in ESB3.2 x1 Host Application figure to include ESD and optional 220 k Ω pu        | ıll-            |

|   | down on RX pins                                                                                          | 19              |

| • | Updated the Design Parameters table to include pre-channel and post-channel min/max limits               | 20              |

| • | Changed 100 nF recommendation to 220 nF for ac-coupling capacitors                                       | 20              |

| • | Added the ESD Protection section                                                                         | <mark>22</mark> |

| С | hanges from Revision * (March 2018) to Revision A (November 2018)                                        | Page            |

| • | Changed text from: "Inclusion of these 330 nF capacitors and 220 kΩ resistors is optional but highly     |                 |

|   | recommended." to: "Inclusion of the 330 nF capacitors and 220 kΩ resistors is optional." in the Detailed | d               |

|   | Design Procedure                                                                                         |                 |

| • | Added ordered list of implementation options for USB connector to TUSB1002A RX pins                      | 20              |

Product Folder Links: TUSB1002A

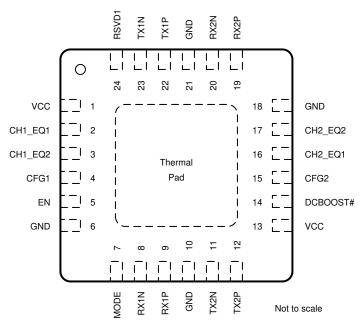

# **5 Pin Configuration and Functions**

图 5-1. RGE Package, 24-Pin VQFN (Top View)

表 5-1. Pin Functions

| P       | PIN | TYPE             | INTERNAL PULLUP   | DESCRIPTION                                                                                                                                                                                                                                   |  |  |  |  |

|---------|-----|------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME    | NO. | 90Ω Differential | PULLDOWN          | DESCRIPTION                                                                                                                                                                                                                                   |  |  |  |  |

| RX1P    | 9   | 90Ω Differential |                   | Differential input for SuperSpeed (SS) and SuperSpeedPlus (SSP) positive signals for Channel 1                                                                                                                                                |  |  |  |  |

| RX1N    | 8   | Input            | _                 | Differential input for SuperSpeed (SS) and SuperSpeedPlus (SSP) negative signals for Channel 1                                                                                                                                                |  |  |  |  |

| RX2P    | 19  | 90Ω Differential |                   | Differential input for SuperSpeed (SS) and SuperSpeedPlus (SSP) positive signals for Channel 2                                                                                                                                                |  |  |  |  |

| RX2N    | 20  | Input            | _                 | Differential input for SuperSpeed (SS) and SuperSpeedPlus (SSP) negative signals for Channel 2.                                                                                                                                               |  |  |  |  |

| TX1P    | 22  | 90Ω Differential |                   | Differential output for SuperSpeed (SS) and SuperSpeedPlus (SSP) positive signals for Channel 1.                                                                                                                                              |  |  |  |  |

| TX1N    | 23  | Output           | _                 | Differential output for SuperSpeed (SS) and SuperSpeedPlus (SSP) negative signals for Channel 1.                                                                                                                                              |  |  |  |  |

| TX2P    | 12  | 90Ω Differential |                   | Differential output for SuperSpeed (SS) and SuperSpeedPlus (SSP) positiv signals for Channel 2.                                                                                                                                               |  |  |  |  |

| TX2N    | 11  | Output           | _                 | Differential output for SuperSpeed (SS) and SuperSpeedPlus (SSP) negative signals for Channel 2.                                                                                                                                              |  |  |  |  |

| CH1_EQ1 | 2   | I (4-level)      |                   | CH1_EQ1. Configuration pin used to control Rx EQ level for RX1P/N. The state of this pin is sampled after the rising edge of EN. Refer to 图 6-2 for details of timing. This pin along with CH1_EQ2 allows for up to 16 equalization settings. |  |  |  |  |

| CH1_EQ2 | 3   | I (4-level)      | PU (approx 45K)   | CH1_EQ2. Configuration pin used to control Rx EQ level for RX1P/N. The state of this pin is sampled after the rising edge of EN. Refer to 图 6-2 for details of timing. This pin along with CH1_EQ1 allows for up to 16 equalization settings. |  |  |  |  |

| CH2_EQ1 | 16  | I (4-level)      | PD (approx 95K)   | CH2_EQ1. Configuration pin used to control Rx EQ level for RX2P/N. The state of this pin is sampled after the rising edge of EN. Refer to 图 6-2 for details of timing. This pin along with CH2_EQ2 allows for up to 16 equalization settings. |  |  |  |  |

| CH2_EQ2 | 17  | I (4-level)      |                   | CH2_EQ2. Configuration pin used to control Rx EQ level for RX2P/N. The state of this pin is sampled after the rising edge of EN. Refer to 图 6-2 for details of timing. This pin along with CH2_EQ1 allows for up to 16 equalization settings. |  |  |  |  |

| EN      | 5   | I (2-level)      | PU (approx 400 K) | EN. Places TUSB1002A into shutdown mode when asserted low. Normal operation when pin is asserted high. When in shutdown, TUSB1002A's receiver terminations will be high impedance and tx/rx channels will be disabled.                        |  |  |  |  |

Product Folder Links: TUSB1002A

提交文档反馈

3

# 表 5-1. Pin Functions(续)

| P                        | IN    | TYPE              | INTERNAL PULLUP                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------|-------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                     | NO.   | IIFE              | PULLDOWN                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                           |

| CFG1 4 I (4-level)       |       | I (4-level)       | PU (approx 45K)<br>PD (approx 95K)                                                                                                                                                                                                                                                                                                                                                                                                                                              | CFG1. This pin along with CFG2 will select VOD linearity range and DC gain for both channels 1 and 2. The state of this pin is sampled after the rising edge of EN. Refer to 图 6-2 for details of timing. Refer to 表 7-3 for VOD linearity range and DC gain options.                                                                                                 |

| CFG2 15 I (4-level)      |       | I (4-level)       | PU (approx 45K)<br>PD (approx 95K)                                                                                                                                                                                                                                                                                                                                                                                                                                              | CFG2. This pin along with CFG1 will set VOD linearity range and DC gain for both channels 1 and 2. The state of this pin is sampled after the rising edge of EN. Refer to 图 6-2 for details of timing. Refer to 表 7-3 for VOD linearity range and DC gain options.                                                                                                    |

| MODE 7 I (4-level)       |       | l (4-level)       | PU (approx 45 K)<br>PD (approx 95K)                                                                                                                                                                                                                                                                                                                                                                                                                                             | MODE. This pin is for selecting different modes of operation. The state of this pin is sampled after the rising edge of EN. Refer to   6-2 for details of timing.  9 = Basic Redriver Mode.  R = PCle / Test Mode. PCle Mode and TI Internal use only  F = USB3.2 x1 Dual Channel Operation enabled (TUSB1002A normal mode).  1 = USB3.2 x1 Single-channel operation. |

| RSVD1                    | 24    | 0                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RSVD1. Under normal operation, this pin will be driven low by TUSB1002A. Recommend leaving this pin unconnected on PCB.                                                                                                                                                                                                                                               |

| DCBOOST # 14 I (2-level) |       | PU (approx 400 K) | DCBOOST#. This pin when asserted low will increase the DC Gain level defined in $\[ \frac{\pi}{8} \]$ 7-3 by +1 dB unless already at +2dB. If DC Gain level defined in $\[ \frac{\pi}{8} \]$ 7-3 is already at +2 dB, then asserting this pin low will not change the DC Gain level. This pin can be left unconnected if this function is not needed. 1 = DC Gain defined by $\[ \frac{\pi}{8} \]$ 7-3. 0 = DC Gain defined by $\[ \frac{\pi}{8} \]$ 7-3 is increased by +1 dB. |                                                                                                                                                                                                                                                                                                                                                                       |

| VCC                      | 1, 13 | Power             | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3.3 V (±10%) Supply.                                                                                                                                                                                                                                                                                                                                                  |

| GND 6, 10, 18, GND 21    |       | _                 | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                       |

| Thermal pad              |       |                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Thermal pad. Recommend connecting to a solid ground plane.                                                                                                                                                                                                                                                                                                            |

### **6 Specifications**

### **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

|                           |                                            | MIN  | MAX | UNIT |

|---------------------------|--------------------------------------------|------|-----|------|

| Supply Voltage<br>Range   | Vcc                                        | -0.3 | 4   | V    |

|                           | Differential voltage for RX1P/N and RX2P/N | -2.5 | 2.5 | V    |

| Voltage Range on I/O pins | Voltage at RX pins                         | -0.5 | 4   | V    |

| 5 p                       | Voltage on Control pins                    | -0.5 | 4   | V    |

| T <sub>stg</sub>          | Storage temperature                        | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Rating* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Condition*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|                    |                                                                                 |                                                                                          | VALUE | UNIT |

|--------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001, all pins <sup>(1)</sup> |                                                                                          | ±5000 | V    |

|                    |                                                                                 | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±1500 | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                  |                                      | MIN | NOM | MAX | UNIT |

|------------------|--------------------------------------|-----|-----|-----|------|

| V <sub>CC</sub>  | Supply voltage                       | 3   | 3.3 | 3.6 | V    |

| V <sub>PSN</sub> | Supply noise on V <sub>CC</sub> pins |     |     | 100 | mV   |

| т.               | TUSB1002A Ambient temperature        | 0   |     | 70  | °C   |

| T <sub>A</sub>   | TUSB1002Al Ambient temperature       | -40 |     | 85  | °C   |

| TJ               | TUSB1002A Junction temperature       | 0   |     | 105 | °C   |

| '                | TUSB1002AI Junction temperature      | -40 |     | 105 | °C   |

#### 6.4 Thermal Information

Copyright © 2023 Texas Instruments Incorporated

|                        |                                              | TUSB1002A  |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC(1)                            | RGE (VQFN) | UNIT |

|                        |                                              | 24 PINS    |      |

| R <sub>0</sub> JA      | Junction-to-ambient thermal resistance       | 38.5       | °C/W |

| R <sub>θ JC(top)</sub> | Junction-to-case (top) thermal resistance    | 41.6       | °C/W |

| R <sub>0</sub> JB      | Junction-to-board thermal resistance         | 16.3       | °C/W |

| $\Psi_{JT}$            | Junction-to-top characterization parameter   | 1.0        | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 16.4       | °C/W |

| R <sub>θ JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 6.9        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Product Folder Links: TUSB1002A

#### **6.5 Electrical Characteristics**

over operating free-air temperature and voltage range (unless otherwise noted)

|                              | PARAMETER                                                                                                | TEST CONDITIONS                                                                              | MIN  | TYP  | MAX | UNIT               |

|------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------|------|-----|--------------------|

| POWER                        |                                                                                                          |                                                                                              |      |      |     |                    |

| P <sub>U0_SSP_1200m</sub> V  | Power under USB3.1 operation in U0 operating at SuperSpeedPlug datarate with linear range set to 1200mV. | At 10 Gbps; V <sub>CC</sub> = 3.3 V; EN = 1; Pattern = CP9; V <sub>OD</sub> = 1200mVpp       |      | 330  |     | mW                 |

| P <sub>U0_SSP_1000m</sub> V  | Power under USB3.1 operation in U0 operating at SuperSpeedPlug datarate with linear range set to 1000mV. | At 10 Gbps; V <sub>CC</sub> = 3.3 V; EN = 1; Pattern = CP9; V <sub>OD</sub> = 1000mVpp       |      | 310  |     | mW                 |

| P <sub>U0_SSP_900m</sub> V   | Power under USB3.1 operation in U0 operating at SuperSpeedPlug datarate with linear range set to 900mV.  | At 10 Gbps; V <sub>CC</sub> = 3.3 V; EN = 1; Pattern = CP9; V <sub>OD</sub> = 900mVpp        |      | 295  |     | mW                 |

| P <sub>U1</sub>              | Power in U1 with linear range set to 1200mV.                                                             | In U1; V <sub>CC</sub> = 3.3 V; EN = 1; V <sub>OD</sub> = 1200mVpp                           |      | 330  |     | mW                 |

| P <sub>U2U3</sub>            | Power when in U2/U3 state.                                                                               | V <sub>CC</sub> = 3.3 V; EN = 1; Both channels in U2/U3;                                     |      | 1.5  |     | mW                 |

| P <sub>DISCONNECT_NONE</sub> | Power when no USB device detected on both TX1P/N and TX2P/N.                                             | V <sub>CC</sub> = 3.3 V; EN = 1; RX1 and RX2 termination disabled;                           |      | 1.9  |     | mW                 |

| P <sub>DISCONNECT_ONE</sub>  | Power when a single USB device detected on either TX1P/N or TX2P/N.                                      | V <sub>CC</sub> = 3.3 V; EN = 1; Either RX1 or RX2 termination enabled but not both enabled; |      | 1.9  |     | mW                 |

| P <sub>SHUTDOWN</sub>        | Shutdown power when EN = 0.                                                                              | VCC = 3.3 V; EN = 0;                                                                         |      | 0.7  |     | mW                 |

| 4-level Inputs (CFC          | G[2:1], MODE, CH1_EQ[2:1], CH                                                                            | 2_EQ[2:1])                                                                                   |      |      |     |                    |

|                              | Threshold "0" / "R"                                                                                      | V <sub>CC</sub> = 3.3 V                                                                      |      | 0.55 |     | V                  |

| $V_{TH}$                     | Threshold "R" / "F"                                                                                      | V <sub>CC</sub> = 3.3 V                                                                      |      | 1.65 | 65  | V                  |

|                              | Threshold "F" / "1"                                                                                      | V <sub>CC</sub> = 3.3 V                                                                      |      | 2.8  |     | V                  |

| I <sub>IH</sub>              | High-level input current                                                                                 | V <sub>CC</sub> = 3.6 V; V <sub>IN</sub> = 3.6 V                                             | 20   |      | 80  | μΑ                 |

| I <sub>IL</sub>              | Low-level input current                                                                                  | V <sub>CC</sub> = 3.6 V; V <sub>IN</sub> = 0 V                                               | -160 |      | -40 | μΑ                 |

| R <sub>PU</sub>              | Internal pullup resistance                                                                               |                                                                                              |      | 45   |     | kΩ                 |

| R <sub>PD</sub>              | Internal pulldown resistance                                                                             |                                                                                              |      | 95   |     | $\mathbf{k}\Omega$ |

| EN, DCBOOST#                 |                                                                                                          |                                                                                              |      |      |     |                    |

| V <sub>IH</sub>              | High-level input voltage                                                                                 | V <sub>CC</sub> = 3.3 V                                                                      | 1.7  |      | 3.6 | V                  |

| V <sub>IL</sub>              | Low-level input voltage                                                                                  | V <sub>CC</sub> = 3.3 V                                                                      | 0    |      | 0.7 | V                  |

| I <sub>IH</sub>              | High-level input current                                                                                 | V <sub>CC</sub> = 3.6 V; V <sub>IN</sub> = 3.6 V                                             | -10  |      | 10  | μA                 |

| I <sub>IL</sub>              | Low-level input current                                                                                  | V <sub>CC</sub> = 3.6 V; V <sub>IN</sub> = 0 V                                               | -15  |      | 15  | μA                 |

| R <sub>PU_EN</sub>           | Internal pullup resistance for EN and DCBOOST#                                                           |                                                                                              |      | 400  |     | <b>k</b> Ω         |

| USB3.1 Receiver I            | nterface (RX1P/N and RX2P/N)                                                                             | · · · · · · · · · · · · · · · · · · ·                                                        |      |      |     |                    |

| R <sub>L_100 MHz</sub>       | Rx Differential return loss at 100 MHz to 2.5 GHz                                                        | SDD11 100 MHz to 2.5 GHz at 90-Ω                                                             |      | -18  |     | dB                 |

| R <sub>L_5 GHz</sub>         | Rx Differential return loss at 5 GHz                                                                     | SDD11 5 GHz at 90-Ω                                                                          |      | -14  |     | dB                 |

| R <sub>L_10 GHz</sub>        | Rx Differential return loss from 5 to 10 GHz                                                             | SDD11 5 GHz to 10 GHz at 90-Ω                                                                |      | -6   |     | dB                 |

| R <sub>L_CM</sub>            | Rx common mode return loss                                                                               | SCC11 0.5 to 5 GHz at 90-Ω                                                                   |      | -12  |     | dB                 |

| X-Talk                       | Differential crosstalk between TX and RX signal pairs                                                    |                                                                                              |      | -50  |     | dB                 |

Product Folder Links: TUSB1002A

# 6.5 Electrical Characteristics (续)

over operating free-air temperature and voltage range (unless otherwise noted)

|                             | PARAMETER                                                                 | TEST CONDITIONS                                                                                                                                                            | MIN | TYP   | MAX | UNIT       |

|-----------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|------------|

| E <sub>ACGAIN_5 GHz</sub>   | Max AC Equalization Gain                                                  | 50 mVpp CP10 at 5 GHz; VCC = 3.3V;                                                                                                                                         |     | 16    |     | dB         |

| E <sub>DC_GAIN0</sub>       | DC Gain at 0 dB setting                                                   | 200 mVpp VID at 100 MHz; 1200mV<br>Linear Range Setting;                                                                                                                   |     | .7    |     | dB         |

| E <sub>DC_GAIN1</sub>       | DC Gain at 1 dB setting                                                   | 200 mVpp VID at 100 MHz; 1200mV<br>Linear Range Setting;                                                                                                                   |     | 1.6   |     | dB         |

| E <sub>DC_GAIN2</sub>       | DC Gain at 2 dB setting                                                   | 200 mVpp VID at 100 MHz; 1000mV<br>Linear Range Setting;                                                                                                                   |     | 2.3   |     | dB         |

| E <sub>DC_GAIN-1</sub>      | DC Gain at -1 dB setting                                                  | 200 mVpp VID at 100 MHz; 1200mV<br>Linear Range Setting;                                                                                                                   |     | -0.25 |     | dB         |

| V <sub>DIFF_IN</sub>        | Input differential peak-peak voltage swing range                          |                                                                                                                                                                            |     | 1200  |     | mV         |

| V <sub>RX-DC-CM</sub>       | RX DC common mode voltage                                                 |                                                                                                                                                                            |     | 0     |     | V          |

| R <sub>RX-DC-CM</sub>       | RX DC common mode impedance                                               | Measured at connector; Present when USB Device detected on TXP/N;                                                                                                          | 18  |       | 30  | Ω          |

| R <sub>RX-DC-DIFF</sub>     | RX DC differential impedance                                              | Measured at connector; Present when USB Device detected on TXP/N;                                                                                                          | 72  |       | 120 | Ω          |

| Z <sub>RX-DC-DIFF</sub>     | DC Input CM Input Impedance V > 0 during RESET or power down.             | 1. Rx DC CM Impedance with Rx terminations not powered. 2. Measured over the range 0 - 500 mV with respect to GND. 3. Only DC input CM Input impedance V > 0 is specified. | 35  |       |     | <b>k</b> Ω |

| V <sub>RX-SIGNAL-DET</sub>  | Input differential peak-to-peak signal detect assert level                | At 10 Gbps; No loss input channel and PRBS7 pattern.                                                                                                                       |     | 85    |     | mV         |

| V <sub>RX-IDLE-DET</sub>    | Input differential peak-to-peak signal detect de-assert level             | At 10 Gbps; No loss input channel and PRBS7 pattern.                                                                                                                       |     | 60    |     | mV         |

| V <sub>RX-LFPS-DET</sub>    | LFPS detect threshold.                                                    | Below min is squelched                                                                                                                                                     | 100 |       | 310 | mV         |

| V <sub>RX-CM-AC-P</sub>     | Peak RX AC common mode voltage                                            | Measured at package pin.                                                                                                                                                   |     |       | 150 | mV         |

| USB3.1 Transmit             | ter Interface (TX1P/N and TX2P/N                                          | N)                                                                                                                                                                         |     |       |     |            |

| R <sub>L_TX_100 MHz</sub>   | Tx Differential return loss at 100 MHz                                    | SDD22 100 MHz - 2.5 GHz at 90-Ω                                                                                                                                            |     | -20   |     | dB         |

| R <sub>L_TX_2.5 GHz</sub>   | Tx Differential return loss at 5 GHz                                      | SDD22 5 GHz at 90-Ω                                                                                                                                                        |     | -16   |     | dB         |

| R <sub>L_TX_10 GHz</sub>    | Tx Differential return loss from 5 to 10 GHz                              | SDD22 5 GHz to 10 GHz at 90-Ω                                                                                                                                              |     | -8.5  |     | dB         |

| R <sub>L_TX_CM</sub>        | Tx common mode return loss                                                | SCC22 0.5 to 5 GHz at 90-Ω                                                                                                                                                 |     | -6.7  |     | dB         |

|                             | Differential peak-to-peak TX voltage swing linear dynamic range at 100MHz | 1200 mVpp setting; 100MHz; Measured at -1dB compression point = 20 log(VOD/VOD_linear)                                                                                     |     | 1000  |     | mV         |

| V <sub>TX-DIFFPP-1200</sub> | Differential peak-to-peak TX voltage swing linear dynamic range at 5GHz   | 1200 mVpp setting; 5GHz; Measured at -1dB compression point = 20 log(VOD/VOD_linear)                                                                                       |     | 1300  |     | mV         |

| V                           | Differential peak-to-peak TX voltage swing linear dynamic range at 100MHz | 1000 mVpp setting; 100MHz; Measured at -1dB compression point = 20 log(VOD/VOD_linear)                                                                                     |     | 900   |     | mV         |

| V <sub>TX-DIFFPP-1000</sub> | Differential peak-to-peak TX voltage swing linear dynamic range at 5GHz   | 1000 mVpp setting; 5GHz; Measured at -1dB compression point = 20 log(VOD/VOD_linear)                                                                                       |     | 1150  |     | mV         |

1

### 6.5 Electrical Characteristics (续)

over operating free-air temperature and voltage range (unless otherwise noted)

| F                               | PARAMETER                                                                                                      | TEST CONDITIONS                                                                                                                                                                             | MIN  | TYP  | MAX  | UNIT |

|---------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| V                               | Differential peak-to-peak TX voltage swing linear dynamic range at 100MHz                                      | 900 mVpp setting; 100MHz; Measured at -1dB compression point = 20 log(VOD/VOD_linear)                                                                                                       |      | 800  |      | mV   |

| V <sub>TX-DIFFPP-900</sub>      | Differential peak-to-peak TX voltage swing linear dynamic range at 5GHz                                        | 900 mVpp setting; 5GHz; Measured at -1dB compression point = 20 log(VOD/VOD_linear)                                                                                                         |      | 1000 |      | mV   |

| V <sub>TX-RCV-DETECT</sub>      | Amount of voltage change allowed during Rx Detection.                                                          | Measured at package pins.                                                                                                                                                                   |      |      | 600  | mV   |

| V <sub>TX-CM-IDLE-DELTA</sub>   | Transmitter idle common mode voltage change U2/U3 state.                                                       | Max allowed instantaneous commode-<br>mode voltage at connector side of AC<br>coupling capacitor. This is an absolute<br>voltage spec referenced to the receive<br>side termination ground. | -600 |      | 600  | mV   |

| V <sub>TX-DC-CM</sub>           | TX DC common mode voltage                                                                                      | 1200mVpp linear range setting;                                                                                                                                                              | 0    | 1.85 | 2.05 | V    |

| V <sub>TX-CM-AC-PP-ACTIVE</sub> | Transmitter AC common mode peak-peak voltage in U0. Maximum mismatch from TXP+TXN for both time and amplitude. | 1200mVpp linear setting; CHx_EQ setting matches input channel insertion loss;                                                                                                               |      |      | 116  | mV   |

| V <sub>TX-IDLE-DIFF-AC-PP</sub> | AC electrical idle differential peak-to-peak output voltage                                                    |                                                                                                                                                                                             | 0    |      | 10   | mV   |

| V <sub>TX-CM-DC-ACTIVE</sub> -  | Absolute DC common mode voltage between U1 and U0                                                              |                                                                                                                                                                                             |      |      | 200  | mV   |

| R <sub>TX-DC-CM</sub>           | TX DC common mode impedance                                                                                    |                                                                                                                                                                                             | 18   |      | 30   | Ω    |

| R <sub>TX-DC-DIFF</sub>         | TX DC differential impedance                                                                                   |                                                                                                                                                                                             | 72   |      | 120  | Ω    |

| I <sub>TX-SHORT</sub>           | Transmitter short-circuit current limit.                                                                       |                                                                                                                                                                                             |      |      | 107  | mA   |

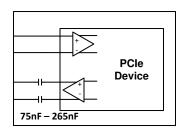

| C <sub>AC-COUPLING</sub>        | External AC coupling capacitor on differential pairs.                                                          |                                                                                                                                                                                             | 75   |      | 265  | nF   |

### 6.6 Timing Requirements

over operating free-air temperature and voltage range (unless otherwise noted)

|                       |                                                                         | MIN | NOM MAX | UNIT |

|-----------------------|-------------------------------------------------------------------------|-----|---------|------|

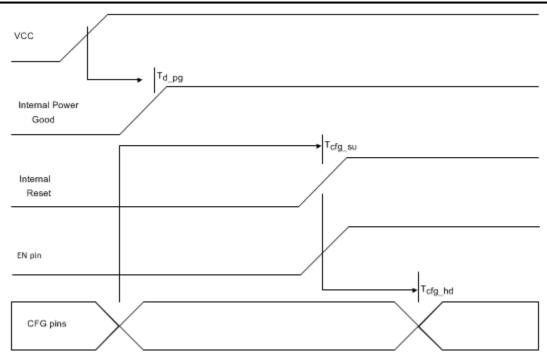

| t <sub>d_pg</sub>     | Internal power good asserted high when V <sub>CC</sub> is at 2.5V       |     | 5       | μs   |

| t <sub>CFG_SU</sub>   | CFG <sup>(1)</sup> pins setup before internal Reset <sup>(2)</sup> high | 0   |         | μs   |

| t <sub>CFG_HD</sub>   | CFG <sup>(1)</sup> pins hold after internal Reset <sup>(2)</sup> high   | 500 |         | μs   |

| t <sub>VCC_RAMP</sub> | V <sub>CC</sub> supply ramp requirement                                 | 0.1 | 50      | ms   |

- (1) Following pins comprise CFG pins: MODE, CFG[2:1], CH1\_EQ[2:1], CH2\_EQ[2:1]

- (2) Internal reset is the logical AND of EN pin and internal power good.

### 6.7 Switching Characteristics

over operating free-air temperature and voltage range (unless otherwise noted)

| PARAMETER                  |                                                                   | TEST CONDITIONS                            | MIN | TYP | MAX | UNIT |

|----------------------------|-------------------------------------------------------------------|--------------------------------------------|-----|-----|-----|------|

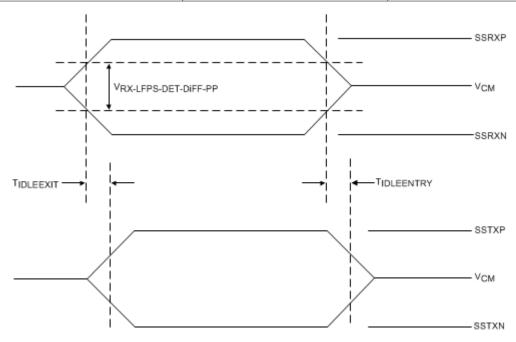

| t <sub>IDLEEntry</sub>     | Delay from U0 to electrical idle                                  | V <sub>CC</sub> = 3.0 V; EN = 1; See 图 6-1 |     |     | 150 | ps   |

| t <sub>IDLEEntry_U1</sub>  | U1 exit time. Break in electrical idle to transmission of LFPS.   | V <sub>CC</sub> = 3.0 V; EN = 1; See 图 6-1 |     |     | 150 | ps   |

| t <sub>IDLEEntry_U2U</sub> | U2/U3 exit time; Break in electrical idle to transmission of LFPS | V <sub>CC</sub> = 3.0 V; EN = 1; See 图 6-1 |     |     | 6   | μs   |

| t <sub>DIFF_DLY</sub>      | Differential propagation delay                                    | V <sub>CC</sub> = 3.0 V; EN = 1;           |     |     | 150 | ps   |

Product Folder Links: TUSB1002A

# 6.7 Switching Characteristics (续)

over operating free-air temperature and voltage range (unless otherwise noted)

|                           | PARAMETER                                                                         | TEST CONDITIONS                                                                                                                                              | MIN | TYP  | MAX | UNIT |

|---------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| t <sub>PWRUP_</sub> ACTIV | Time from assertion of EN to device active and performing Rx.Detect on both ports | V <sub>CC</sub> = 3.0 V; EN = 1;                                                                                                                             |     |      | 8   | ms   |

| t <sub>TX_RISE_FALL</sub> | Transmitter rise/fall time                                                        | V <sub>CC</sub> = 3.3 V; EN = 1; 10 Gbps; 20% to 80% of differential output; 1200 mVpp linear range setting; Fast Input rise/fall time;                      |     | 27   |     | ps   |

| t <sub>RF_MISMATCH</sub>  | Transmitter rise/fall mismatch                                                    | V <sub>CC</sub> = 3.3 V; EN = 1; 10 Gbps; 20% to 80% of differential output; 1200 mVpp linear range setting; 1000 mVpp VID                                   |     | .6   |     | ps   |

| t <sub>TX_DJ</sub>        | Transmitter residual deterministic jitter                                         | V <sub>CC</sub> = 3.3 V; EN = 1; 10 Gbps; 1200<br>mVpp linear range setting; Input channel<br>loss of 12 dB; Output channel loss of 1.5<br>dB; Optimized EQ; |     | 0.05 |     | UI   |

图 6-1. Idle Entry and Exit Latency

Product Folder Links: TUSB1002A

提交文档反馈

9

图 6-2. Power-Up Diagram

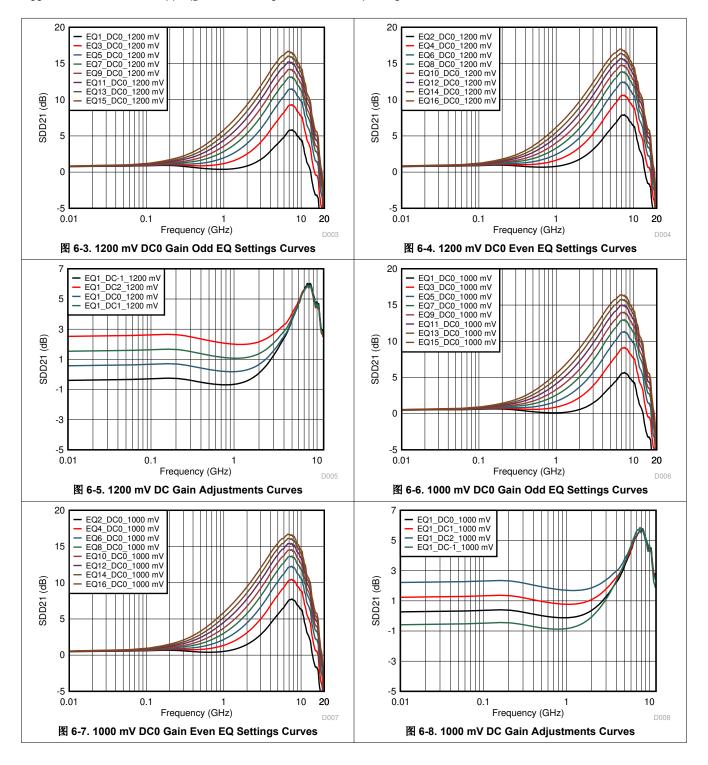

### **6.8 Typical Characteristics**

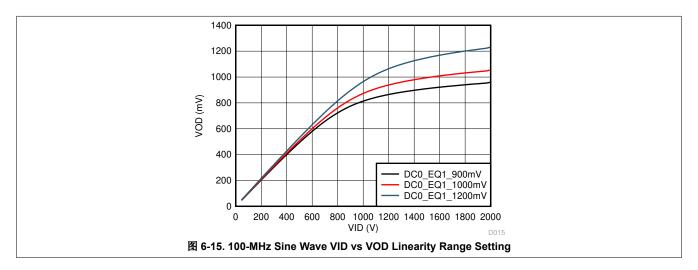

$V_{CC}$  = 3.3V , 25°C, 200 mVpp  $V_{ID}$  sine wave,  $Z_{O}$  = 100  $\Omega$  , RGE package

提交文档反馈

11

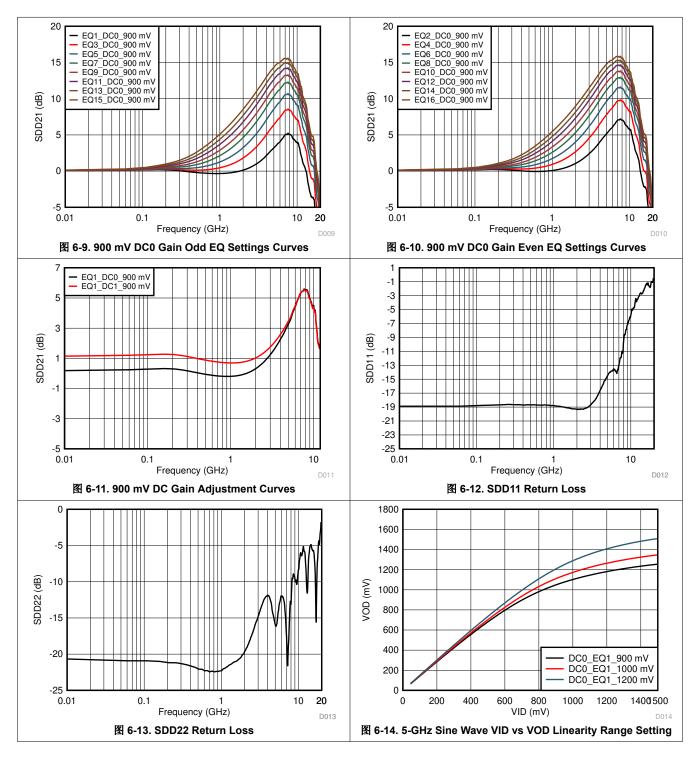

### **6.8 Typical Characteristics (continued)**

$V_{CC}$  = 3.3V , 25°C, 200 mVpp  $V_{ID}$  sine wave,  $Z_{O}$  = 100  $\,\Omega$  , RGE package

Product Folder Links: TUSB1002A

## **6.8 Typical Characteristics (continued)**

$\rm V_{CC}$  = 3.3V , 25°C, 200 mVpp  $\rm V_{ID}$  sine wave,  $\rm Z_{O}$  = 100  $\, \Omega$  , RGE package

Product Folder Links: TUSB1002A

提交文档反馈

13

### 7 Detailed Description

### 7.1 Overview

The TUSB1002A is the industry's first, dual lane USB 3.2 x1 SuperSpeedPlus redriver. As signals traverse through a channel (like FR4 trace) the amplitude of the signal is attenuated. The attenuation varies depending on the frequency content of the signal. Depending the length of the channel this attenuation could be large enough resulting in signal integrity issues at a USB 3.2 receiver. By placing a TUSB1002A between USB3.2 host and device the attenuation effect of the channel can eliminated or minimized. The result is a USB3.2 compatible eye at the devices receiver. With up to 16 receiver equalization settings, the TUSB1002A can support many different channel loss combinations. The TUSB1002A offers low power consumption on a single 3.3-V supply with its ultra-low power architecture. It supports the USB3.2 low power modes which further reduces idle power consumption. The TUSB1002A settings are configurable through pins. In addition to equalization adjustment, the TUSB1002A provides knobs for adjusting DC gain and voltage output linearity range.

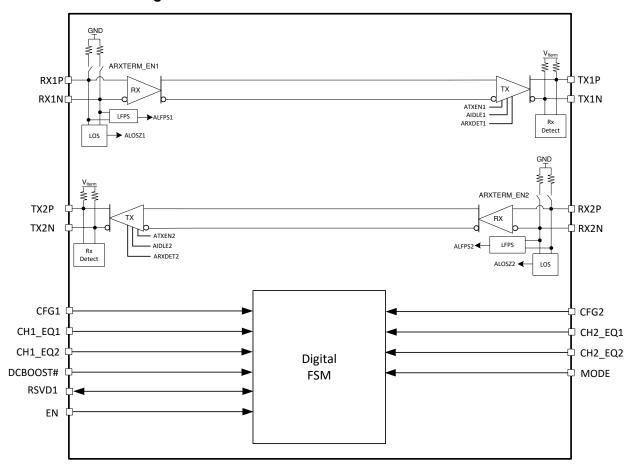

### 7.2 Functional Block Diagram

Copyright © 2023 Texas Instruments Incorporated

### 7.3 Feature Description

#### 7.3.1 4-Level Control Inputs

The TUSB1002A has (MODE, CFG1, CFG2, CH1\_EQ1, CH1\_EQ2, CH2\_EQ1, and CH2\_EQ2) 4-level inputs pins that are used to control the equalization gain and the output voltage swing dynamic range. These 4-level inputs use a resistor divider to help set the 4 valid levels and provide a wider range of control settings. These resistors together with the external resistor connection combine to achieve the desired voltage level.

| 表 7-1. | 4-Level | Control | Pin | <b>Settings</b> |

|--------|---------|---------|-----|-----------------|

|--------|---------|---------|-----|-----------------|

| LEVEL | SETTINGS                                                                                       |

|-------|------------------------------------------------------------------------------------------------|

| 0     | Option 1: Tie 1 k $\Omega$ 5% to GND. Option 2: Tie directly to GND.                           |

| R     | Tie 20 kΩ 5% to GND.                                                                           |

| F     | Float (leave pin open)                                                                         |

| 1     | Option 1: Tie 1 k $\Omega$ 5% to V <sub>CC</sub> . Option 2: Tie directly to V <sub>CC</sub> . |

#### 备注

To conserve power, the TUSB1002A disables 4-level input's internal pull-up/pull-down resistors after the state of 4-level pins have been sampled on rising edge of EN. A change of state for any four level input pin is not applied to TUSB1002A until after EN pin transitions from low to high.

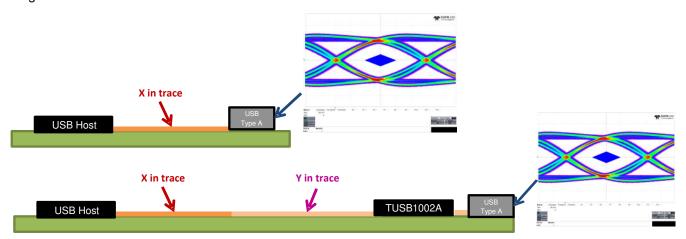

#### 7.3.2 Linear Equalization

With a linear equalizer, the TUSB1002A can electrically shorten a particular channel allowing for longer run lengths.

图 7-1. Linear Equalizer

With a TUSB1002A, a longer trace can be made to have similar insertion loss as a shorter trace. For example, a long trace of X + Y inches can be made to have similar loss characteristics of a shorter trace of X inches.

The receiver equalization level for each channel is determined by the state of the CHx\_EQ1 and CHx\_EQ2 pins, where x = 1 or 2.

Product Folder Links: TUSB1002A

Copyright © 2023 Texas Instruments Incorporated

提交文档反馈

15

表 7-2. EQ Configuration Options for 1200mV Linearity 0 dB DC Gain Setting

|              | •                 |                   | •                              |

|--------------|-------------------|-------------------|--------------------------------|

| EQ SETTING # | CHx_EQ2 PIN LEVEL | CHx_EQ1 PIN LEVEL | EQ GAIN at 2.5GHz / 5 GHz (dB) |

| 1            | 0                 | 0                 | 1.0 / 3.6                      |

| 2            | 0                 | R                 | 2.1 / 5.5                      |

| 3            | 0                 | F                 | 3.0 / 6.8                      |

| 4            | 0                 | 1                 | 4.0 / 8.1                      |

| 5            | R                 | 0                 | 4.6 / 9.0                      |

| 6            | R                 | R                 | 5.5 / 10.0                     |

| 7            | R                 | F                 | 6.2 / 10.8                     |

| 8            | R                 | 1                 | 6.9 / 11.6                     |

| 9            | F                 | 0                 | 7.3 / 11.9                     |

| 10           | F                 | R                 | 7.9 / 12.6                     |

| 11           | F                 | F                 | 8.4 / 13.1                     |

| 12           | F                 | 1                 | 9.0 / 13.7                     |

| 13           | 1                 | 0                 | 9.4 / 14.1                     |

| 14           | 1                 | R                 | 9.9 / 14.6                     |

| 15           | 1                 | F                 | 10.3 / 14.9                    |

| 16           | 1                 | 1                 | 10.7 / 15.3                    |

|              |                   |                   |                                |

### 7.3.3 Adjustable VOD Linear Range and DC Gain

The CFG1 and CFG2 pins can be used to adjust the TUSB1002A output voltage swing linear range and receiver equalization DC gain.  $\frac{1}{8}$  7-3 details the available options.

For best performance, the TUSB1002A should be operated within its defined VOD linearity range. The gain of the incoming VID should be kept to less than or equal to the TUSB1002A VOD linear range setting. The can be determined by 方程式 1:

VID at 5 GHz = VOD x

$$(10^{-(Gv/20)})$$

(1)

#### where

• Gv = TUSB1002A Gain and VOD = TUSB1002A VOD linearity setting.

For example, for a VOD linearity range setting of 1200 mV, the maximum incoming VID signal at 5 GHz with a CHx\_EQ[1:0] setting of 2 (5.5 dB) is 1200 x ( $10^{-(5.5/20)}$ ) = 637 mVpp. The TUSB1002A can be operated outside its VOD linear range but jitter will be higher.

表 7-3. VOD Linear Range and DC Gain

| SETTING # | CFG1 PIN LEVEL | CFG2 PIN LEVEL | CH1 DC GAIN (dB) | CH2 DC GAIN (dB) | CH1 V <sub>OD</sub> LINEAR<br>RANGE (mVpp) | CH2 V <sub>OD</sub> LINEAR<br>RANGE (mVpp) |

|-----------|----------------|----------------|------------------|------------------|--------------------------------------------|--------------------------------------------|

| 1         | 0              | 0              | +1               | 0                | 900                                        | 900                                        |

| 2         | 0              | R              | 0                | +1               | 900                                        | 900                                        |

| 3         | 0              | F              | 0                | 0                | 900                                        | 900                                        |

| 4         | 0              | 1              | +1               | +1               | 900                                        | 900                                        |

| 5         | R              | 0              | 0                | 0                | 1000                                       | 1000                                       |

| 6         | R              | R              | +1               | 0                | 1000                                       | 1000                                       |

| 7         | R              | F              | 0                | -1               | 1000                                       | 1000                                       |

| 8         | R              | 1              | +2               | +2               | 1000                                       | 1000                                       |

| 9         | F              | 0              | -1               | -1               | 1200                                       | 1200                                       |

| 10        | F              | R              | +2               | +2               | 1200                                       | 1200                                       |

| 11        | F              | F              | 0                | 0                | 1200                                       | 1200                                       |

| 12        | F              | 1              | +1               | +1               | 1200                                       | 1200                                       |

| 13        | 1              | 0              | +2               | 0                | 1200                                       | 1200                                       |

| 14        | 1              | R              | 0                | +2               | 1200                                       | 1200                                       |

Product Folder Links: TUSB1002A

Copyright © 2023 Texas Instruments Incorporated

表 7-3. VOD Linear Range and DC Gain (续)

|           |                | ,              | our runigo uma   |                  |                                            |                                            |

|-----------|----------------|----------------|------------------|------------------|--------------------------------------------|--------------------------------------------|

| SETTING # | CFG1 PIN LEVEL | CFG2 PIN LEVEL | CH1 DC GAIN (dB) | CH2 DC GAIN (dB) | CH1 V <sub>OD</sub> LINEAR<br>RANGE (mVpp) | CH2 V <sub>OD</sub> LINEAR<br>RANGE (mVpp) |

| 15        | 1              | F              | 0                | +1               | 1200                                       | 1200                                       |

| 16        | 1              | 1              | +1               | 0                | 1200                                       | 1200                                       |

#### 7.3.4 USB3.2 Dual Channel Operation (MODE = "F")

TheTUSB1002A in dual-channel operation waits for far-end terminations on both channels 1 and 2 before transitioning to fully active state (U0 mode). This mode of operation, defined as MODE pin = 'F', is the most common configurable for USB3.2 Source (DFP) and Sink (UFP) applications.

In a USB3.2 x2 application, two TUSB1002A redrivers are used: One on the configuration lane and the other on the non-configuration lane. The TUSB1002A on the non-configuration lane must be placed in basic redriver mode (MODE pin = "0"). The TUSB1002A on the configuration lane should be placed in USB3.2 dual channel operation (MODE pin = "F"). The expectation is the USB power delivery (PD) controller will hold both TUSB1002A in shutdown mode until a connection can be established. Upon establishing a connection, the USB PD controller will place each TUSB1002A into the appropriate mode.

### 7.3.5 USB3.2 Single Channel Operation (MODE = "1")

In some applications, like Type-C USB3.2 active cables, only one of the two channels may be active. For this application, setting MODE pin = '1', enables single-channel operation. In this mode of operation, the TUSB1002A attempts far-end termination on both channels 1 and 2. The channel which has a far-end termination detected is enabled while the remaining channel is disabled. If far-end termination is detected on both channels, then TUSB1002A behaves in dual channel operation (both channels enabled).

### 7.3.6 PCIe/SATA/SATA Express Redriver Operation (MODE = "R"; CFG1 = "0"; CFG2 = "0")

The TUSB1002A can be used as a PCI Express (PCIe) Gen3, SATA Gen3, or SATA Express redriver. When TUSB1002A's MODE pin = "R", CFG1 pin = "0", and CFG2 pin = "0", the TUSB1002A enables both channels (upstream and downstream) receiver and transmitter paths upon detecting far-end termination on both TX1 and TX2. Both upstream and downstream paths remain enabled until EN pin is de-asserted low. All USB3.2 power management functionality is disabled in this mode. In this mode, the TUSB1002A is transparent to PCIe link power management (L0s, L1) and SATA interface power states. Once far-end termination is detected on both TX1 and TX2, the TUSB1002A power is at  $P_{(U0\_SSP\_1200mV)}$  regardless of the PCIe or SATA power state. To save power during system S3/S4/S5 states it is suggested to de-assert the EN pin to conserve power.

#### 备注

In this mode the linearity range will be fixed at 1200mVpp and DC gain to 0dB.

#### 7.3.7 Basic Redriver Operation (MODE = "0")

The TUSB1002A can be used as a basic redriver for non-USB3.2 x1 applications. When the TUSB1002A MODE pin = "0", the TUSB1002A enables both channels receiver and transmitter paths. The channel receiver and transmitter termination are both enabled. All USB3.2 power management functionality is disabled.

Product Folder Links: TUSB1002A

#### 7.4 Device Functional Modes

#### 7.4.1 Shutdown Mode

The Shutdown mode is entered when EN pin is low and VCC is active and stable. This mode is the lowest power state of the TUSB1002A. While in this mode, the TUSB1002A receiver terminations is disabled.

#### 7.4.2 Disconnect Mode

Next to Shutdown Mode, the Disconnect mode is the lowest power state of the TUSB1002A. The TUSB1002A enters this mode when exiting Shutdown mode. In this state, the TUSB1002A periodically checks for far-end receiver termination on both SSTX1 and SSTX2. Upon detection of the far-end receiver's termination on both ports, the TUSB1002A transitions to a fully active mode called U0 mode.

#### 7.5 U0 Mode

The U0 mode is the highest power state of the TUSB1002A. Anytime high-speed traffic (SuperSpeed or SuperSpeedPlus) is being received, the TUSB1002A remains in this mode. The TUSB1002A only exits this mode if electrical idle is detected on both SSRX1 and SSRX2. While in this mode, the TUSB1002A hs speed receivers and transmitters are powered and active.

#### 7.6 U1 Mode

The U1 mode is the intermediate mode between U0 mode and U2/U3 mode. In U1 mode, the TUSB1002A receiver termination remains enabled and the TXP/N DC common mode is maintained.

#### 7.7 U2/U3 Mode

Next to the disconnect mode, the U2/U3 mode is next lowest power state. While in this mode, the TUSB1002A periodically performs far-end receiver detection. Anytime the far-end receiver termination is not detected on either CH1 or CH2, the TUSB1002A leaves the U2/U3 mode and transition to the Disconnect mode. It also monitors the SSRX1 and SSRX2 for a valid LFPS. Upon detection of a valid LFPS, the TUSB1002A immediately transitions to the U0 mode.

Copyright © 2023 Texas Instruments Incorporated Product Folder Links: *TUSB1002A*

### 8 Application and Implementation

#### 备注

以下应用部分中的信息不属于 TI 器件规格的范围, TI 不担保其准确性和完整性。TI 的客户应负责确定器件是否适用于其应用。客户应验证并测试其设计,以确保系统功能。

### 8.1 Application Information

The TUSB1002A is a linear redriver designed specifically to compensation for ISI jitter caused by attenuation through a passive medium like traces and cables. Because the TUSB1002A has two independent channels, it can be optimized to correct ISI in both the upstream and downstream direction through 16 different equalization choices. Placing the TUSB1002A between a USB3.2 Host/device controller and a USB3.2 receptacle can correct signal integrity issues resulting in a more robust system.

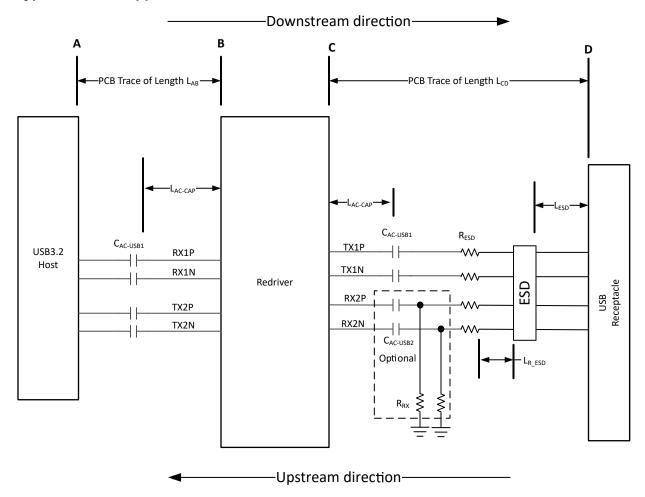

### 8.2 Typical USB3.2 Application

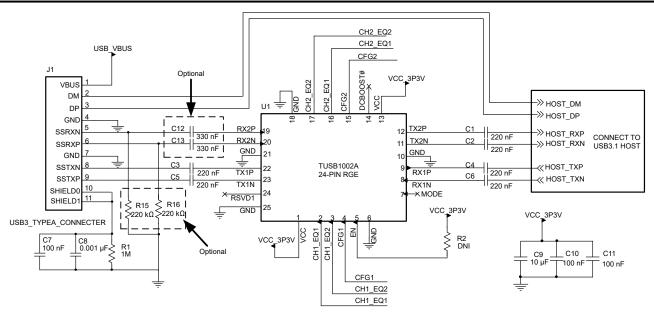

图 8-1. TUSB1002A in USB3.2 x1 Host Application

Product Folder Links: TUSB1002A

Copyright © 2023 Texas Instruments Incorporated

提交文档反馈

19

#### 8.2.1 Design Requirements

For this design example, use the parameters shown in  $\frac{1}{2}$  8-1.

表 8-1. Design Parameters

| PARAMETER                                                                                 | VALUE                                                              |

|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Pre-channel A to B PCB trace length <sup>(1)</sup> , L <sub>AB</sub> .                    | 1 inches $\leq$ L <sub>AB</sub> $\leq$ 12 inches - L <sub>CD</sub> |

| Post-channel C to D PCB trace length <sup>(1)</sup> , L <sub>CD</sub> .                   | ≤ 4 inches                                                         |

| Minimum distance of the AC capacitors from TUSB1002A, L <sub>AC-CAP</sub>                 | 0.25 inches                                                        |

| Maximum distance of ESD component from the USB receptacle, $L_{\mbox{\footnotesize ESD}}$ | 0.6 inches                                                         |

| Maximum distance of series resistor ( $R_{ESD}$ ) from ESD component, $L_{R\_{ESD}}$ .    | 0.25 inches                                                        |

| C <sub>AC-USB1</sub> AC-coupling capacitor (75 nF to 265 nF)                              | 220 nF                                                             |

| C <sub>AC-USB2</sub> AC-coupling capacitor (297 nF to 363 nF)                             | Options:                                                           |

|                                                                                           | RX1 and RX2 are DC-coupled to USB                                  |

|                                                                                           | receptacle                                                         |

|                                                                                           | 330 nF AC-couple with R <sub>RX</sub> resistor                     |

| Optional R <sub>RX</sub> resistor (220-k $\Omega \pm 5\%$ )                               | No used                                                            |

| Optional R <sub>ESD</sub> (0- $\Omega$ to 2.2- $\Omega$ )                                 | 1-Ω                                                                |

| V <sub>CC</sub> supply (3-V to 3.6-V)                                                     | 3.3-V                                                              |

| Mode of Operation (Dual or Half Channel)                                                  | MODE = F (Floating) for USB3.2 Dual Channel                        |

| Linear Range (900 mV, 1000 mV, or 1200 mV)                                                | 1200 mV (CFG[2:1] pins floating)                                   |

| DC Gain (-2, -1, 0, +1, +2)                                                               | 0 dB (CFG[2:1] pins floating)                                      |

<sup>(1)</sup> Maximum trace length assumes an insertion loss of 0.2 dB/inch/GHz. If insertion loss is more than 0.2 dB/inch/GHz, then maximum trace length must be reduced accordingly.

#### 8.2.2 Detailed Design Procedure

The TUSB1002A differential receivers and transmitters have internal BIAS and termination. For this reason, the TUSB1002A must be connected to the USB3.2 host and receptacle through external A/C coupling capacitors. In this example 220 nF capacitors are placed on TX2P and TX2N, RX1P and RX1N, and TX1P and TX1N. 330 nF A/C coupling capacitors along with 220 k $\Omega$  resistors to ground are placed on the RX2P and RX2N. Inclusion of the 330 nF capacitors and 220k resistors is optional. The ordered list below details the three implementation options for the RX2p/n path.

Three implementation options for USB connector to TUSB1002A's RX pins:

- 1. DC couple TUSB1002A's RX pins to USB connector. No 330 nF capacitors and no 220 k  $\Omega$  pull-down resistors.

- 2. 330 nF capacitors with 220 k $\Omega$  resistors as shown in  $\boxtimes$  8-2. The purpose of 220 k $\Omega$  resistors is to discharge the capacitor within 250ms after a USB device is removed from the USB connector.

- 3. The stub from the 220 k  $\Omega$  resistor pad may create impedance discontinuities causing negative impact to performance. Assuming leakage current from external components is enough to discharge capacitor, 330 nF capacitor without the 220 k  $\Omega$  resistor is a valid option.

Copyright © 2023 Texas Instruments Incorporated Product Folder Links: *TUSB1002A*

Copyright © 2018, Texas Instruments Incorporated

图 8-2. Host Implementation Schematic

The USB3.2 Dual channel operation is used in this example. Mode pin should be left floating (unconnected) when using this mode.

The TUSB1002A compensates for channel loss in both the upstream (D to C) and downstream direction (A to B). This is done by configurable the CH1\_EQ[2:1] and CH2\_EQ[2:1] pins to the equalization setting that matches as close possible to the channel insertion loss. In this particular example, CH1\_EQ[2:1] is for path A to B which is the channel between USB3.2 host and the TUSB1002A, and CH2\_EQ[2:1] is for path C to D which is the channel between TUSB1002A and the USB3.2 receptacle.

The TUSB1002A supports 5 levels of DC gain that are selected by the CFG[2:1] pins. Typically, the DC gain should be set to 0 dB but may need to be adjusted to correct any one of the following conditions:

- 1. Input  $V_{\text{ID}}$  too high resulting in  $V_{\text{OD}}$  being greater than USB 3.2 defined swing. For this case, a negative DC gain should be used.

- 2. Input V<sub>ID</sub> too low resulting in V<sub>OD</sub> being less than USB 3.2 defined swing. For this case, a positive DC gain should be used.

- 3. Low frequency discontinuities in the channel resulting in DC component of the signal clipping the vertical eye mask. For this case, a positive DC gain should be used.

It is assumed in this example the incoming  $V_{\text{ID}}$  is at the nominal defined USB3.2 range and the channel is linear across frequency. The CFG1 and CFG2 pins can both be left floating if these assumptions are true.

In this particular example, the channel A-B has a trace length of 8 inches with a 4 mil trace width. This particular channel has about 0.83 dB per inch of insertion loss at 5 GHz. This equates to approximately 6.7 dB of loss for the entire 8 inches of trace. An additional 1.5 dB of loss is added due to package of the USB3.2 Host, TUSB1002A, and the A/C coupling capacitor. This brings the entire channel loss at 5 GHz to 6.7 dB + 1.5 dB = 8.2 dB. A typical USB 3.1 host/device will have around 3 dB of transmitter de-emphasis. Transmitter de-emphasis pre-compensates for the loss of the output channel. With 3 dB of de-emphasis, the total equalization required by the TUSB1002A is in the 5.2 dB (8.2 dB - 3 dB) range. The channel A-B for this example is connected to TUSB1002A's RX1P/N input and therefore CH1\_EQ[2:1] pins are used for adjusting TUSB1002A RX1P/N equalization settings. The CH1\_EQ[2:1] pins should be set such that TUSB1002A equalization is between 5dB and 8dB.

The channel C-D has a trace length of 2 inches with a 4mil trace width. Assuming 0.83 dB per inch of insertion loss, the 2 inch trace will equate to about 1.66 dB of loss at 5 GHz. An additional 2dB of loss needs to be added due to package, A/C coupling capacitor, and the USB 3.1 receptacle. The total loss is around 3.66 dB. Because channel C-D includes a USB 3.1 receptacle, the actual total loss could be much greater than 3.66dB due to the fact that devices plugged into the receptacle will also have loss. The device plugged into receptacle will have either a short or long channel. USB3.2 standard defines total loss limit of 23dB that is distributed as 8.5 dB for Host, 8.5dB for device, and 6.0dB for cable. With variable channel of devices plugged into the USB3.2 receptacle, configurable TUSB1002A's RX2P/N equalization settings is not as straight forward as Channel A-B.

Engineer can not set TUSB1002A CH2\_EQ[2:1] pins to the largest equalization setting to accommodate the largest allowed USB3.2 device/cable loss of 14.5 dB. Doing so will result in TUSB1002A operating outside its linear range when a device with short channel is plugged into the receptacle. For this reason, it is recommended to configurable TUSB1002A CH2\_EQ[2:1] pins to equalize a shorter device channel. This will result in requiring USB3.2 host to compensate for remaining channel loss for the worse case USB3.2 channel of 14.5 dB. The definition of a short device channel is not specified in USB 3.2 specification. Therefore, an engineer must make their own loss estimate of what constitutes a short device channel. For particular example, we will assume the short channel is around 2 to 3 dB. The device's channel loss will need to be added to estimated Channel C-D loss minus the typical 3db of de-emphasis. This means CH2\_EQ[2:1] pins should be configurable to handle a loss of 3 to 5 db.

#### 8.2.3 ESD Protection

It may be necessary to incorporate an ESD component to protect the TUSB1002A from electrostatic discharge (ESD). It is recommended that the ESD protection component has working peak voltage of  $\geq$  2.5 V, a breakdown voltage of  $\geq$  3.5 V, and a clamp voltage of  $\leq$  4.3 V. A clamp voltage greater than 4.3 V may require a R<sub>ESD</sub> on each differential pin. The ESD component should be placed near the USB connector.

| Manufacturer      | Part Number    | Required R <sub>ESD</sub> to pass IEC 61000-4-2 Contact ±8-kV |

|-------------------|----------------|---------------------------------------------------------------|

| Nexperia          | PUSB3FR4       | None                                                          |

| Nexperia          | PESD2V8Y1BSF   | None                                                          |

| Texas Instruments | TPD1E04U04DPLR | 2- Ω                                                          |

| Texas Instruments | TPD4E02B04DQAR | <b>2-</b> Ω                                                   |

表 8-2. Recommended ESD Protection Component

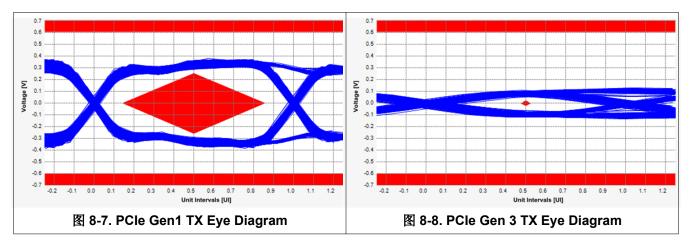

#### 8.2.4 Application Curves

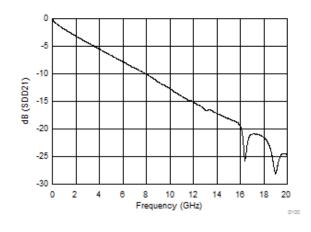

Freq = 5 GHz dB(SDD21) = -6.666

图 8-3. Insertion Loss for 8inch 4 mil FR4 Trace

Copyright © 2023 Texas Instruments Incorporated Product Folder Links: *TUSB1002A*

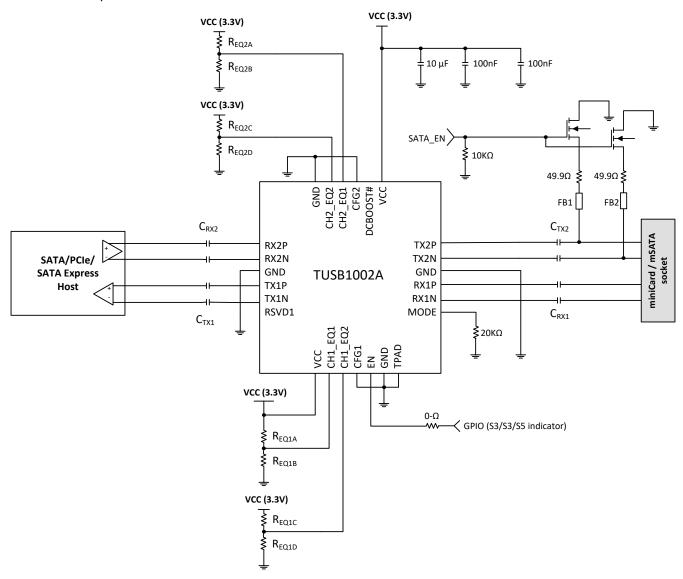

# 8.3 Typical SATA, PCle and SATA Express Application

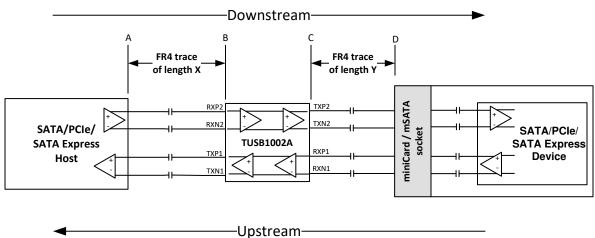

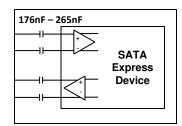

图 8-4. SATA/PCIe/SATA Express Typical Application

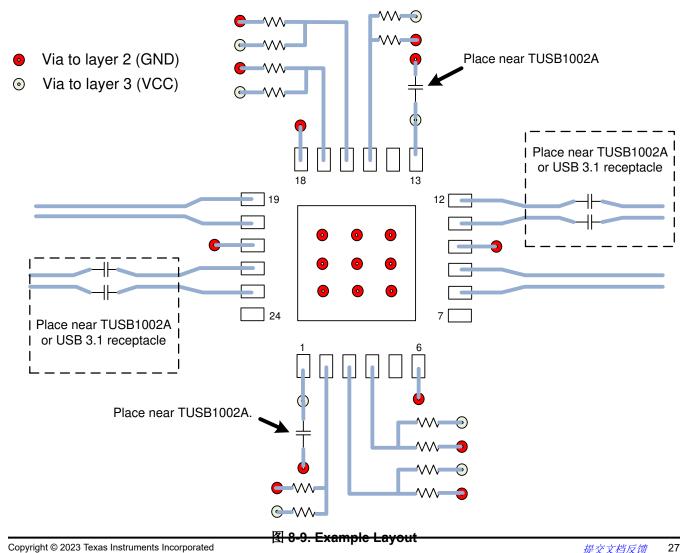

### 8.3.1 Design Requirements