# Mode Pin Precautions for TPD2S701-Q1 and TPD2S703-Q1

Cameron Phillips

## ABSTRACT

In the TPD2S701-Q1 and TPD2S703-Q1 overvoltage protection devices, the MODE corner pin must be set up correctly to ensure the devices enter the correct mode. If the MODE pin loses connection, breaks, or is otherwise floating there is potential for damage to downstream devices. This application report will show the MODE pin functionality, effects of faults associated with the MODE pin, and solutions that protect all devices connected.

#### Contents

| 1 | Introduction    | 2 |

|---|-----------------|---|

| 2 | How to Set Mode | 2 |

| 3 | Mode Pin Faults | 3 |

| 4 | Solutions       | 3 |

| 5 | Summary         | 5 |

|   |                 |   |

#### List of Figures

| 1 | Pinout of TPD2S701-Q1 and TPD2S703-Q1 | 2 |

|---|---------------------------------------|---|

| 2 | Mode Functionality Block Diagram      | 2 |

| 3 | MODE Pin Fault                        | 3 |

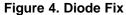

| 4 | Diode Fix                             | 4 |

| 5 | Zener Diode Fix                       | 4 |

## Trademarks

All trademarks are the property of their respective owners.

## 1 Introduction

The TPD2S701-Q1 and the TPD2S703-Q1 family of devices are used for overvoltage and ESD protection of the USB data lines D+ and D–. The TPD2S701-Q1 has short-to- $V_{BUS}$  protection while the TPD2S703-Q1 has short-to- $V_{BUS}$  and short-to-battery protection.

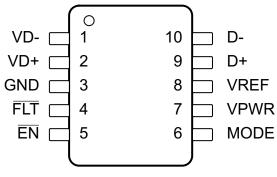

Figure 1. Pinout of TPD2S701-Q1 and TPD2S703-Q1

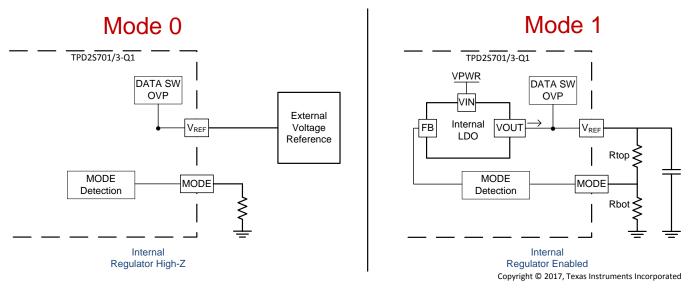

Both TPD2S701-Q1 and TPD2S703-Q1 have the same pinout as in Figure 1. Pin 6 in both the DGS and the DSK packages is the MODE pin. This pin selects between the two device modes: Mode 0 where there is an external supply to the VREF pin that sets the overvoltage protections, and Mode 1 that can be thought of as an internal voltage regulator for VREF whose output is controlled by the feedback being produced in the resistor divider at the MODE pin. In essence, this pin is the deciding factor for whether pin 8, VREF, is an input being supplied with an external reference or if VREF is an output to which an internal LDO is outputting nominally 3.3 V. This functionality can be modeled in Figure 2

Figure 2. Mode Functionality Block Diagram

# 2 How to Set Mode

2

The way that the TPD2S701/3-Q1 can distinguish between the two modes is through the resistance the MODE pins see with respect to ground. If it sees that the resistance to ground is less than 2.6 k $\Omega$ , it knows that an external power supply will power VREF which is classified as mode 0. For the device to know that it is in mode 1, the parallel resistance of the resistor from the MODE pin to VREF, Rtop, and MODE pin to ground, Rbot is greater than 14 k $\Omega$ . When the device powers up, it delays 150 µs to measure the resistance from the MODE pin to ground to see what mode it should be set in. Additionally, it will take extra time to turn on if set in mode 1 because the capacitor on VREF has to be charged. This

charging time is outlined in the data sheet in Section 9.2.2.2. The reason that mode 1 has to do with the parallel resistance of Rtop and Rbot instead of just Rbot is that when the device is initially powered the VREF pin, when not externally powered, is considered as ground too. Therefore, to be certain the device is in a known state, the resistor from MODE to ground must be less than 2.6 k $\Omega$  or the parallel resistance of MODE to VREF and MODE to ground must be greater than 14 k $\Omega$ .

# 3 Mode Pin Faults

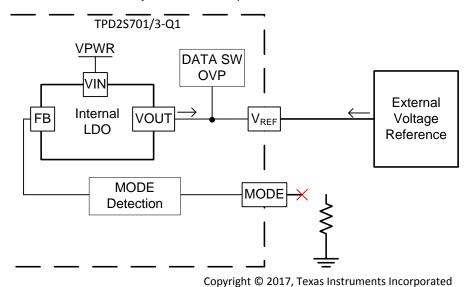

However, even when the schematic for this device is properly set up, faults can still occur if the MODE pin somehow becomes disconnected or is otherwise floating. For example, system damage may occur if the device is intended to be in mode 0 where an external 3.3-V supply is connected to VREF. If the MODE pin then becomes floating, there is a chance that the mode detection circuitry could mistakenly put the device into mode 1 where it would then try to drive an output on VREF.

Figure 3. MODE Pin Fault

As Figure 3 shows, the MODE pin is disconnected from the resistor to ground and the mode detection circuitry has provided feedback to the internal regulator which caused the regulator to come out of High-Z mode and start driving against the external voltage reference. The internal regulator is based on  $V_{PWR}$  which can be up to 7 V. If the output of the internal regulator to  $V_{REF}$  is at or near 7 V, the external voltage reference would begin sinking 50 mA of current (set by the internal current limit of  $V_{REF}$ ) since the potential of  $V_{REF}$  is higher than its own output. If any other components were connected to the same rail as the external voltage reference, they would all be brought up to  $V_{REF}$ , which could also damage some devices without a maximum rated voltage of > 7 V.

# 4 Solutions

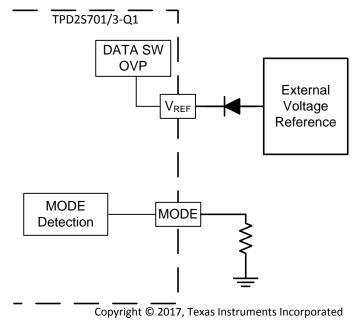

Solutions to this issue are simple. The first solution that can be done is put a blocking diode from the external voltage reference to  $V_{REF}$ . This diode will protect all downstream devices if the MODE pin fault occurs. Consideration should be given to the voltage drop across the diode. This is shown in Figure 4.

However, this solution will not completely solve the issue because the TPD2S701/3-Q1 OVP threshold will not be at the same value as intended by the output of the external voltage reference. Therefore, another solution is to place a bias resistor and a zener diode from the external reference to  $V_{REF}$ , shown in Figure 5.

## Figure 5. Zener Diode Fix

This would mean that  $V_{REF}$  would always stay in the recommended operating range keeping the device in a good state. Note that the zener diode can be set to whatever rail voltage the external voltage reference is at as long as it is within the recommended operating conditions of the device.

4

www.ti.com

# 5 Summary

When functioning properly, the TPD2S701-Q1 and TPD2S703-Q1 are excellent devices for overvoltage and ESD protection on the data lines of a USB controller. While environmental factors can cause the device to be in a different mode than expected, taking preliminary actions as outlined can protect downstream circuitry and the device itself.

Summary

5

## IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated