#### 1 Startup

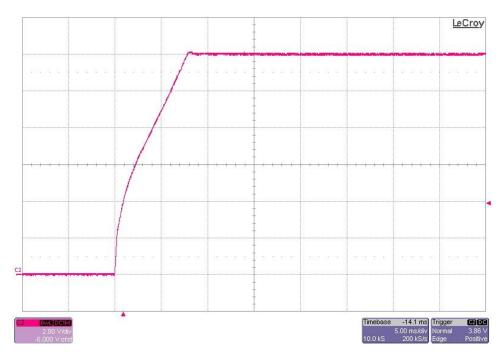

The photo below shows the output voltage startup waveform of a single flyback after the application of 53V in. The 12Voutput wase loaded to 0A. (2V/DIV, 5mS/DIV)

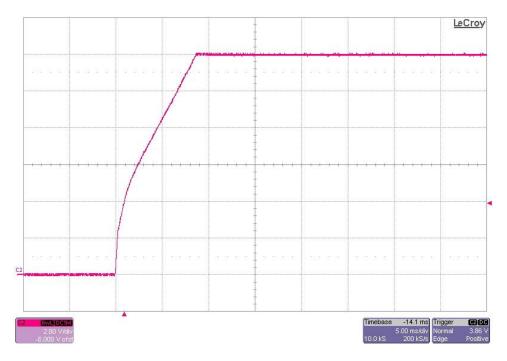

The photo below shows the output voltage startup waveform of a single flyback after the application of 53V in. The 12Voutput wase loaded to 2.5A. (2V/DIV, 5mS/DIV)

# 2 Efficiency

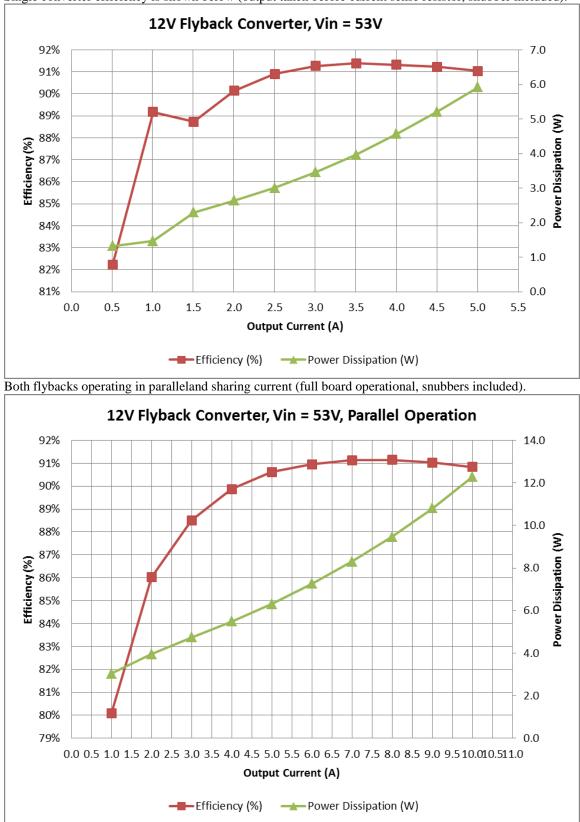

Single converter efficiency is shown below (output taken before current sense resistor, snubber included).

# 3 Output Ripple Voltage

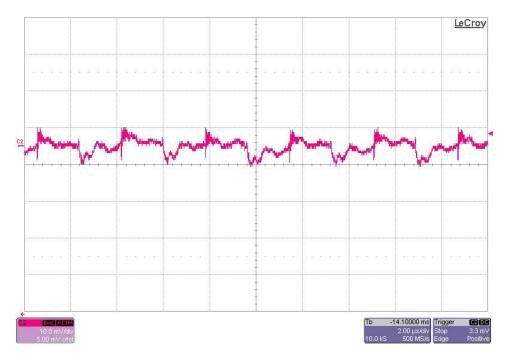

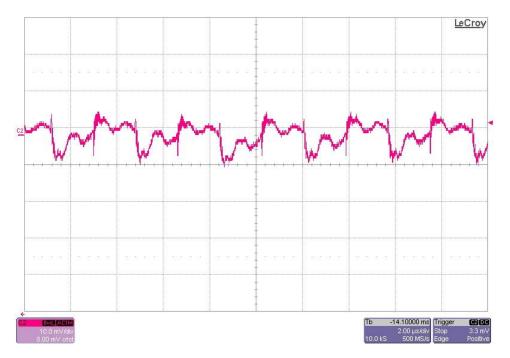

The 12V output ripple voltage is shown in the figure below. The image was taken with the output loaded to 2.5A. The input voltage is set to 53V. (10mV/DIV, 2uS/DIV)

The 12V output ripple voltage is shown in the figure below. The image was taken with the output loaded to 5A. The input voltage is set to 53V. (10mV/DIV, 2uS/DIV)

### 2/28/2013 PMP8906 REVB Test Results

# 4 Load Transients

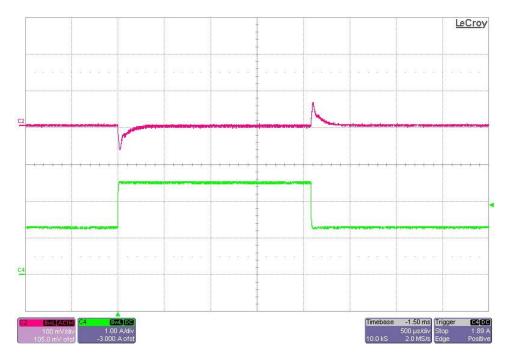

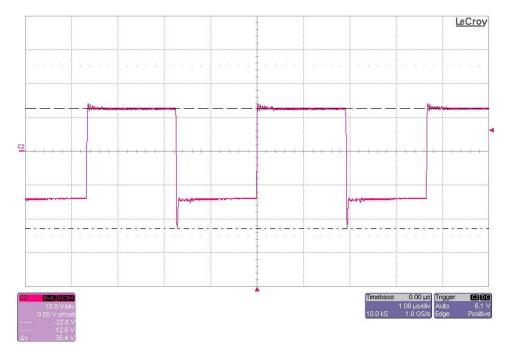

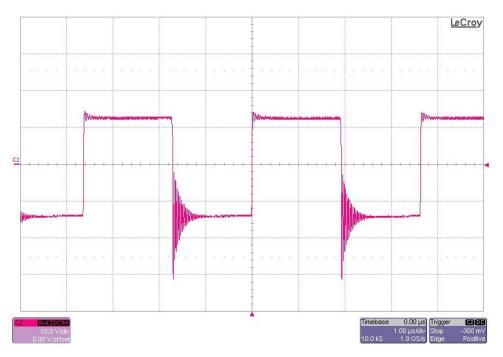

The photo below shows the single flyback output voltage (ac coupled) when the load current is stepped between 1.25A and 2.5A. Vin = 53V. (100mV/DIV, 1A/DIV, 500uS/DIV)

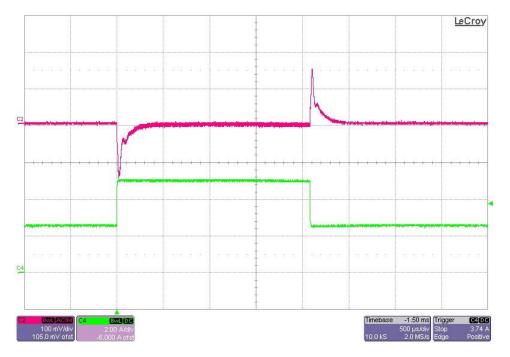

The photo below shows the single flyback output voltage (ac coupled) when the load current is stepped between 2.5A and 5A. Vin = 53V. (100mV/DIV, 2A/DIV, 500uS/DIV)

# 5 Switch Node Waveforms

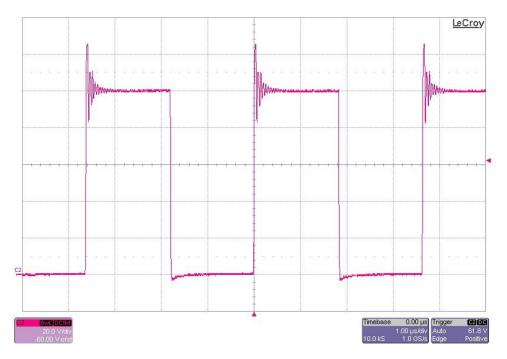

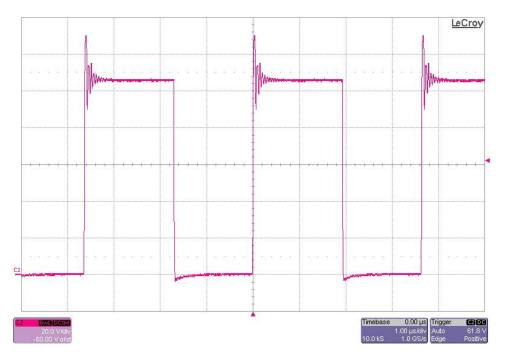

The photo below shows the 12V primary FET switching voltage. The input voltage is 51V and the output is loaded to 2.5A. (20V/DIV, 1uS/DIV)

The photo below shows the 12V primary FET switching voltage. The input voltage is 57V and the output is loaded to 2.5A. (20V/DIV, 1uS/DIV)

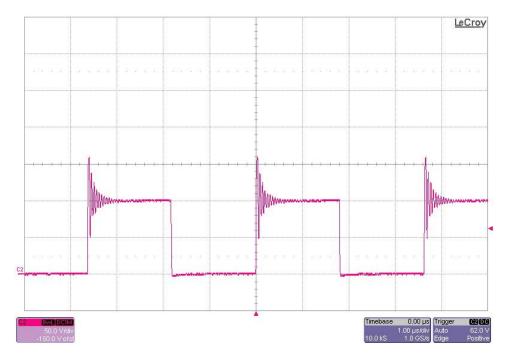

The photo below shows the 12V primary FET switching voltage. The input voltage is 51V and the output is loaded to 5A. (50V/DIV, 1uS/DIV)

The photo below shows the 12V primary FET switching voltage. The input voltage is 57V and the output is loaded to 5A. (50V/DIV, 1uS/DIV)

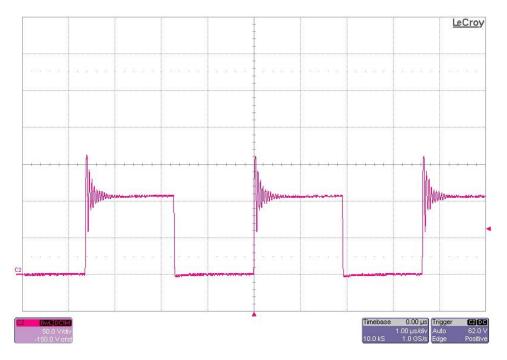

The photo below shows the 12V main secondary Rectifier (D1) switching voltage. The input voltage is 57V and the output is loaded to 5A. (10V/DIV, 1uS/DIV)

The photo below shows the 12V main secondary Rectifier (D1) switching voltage with the diode snubber **removed** (for reference). The input voltage is 57V and the output is loaded to 5A. (10V/DIV, 1uS/DIV)

#### 2/28/2013 PMP8906 REVB Test Results

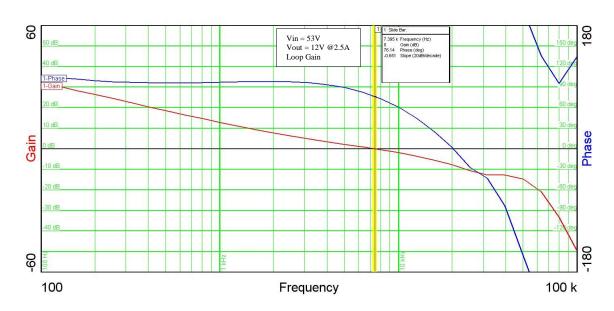

# 6 Control Loop Gain / Stability

The plot below shows the 12V loop gain and phase margin with the output loaded to 2.5A (without load share controller and C22 = 2200 pF, R132 = 0). The input voltage was set to 53V.

Band Width = 7.40KHz,

Phase Margin = 76 degrees

(12V@2.5A)

The plot below shows the 12V loop gain and phase margin with the output loaded to 2.5A (without load share controller and C22 = 2200 pF, R132 = 0). The input voltage was set to 53V.

#### 2/28/2013 PMP8906 REVB Test Results

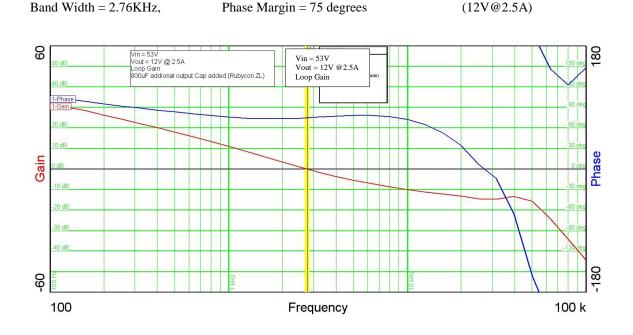

The plot below shows the 12V loop gain and phase margin with the output loaded to 2.5A (without load share controller and C22 = 2200pF, R132 = 0) and 800uF additional output cap added. The input voltage was set to 53V.

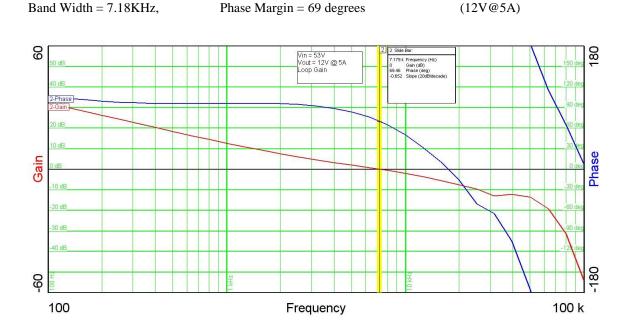

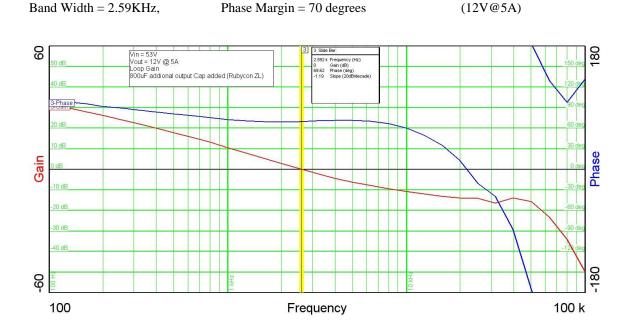

The plot below shows the 12V loop gain and phase margin with the output loaded to 5A (without load share controller and C22 = 2200pF, R132 = 0) and 800uF additional output cap added. The input voltage was set to 53V.

### 7 Photo

The photo below shows the PMP8906 REVB assy (snubbers not shown).

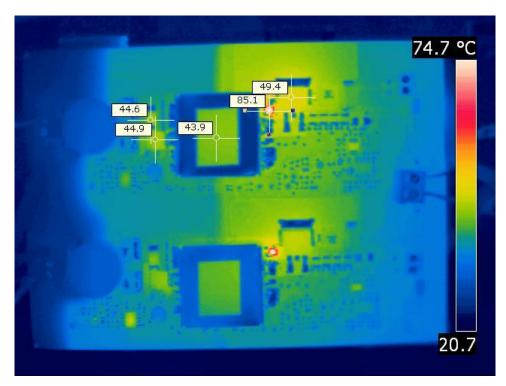

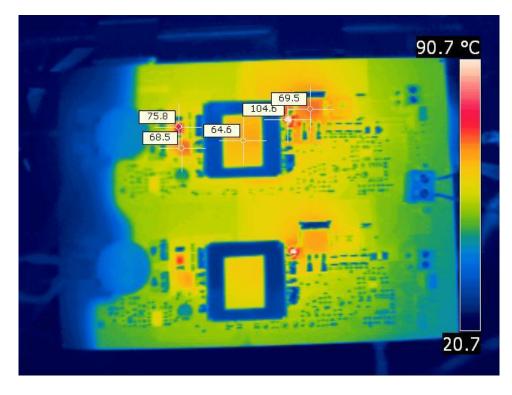

# 8 Thermal Image

A thermal image is shown below when operating in parallel at 53V input and 5A output (2.5A each flyback), with no airflow.

A thermal image is shown below when operating in parallel at 53V input and 10A output (5A each flyback), with no airflow.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (https://www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated