#### TEST REPORT

### **1** Introduction

PMP9013A is an IEEE802.3at, Type 2 compliant powered device. The EVM is a low cost self driven synchronous flyback designed for 22.5W output power at 5V/4.5A from either an adapter (21.6V - 57VDC) or power over Ethernet (PoE) input.

### 2 Configurable features

#### 1.1 Features

- Good efficiency, self driven, synchronous flyback design.

- Gigabit Ethernet pass through interface

- 21.6V and 57V adapter input capability

- IEEE 802.3at type-2 hardware classification with secondary side status flag (T2P)

- 5V @ 4.5A DC output.

- Ultra-Low Power Sleep Modes

#### 1.2 Applications

- IEEE 802.3at-compliant devices

- Video and VoIP telephones

- Multiband access points

- Security cameras

- Pico-base stations

# 3 Electrical specifications

#### **TPS23751EVM-104 Electrical and Performance Specifications**

| Parameter                          |                                        | Condition                                           |           | Min  | Тур  | Max  | Units   |

|------------------------------------|----------------------------------------|-----------------------------------------------------|-----------|------|------|------|---------|

| Power Interface                    |                                        | 1                                                   |           | T    | ſ    | 1    |         |

| Input Voltage                      |                                        | Applied to the power pins of<br>connectors J1 or J3 |           | 0    | -    | 57   | - Volts |

| Operating Voltage                  |                                        | After start up.                                     |           | 30   | -    | 57   |         |

| Input UVLO, POE input J1           |                                        | Rising input voltage                                |           | -    | -    | 40   |         |

|                                    |                                        | Falling input voltage                               |           | 30   | -    | -    |         |

| Input UVLO, adapt                  | er J3                                  | Rising input voltage                                |           |      | 18.7 |      |         |

| Detection voltage                  |                                        | @ device terminals                                  |           | 1.4  | -    | 10.1 |         |

| Classification volta               | ge                                     | @ device terminals                                  | 5         | 11.9 | -    | 23.0 |         |

| Classification curre               | nt                                     | Rclass = 63.4 ohm                                   | S         | 38   | -    | 42   |         |

| Inrush current-limit               |                                        |                                                     |           |      | -    | 180  | mA      |

| Operating current-I                | imit                                   |                                                     |           | 850  | -    | 1200 |         |

| DC/DC Converter                    |                                        |                                                     |           | •    |      |      |         |

| Output Voltage                     | 21.6V ≤ Vin ≤ 57V, ILOAD ≤ ILOAD (max) |                                                     | 5V output | 4.75 | 5.00 | 5.25 | Volts   |

| Output Current                     | 21.6V ≤ Vin ≤ 57V                      |                                                     | 5V output | -    | -    | 4.5  | Amps    |

| Output ripple<br>voltage, pk-to-pk | Vin = 44V, ILOAD = 4.5A                |                                                     | 5V output | -    | 30   | -    | mV      |

| Efficiency, dc-dc<br>converter     | Vin = 48V, ILOAD = 4.5A                |                                                     | 5V output | -    | 91   | -    | %       |

| Efficiency, end-<br>to-end         | Vin = 48V, ILOAD = 4.5A                |                                                     | 5V output | -    | 88   | -    | %       |

| Switching<br>frequency             |                                        |                                                     |           | 225  | -    | 275  | kHz     |

#### TEST REPORT

# 4 Efficiency

Efficiency is shown below with 48V applied to the adapter input connector (J3). Adapter efficiency measured from the input J3 to output connector, J6 is represented as Nadp. DC-DC converter only efficiency measured from the input (VDD-PWRGND test points, TP6/TP19) to output connector, J6 is represented as Ncnvrtr.

| Vin   | Vcnvrtr | lin   | Vout  | lout  | Nadp  | Ncnvrtr |

|-------|---------|-------|-------|-------|-------|---------|

| 48.00 | 47.64   | 0.025 | 4.970 | 0.000 | 0.00  | 0.00    |

| 47.98 | 47.58   | 0.079 | 4.970 | 0.506 | 66.77 | 67.33   |

| 47.97 | 47.54   | 0.131 | 4.970 | 1.005 | 79.48 | 80.20   |

| 47.95 | 47.46   | 0.239 | 4.970 | 2.004 | 86.91 | 87.81   |

| 47.92 | 47.39   | 0.348 | 4.960 | 2.999 | 89.20 | 90.20   |

| 47.89 | 47.33   | 0.461 | 4.960 | 4.000 | 89.87 | 90.93   |

| 47.88 | 47.29   | 0.519 | 4.960 | 4.500 | 89.82 | 90.94   |

# 5 End-end efficiency

End to end efficiency is shown below with 48Vinput from the J1 ethernet connector to output connector, J6 is represented as Npoe.

| Vin   | lin   | Vout  | lout  | Npoe  |

|-------|-------|-------|-------|-------|

| 48.00 | 0.025 | 4.970 | 0.000 | 0.00  |

| 47.98 | 0.079 | 4.970 | 0.506 | 66.77 |

| 47.97 | 0.132 | 4.970 | 1.005 | 78.88 |

| 47.95 | 0.242 | 4.970 | 2.004 | 86.01 |

| 47.92 | 0.353 | 4.960 | 2.999 | 87.94 |

| 47.89 | 0.470 | 4.960 | 4.000 | 88.24 |

| 47.88 | 0.529 | 4.960 | 4.500 | 88.12 |

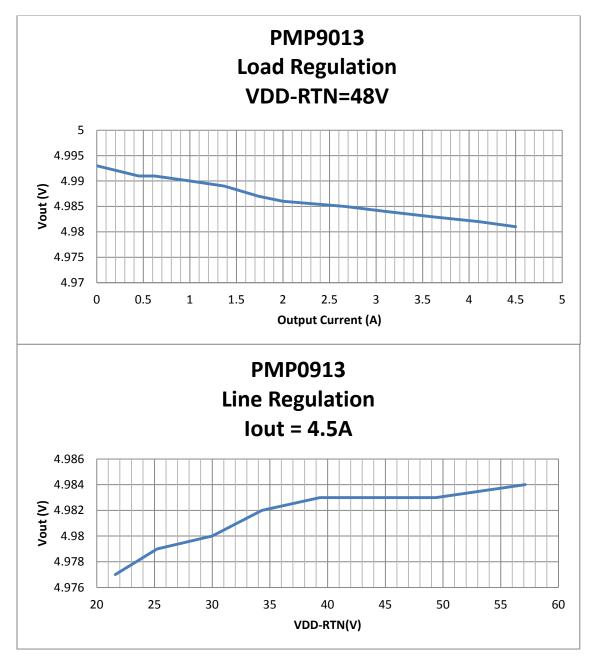

# 6 Load Regulation

PMP9013A load regulation is less than +/-10mV.

#### TEST REPORT

# 7 Start up

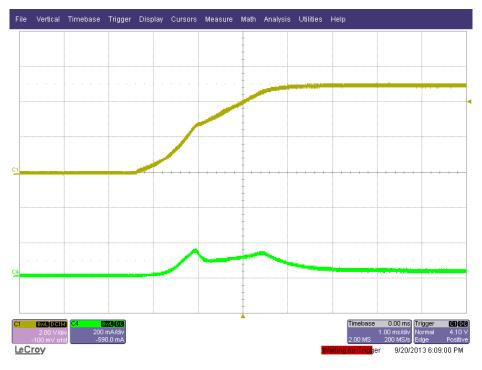

The scope plot below shows the 5V output voltage startup waveform after the application of 48Vdc at J1 (Ethernet connector. The output was loaded to 0A.

The scope plot below shows the 5V output voltage startup waveform after the application of 48Vdc at J1 (Ethernet connector. The output was loaded to 4.5A using an electronic load in CR mode.

#### TEST REPORT

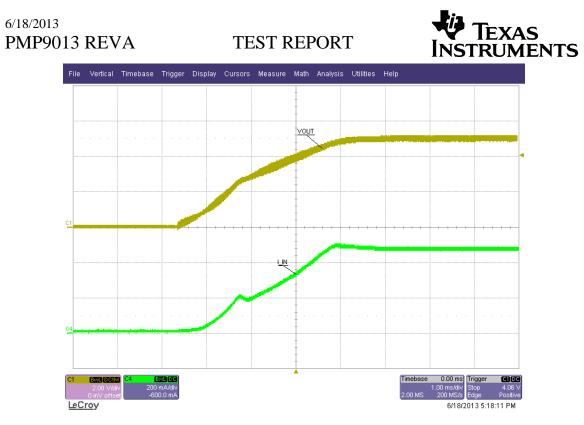

The scope plot below shows the 5V output voltage startup waveform after the application of 48Vdc at J1 (Ethernet connector. The output was loaded to 0A.

The scope plot below shows the 5V output voltage startup waveform after the application of 48Vdc at J1 (Ethernet connector. The output was loaded to 4.5A using an electronic load in CR mode.

The scope plot below shows the 5V output voltage startup waveform after the application of 48Vdc at J1 (Ethernet connector. The output was loaded to ~4A using a decade box.

### 8 Switch Node Waveforms

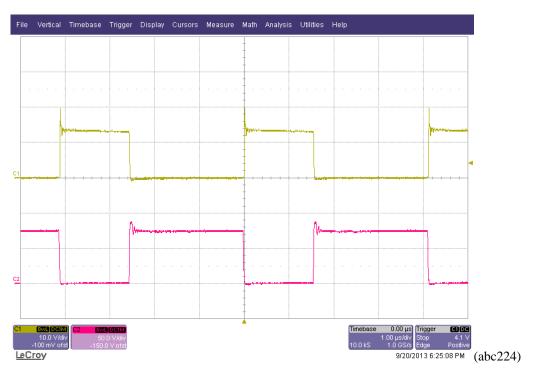

The scope plot below shows the waveforms on the drain of the secondary side FET (CH1) and primary side FET (CH2). The output is loaded at 4.0A. Vin = 48Vdc at J1

# 9 Output Ripple Voltage

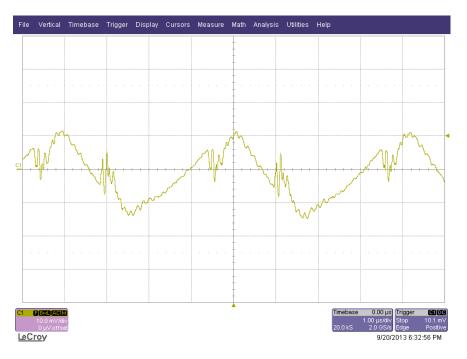

The 5V output ripple voltage is shown in the scope plot below (J6 connector across pins w/tip and ring). The scope plot was taken with the output loaded to 4.5A.Vin = 48Vdc at J1.

# **10 Load Transients**

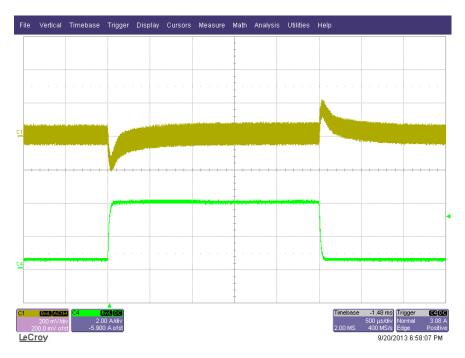

The scope plot below shows the 5V output voltage (at J6) when the load current is pulsed from 0.5 to 4.0A at a 300A/ms slew rate. Vin = 48Vdc at J1.

# 11 Control Loop Gain / Stability

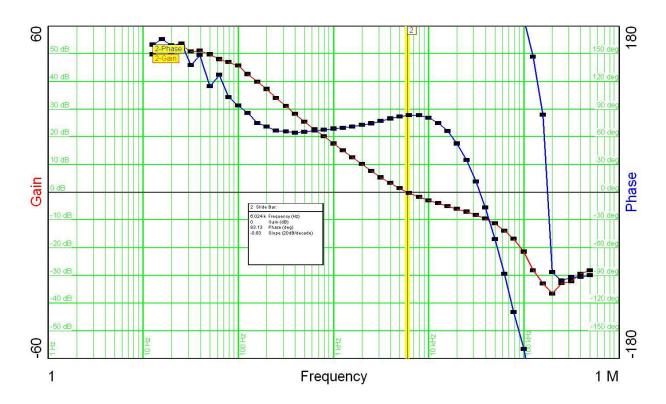

The figure below shows the closed loop response of the PMP9013 at 48V input and a 4.5A electronic load.

The table below shows the loop gain and phase margin.

| Input voltage | 48VDC     |              |  |  |

|---------------|-----------|--------------|--|--|

| Gain/Phase    | Crossover | Phase Margin |  |  |

| PMP9013A      | 6.0kHz    | 83°          |  |  |

# TEST REPORT

The image below shows the board with a 48VDC input. The ambient temperature was 25C with no forced air flow. The output was loaded with 4.5A

The below image shows the PMP9013 board and relative solution size.

**TEST REPORT**

The table below shows the results of the Sifos Technologies PoE Powered Device Analyzer using a 1A load.

| Test Parameter | Description                                                                                                                                                                                                  | Analyzer Results | Pass/Fail |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------|

| Rdet           | Detection resistance (2.7 to 10.1 Volt band)                                                                                                                                                                 | 24.62k ohms      | Р         |

| Cdet           | Detection capacitance (2.7 to 10.1 Volt band)                                                                                                                                                                | 0.113uF          | Р         |

| IClass         | Classification signature current (15 – 20 Volt band)                                                                                                                                                         | 39.5mA           | Р         |

| Class          | PD Class determined from classification                                                                                                                                                                      | 4                | Р         |

| Туре           | PD Type determined from classification                                                                                                                                                                       | 2                | -         |

| Von            | Voltage at which PD draws load current                                                                                                                                                                       | 39.1V            | Р         |

| Voff           | Voltage at which PD stops load current                                                                                                                                                                       | 33.8V            | Р         |

| Einr           | Capacitive charging energy (watt-sec) over worst 20msec sub-<br>interval of Inrush interval – a failure indicates an linrush_pd<br>violation while a pass indicates very low inrush interoperability<br>risk | 0.123Ws          | Ρ         |

|                |                                                                                                                                                                                                              |                  |           |

| Power          | Single-Event Classification Average PD power draw following the 50msec inrush interval                                                                                                                       | 5.76W            | Р         |

| Peak           | Maximum PD transient load following the 50msec inrush interval                                                                                                                                               | 5.84W            | P         |

| Imax           | Maximum ransient load current sampled following the 50msec<br>inrush interval                                                                                                                                | 122.1mA          | -         |

| Imin           | Minimum load current sampled after power-up. (Note: PD's meeting DC MPS signature criteria described in IEEE 802.3at paragraph 33.3.8 will report 10mA or higher.)                                           | 119.1mA          | Р         |

| lavg           | Average load current following the 50msec inrush interval                                                                                                                                                    | 120.2mA          | -         |

|                | Two-Event Classification                                                                                                                                                                                     |                  |           |

| Imark          | Class pulse discharge current measured between class pulses                                                                                                                                                  | 0.84mA           | Р         |

| Power          | Average PD power draw following the 50msec inrush interval                                                                                                                                                   | 5.89W            | Р         |

| Peak           | Maximum PD transient load following the 50msec inrush interval                                                                                                                                               | 6W               | Р         |

| Init           | Power load measured between end of inrush interval (50msec)<br>and Tdelay (80msec) (see IEEE 802.3at paragraph 33.3.7.3)                                                                                     | 0.13W            | Р         |

| Imax           | Maximum transient load current sampled following the 50msec inrush interval                                                                                                                                  | 111.1mA          | -         |

| Imin           | Minimum load current sampled after power-up. (Note: PD's meeting DC MPS signature criteria described in IEEE 802.3at paragraph 33.3.8 will report 10mA or higher.)                                           | 108.2mA          | Р         |

| lavg           | Average load current following the 50msec inrush interval                                                                                                                                                    | 109.3mA          | -         |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (https://www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated