# Applications of Low-Voltage Differential Signaling (LVDS) in Ultrasound Scanners

Ikechukwu Anyiam

### ABSTRACT

Medical imaging devices like ultrasound scanners often include a data path where data must be passed between multiple units in the system. This creates concerns for designers including noise immunity, low EMI, number of interface lines, driving capability, and power consumption while communicating between these interfaces. This document will examine how the different units in ultrasound scanners communicate with each other, with a particular focus on where LVDS or similar signaling is applicable.

#### Contents

| 1 | Introduction                 | 1 |

|---|------------------------------|---|

| 2 | AFE and Beamformer Block     | 2 |

| 3 | Clock Tree Block             | 3 |

| 4 | DSP and User Interface Block | 4 |

| 5 | Summary                      | 4 |

|   |                              |   |

### List of Figures

| 1 | Ultrasound Scanner Simplified Block Diagram | 2 |

|---|---------------------------------------------|---|

| 2 | AFE Board and Beamformer Subsystem          | 2 |

| 3 | Clock Tree Subsystem                        | 3 |

| 4 | DSP and User Interface Subsystem            | 4 |

|   |                                             |   |

# Trademarks

## 1 Introduction

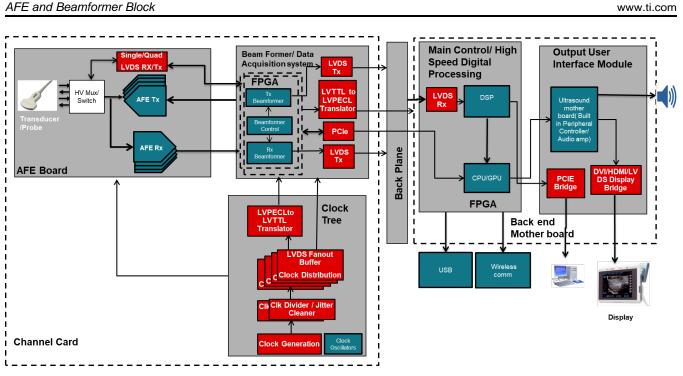

Figure 1 depicts a functional breakdown of an ultrasound scanner. A conceptual data path for an ultrasound scanner begins with a pulse generated and transmitted from numerous transducer elements. While this pulse illuminates a specific region of the body, the transducer elements switch into receive mode. The pulse propagates through the body as high frequency sound waves and as it travels, portions of the wavefront energy are reflected back to the transducer/receiver.

1

www.ti.com

### Figure 1. Ultrasound Scanner Simplified Block Diagram

After passing through an amplifier and filter stage, this energy is transmitted through an ADC on the AFE (Analog Front End) board. The number of ADC channels normally varies from 8 to 512 (depending on the system), but can be even more. An LVDS interface is usually integrated into the ADCs, and the ADCs serialize and digitize the data coming out before sending it to the beamformer.

After beamforming, the data is processed in the DSP block. The CPU creates the final image, which is then displayed on a monitor. In addition to storing/processing the final image, the CPU also sends electrical signals to the beamformer/transducer so that the transducer can emit more sound waves.

#### 2 **AFE and Beamformer Block**

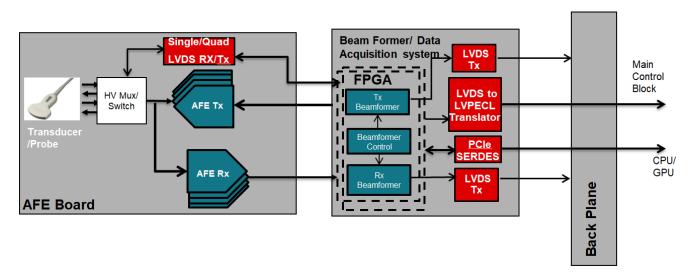

Figure 2 takes a closer look at the AFE board and beamformer/DAQ system. Although LVDS functionality is increasingly integrated (like the interface between the AFE ADCs and beamforming FPGAs), there are still many use cases for discrete LVDS components in ultrasound scanners.

www.ti.com

For example, when the beamfomer unit sends control signals to the transducer to verify what signals (temperature, status, and so forth) are being sent, and to the HV MUX/switch to control the transmit/receive function of the transducer, LVDS drivers like the DS90LV047A are usually utilized due to the distance between the beamformer unit and the transducer.

Additionally, there is the case of data being sent to the DSP from the beamformer, or vice versa. Since the input/output signals of these units may be incompatible with each other, a variety of standard translators like LVDS to LVPECL (SN65LVDS101), LVTTL to LVPECL (SN65EPT22), and so forth. can be utilized. Bus tranceivers (SN74LVC16T245) would also be useful here due to the bidirectional nature of the signals.

# 3 Clock Tree Block

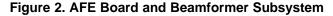

Figure 3 takes a closer look at the clock tree block. Each element of the ultrasound scanner requires a clean, precise clock.

Figure 3. Clock Tree Subsystem

LVDS fanout buffers like the SN65LVDS108 device can be utilized to repeat and distribute clock signals from a single clock generator across large distances to each element of the ultrasound scanner with high noise immunity and low propagation delay times. Additionally, if some elements of the ultrasound scanner only accept specific standards other than LVDS, standard translators like LVDS/LVPECL to LVTTL (SN65LVDS108) can be utilized to help distribute the clocks.

3

www.ti.com

DSP and User Interface Block

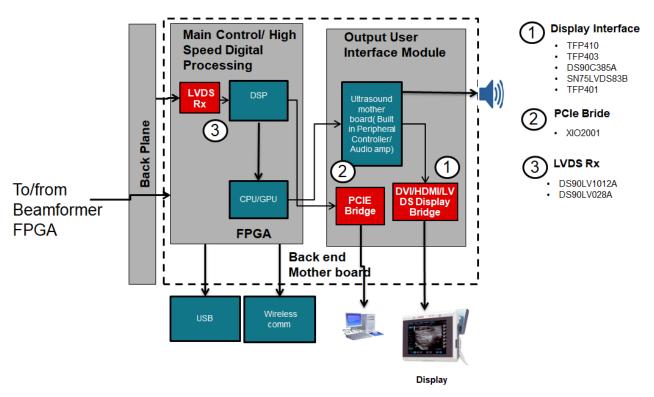

#### 4 **DSP and User Interface Block**

Figure 4 takes a closer look at the DSP and user interface block. After the CPU sends the processed data to a computer via PCIe bridge, a technician can view the results of a scan on the computer monitor. They can also alter features of the scan (frequency of the sound waves being emitted, duration of each pulse, and so forth) with a control panel connected to the computer.

Figure 4. DSP and User Interface Subsystem

The CPU also sends image data to an HDMI/DVI receiver like the TFP401, TFP403, and TFP501. This data is then sent to an LVDS transmitter like the SN75LVDS83B, and can then be connected to a display for viewing.

#### 5 Summary

In summary, LVDS is a preferred method of communication when transmitting high-speed data over longer distances or when there are concerns about EMI, power consumption, or cable cost/PCB layer cost.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated