*RM44x Microcontroller* Silicon Revision A

# **Silicon Errata**

Literature Number: SPNZ231B July 2015-Revised May 2016

### Contents

| 1 | Device Nomenclature                                  | 4  |

|---|------------------------------------------------------|----|

| 2 | Revision Identification                              | 5  |

| 3 | Silicon Changes From Previous Device Revision        | 6  |

| 4 | Known Design Exceptions to Functional Specifications | 7  |

| 5 | Revision History                                     | 12 |

### List of Figures

| 1 | Device Revision Code Identification  | 5  |

|---|--------------------------------------|----|

| 2 | Shared Input Channel in "Open" State | 9  |

| 3 | Example ADC1/ADC2 Channel Connection | 10 |

#### List of Tables

| 1 | Device Revision Codes                                | 5  |

|---|------------------------------------------------------|----|

| 2 | Known Design Exceptions to Functional Specifications | 7  |

| 3 | Revision History                                     | 42 |

### RM44x Microcontroller

This document describes the known exceptions to the functional specifications for the device.

#### **1** Device Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all MCU devices. Each MCU commercial family member has one of three prefixes: X, P, or NULL [blank] (for example, xRM48L952). These prefixes represent evolutionary stages of product development from engineering prototypes (X) through fully qualified production devices (NULL[blank]).

Device development evolutionary flow:

- **X** Experimental device that is not necessarily representative of the final device's electrical specifications.

- **P** Final silicon die that conforms to the device's electrical specifications but has not completed quality and reliability verification.

- **NULL** Fully-qualified production device.

X and P devices are shipped against the following disclaimer:

"Developmental product is intended for internal evaluation purposes."

Production devices have been characterized fully, and the quality and reliability of the device have been demonstrated fully. TI's standard warranty applies.

Predictions show that prototype devices (X or P) have a greater failure rate than the standard production devices. Texas Instruments recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

All trademarks are the property of their respective owners.

#### 2 Revision Identification

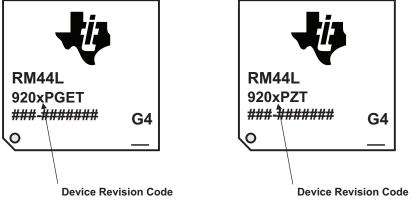

Figure 1 provides examples of the RM44x device markings. The device revision can be determined by the symbols marked on the top of the device.

Figure 1. Device Revision Code Identification

Silicon revision is identified by a device revision code. The code is of the format RM44L920x, where "x" denotes the silicon revision. If x is "A" in the device part number, it represents silicon revision A. If the x is missing in the device part number, it represents the initial (original) silicon revision. Table 1 lists the information associated with each silicon revision.

| Table | 1. | Device | Revision | Codes |

|-------|----|--------|----------|-------|

|-------|----|--------|----------|-------|

| DEVICE PART NUMBER | SILICON REVISION | ORDERABLE PART NUMBERS/COMMENTS                                              |

|--------------------|------------------|------------------------------------------------------------------------------|

|                    |                  | This silicon revision is available as xRM only.                              |

| RM44L920           | Initial          | xRM44L920PGET, xRM44L920PZT<br>xRM44L520PGET, xRM44L520PZT                   |

| RM44L520           |                  | This silicon revision is available as RM for PGE and xRM for PZ.             |

|                    | A                | RM44L920APGET, <b>x</b> RM44L920APZT<br>RM44L520APGET, <b>x</b> RM44L520APZT |

#### 3 Silicon Changes From Previous Device Revision

The following errata have been fixed going from the initial silicon revision (silicon revision 0) to silicon revision A. For a description of these errata see the initial silicon revision errata document SPNZ209.

| Erratum    | Considerations When Migrating From Revision 0 to Revision A Silicon |

|------------|---------------------------------------------------------------------|

| DEVICE#41  | May leave workaround in place, no change to SW required.            |

| DEVICE#42  | May leave workaround in place, no change to SW required.            |

| SSWF021#44 | Evaluate impact of additional 384 OSCIN cycles to PLL lock time.    |

#### **Errata Which Have Been Fixed**

TEXAS INSTRUMENTS

www.ti.com

#### 4 Known Design Exceptions to Functional Specifications

The following table lists the known exceptions to the functional specifications for the device.

#### Table 2. Known Design Exceptions to Functional Specifications

| Title                                                                                                                                                                                             | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| ADC#1 — Injecting current into an input channel shared between the two ADCs causes a DC offset in conversion results of other channels                                                            | . 9  |

| AHB_ACCES_PORT#3 (ARM ID-529470) — Debugger may display unpredictable data in the memory browser window if a system reset occurs                                                                  | 12   |

| <b>CORTEX-R4#26 (ARM ID-577077)</b> — Thumb STREXD Treated As NOP If Same Register Used For Both Source Operands                                                                                  | 13   |

| CORTEX-R4#27 (ARM ID-412027) — Debug Reset Does Not Reset DBGDSCR When In Standby Mode                                                                                                            | 14   |

| CORTEX-R4#33 (ARM ID-452032) — Processor Can Deadlock When Debug Mode Enables Cleared                                                                                                             | 15   |

| CORTEX-R4#46 (ARM ID-599517) — CP15 Auxiliary ID And Prefetch Instruction Accesses Are UNDEFINED                                                                                                  | 16   |

| <b>CORTEX-R4#55 (ARM ID-722412)</b> — CPACR.ASEDIS and CPACR.D32DIS return incorrect value when implementation includes floating point unit.                                                      | 17   |

| CORTEX-R4#57 (ARM ID-737195) — Conditional VMRS APSR_Nzcv, FPSCR May Evaluate With Incorrect Flags                                                                                                | 18   |

| CORTEX-R4#58 (ARM ID-726554) — DBGDSCR.Adadiscard Is Wrong When DBGDSCR.Dbgack Set                                                                                                                | 19   |

| CORTEX-R4#61 (ARM ID-720270) — Latched DTR-Full Flags Not Updated Correctly On DTR Access.                                                                                                        | 20   |

| <b>CORTEX-R4#66 (ARM ID-754269)</b> — Register Corruption During a Load-Multiple Instruction at an Exception Vector .                                                                             | 21   |

| CORTEX-R4#67 (ARM ID-758269) — Watchpoint On A Load Or Store Multiple May Be Missed.                                                                                                              | 22   |

| DCC#24 — Single Shot Mode Count may be Incorrect                                                                                                                                                  | 23   |

| DEVICE#142 — CPU Abort Not Generated on Write to Unimplemented MCRC Space                                                                                                                         | 24   |

| <b>DEVICE#B053</b> — CPU code execution could be halted on a device warm reset if the core power domain # 2 is disabled by software.                                                              | 25   |

| DEVICE#B063 — Incorrect PSCON Compare Error                                                                                                                                                       | 26   |

| DEVICE#B066 — HCLK Stops Prematurely when Executing from Flash                                                                                                                                    | 27   |

| DMA#27 — DMA Requests Lost During Suspend Mode                                                                                                                                                    | 28   |

| GCM#59 — Oscillator can be disabled while PLL is running                                                                                                                                          | 29   |

| MCRC#18 — CPU Abort Generated on Write to Implemented CRC Space After Write to Unimplemented CRC Space                                                                                            | 30   |

| MIBSPI#110 — Multibuffered SPI in Slave Mode In 3- or 4-Pin Communication Transmits Data Incorrectly for Slow<br>SPICLK Frequencies and for Clock Phase = 1                                       | 31   |

| MIBSPI#111 — Data Length Error Is Generated Repeatedly In Slave Mode when I/O Loopback is Enabled                                                                                                 | 32   |

| MIBSPI#137 — Spurious RX DMA REQ from a Slave mode MIBSPI                                                                                                                                         | 33   |

| MIBSPI#139 — Mibspi RX RAM RXEMPTY bit does not get cleared after reading                                                                                                                         | 34   |

| <b>NHET#54</b> — PCNT incorrect when low phase is less than one loop resolution                                                                                                                   | 35   |

| NHET#55 — More than one PCNT instruction on the same pin results in measurement error                                                                                                             | 36   |

| SSWF021#45 — PLL Fails to Start                                                                                                                                                                   | 38   |

| <b>STC#26</b> — The value programmed into the Self Test Controller (STC) Self-Test Run Timeout Counter Preload Register (STCTPR) is restored to its reset value at the end of each self test run. | 39   |

| SYS#046 — Clock Source Switching Not Qualified With Clock Source Enable And Clock Source Valid                                                                                                    | 40   |

| <b>SYS#102</b> — Bit field EFUSE_Abort[4:0] in SYSTASR register is read-clear instead of write-clear                                                                                              | 41   |

Known Design Exceptions to Functional Specifications

| www.ti.com | ADC#1 — | Injecting current into an input channel shared between the two ADCs causes a DC offset in |

|------------|---------|-------------------------------------------------------------------------------------------|

|            |         | conversion results of other channels                                                      |

ADC#1 Injecting current into an input channel shared between the two ADCs causes a DC offset in conversion results of other channels

Severity 3 - Medium

**Expected Behavior** External circuit connected to one channel must not affect the conversion result of another channel.

Issue

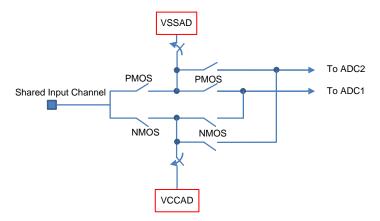

This microcontroller (MCU) has two Analog-to-Digital Converters (ADCs). Some of the input channels are unique to ADC1 while some are shared between ADC1 and ADC2. Figure 2 shows a block diagram of an input channel shared between ADC1 and ADC2.

The PMOS and NMOS switches are open indicating that this shared input channel is not currently being sampled either by ADC1 or by ADC2. Also, there are switches to VCCAD and VSSAD that are closed. If any current is injected into this analog input, any leakage through the open PMOS switch will be shunted to VSSAD. These switches to VSSAD and VCCAD are opened as soon as this shared input channel is being sampled by either ADC1 or ADC2.

ADC#1 — Injecting current into an input channel shared between the two ADCs causes a DC offset in conversion results of other channels www.ti.com

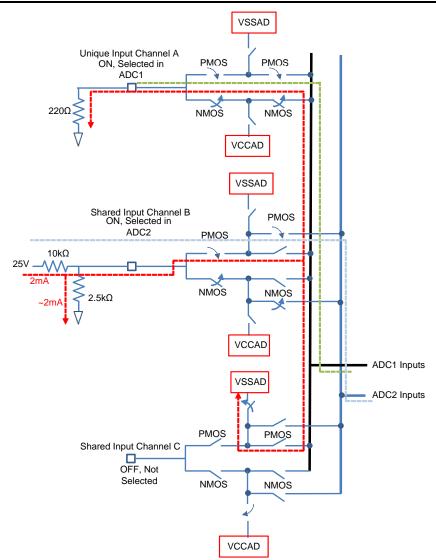

Figure 3. Example ADC1/ADC2 Channel Connection

| www.ti.com    | ADC#1 — Injecting current into an input channel shared between the two ADCs causes a DC offset in conversion results of other channels                                                                                                                                                                                                                                                                                               |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | Figure 3 shows an example where a ADC1 is sampling input channel A which is unique to ADC1, and ADC2 is sampling input channel B, which is a shared-input channel. This is shown by the dashed green and light blue current paths.                                                                                                                                                                                                   |

|               | Another current path is shown in dashed dark red. This is a current injected into channel B as the input level on terminal B is greater than VCCAD - 0.3V. This is a parasitic current that passes through the "open" PMOS switch, and a part of this current flows to ground through the external 220 ohm resistor connected to input channel A. This causes an offset in the conversion result of channel A being sampled by ADC1. |

| Conditions    | This issue occurs if:                                                                                                                                                                                                                                                                                                                                                                                                                |

|               | <ol> <li>Input voltage on a shared input channel being sampled by one ADC is (VCCAD -<br/>0.3V) or higher, and</li> </ol>                                                                                                                                                                                                                                                                                                            |

|               | <ol><li>The second ADC samples another channel such that there is some overlap between<br/>the sampling windows of the two ADCs</li></ol>                                                                                                                                                                                                                                                                                            |

| Implications  | An offset error is introduced in the conversion result of any channel if a current is being injected into a shared input channel.                                                                                                                                                                                                                                                                                                    |

| Workaround(s) | <ol> <li>There are two options to minimize the impact of this issue:</li> <li>Configure the two ADC modules such that their sampling periods do not overlap, or</li> <li>Limit the shared analog input upper limit to be lower than (VCCAD - 0.3V). The PMOS leakage is reduced exponentially if the input is lower than VCCAD - 0.3V.</li> </ol>                                                                                    |

AHB\_ACCES\_PORT#3 (ARM ID-529470) — Debugger may display unpredictable data in the memory browser window if a system reset occurs www.ti.com

#### AHB\_ACCES\_PORT#3 (ARM ID-529470) Debugger may display unpredictable data in the memory browser window if a system reset occurs

| Severity          | 3-Medium                                                                                                                                                                                                                                                                                                                                                        |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Expected Behavior | If a system reset (nRST goes low) occurs while the debugger is performing an access on the system resource using system view, a slave error should be replied to the debugger.                                                                                                                                                                                  |

| Issue             | Instead, the response might indicate that the access completed successfully and return unpredictable data if the access was a read.                                                                                                                                                                                                                             |

| Condition         | System reset is asserted LOW on a specific cycle while the debugger is completing an access on the system using the system view. An example would be the debugger like the CCS's memory browser window is refreshing its content using the system view. This is not an issue for a CPU only reset. This is not an issue during power-on reset (nPORRST) either. |

| Implication(s)    | Data read using the debugger in system view while a system reset occurs may be corrupt, writes may be lost.                                                                                                                                                                                                                                                     |

| Workaround(s)     | This is a workaround for users and tools vendors.<br>Avoid performing debug reads and writes while the device might be reset.                                                                                                                                                                                                                                   |

| www.ti.com | CORTEX-R4#26 (ARM ID-577077) — | Thumb STREXD Treated As NOP If Same Register Used For Both |

|------------|--------------------------------|------------------------------------------------------------|

|            | . , ,                          | Source Operands                                            |

| CORTEX-R4#26 (ARM ID-577077) | Thumb STREXD Treated As NOP If Same Register Used For Both |

|------------------------------|------------------------------------------------------------|

| Source Opera                 | nds                                                        |

| Severity          | 3-Medium                                                                                                                                                                                                                                                                                                                                                                |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Expected Behavior | The STREXD instruction should work in Thumb mode when Rt and Rt2 are the same register.                                                                                                                                                                                                                                                                                 |  |

| Issue             | The ARM Architecture permits the Thumb STREXD instruction to be encoded with the same register used for both transfer registers (Rt and Rt2). Because of this issue, the Cortex-R4 processor treats such encoding as UNPREDICTABLE and executes it as a NOP.                                                                                                            |  |

| Condition         | This error occurs when the processor is in Thumb state and a STREXD instruction is executed with Rt = Rt2.                                                                                                                                                                                                                                                              |  |

|                   | Note: this instruction is new in ARM Architecture version 7 (ARMv7). It is not present in ARMv6T2 or other earlier architecture versions.                                                                                                                                                                                                                               |  |

| Implication(s)    | If this error occurs, the destination register, Rd, which indicates the status of the instruction, is not updated and no memory transaction takes place. If the software is attempting to perform an exclusive read-modify-write sequence, then it might either incorrectly complete without memory being written, or loop forever attempting to complete the sequence. |  |

| Workaround(s)     | This issue can be avoided by using two different registers for the data to be transferred by a STREXD instruction. This may involve copying the data in the transfer register to a second, different register for use by the STREXD.                                                                                                                                    |  |

|                   | Comment: TI Code Generation tool does not generate exclusive access load or store instructions. On these Hercules devices there is no reason to use exclusive access instructions.                                                                                                                                                                                      |  |

#### CORTEX-R4#27 (ARM ID-412027) Debug Reset Does Not Reset DBGDSCR When In Standby Mode

| Severity          | 3-Medium                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Expected Behavior | The debug reset input, PRESETDBGn, resets the processor's debug registers as specified in the ARMv7R Architecture. The debug reset is commonly used to set the debug registers to a known state when a debugger is attached to the target processor.                                                                                                                                                                                                                                                                                                                                                      |

| Issue             | When the processor is in Standby Mode and the clock has been gated off, PRESETDBGn fails to reset the Debug Status and Control Register (DBGDSCR).                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Condition         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   | <ol> <li>The DBGDSCR register has been written so that its contents differ from the reset<br/>values (most fields in this register reset to zero, though a few are UNKNOWN at<br/>reset), and</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                  |

|                   | <ol><li>The processor is in Standby Mode, and the clocks have been gated off, that is<br/>STANDBYWFI is asserted, and</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   | <ol><li>The debug reset, PRESETDBGn, is asserted and de-asserted while the processor<br/>clocks remain gated off.</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                   | Note: the debug reset is commonly used to set the debug registers to a known state when a debugger is attached to the target processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Implication(s)    | This issue affects scan based debug utility developers. The end user should not be affected by this issue if the development tool vendor has implemented the workaround.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                   | If this issue occurs, then after the reset, the DBGDSCR register contains the values that it had before reset rather than the reset values. If the debugger relies on the reset values, then it may cause erroneous debug of the processor. For example, the DBGDSCR contains the ExtDCCmode field which controls the Data Communications Channel (DCC) access mode. If this field was previously set to Fast mode but the debugger assumes that it is in Non-blocking mode (the reset value) then debugger accesses to the DCC will cause the processor to execute instructions which were not expected. |

| Workaround(s)     | This can be avoided by a workaround in the debug control software. Whenever the debugger (or other software) generates a debug reset, follow this with a write of zero to the DBGDSCR which forces all the fields to their reset values.                                                                                                                                                                                                                                                                                                                                                                  |

#### CORTEX-R4#33 (ARM ID-452032) Processor Can Deadlock When Debug Mode Enables Cleared

| Severity          | 3-Medium                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Expected Behavior | The Cortex-R4 processor supports two different debugging modes: Halt-mode and<br>Monitor-mode. Both modes can be disabled. Bits [15:14] in the Debug Status and<br>Control Register (DBGDSCR) control which, if any, mode is enabled. Additionally, debug<br>events can only occur if the invasive debug enable pin, DBGEN is asserted. Deadlocks<br>should not occur when the debug mode is changed. |  |  |

| Issue             | If there are active breakpoints or watchpoints at the time when the debugging modes are disabled via the DBGDSCR or DBGEN, this issue can cause the processor to deadlock (in the case of a breakpoint) or lose data (in the case of a watchpoint).                                                                                                                                                   |  |  |

| Condition         | ondition                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                   | 1. DBGEN is asserted and the processor is running, and                                                                                                                                                                                                                                                                                                                                                |  |  |

|                   | 2. At least one breakpoint or watchpoint is programmed and active, and                                                                                                                                                                                                                                                                                                                                |  |  |

|                   | 3. Either halt-mode debugging or monitor mode debugging is enabled, and                                                                                                                                                                                                                                                                                                                               |  |  |

|                   | <ol><li>Either an instruction is fetched which matches a breakpoint, or an item of data is<br/>accessed which matches a watchpoint, and</li></ol>                                                                                                                                                                                                                                                     |  |  |

|                   | <ol><li>After the instruction or data is accessed, but before the instruction completes<br/>execution, either the DBGEN input is de-asserted or both halt-mode and monitor-<br/>mode debugging are disabled by means of a write the DBGDSCR.</li></ol>                                                                                                                                                |  |  |

| Implication(s)    | This issue affects scan based debug utility developers. The end user should not be affected by this issue if the development tool vendor has implemented the workaround.                                                                                                                                                                                                                              |  |  |

|                   | Depending on which of the conditions are met, the processor will either lose data or deadlock. If the processor deadlocks because of this issue it will still respond to interrupts provided they are not masked.                                                                                                                                                                                     |  |  |

| Workaround(s)     | This issue can be avoided by ensuring that all watchpoints and breakpoints are made inactive before either de-asserting DBGEN or changing the debug mode enables.                                                                                                                                                                                                                                     |  |  |

|                   | 3-Medium                                                                                                                                                                                                                                                                  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Severity          |                                                                                                                                                                                                                                                                           |  |

| Expected Behavior | The ARMv7-R architecture requires implementation of the following two features in CP15:                                                                                                                                                                                   |  |

|                   | <ol> <li>An Auxiliary ID Register (AIDR), which can be read in privileged modes, and the<br/>contents and format of which are IMPLEMENTATION DEFINED.</li> </ol>                                                                                                          |  |

|                   | <ol> <li>The operation to prefetch an instruction by MVA, as defined in the ARMv6<br/>architecture, to be executed as a NOP.</li> <li>Because of this issue, both of these CP15 accesses generate an UNDEFINED exception<br/>on Cortex-R4.</li> </ol>                     |  |

| Issue             | CP15 accesses to Auxiliary ID Register (AIDR) or an operation to prefetch an instruction by MVA will generate an UNDEFINED exception on Cortex-R4.                                                                                                                        |  |

| Condition         | <ul> <li>Either of the following instructions is executed in a privileged mode:</li> <li>MRC p15,1,<rt>,c0,c0,7 ; Read IMPLEMENTATION DEFINED Auxiliary ID Register</rt></li> <li>MCR p15,0,<rt>,c7,c13,1 ; NOP, was Prefetch instruction by MVA in ARMv6</rt></li> </ul> |  |

| Implication(s)    | This issue should only affect portable code supposed to run on different ARM architecture or code running on cached Cortex-R4. Code written for Hercules products should not be affected.                                                                                 |  |

| Workaround(s)     | The CP15 AIDR and MVA registers are not implemented on Cortex-R4 CPU. To avoid this issue, don't read or write to them.                                                                                                                                                   |  |

#### CORTEX-R4#46 (ARM ID-599517) CP15 Auxiliary ID And Prefetch Instruction Accesses Are UNDEFINED

www.ti.com CORTEX-R4#55 (ARM ID-722412) — CPACR.ASEDIS and CPACR.D32DIS return incorrect value when implementation includes floating point unit.

## CORTEX-R4#55 (ARM ID-722412) CPACR.ASEDIS and CPACR.D32DIS return incorrect value when implementation includes floating point unit.

| Severity          | 3-Medium                                                                                                                                                                             |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Expected Behavior | Because the Cortex-R4F CPU does not include the Advance SIMD (NEON) unit or registers D16-D32, it should return a value of 11 (disabled) for CP15 CPACR [31:30] (AESDIS and D32DIS). |

| Issue             | Because of this issue, these bits read zero in implementations of Cortex- R4F which include the floating-point unit.                                                                 |

| Condition         | On reads, CPACR[31:30] actually read as 00 not 11.                                                                                                                                   |

| Implication(s)    | Software cannot uses the CPACR to determine whether Advanced SIMD functionality and registers D16-D32 are available.                                                                 |

| Workaround(s)     | Hercules products do not include Advance SIMD (NEON) unit or registers D16-D32 so there is no need to check for these features.                                                      |

**CORTEX-R4#57 (ARM ID-737195)** — Conditional VMRS APSR\_Nzcv, FPSCR May Evaluate With Incorrect Flags www.ti.com

| CORTEX-R4#57 (A   | RM ID-737195) Conditional VMRS APSR_Nzcv, FPSCR May Evaluate With Incorrect<br>Flags                                                                                                                                                                                                                                                                                                    |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Severity          | 3-Medium                                                                                                                                                                                                                                                                                                                                                                                |

| Expected Behavior | A conditional VMRS APSR_nzcv, FPSCR instruction should evaluate its condition codes<br>using the correct flags.                                                                                                                                                                                                                                                                         |

| Issue             | Under certain circumstances, a conditional VMRS APSR_nzcv, FPSCR instruction may evaluate its condition codes using the wrong flags and incorrectly execute or not execute.                                                                                                                                                                                                             |

| Condition         | The issue requires the following sequence of instructions in ARM state:                                                                                                                                                                                                                                                                                                                 |

|                   | <ol> <li>VMRS<c> APSR_nzcv, FPSCR (formerly FMSTAT<c>), where the condition on the<br/>instruction is not always. This instruction immediately following:</c></c></li> </ol>                                                                                                                                                                                                            |

|                   | 2. A flag-setting integer multiply or multiply and accumulate instruction (e.g. MULS)                                                                                                                                                                                                                                                                                                   |

|                   | <ol> <li>A single-precision floating-point multiply-accumulate (FP-MAC) instruction (e.g.<br/>VMLA), timed such that the accumulate operation is inserted into the pipeline in the<br/>cycle in which the VMRS instruction is first attempted to be issued.</li> </ol>                                                                                                                  |

|                   | To meet the above timing requirements, the VMRS instruction must be three pipeline<br>stages behind the FPMAC. Depending on the rate in which the instructions are fetched,<br>interlocks within this sequence and dual-issuing, this can be up to three other<br>instructions between this pair, plus the multiply. Out-of-order completion of FP-MAC<br>instructions must be enabled. |

| Implication(s)    | If this issue occurs, the VMRS instruction will pass or fail its condition codes incorrectly, and this will appear in any trace produced by the ETM. This can corrupt the N, Z, C, V flag values in the CPSR which will typically affect the program flow.                                                                                                                              |

| Workaround(s)     | Workaround: This issue can be avoided by disabling out-of-order single-precision floating-point multiply-accumulate (SPMAC) instruction completion. Set DOOFMACS, bit [16] in the Secondary Auxiliary Control Register. This will have the side-effect of reducing the performance of SP-MAC operations, though the impact will depend on how these instructions are used in your code. |

#### CORTEX-R4#58 (ARM ID-726554) DBGDSCR.Adadiscard Is Wrong When DBGDSCR.Dbgack Set

| Severity          | 3-Medium                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Expected Behavior | When the DBGDSCR.ADAdiscard bit is set, asynchronous data aborts are discarded, except for setting the DBGDSCR.ADAbort sticky flag. The Cortex-R4 processor ensures that all possible outstanding asynchronous data aborts have been recognized before it enters debug halt state. The flag is immediately on entry to debug halt state to indicate that the debugger does not need to take any further action to determine whether all possible outstanding asynchronous aborts have been recognized. |  |

| Issue             | Because of this issue, the Cortex-R4 processor also sets the DBGDSCR.ADAdiscard bit<br>when the DBGDSCR.DBGack bit is set. This can cause the DBGDSCR.ADAbort bit to<br>become set when the processor is not in debug halt state, and it is not cleared when the<br>processor enters debug halt state. However, the processor does not discard the abort. It<br>is pending or generates an exception as normal.                                                                                        |  |

| Condition         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                   | 1. The processor is not in debug halt state                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|                   | 2. The DBGDSCR.DBGack bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|                   | <ol> <li>An asynchronous data abort (for example, SLVERR response to a store to Normal-<br/>type memory) is recognized</li> </ol>                                                                                                                                                                                                                                                                                                                                                                      |  |

|                   | <b>NOTE:</b> it is not expected that DBGDSCR.DBGack will be set in any Cortex-R4 system                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Implication(s)    | Hercules users will not be impacted by this issue, because Code Composer Studio takes care of this condition.                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                   | If this issue occurs, and the processor subsequently enters debug halt state, the DBGDSCR.ADAbort bit will be set, when in fact no asynchronous data abort has occurred in debug state. Before exiting debug state, the debugger will check this bit and will typically treat it as an error. If no other asynchronous data abort has occurred in debug state, this is a false error.                                                                                                                  |  |

| Workaround(s)     | None.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

#### CORTEX-R4#61 (ARM ID-720270) Latched DTR-Full Flags Not Updated Correctly On DTR Access.

| Severity          | 3-Medium                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Expected Behavior | When the debug Data Transfer Register (DTR) is in non-blocking mode, the latched DTR-full flags (RXfull_I and TXfull_I) record the state of the DTR registers as observed by the debugger and control the flow of data to and from the debugger to prevent race hazards. For example, when the target reads data from DBGDTRRXint, the associated flag RXfull is cleared to indicate that the register has been drained, but the latched value Rxfull_I remains set. Subsequent debugger writes to DBGDTRRXext are ignored because RXfull_I is set. RXfull_I is updated from RXfull when the debugger reads DBGDSCRext such that a debugger write to DBGDTRRXext will only succeed after the debugger has observed that the register is empty. The ARMv7 debug architecture requires that RXfull_I be updated when the debugger reads DBGDSCRext and when it writes DBGDTRRXext. Similarly, TXfull_I must be updated when the debugger reads DBGDSCRext and when it reads DBGDTRTXext. |  |

| Issue             | Because of this issue, RXfull_I and TXfull_I are only updated when the debugger reads DBGDSCRext.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Condition         | <ul> <li>The DTR is in non-blocking mode, that is, DBGDSCR.ExtDCCmode is set to 0b00 and EITHER:</li> <li>1. The debugger reads DBGDSCRext which shows that RXfull is zero, that is, DBGDTRRX is empty, and then</li> <li>2. The debugger writes data to DBGDTRRXext, and</li> <li>3. Without first reading the DBGDSCRext, and before the processor has read from DBGDTRRXint, the debugger performs another write to DBGDTRRXext. OR</li> <li>1. The debugger reads DBGDSCRext which shows that TXfull is one, that is, DBGDTRTX is full, and then</li> <li>2. The debugger reads data from DBGDTRTXext, and then</li> <li>3. The processor writes new data into DBGDTRTXint, and</li> <li>4. Without first reading the DBGDSCRext, the debugger performs another read from DBGDTRTXext.</li> </ul>                                                                                                                                                                                  |  |

| Implication(s)    | The ARMv7 debug architecture requires the debugger to read the DBGDSCRext before attempting to transfer data via the DTR when in non-blocking mode. This issue only has implications for debuggers that violate this requirement. If the issue occurs via data transfer, data loss may occur. The architecture requires that data transfer never occur. Texas Instruments has verified that TI's Code Composer Studios IDE is not affected by this issue.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Workaround(s)     | None.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| www.ti.com | CORTEX-R4#66 (ARM ID-754269) — | Register Corruption During a Load-Multiple Instruction at an Exception<br>Vector |

|------------|--------------------------------|----------------------------------------------------------------------------------|

|            |                                | Vector                                                                           |

|                   | Exception Vector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Severity          | 3-Medium                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Expected Behavior | LDM will execute properly when used as the first instruction of an exception routine.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Issue             | Under certain circumstances, a load multiple instruction can cause corruption of a general purpose register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Condition         | <ul> <li>All the following conditions are required for this issue to occur:</li> <li>A UDIV or SDIV instruction is executed with out-of-order completion of divides enabled</li> <li>A multi-cycle instruction is partially executed before being interrupted by either an IRQ, FIQ or imprecise abort. In this case, a multi-cycle instruction can be any of the following: <ul> <li>LDM/STM that transfers 3 or more registers</li> <li>LDM/STM that transfers 2 registers to an unaligned address without write back</li> <li>LDM/STM that transfers 2 registers to an aligned address with write back</li> <li>TBB/TBH</li> </ul> </li> <li>A load multiple instruction is executed as the first instruction of the exception handler</li> <li>The load multiple instruction itself is interrupted either by an IRQ, FIQ, imprecise abort or external debug halt request.</li> </ul> <li>This issue is very timing sensitive and requires the UDIV or SDIV to complete when the load multiple is in the Issue stage of the CPU pipeline. The register that is corrupted is not necessarily related to the load-multiple instruction and will depend on the state in the CPU store pipeline when the UDIV or SDIV completes.</li> |  |

| Implication(s)    | For practical systems, it is not expected that an interruptible LDM will be executed as the first instruction of an exception handler, because the handler is usually required to save the registers of the interrupted context. Therefore, it is not expected that this issue has any implications for practical systems. If the situation of the issue occurs it will result in the corruption of the register bank state and could cause a fatal failure if the corrupted register is subsequently read before being written.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Workaround(s)     | To work around this issue, set bit [7] of the Auxiliary Control Register to disable out-of-<br>order completion for divide instructions. Code performance may be reduced depending<br>on how often divide operations are used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

#### CORTEX-R4#67 (ARM ID-758269) Watchpoint On A Load Or Store Multiple May Be Missed.

| Severity          | 3-Medium                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Expected Behavior | The Cortex-R4 supports synchronous watchpoints. This implies that for load and store multiples, a watchpoint on any memory access will generate a debug event on the instruction itself.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Issue             | Due to this issue, certain watchpoint hits on multiples will not generate a debug event.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Condition         | <ul> <li>All the following conditions are required for this issue to occur:</li> <li>1. A load or store multiple instruction is executed with at least 5 registers in the register list.</li> <li>2. The address range accessed corresponds to Strongly-Ordered or Device memory.</li> <li>3. A watchpoint match is generated for an access that does not correspond to either the first two or the last two registers in the list.</li> <li>Under these conditions the processor will lose the watchpoint. Note that for a "store multiple" instruction, the conditions are also affected by pipeline state making them timing sensitive.</li> </ul> |

| Implication(s)    | Due to this issue, a debugger may not be able to correctly watch accesses made to<br>Device or Strongly-ordered memory. The ARM architecture recommends that<br>watchpoints should not be set on individual Device or Strongly-ordered addresses that<br>can be accessed as part of a load or store multiple. Instead, it recommends the use of<br>the address range masking functionality provided to set watchpoints on an entire region,<br>ensuring that the watchpoint event will be seen on the first access of a load or store<br>multiple to this region.<br>If this recommendation is followed, this issue will not occur.                   |

| Workaround(s)     | None.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DCC#24            | Single Shot Mode Count may be Incorrect                                                                                                                                                                                                                                                                             |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Severity          | 3-Medium                                                                                                                                                                                                                                                                                                            |  |

| Expected Behavior | When the first clock source counts down to zero, the countdown value remaining for the other clock source is accurately captured.                                                                                                                                                                                   |  |

| Issue             | The first issue is that there is an offset in starting and stopping the two counters due to synchronization with VCLK that leads to a fixed offset. The second issue is that the value remaining in the counter that did not reach zero may be latched while the bits are in transition, giving an erroneous value. |  |

| Condition         | When used in single shot mode and the count value captured is not from VCLK.                                                                                                                                                                                                                                        |  |

| Implication(s)    | The cycle count captured may be incorrect.                                                                                                                                                                                                                                                                          |  |

| Workaround(s)     | Static frequency offset can be removed by making two measurements and subtracting.<br>The sporadic offset can be removed by making multiple measurements and discarding<br>outliers an odd filtering algorithm.                                                                                                     |  |

| DEVICE#142 — CPU  | Abort Not Generated on Write to Unimplemented MCRC Space                                                                                                         | www.ti. |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| DEVICE#142        | CPU Abort Not Generated on Write to Unimplemented MCRC Space                                                                                                     |         |

| Severity          | Low                                                                                                                                                              |         |

| Expected Behavior | A write to the unimplemented region (0xFE00_0200 to 0xFEFF_FFFF) of t module will generate an abort                                                              | he MCRC |

| Issue             | Sometimes a cpu abort does not get generated.                                                                                                                    |         |