# TMS320C6000 DSP Peripheral Component Interconnect (PCI) Reference Guide

Literature Number: SPRU581C January 2007

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from TI under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                |                        | Applications       |                           |

|-------------------------|------------------------|--------------------|---------------------------|

| Amplifiers              | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters         | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                     | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface               | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic                   | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt              | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers        | microcontroller.ti.com | Security           | www.ti.com/security       |

| Low Power Wire-<br>less | www.ti.com/lpw         | Telephony          | www.ti.com/telephony      |

|                         |                        | Video & Imaging    | www.ti.com/video          |

|                         |                        | Wireless           | www.ti.com/wireless       |

Mailing Address:

Post Office Box 655303 Dallas, Texas 75265

**Texas Instruments**

Copyright © 2007, Texas Instruments Incorporated

# Preface

# **Read This First**

#### About This Manual

This document describes the peripheral component interconnect (PCI) port in the digital signal processors (DSPs) of the TMS320C6000<sup>™</sup> DSP family. Also refer to the PCI Specification revision 2.2 for details on PCI interface.

#### Notational Conventions

This document uses the following conventions.

- □ Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register. Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion. Reads from this reserved bit always return the default value. Writes to this reserved bit are ignored. If writing to this field, always write the default value for future device compatibility.

| 3 | 31 1                  | 0     |

|---|-----------------------|-------|

|   | Reserved <sup>†</sup> | Bit   |

| _ | R-0                   | R/W-0 |

**Legend:** R = Read only; R/W = Read/Write; -n = value after reset

<sup>+</sup> If writing to this field, always write the default value for future device compatibility.

#### **Related Documentation From Texas Instruments**

The following documents describe the C6000<sup>TM</sup> devices and related support tools. Copies of these documents are available on the Internet at www.ti.com. *Tip:* Enter the literature number in the search box provided at www.ti.com.

**TMS320C6000 CPU and Instruction Set Reference Guide** (literature number SPRU189) describes the TMS320C6000<sup>™</sup> CPU architecture, instruction set, pipeline, and interrupts for these digital signal processors.

- TMS320C6000 DSP Peripherals Overview Reference Guide (literature number SPRU190) describes the peripherals available on the TMS320C6000<sup>™</sup> DSPs.

- **TMS320C6000 Technical Brief** (literature number SPRU197) gives an introduction to the TMS320C62x<sup>™</sup> and TMS320C67x<sup>™</sup> DSPs, development tools, and third-party support.

- *TMS320C64x Technical Overview* (SPRU395) gives an introduction to the TMS320C64x<sup>™</sup> DSP and discusses the application areas that are enhanced by the TMS320C64x VelociTI<sup>™</sup>.

- **TMS320C6000 Programmer's Guide** (literature number SPRU198) describes ways to optimize C and assembly code for the TMS320C6000<sup>™</sup> DSPs and includes application program examples.

- **TMS320C6000 Code Composer Studio Tutorial** (literature number SPRU301) introduces the Code Composer Studio<sup>™</sup> integrated development environment and software tools.

- Code Composer Studio Application Programming Interface Reference Guide (literature number SPRU321) describes the Code Composer Studio<sup>™</sup> application programming interface (API), which allows you to program custom plug-ins for Code Composer.

- **TMS320C6x Peripheral Support Library Programmer's Reference** (literature number SPRU273) describes the contents of the TMS320C6000<sup>™</sup> peripheral support library of functions and macros. It lists functions and macros both by header file and alphabetically, provides a complete description of each, and gives code examples to show how they are used.

- **TMS320C6000 Chip Support Library API Reference Guide** (literature number SPRU401) describes a set of application programming interfaces (APIs) used to configure and control the on-chip peripherals.

#### Trademarks

4

Code Composer Studio, C6000, C62x, C64x, C67x, TMS320C6000, TMS320C62x, TMS320C64x, TMS320C67x, and VelociTI are trademarks of Texas Instruments.

Peripheral Component Interconnect (PCI)

# **Contents**

| 1 | Overview                                                                                                                                                                                                                                                                                                                                           | 13                         |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 2 | PCI Architecture                                                                                                                                                                                                                                                                                                                                   | 17                         |

| 3 | Метогу Мар                                                                                                                                                                                                                                                                                                                                         | 20                         |

| 4 | Byte Addressing                                                                                                                                                                                                                                                                                                                                    | 21                         |

| 5 | PCI Address Decode                                                                                                                                                                                                                                                                                                                                 | 21                         |

| 6 | Special Considerations for PCI Memory Service6.1Prefetchable Reads (C62x DSP only)6.2PCI Transfers To and From Program Memory (C62x DSP only)6.3PCI EDMA Usage Control (C64x DSP only)                                                                                                                                                             | 22<br>23                   |

| 7 | Slave Transfers         7.1       DSP Slave Writes         7.2       DSP Slave Reads         7.2.1       Nonprefetchable Slave Reads (BAR 1)         7.2.2       Prefetchable Slave Reads (BAR 0)         7.2.3       Prefetchable Slave Read Multiple and Prefetchable Slave Read Line (BAR 0)         7.3       PCI Target-Initiated Termination | 25<br>25<br>26<br>26<br>26 |

| 8 | Master Transfers         8.1       DSP Master Writes         8.2       DSP Master Reads         8.2.1       Master Read Completion         8.3       DSP as System Host         8.3.1       Generating IDSEL                                                                                                                                       | 28<br>29<br>31<br>31       |

| 9 | Reset9.1PCI Reset of DSP9.2FIFO Resets9.3PCI Configuration Register Reset9.4PCI Behavior During DSP Reset                                                                                                                                                                                                                                          | 33<br>33<br>33             |

| 10 | Interrupts and Status Reporting3410.1Host Interrupt to the DSP3410.2DSP to Host Interrupt34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11 | Boot Configuration for PCI Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 12 | EEPROM Interface3612.1PCI Autoinitialization from EEPROM3712.2EEPROM Memory Map3812.3EEPROM Checksum3912.4DSP EEPROM Interface39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 13 | Error Handling4113.1PCI Parity Error Handling4113.2PCI System Error Handling4213.3PCI Master Abort Protocol4213.4PCI Target Abort Protocol42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 14 | Power Management (C62x DSP only)4314.1PCI Power Management4314.2DSP Power Management Strategy4614.3DSP Resets4714.4DSP Support for Power Management4814.4.1Power Management Control/Status Register (PMCSR) Bits4814.4.23.3 Vaux Presence Detect Status Bit (AUXDETECT)4914.4.3PCI Port Response to PWR_WKP and PME Generation4914.4.4DSP Interrupt Indicating that PWRSTATE has Changed50                                                                                                                                                                                                                                                                                |

| 15 | PCI Registers5015.1Configuration Registers5015.1.1Vendor Identification Register5315.1.2Device Identification Register5315.1.3PCI Command Register5315.1.4PCI Status Register5415.1.5Revision Identification Register5615.1.6Class Code Register5615.1.7Cache Line Size Register5615.1.8Latency Timer Register5715.1.9Header Type Register5815.1.10Base 0 Address Register5815.1.11Base 1 Address Register5915.1.2Base 2 Address Register5915.1.3Subsystem Identification Register6015.1.4Subsystem Vendor Identification Register6015.1.4Subsystem Vendor Identification Register6015.1.4Subsystem Vendor Identification Register6015.1.5Capabilities Pointer Register61 |

|          | 15.1.16 | Interrupt Line Register                                       | 61  |

|----------|---------|---------------------------------------------------------------|-----|

|          |         | Interrupt Pin Register                                        |     |

|          |         | Min_Grant Register                                            |     |

|          |         | Max_Latency Register                                          |     |

|          |         | Capability Identification Register                            |     |

|          |         | Next Item Pointer Register                                    |     |

|          |         | Power Management Capabilities Register (PMC)                  |     |

|          |         | Power Management Control/Status Register (PMCSR)              |     |

|          |         | Power Data Register (PWRDATA)                                 |     |

| 15.2     |         | isters                                                        |     |

|          |         | Host Status Register (HSR)                                    |     |

|          |         | Host-to-DSP Control Register (HDCR)                           |     |

|          |         | DSP Page Register (DSPP)                                      |     |

| 15.3     |         | /-Mapped Registers                                            |     |

|          |         | DSP Reset Source/Status Register (RSTSRC)                     |     |

|          |         | Power Management DSP Control/Status Register                  |     |

|          |         | (PMDCSR) (Č62x DSP only)                                      |     |

|          |         | PCI Interrupt Source Register (PCIIS)                         |     |

|          |         | PCI Interrupt Enable Register (PCIIEN)                        |     |

|          |         | DSP Master Address Register (DSPMA)                           |     |

|          |         | PCI Master Address Register (PCIMA)                           |     |

|          |         | PCI Master Control Register (PCIMC)                           |     |

|          |         | Current DSP Address Register (CDSPA)                          |     |

|          |         | Current PCI Address Register (CPCIA)                          |     |

|          | 15.3.10 | Current Byte Count Register (CCNT)                            | 93  |

|          | 15.3.11 | EEPROM Address Register (EEADD)                               | 94  |

|          | 15.3.12 | EEPROM Data Register (EEDAT)                                  | 95  |

|          | 15.3.13 | EEPROM Control Register (EECTL)                               | 96  |

|          |         | PCI Transfer Halt Register (HALT) (C62x DSP only)             |     |

|          | 15.3.15 | PCI Transfer Request Control Register (TRCTL) (C64x DSP only) | 99  |

| Devision | Listers |                                                               | 104 |

| Revision | nistory | ······································                        | 101 |

# Figures

| TMS320C62x DSP Block Diagram                          | 15                           |

|-------------------------------------------------------|------------------------------|

| TMS320C64x DSP Block Diagram                          | 16                           |

| PCI Port Block Diagram                                | 19                           |

| PCI Base Slave Address Generation (Prefetchable)      | 20                           |

| PCI Base 1 Slave Address Generation (Nonprefetchable) | 20                           |

| PCI Port Power Management State Transition Diagram    | 45                           |

| Vendor Identification Register                        | 53                           |

| Device Identification Register                        | 53                           |

| PCI Command Register                                  | 54                           |

| PCI Status Register                                   | 55                           |

| Revision Identification Register                      | 56                           |

| Class Code Register                                   | 56                           |

| Cache Line Size Register                              | 57                           |

| Latency Timer Register                                | 57                           |

| Header Type Register                                  | 58                           |

| Base 0 Address Register                               | 58                           |

| Base 1 Address Register                               | 59                           |

| Base 2 Address Register                               | 59                           |

| Subsystem Identification Register                     | 60                           |

| Subsystem Vendor Identification Register              | 60                           |

| Capabilities Pointer Register                         | 61                           |

| Interrupt Line Register                               | 61                           |

| Interrupt Pin Register                                | 62                           |

| Min_Grant Register                                    | 62                           |

| Max_Latency Register                                  | 63                           |

| Capability Identification Register                    | 63                           |

| Next Item Pointer Register                            | 64                           |

| Power Management Capabilities Register (PMC)          | 65                           |

| Power Management Control/Status Register (PMCSR)      | 66                           |

| Power Data Register (PWRDATA)                         | 69                           |

| Host Status Register (HSR)                            | 71                           |

| Host-to-DSP Control Register (HDCR)                   | 73                           |

| DSP Page Register (DSPP)                              | 74                           |

| DSP Reset Source/Status Register (RSTSRC)             |                              |

| Power Management DSP Control/Status Register (PMDCSR) |                              |

| PCI Interrupt Source Register (PCIIS)                 |                              |

|                                                       | TMS320C64x DSP Block Diagram |

| 37 | PCI Interrupt Enable Register (PCIIEN)        | 85 |

|----|-----------------------------------------------|----|

| 38 | DSP Master Address Register (DSPMA)           | 88 |

| 39 | PCI Master Address Register (PCIMA)           | 89 |

| 40 | PCI Master Control Register (PCIMC)           | 90 |

| 41 | Current DSP Address (CDSPA)                   | 92 |

| 42 | Current PCI Address Register (CPCIA)          | 92 |

| 43 | Current Byte Count Register (CCNT)            | 93 |

| 44 | EEPROM Address Register (EEADD)               | 94 |

| 45 | EEPROM Data Register (EEDAT)                  | 95 |

| 46 | EEPROM Control Register (EECTL)               | 96 |

| 47 | PCI Transfer Halt Register (HALT)             | 98 |

| 48 | PCI Transfer Request Control Register (TRCTL) | 99 |

|    |                                               |    |

# **Tables**

| 1  | Differences Between the C62x and C64x PCI                           | 16 |

|----|---------------------------------------------------------------------|----|

| 2  | EEPROM Serial Interface Pins                                        | 36 |

| 3  | TMS320C62x DSP EEPROM Sizes Supported                               | 36 |

| 4  | EEPROM Autoinitialization (EEAI)                                    | 37 |

| 5  | EEPROM Memory Map                                                   |    |

| 6  | EEPROM Command Summary                                              | 40 |

| 7  | PCI Configuration Registers                                         | 52 |

| 8  | Vendor Identification Register Field Descriptions                   | 53 |

| 9  | Device Identification Register Field Descriptions                   | 53 |

| 10 | PCI Command Register Field Descriptions                             | 54 |

| 11 | PCI Status Register Field Descriptions                              | 55 |

| 12 | Revision Identification Register Field Descriptions                 | 56 |

| 13 | Class Code Register Field Descriptions                              | 56 |

| 14 | Cache Line Size Register Field Descriptions                         | 57 |

| 15 | Latency Timer Register Field Descriptions                           | 57 |

| 16 | Header Type Register Field Descriptions                             | 58 |

| 17 | Base 0 Address Register Field Descriptions                          | 58 |

| 18 | Base 1 Address Register Field Descriptions                          | 59 |

| 19 | Base 2 Address Register Field Descriptions                          | 60 |

| 20 | Subsystem Identification Register Field Descriptions                | 60 |

| 21 | Subsystem Vendor Identification Register Field Descriptions         | 60 |

| 22 | Capabilities Pointer Register Field Descriptions                    | 61 |

| 23 | Interrupt Line Register Field Descriptions                          | 61 |

| 24 | Interrupt Pin Register Field Descriptions                           | 62 |

| 25 | Min_Grant Register Field Descriptions                               | 62 |

| 26 | Max_Latency Register Field Descriptions                             | 63 |

| 27 | Capability Identification Register Field Descriptions               | 63 |

| 28 | Next Item Pointer Register Field Descriptions                       | 64 |

| 29 | Power Management Capabilities Register (PMC) Field Descriptions     | 65 |

| 30 | Power Management Control/Status Register (PMCSR) Field Descriptions | 66 |

| 31 | Power Data Register (PWRDATA) Field Descriptions                    | 69 |

| 32 | PCI I/O Registers                                                   | 70 |

| 33 | PCI I/O Registers Accessed via I/O Space (Base 2 Memory)            | 70 |

| 34 | Host Status Register (HSR) Field Descriptions                       |    |

| 35 | Host-to-DSP Control Register (HDCR) Field Descriptions              |    |

| 36 | DSP Page Register (DSPP) Field Descriptions                         | 74 |

| 37 | PCI Memory-Mapped Registers                                              | 75 |

|----|--------------------------------------------------------------------------|----|

| 38 | DSP Reset Source/Status Register (RSTSRC) Field Descriptions             | 76 |

| 39 | Power Management DSP Control/Status Register (PMDCSR) Field Descriptions | 79 |

| 40 | PCI Interrupt Source Register (PCIIS) Field Descriptions                 | 82 |

| 41 | PCI Interrupt Enable Register (PCIIEN) Field Descriptions                | 85 |

| 42 | DSP Master Address Register (DSPMA) Field Descriptions                   | 88 |

| 43 | PCI Master Address Register (PCIMA) Field Descriptions                   | 89 |

| 44 | PCI Master Control Register (PCIMC) Field Descriptions                   | 91 |

| 45 | Current DSP Address (CDSPA) Field Descriptions                           | 92 |

| 46 | Current PCI Address Register (CPCIA) Field Descriptions                  | 92 |

| 47 | Current Byte Count Register (CCNT) Field Descriptions                    | 93 |

| 48 | EEPROM Address Register (EEADD) Field Descriptions                       | 94 |

| 49 | EEPROM Data Register (EEDAT) Field Descriptions                          | 95 |

| 50 | EEPROM Control Register (EECTL) Field Descriptions                       | 96 |

| 51 | PCI Transfer Halt Register (HALT) Field Descriptions                     | 98 |

| 52 | PCI Transfer Request Control Register (TRCTL) Field Descriptions         | 99 |

| 53 | Document Revision History 1                                              | 01 |

|    |                                                                          |    |

# **Peripheral Component Interconnect (PCI)**

This manual describes the peripheral component interconnect (PCI) port in the digital signal processors (DSPs) of the TMS320C6000<sup>™</sup> DSP family. Also refer to the PCI Specification revision 2.2 for details on PCI interface.

#### 1 Overview

The PCI port supports the following PCI features:

- Conforms to PCI specification revision 2.2

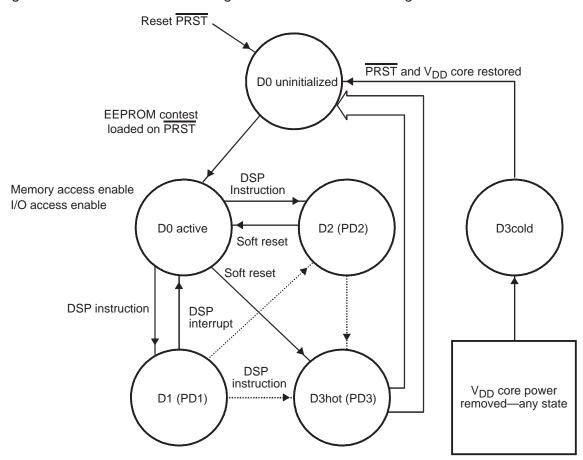

- Conforms to power management interface specification revision1.1 (C6205 DSP only)

- Meets requirements of PC99

- PCI master/slave interface

- 32-bit address/data bus

- Single function device

- Medium address decode

- PCI access to all on-chip RAM, peripherals, and external memory via external memory interface (EMIF)

- Supports memory read, memory read multiple, memory read line, memory write commands, I/O read, I/O write, CFG read, and CFG write.

- Unlimited slave-access burst lengths

- Master transfers of up to 64K bytes

- Single-word transfers for I/O read/writes

- Single-word transfers for configuration register access

- Many configuration register contents (subsystem ID/subsystem vendor ID, etc.) initialized from an external serial EEPROM at PCI reset.

- Supports 4-wire serial EEPROM interface

- EEPROM interface used directly by PCI port without DSP intervention on PCI reset. DSP software control of EEPROM after PCI reset.

SPRU581C

- PCI interrupt request under DSP program control

- DSP interrupt via PCI I/O cycle

- DSP power control via software (C6205 DSP only)

- Peripheral power control via software (C6205 DSP only)

- Software-controlled assertion of PME from D0, D1, D2, D3<sub>hot</sub> (C6205 DSP only)

- Hardware-controlled assertion of PME on power wakeup active from D3<sub>cold</sub>. Optional hardware-controlled assertion of PME from D0, D1, D2, D3<sub>hot</sub>. (C6205 DSP only)

- Supports D0, D1, D2, D3<sub>hot</sub>, D3<sub>cold</sub> power management modes (C6205 DSP only)

- Implements PCI power management control status register "sticky" bits from logic powered by 3.3V<sub>aux</sub> (C6205 DSP only)

- Four FIFOs for efficient data transfer (master write, master read, slave write, slave read)

- □ Independent master/slave operation

- Independent slave read/slave write operation

- Three PCI base address registers (prefetchable memory, nonprefetchable memory, I/O)

- Disconnect with retry on memory read line, memory read multiple to prefetchable memory

- No wait states inserted by DSP on PCI master or slave transactions

The PCI port does not support:

- PCI special cycles

- PCI interrupt acknowledge cycles

- PCI lock

- PCI memory caching

- □ 64-bit bus operation

- Master address/data stepping

- Master combining (for write posting)

- Collapsing

- Merging

- Cache line-wrap accesses

- Reserved accesses

- Message-signaling interrupts

- Vital product data

- Compact PCI hot swap

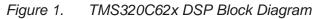

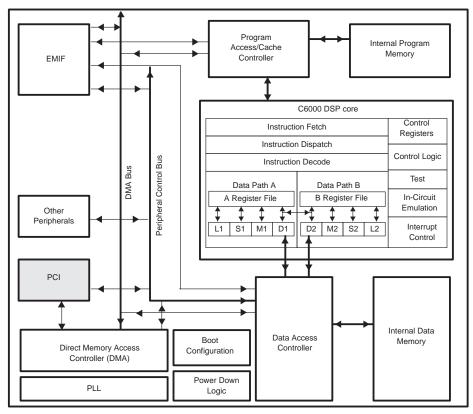

The PCI port supports connection of the DSP to a PCI host via the integrated PCI master/slave bus interface. For C62x devices, the PCI port interfaces to the DSP via the auxiliary channel of the DMA controller (Figure 1). For C64x devices, the PCI port interfaces to the DSP via the enhanced DMA (EDMA) controller (Figure 2). This architecture allows for both PCI master and slave transactions, while keeping the DMA/EDMA channel resources available for other applications.

The C62x PCI port provides the auxiliary DMA with a source/destination address in the DSP memory. Address decode is performed by the DMA to select the appropriate interface (data memory, program memory, register I/O, or external memory). The auxiliary channel of the DMA controller should be programmed for the highest priority in order to achieve the maximum throughput on the PCI interface.

The C64x PCI port uses the EDMA internal address generation hardware to perform address decode instead.

Table 1 lists the differences between the C62x and C64x PCI ports.

### Figure 2. TMS320C64x DSP Block Diagram

Table 1. Differences Between the C62x and C64x PCI

| Features                    | C62x PCI        | C64x PCI                                  |

|-----------------------------|-----------------|-------------------------------------------|

| Internal transfer           | Auxiliary DMA   | EDMA internal address generation hardware |

| PMDCSR register             | Supported       | Does not apply                            |

| HALT register               | Supported       | Does not apply                            |

| TRCTL register              | Does not apply  | Supported                                 |

| Supported EEPROM size, bits | 1K, 2K, 4K, 16K | 4K                                        |

| Power management support    | Yes             | No                                        |

| FIFO depth                  | 8 words         | 16 words                                  |

$\dagger P = CPU$  clock period

#### 2 PCI Architecture

The PCI port supports four types of PCI data transactions:

- Slave Writes: External PCI master writes to DSP slave

- Slave Reads: External PCI master reads from DSP slave

- Master Writes: DSP master writes to external slave

- Master Reads: DSP master reads from external slave

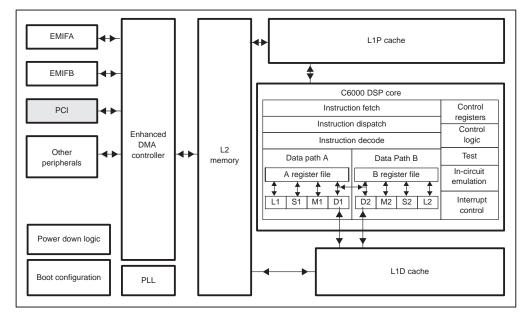

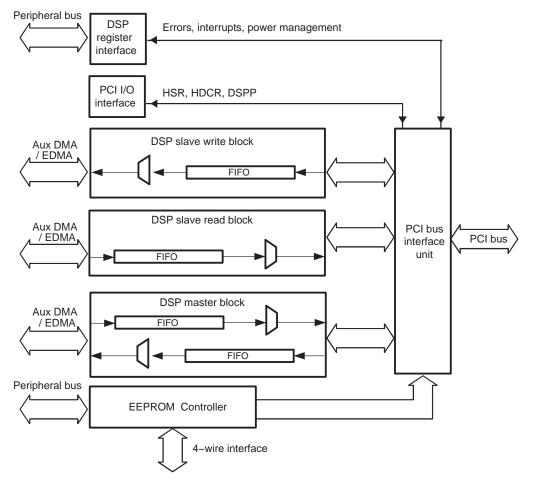

The PCI port block diagram, shown in Figure 3 (page 19), consists of the following primary blocks:

PCI Bus Interface Unit (PBIN)

The PCI bus protocol is implemented in the PCI bus interface unit (PBIN). To maximize PCI bus bandwidth, the PCI interface does not insert wait states for slave or master burst transactions. If the corresponding FIFO goes full or empty, the PCI interface disconnects the current transfer. The PCI bus interface unit inserts the following delays on the PCI bus:

- Slave Writes:

- Zero wait state initial transfer

- Zero wait state subsequent transfers

- Disconnect if FIFO is full, or previous frame is not complete

- Slave Reads:

- Prefetchable: Initial access disconnected with retry

- Up to 16 wait states inserted for single-word transfers

- Zero wait state initial transfer (prefetchable retry)

- Zero wait state subsequent transfers (prefetchable retry)

- Disconnect if FIFO is empty, or other slave read frame is in progress

- Master Writes:

- Zero wait state initial transfer

- Zero wait state subsequent transfers

- Master Reads:

- Zero wait state initial transfer

- Zero wait state subsequent transfers

- EEPROM Controller

The EEPROM controller interfaces to the 4-wire serial EEPROM interface. On PCI reset, the EEPROM controller reads the EEPROM and provides the PCI bus interface unit with the configuration data. During normal operation, the EEPROM can be accessed by the DSP via the memorymapped registers. DSP Slave Write Block

The DSP slave write block contains a multiplexer and a FIFO to transfer data (written by the external PCI master) from the PCI bus interface unit to the DSP.

DSP Slave Read Block

The DSP slave read block contains a multiplexer and a FIFO to transfer data from the DSP to the PCI bus interface unit. The external PCI master is the requester of this data.

DSP Master Block

The DSP master block is divided into the read and write portions. The device cannot perform both read and write operations simultaneously.

- The write portion of the DSP master block contains a data multiplexer and a FIFO for DSP master writes. It transfers data from the DSP (master) to an external slave via the PCI bus interface unit.

- The read portion of the DSP master block contains a data multiplexer and a FIFO for DSP master reads. It transfers data from the PCI bus interface unit to the DSP (master).

- PCI I/O Interface

The input/output (I/O) interface contains the PCI I/O-mapped registers. These registers control the DMA/EDMA page for slave transactions, indicate the host status, and can interrupt or reset the DSP core.

DSP Register Interface

The DSP register interface contains DSP memory-mapped registers for the control of the master interface, PCI host interrupts, and power management.

#### 3 Memory Map

The PCI port has full visibility into the DSP memory map through three base address registers:

- □ Base 0: 4M-byte prefetchable maps to all of DSP memory with the DSP page register (DSPP). Prefetch reads have all bytes valid.

- Base 1:8M-byte nonprefetchable maps to DSP memory-mapped registers. Nonprefetch supports byte enables.

- Base 2: 16-byte I/O contains I/O registers for the PCI host

These three registers belong to the group of PCI configuration registers. PCI host accesses to DSP (prefetchable) memory are mapped to a 4M-byte window in the PCI memory space. The PCI port contains a PCI I/O register, the DSP page register (DSPP), that specifies the address mapping from the PCI address to the DSP address. This address mapping is used when the DSP is a slave on the PCI local bus.

The DSPP, described in section 15.2.3, is used to locate the 4M-byte window within the DSP memory map. Bits 21–0 of the PCI address are concatenated with bits 9–0 of DSPP to form the DSP address for PCI slave access to the DSP as shown in Figure 4.

#### Figure 4. PCI Base Slave Address Generation (Prefetchable)

| 31 22                    | 21                              | 0 |

|--------------------------|---------------------------------|---|

| DSPP register (bits 9–0) | Current PCI address (bits 21–0) |   |

The PCI base 1 register on the DSP is configured for an 8M-byte nonprefetchable region. This memory is mapped into the DSP at a fixed location (0180 0000h–0200 0000h). Bits 22–0 of the PCI address are concatenated with a fixed offset to map the base 1 access into the memory-mapped registers as shown in Figure 5.

#### Figure 5. PCI Base 1 Slave Address Generation (Nonprefetchable)

| 31 | 23          | 22                              | 0 |

|----|-------------|---------------------------------|---|

|    | 0000 0001 1 | Current PCI address (bits 22–0) |   |

Base address register 2 is configured for a 16-byte I/O region for the PCI host to access the PCI I/O registers. See section 15.2.

20 Peripheral Component Interconnect (PCI)

The PCI bus interface provides two access methods for PCI host access to DSP memory. The 4M-byte base 0 region is used for prefetchable data, and the 8M-byte base 1 region is used for nonprefetchable (register) access. All transfers to the nonprefetchable region transfer single words and then disconnect.

Data access to the prefetchable region may be transferred in bursts limited mainly by the host system setup (PCI bridge latency timer, burst length count). Prior to transferring data, the PCI host must first write DSPP to locate the 4M-byte window within the DSP memory map.

PCI master transactions issued by the DSP will attempt to use bursts. Through disconnects, however, the external slave can force the DSP master to perform single-word transfers.

Internal to the DSP, all data transfers are handled by the auxiliary channel of the DMA controller (C62x devices) or the EDMA internal address generation hardware (C64x devices).

**Note:** You must ensure that no PCI transactions cross the port boundaries of the DMA/EDMA controller. A port boundary is the address boundary between external memory and internal memory, between external memory and the peripheral address space, or between internal memory and the peripheral address space.

#### 4 Byte Addressing

The PCI interface is byte-addressable. The PCI interface can read and write 8-bit bytes, 16-bit halfwords, 24-bit words, and 32-bit words. Words are aligned on an even four-byte boundary. Words always start at a byte address where the two LSBs are 00. Halfwords always start at a byte address where the last LSB is 0.

PCI slave transactions to non-prefetchable spaces are fully byte-addressable. PCI slave transactions to prefetchable spaces are done with no smaller than word granularity.

#### 5 PCI Address Decode

The PCI port supports "medium" address decode of the PCI address for memory and I/O cycles. The PDEVSEL signal is asserted two PCI clock periods after PFRAME is sampled and asserted.

SPRU581C

## 6 Special Considerations for PCI Memory Service

#### 6.1 Prefetchable Reads (C62x DSP only)

When the PCI executes a read from the DSP memory space, it performs burst prefetches of four words. This results in the DMA auxiliary channel reading three higher-word addresses that you may not have explicitly requested. This occurs only when he PCI port performs prefetchable reads on behalf of an external PCI master.

These prefetchable reads can generate the following undesired operations:

- 1) Accesses to undesired CE spaces:

- When reading the top three words of EMIF CE0, the resulting prefetches can cause an inadvertent access to CE1 that may cause an undesired read to a device or a stall if the inadvertent access is to an asynchronous memory space with ARDY left floating or pulled inactive (not-ready).

- The above example also applies to CE2 with the resulting prefetches possibly causing an inadvertent access to CE3.

Associated design tip: If not using ARDY, always pull to the ready state to avoid stalls. If you always want to detect bad software setups, always pull to the not-ready state to detect system stalls.

- 2) Unintended port crossings or illegal accesses to a reserved location:

- When reading the top three words of EMIF CE1, the access can cross into either program memory (PMEM) block 0 when in map 0 or to the internal peripheral bus (PBus) region storing EMIF control registers when in map 1. This is an illegal port crossing.

- When reading the top three words of EMIF CE3, the access can cross into reserved address space. This is an illegal access.

- When reading the top three words of PMEM block 0 the access can cross into PMEM block 1. This is an illegal port crossing.

- When reading the top three words of PMEM block 1, the access can cross into reserved address space. This is an illegal access.

- When reading the top three words of data memory (DMEM) block 1, the access can cross into reserved address space. This is an illegal access.

- When reading anywhere in the PBus space, you may prefetch ahead to three undesired control registers. This can cause an illegal access when accessing a reserved register address. If the register access has side effects (like reading the McBSP DRR, clearing RRDY), then you may inadvertently cause these side effects.

Note: A restriction does not exist when crossing between DMEM block 0 and block 1 because they both use the same DMA port.

Associated design tips:

- When reading internal peripheral registers:

- For reads from an external master, use fixed-mode addressing. As a broader statement, it is good practice to use fixed mode also when writing to peripheral registers as sometimes there are gaps between them.

- On PCI, always use non-prefetchable reads of peripheral registers.

- When reading the top three locations of an EMIF CEx, internal program block or DMEM block 1, use fixed-mode addressing. Note this procedure does not have to be followed when accessing the top three words of DMEM block 0, this is because DMEM block 0 and block 1 are in the same DMA port.

## 6.2 PCI Transfers To and From Program Memory (C62x DSP only)

The CPU has priority over the DMA (and auxiliary DMA) for access to program memory. Since the CPU can access the program memory on every CPU clock, it can possibly lock out the DMA from accessing the program memory.

If the PCI port is requesting program memory transfers via the auxiliary channel, all the other four DMA channels are halted. Thus, no DMA channel activity occurs during the PCI port requests, even if a DMA channel is accessing a different memory (EMIF/peripheral/data memory). If the CPU has higher priority, all DMA activity can be blocked while the CPU is executing a tightly coded routine from program memory.

The PCI transfer halt register (HALT) prevents the PCI port from performing master/slave auxiliary channel requests. If the HALT bit is set, all auxiliary transfers are prevented. Any current PCI master transaction will complete its DMA cycle. The PCI transaction will not commence until the HALT bit is deasserted. This prevents DMA lockup when a PCI transaction is in progress and the DSP is executing a packed section of code. The other DMA channels are free to access memory when the PCI master is halted.

The HALT register does not apply to C64x devices, because the DMA lockup condition does not apply. The C64x EDMA uses a priority queue implementation. Only EDMA transfers placed in the same priority queue as the PCI transfer will be stalled in the above condition. See *TMS320C6000 DSP Enhanced DMA* (*EDMA*) Controller Reference Guide (SPRU234), for details on priority queues.

## 6.3 PCI EDMA Usage Control (C64x DSP only)

The PCI port uses the EDMA hardware for memory requests. Use of this shared resource is governed by the PCI transfer request control register (TRCTL), and is user-configurable, provided care is taken when changing the values in the register.

To safely change the PALLOC or PRI bits in TRCTL, the TRSTALL bit needs to be used to ensure a proper transition. The following procedure must be followed to change the PALLOC or PRI bits:

- Set the TRSTALL bit to 1 to stop the PCI from submitting TR requests on the current PRI level. In the same write, the desired new PALLOC and PRI bits may be specified.

- Clear all EDMA event enables (EER) corresponding to both old and new PRI levels to stop the EDMA from submitting TR requests on both PRI levels. Do not manually submit additional events via the EDMA.

- 3) Do not submit new QDMA requests on either old or new PRI level.

- 4) Stop L2 cache misses on either old or new PRI level. This can be done by forcing program execution or data accesses in internal memory. Another way is to have the CPU executing a tight loop that does not cause additional cache misses.

- 5) Poll the appropriate PQ bits in the priority queue status register (PQSR) of the EDMA until both queues are empty (see *TMS320C6000 DSP Enhanced DMA (EDMA) Controller Reference Guide*, SPRU234).

- 6) Clear the TRSTALL bit to 0 to allow the PCI to continue normal operation.

Requestors are halted on the old PCI PRI level so that memory ordering can be preserved. In this case, all pending requests corresponding to the old PRI level must be allowed to complete before PCI is released from stall state.

Requestors are halted on the new PRI level to ensure that at no time can the sum of all requestor allocations exceed the queue length. By halting all requestors at a given level, you can be free to modify the queue allocation counters of each requestor.

### 7 Slave Transfers

#### 7.1 DSP Slave Writes

The slave write FIFO in the DSP slave write block (Figure 3, page 19) is used to efficiently handle PCI host writes to the DSP slave. The address for a DSP slave write is derived from the PCI address concatenated with the fixed offset in DSPP, as described in section 3. No wait states are inserted by the slave PCI port. DSP slave writes execute with zero wait states on all data phases for both single and burst accesses. The PCI interface supports unlimited length memory burst transfers.

Slave write access to DSP is only disconnected when the FIFO is full, or when the FIFO is not empty from a previous PCI slave write frame. Slave reads and master read/write transactions have no effect on slave write PCI transactions.

Internally, the auxiliary DMA or EDMA internal address generation hardware service the slave write FIFO when:

FIFO has at least 4 words of data, or

PCI transaction has terminated (PFRAME deasserted)

The DSP slave write address is autoincremented internally. DSP memory writes continue until there is no longer any valid data in the FIFO. This applies to both single and burst PCI transactions. For single access transactions, the internal transfer request is made after the PCI transaction has terminated.

#### 7.2 DSP Slave Reads

Similar to slave writes, the slave read FIFO in the DSP slave read block (Figure 3, page 19) is used to efficiently handle PCI host reads from the DSP slave. The PCI slave read interface supports unlimited length memory burst transfers.

The PCI port uses the cache line size and PCI command to determine the number of bytes transferred for a slave read. The type of PCI access is indicated by the PCI command/byte enable signals (PCBEx) during the address phase. The following slave read commands are supported:

- Memory read

- Memory read multiple

- Memory read line

All of the above PCI slave reads can be prefetchable and nonprefetchable.

SPRU581C

Peripheral Component Interconnect (PCI) 25

#### 7.2.1 Nonprefetchable Slave Reads (BAR 1)

For nonprefetchable slave reads, the PCI port inserts wait cycles until the requested word, halfword, or byte is written to the FIFO. The data is then transferred on the PCI bus, and the cycle is terminated regardless if the command was a memory read, a memory read multiple, or a memory read line.

#### 7.2.2 Prefetchable Slave Reads (BAR 0)

For prefetchable slave reads, the PCI port inserts wait cycles until the requested word is ready. The PCI port adheres to the 16-clock rule, if data is not ready in 16 PCI clocks, the memory read is disconnected with retry. Memory read commands always produce one (1) word of data. Memory Read Line and Memory Read Multiple should be used for burst accesses.

#### 7.2.3 Prefetchable Slave Read Multiple and Prefetchable Slave Read Line (BAR 0)

These requests are initially terminated on the PCI bus with a disconnect with retry. Subsequently, the auxiliary DMA or EDMA internal address generation hardware services the PCI port by transferring read data to the FIFO. The PCI slave transfer occurs when the original master reattempts the initial transfer. Nonrelated slave requests are terminated with a disconnect.

For memory read line commands, the number of bytes transferred to the slave read FIFO is based on the cache-line size register. For memory read multiple commands, the DSP slave read continuously fills the FIFO with data until the PCI master terminates the transaction (PFRAME deasserted), at which point the last PCI valid data sample is transferred and the FIFO is flushed.

The auxiliary DMA or EDMA internal address generation hardware bursts until the slave read FIFO is full. The DSP slave address is autoincremented internally.

Memory read line and memory read multiple commands transfer data with zero wait states inserted by the PCI port, when the requestor retries the command and the FIFO has data. The FIFO request is also terminated, if the PCI transaction is disconnected prematurely by the master.

#### 7.3 PCI Target-Initiated Termination

The DSP issues target terminations under these conditions:

- Data transfer with disconnect, if the master issues a burst memory access with an addressing mode that is not supported.

- □ Retry with data transfer, if the master attempts a burst access to the configuration space (see section 15.1).

- Retry with data transfer, if the master attempts a burst access to the I/O space (see section 15.2).

- Disconnect for slave memory or I/O writes and a transaction is waiting in the internal slave read FIFO.

- Disconnect for slave memory reads, if the PCI address value does not match the address in the internal read prefetch buffer.

- Once a prefetch has been started, retry for all other memory and I/O reads until the original posted transaction is repeated by the PCI bus master and the prefetched data is transferred.

The PCI interface meets all 16-clock and 8-clock rules for data transfers within single access and burst accesses.

### 8 Master Transfers

Master transfers are initiated under DSP control. The following PCI memory-mapped peripheral registers are used to configure a DSP master transfer:

- DSP master address register (DSPMA)

- PCI master address register (PCIMA)

- PCI master control register (PCIMC)

The following PCI memory-mapped peripheral registers indicate the status of the current master transfer:

- Current DSP address register (CDSPA)

- Current PCI address register (CPCIA)

- Current byte count register (CCNT)

For C62x devices, the PCI transfer halt register (HALT) allows the DSP to terminate internal transfer requests to the auxiliary DMA channel.

SPRU581C

#### 8.1 DSP Master Writes

The master write FIFO in the DSP master block (Figure 3, page 19) is used to efficiently handle DSP master writes to an external slave. The master write interface supports burst lengths of up to 64K - 1 bytes.

Master writes are initiated under DSP control via the DSP master address register (DSPMA), the PCI master address register (PCIMA), and the PCI master control register (PCIMC).

For DSP master writes, the ADDRMA bits in DSPMA contain the word-aligned source (DSP) address. For the C6205 DSP only, if the AINC bit in DSPMA is cleared, the source address is autoincremented by 4 bytes after each internal data transfer. On the C64x, all transfers autoincrement. Note that for both C6205 and C64x, DSPMA will never autoincrement past a 16MB boundary. Instead, it will wrap around within the 16MB block. PCIMA contains the word-aligned destination (PCI) address. An internal register keeps track of the PCI master address.

A master write is initiated by enabling the START bits in PCIMC. The auxiliary DMA or EDMA transfers data from the source address (pointed to by DSPMA) to the master write FIFO. It either fills up the FIFO or transfers only the number of words desired if that number is less than the FIFO length. Subsequent internal data transfers are performed when the FIFO has space for 4 or more words of data. Internal data transfer continues until the FIFO is full or until the transfer is completed.

Once the FIFO has valid data, a PCI bus request is made and data is transferred from the FIFO to the PCI. DSP master writes execute with zero wait states on all data phases of both single and burst accesses. The PCI command/byte enable signals (PCBEx) indicate the master write bytes on the PCI interface.

Internal data transfers stop once all master write data has been transferred from the DSP source to the master write FIFO. For C62x devices, internal data transfers and the current PCI bus cycle can also be terminated by asserting the HALT bit in the HALT register. The PCI bus interface monitors the PCI interface for disconnects, retries, and target-aborts. The PCI port complies with PCI Specification revision 2.2 and retries the exact same cycle during retries.

If the cycle is terminated with a master abort or a target abort, the current transfer is terminated both internally and externally on the PCI bus. The master write FIFO is flushed and either the master abort (PCIMASTER) or target abort (PCITARGET) bit is set in the PCI interrupt source register (PCIIS). These error conditions can generate a CPU interrupt, if the corresponding bits are set in the PCI interrupt enable register (PCIIEN).

If the PCI latency timer (specified in the PCI configuration register space) times out, the PCI master gives up the bus. The master requests the bus later and completes the necessary transfers.

The progress of the transfer can be polled by reading the PCI master control register (PCIMC). The START bits go to 000b, when the transfer is complete on both the DSP and PCI side. Alternatively, the master can be programmed to generate an interrupt upon completion of a frame transfer by setting the MASTEROK bit in PCIIEN.

#### 8.2 DSP Master Reads

The master read FIFO in the DSP master block (Figure 3, page 19) is used to efficiently handle DSP master reads from an external slave. The master read interface supports burst lengths of up to 64K - 1 bytes.

Master reads are initiated under DSP control via the DSP master address register (DSPMA), the PCI master address register (PCIMA), and the PCI master control register (PCIMC).

For DSP master reads, PCIMA contains the external PCI slave source address. The ADDRMA bits in DSPMA contain the word-aligned destination (DSP) address. For the C6205 DSP only, if the AINC bit in DSPMA is cleared, the destination address is autoincremented by 4 bytes after each internal data transfer. On the C64x, all transfers autoincrement. Note that for both C6205 and C64x, DSPMA will never autoincrement past a 16MB boundary. Instead, it will wrap around within the 16MB block.

A master memory read is initiated by enabling the START bits in PCIMC. The PCI port performs a PCI bus request. Once a PCI bus request is granted, a PCI bus cycle is initiated. The type of cycle initiated depends on the number of bytes to be transferred and the cache line size. The following master memory read commands are supported:

- Memory read

- Memory read multiple

- Memory read line

You can initiate two types of memory reads, based on the START bits in PCIMC. Prefetchable memory reads (START = 010b) use the memory read multiple and memory read line commands for transfers greater than one word. A memory read command is used for transfers of one word.

Nonprefetchable memory reads (START = 011b) always use a memory read command. A transfer size of N words is broken up into N one-word read cycles on the PCI bus. You should read from prefetchable memory whenever possible.

No wait states are inserted on the initial data phase or subsequent data phases of the PCI master read access. Read data is written to the master read FIFO. An internal auxiliary DMA or EDMA data transfer request occurs when the FIFO has at least 4 words of data, or when the PCI transaction has terminated. The auxiliary DMA channel or EDMA transfers data from the master read FIFO to the DSP destination address (ADDRMA bits in DSPMA). All master read transactions are word-aligned.

Auxiliary DMA or EDMA transfers continue until there are no longer any valid data in the FIFO. This applies to both single access and burst PCI transactions. For single access transactions, the internal data transfer occurs after the PCI transaction has terminated (PFRAME deasserted).

Internal data transfers stop once all master read data has been transferred from the master read FIFO to the DSP destination. For C62x devices, internal data transfers and the current PCI bus cycle can also be terminated by asserting the HALT bit in the HALT register. The PCI bus interface monitors the PCI interface for disconnects, retries, and target-aborts. The PCI port complies with PCI Specification revision 2.2 and retries the exact same cycle during retries.

If the cycle is terminated with a master abort or a target abort, the current transfer is terminated both internally and externally on the PCI bus. The master read FIFO is flushed and either the master abort (PCIMASTER) or target abort (PCITARGET) bit is set in PCI interrupt source register (PCIIS). These error conditions can generate a CPU interrupt, if the corresponding bits are set in the PCI interrupt enable register (PCIIEN).

If the PCI latency timer (specified in the PCI configuration register space) times out, the PCI master gives up the bus. The master requests the bus later and completes the necessary transfers.

The progress of the transfer can be polled by reading the PCI master control register (PCIMC). The start bits go to 000b when the transfer is complete on the PCI side. Alternatively, the master can be programmed to generate an interrupt upon completion of frame transfer by setting the MASTEROK bit in PCIIEN.

#### 8.2.1 Master Read Completion

When the start bits return to 000b, or the MASTEROK interrupt is generated, the current transaction is complete from the PCI point of view. However, in the case of reads, this means the data has been handed off to DMA or EDMA for actual memory service. Due to differing paths for PCI data versus interrupts or register reads, the CPU may receive notification before data has landed. You should be careful when doing master reads to ensure that the CPU reads the correct data from memory.

This is a more likely problem in EDMA systems, due to its longer latencies. A simple way to ensure data correctness is to preform a small dummy QDMA access on the same priority queue as the PCI. When this QDMA completes, you can be sure the PCI data has landed.

#### 8.3 DSP as System Host

The PCI port can perform master configuration cycles regardless of the master bit setting in the PCI configuration registers. Also, the internal slave and master can run concurrently, allowing the DSP to read and write its own configuration registers over the PCI bus. These capabilities allow the PCI port to act as a system host by configuring itself and the rest of the PCI bus. This is subject to the following limitations:

- DISELs must be under DSP control.

- ☐ There is just one PCI bus segment, that is, the DSP cannot generate type 1 configuration cycles.

- External logic to arbitrate the bus.

#### 8.3.1 Generating IDSEL

To properly configure the bus, the DSP must be able to assert the IDSEL line of each device at the appropriate time. The PCI interface does not directly provide for this; it must be accomplished by indirect means. The following sections provide two different procedures to generate IDSEL.

#### 8.3.1.1 Resistively Coupled IDSEL

Resistively coupling IDSEL is a common and easy method of generating IDSELs; however, you must be careful to adhere to PCI specification with this method. Using coupled IDSELs requires the host to step the address phase onto the bus to allow IDSEL sufficient time to propagate to the target device. The PCI interface does not do address stepping. The compact nature of most systems where the DSP is the host should allow for a functional coupling without address stepping. Regardless, it is your responsibility to ensure the IDSEL signal propagates through the resistive coupling in time to meet PCI's timing specification.

When using resistive coupling for IDSEL generation, the procedure to read or write a configuration word is as follows:

- 1) Set PCIMA:

- a) PCIMA[31–11] = one bit set to select appropriate device's IDSEL (important: only one bit should be set at a time)

- b) PCIMA[10-8] = device function to be addressed

- c) PCIMA[7–0] = 32-bit configuration word address (See PCI specification for type 0 configuration access details)

- 2) Set DSPMA to point to a local buffer (buffer contains source data for writes, space for data for reads)

- 3) Set PCIMC for 4 bytes, desired function

- 4) Poll for START==0 or wait for MASTEROK interrupt

#### 8.3.1.2 GPIO Generated IDSEL

An alternate and fully-compliant method of generating IDSEL is to attach the IDSEL lines to GPIO pins and control them directly. The procedure is only slightly different from above:

- 1) Set GPIO to enable one IDSEL only (important: only one IDSEL should be enabled at a time) You should read back new values written to GPIO pins to avoid race conditions.

- 2) Set PCIMA:

- a) PCIMA[11-8] = device function to be addressed

- b) PCIMA[7–0] = 32-bit configuration word address (See PCI specification for type 0 configuration access details)

- 3) Set DSPMA to point to a local buffer (buffer contains source data for writes, space for data for reads)

- 4) Set PCIMC for 4 bytes, desired function

- 5) Poll for START==0 or wait for MASTEROK interrupt

- 6) Set GPIO to turn off IDSEL

#### 9 Reset

### 9.1 PCI Reset of DSP

The PCI host can reset the DSP via the host-to-DSP control register (HDCR). Setting the WARMRESET bit in HDCR to 1 causes a DSP reset, which resets all of the internal CPU and peripheral logic. WARMRESET can wake the DSP from PD2 and PD3 power-down modes. WARMRESET does not relatch the boot configuration pins.

#### 9.2 FIFO Resets

The PCI FIFOs and control logic are held in reset when either the DSP is reset or the PCI pin PRST is asserted.

### 9.3 PCI Configuration Register Reset

The PCI configuration registers read from the EEPROM are initialized on the PCI bus ( $\overline{PRST}$ ) reset. Neither the DSP core reset nor the power on reset, affects them.

## 9.4 PCI Behavior During DSP Reset

If the device reset is asserted, the PCI port will disconnect all incoming transactions until the device is taken out of reset. The PCI port will not perform any master transactions while the device is in reset.

### 10 Interrupts and Status Reporting

The PCI port can generate the following CPU interrupts:

- PCI\_WAKEUP (C62x devices): this is dedicated to PCI power wake-up events.

- ADMA\_HLT (C62x devices): this interrupt is generated when the auxiliary DMA is halted (DMAHALTED).

- DSPINT: this interrupt is asserted and enabled in the PCI interrupt enable register (PCIIEN), when any of these events occurs: PWRMGMT, PCITRAGET, PCIMASTER, HOSTSW, PWRLH, PWRHL, MASTEROK, CFGDONE, CFGERR, EERDY, or PRST.

The PCI master/slave interface status/errors are shown in the PCI interrupt source register (PCIIS). All status/error conditions can generate a CPU interrupt, if they are enabled in the PCI interrupt enable register (PCIIEN). Status bits in PCIIS are still set, even if the interrupt is not enabled. If an enabled interrupt occurs, it sends a DSPINT interrupt to the DSP. Writing a 1 to the corresponding PCIIS bit(s) clears the interrupt. If an interrupt bit is still set, a new interrupt will then occur. Thus, upon a PCI interrupt, you should perform the following in the interrupt service routine:

- Read the PCIIS register

- Clear the appropriate PCIIS bits by writing a 1 to them

The PCI port can generate interrupts to both the CPU and the PCI host (via the PINTA pin). The following sections describe these two types of interrupts.

#### 10.1 Host Interrupt to the DSP

The PCI host can generate an interrupt to the DSP by writing the DSPINT bit in the PCI I/O host-to-DSP control register (HDCR). Writing this bit causes the HOSTSW interrupt, if it is enabled in the PCI interrupt enable register (PCIIEN).

#### **10.2 DSP to Host Interrupt**

The DSP can generate an interrupt to the PCI host via the PINTA pin. Interrupts to the host are generated only under DSP software control.

34 Peripheral Component Interconnect (PCI)

The interrupt is generated by writing a 1 to the INTREQ bit in the DSP reset source/status register (RSTSRC). This causes the PINTA pin to be asserted on the local PCI bus, if the INTAM bit in the host status register (HSR) is 0. The PINTA pin is negated by writing a 1 to the INTRST bit in RSTSRC. The interrupt must be cleared by writing 1 to INTRST before another interrupt can be requested via INTREQ.

#### 11 Boot Configuration for PCI Port

The following PCI port configurations, along with other device configurations, are determined at device reset via the boot configuration pins:

- EEPROM autoinitialization (EEAI) bits in EECTL: determines if PCI uses default values or read configure values from EEPROM.

- □ EEPROM size selection (EESZ) bits in EECTL (C62x only): determines EEPROM size.

For details on device and PCI boot configurations, refer to the device datasheet. The EEPROM interface is discussed in section 12.

The PCI port supports booting from the PCI bus. The CPU is stalled while the remainder of the device awakes from reset. During this period, the PCI host can initialize the DSP memory as necessary through the PCI. Once the PCI host is finished with all necessary initialization, it writes a 1 to the DSPINT bit in the host-to-DSP control register (HDCR) to release the DSP core from its stalled state. The DSP then begins execution from address 0h.

The sequence of events for PCI booting is:

- 1) PCI BOOTMODE is selected via configuration pins at reset. Refer to the device datasheet for details.

- The PCI interface autoinitializes the PCI configuration registers via EEPROM (if selected).

- 3) PCI host sets memory and I/O enable.

- 4) The PCI master writes the DSP page register (DSPP).

- 5) The PCI master transfers the data to DSP memory-mapped space, starting at address 0h.

- 6) The PCI master can also access data memory, peripheral registers, EMIF.

- The PCI master writes the DSPINT bit in HDCR with a 1 to release the DSP from reset.

- 8) DSP begins executing code from the program memory-mapped at 0h.

SPRU581C

#### 12 EEPROM Interface

The DSP supports the 4-wire serial EEPROM interface. The inter-integrated circuit ( $I^2C$ ) and SPI interfaces are not supported. The EEPROM interface consists of the pins listed in Table 2.

|  | Table 2. | EEPROM Serial Interface Pins |

|--|----------|------------------------------|

|--|----------|------------------------------|

| Pin     | Input/Output | Description               |

|---------|--------------|---------------------------|

| XSP_CLK | 0            | Serial EEPROM Clock       |

| XSP_CS  | 0            | Serial EEPROM Chip Select |

| XSP_DI† | Ι            | Serial EEPROM Data In     |

| XSP_DO  | 0            | Serial EEPROM Data Out    |

<sup>†</sup> The XSP\_DI pin should be pulled down.

The serial EEPROM clock is derived from the DSP peripheral clock. Normally, it is divided down by 2048 to drive the XSP\_CLK pin. The XSP\_CLK pin is only active during EEPROM access to minimize power.

For C62x devices, the state of the boot configuration pins, EESZ, at power-on reset determines if a serial EEPROM is present, and if so, what size. Table 3 summarizes the EEPROM sizes supported by the C62x devices. The C64x devices only support a 4K-bits EEPROM, and EESZ does not exist.

The EEPROM interface accesses the EEPROM as a 16-bit device only. The ORG pin of the EEPROM must be connected to  $V_{CC}$ .

#### Table 3. TMS320C62x DSP EEPROM Sizes Supported

| EEPROM Size Supported on C62x DSP(bits) |

|-----------------------------------------|

| No EEPROM present                       |

| 1К                                      |

| 2К                                      |

| 4К                                      |

| 16K                                     |

| Reserved                                |

|                                         |

Peripheral Component Interconnect (PCI)

# 12.1 PCI Autoinitialization from EEPROM

The DSP allows some of the PCI configuration registers to be loaded from an external serial EEPROM. The PCI port without DSP intervention performs the autoinitialization process.

The state of the boot configuration pins EEAI and EESZ (C62x device only) at device reset determine if autoinitialization is enabled. Table 4 shows how the EEAI pin selects autoinitialization at reset.

Table 4. EEPROM Autoinitialization (EEAI)

| EEAI Bit Autoinitialization |                         |

|-----------------------------|-------------------------|

| 0                           | Use default values      |

| 1                           | Read values from EEPROM |

Autoinitialization is enabled if:

- 1) Configuration pin EEAI = 1 (autoinitialization is enabled).

- 2) Configuration pins  $EESZ \neq 00b$  (indicates an EEPROM is present).

- 3) PCI operation is selected.

If any of these conditions are not met, default values are used for the PCI configuration registers and the EEPROM is not accessed. When all of these conditions are met, the contents from the EEPROM are loaded into some of the PCI configuration registers by the PCI interface (section 15.1). The size of the serial EEPROM is required to determine the serial protocol.

# 12.2 EEPROM Memory Map

The DSP requires a specific format for the data stored in the serial EEPROM. The first 28 bytes of the EEPROM are reserved for autoinitialization of PCI configuration registers. The remaining locations are not used for autoinitialization and can be used for storing other data. The EEPROM is always accessed as a 16-bit device. Table 5 summarizes the EEPROM memory map for the first 28 bytes. See also section 15.1 for details.

### Table 5. EEPROM Memory Map

| Address | Contents (msb Isb)                    |

|---------|---------------------------------------|

| 0h      | Vendor ID                             |

| 1h      | Device ID                             |

| 2h      | Class Code [7–0]/Revision ID          |

| 3h      | Class Code [23–8]                     |

| 4h      | Subsystem Vendor ID                   |

| 5h      | Subsystem ID                          |

| 6h      | Max_Latency/Min_Grant                 |

| 7h      | PC_D1/PC_D0 (power consumed D1, D0)   |

| 8h      | PC_D3/PC_D2 (power consumed D3, D2)   |

| 9h      | PD_D1/PD_D0 (power dissipated D1, D0) |

| Ah      | PD_D3/PD_D2 (power dissipated D3, D2) |

| Bh      | Data_scale (PD_D3PC_D0)               |

| Ch      | 0000 0000 PMC[14-9], PMC[5], PMC[3]   |

| Dh      | Checksum                              |

# 12.3 EEPROM Checksum

The configuration data contained in the EEPROM is checked against a checksum. The checksum is a 16-bit cumulative exclusive-OR (XOR) of the configuration data words contained in the EEPROM starting with an initial value of AAAAh. You must ensure that the proper 16-bit checksum value is written to address 0Dh when programming the EEPROM.

Checksum = AAAAh XOR Data(00h) XOR Data(01h)... XOR Data(0Ch)

If the checksum fails, the CFGERR bit in PCIIS and in HSR are set, and optionally, an interrupt to the DSP is generated. The DSP may or may not catch the interrupt, depending on the state of the core at the time. If the PCI is booting the device, the core is held in reset and will miss the interrupt.

The EEREAD bit in HSR is set, if EEPROM autoinitialization is used at power-on reset.

If the serial EEPROM is not accessed for PCI configuration purposes (that is, EEAI = 0, EESZ = 000b at reset), then the checksum is not performed.

Failed checksums result in the PCI configuration registers being initialized with default data. Refer to the specific PCI configuration registers to determine their default values (see section 15.1).

After successful PCI configuration register initialization (auto or default), the CFGDONE bit in RSTSRC is updated to allow the DSP to respond to reads, rather than terminating the cycle with disconnect retry.

### 12.4 DSP EEPROM Interface

The EEPROM can also be used by the DSP through three memory-mapped registers, EEPROM address register (EEADD), EEPROM data register (EEDAT), and EEPROM control register (EECTL). The DSP EEPROM interface is available immediately after reset. The CFGDONE bit in RSTSRC indicates when the EEPROM has been read for PCI autoinitialization.

Serial EEPROM device operation is controlled by seven instructions. The instruction opcode consists of two bits. Valid opcodes are presented in Table 6.

| Op Code               | Instruction | Description                       |

|-----------------------|-------------|-----------------------------------|

| 10                    | READ        | Reads data at specified address   |

| 00 (Address = 11xxxx) | EWEN        | Write enable                      |

| 11                    | ERASE       | Erase memory at address           |

| 01                    | WRITE       | Write memory at address           |

| 00 (Address = 10xxxx) | ERAL        | Erases all memory locations       |

| 00 (Address = 01xxxx) | WRAL        | Writes all memory locations       |

| 00 (Address = 00xxxx) | EWDS        | Disables programming instructions |

| Table 6. | FFPROM | Command | Summary |

|----------|--------|---------|---------|

|          |        | Commanu | Summary |

The EEPROM protocol is as follows:

- 1) Wait for the CFGDONE bit in RSTSRC to be set. The READY bit in EECTL and the EERDY bit in PCIIS are set as well.

- 2) Write EEPROM address to EEADD (address register, the EESZ determines which bits are significant).

- For EEPROM reads, skip this step. For EEPROM writes (instruction WRITE/WRAL), write data to EEDAT. This data is immediately transferred to an internal register. Therefore, a DSP read from EEDAT returns invalid data.

- 4) Write the two-bit op code to the EECNT bits in EECTL.

- 5) The EEPROM interface then clocks out the EEPROM serial sequence.

- 6) Poll for READY = 1 in EECTL, or wait for interrupt (EERDY = 1 in PCIIS).

- 7) For EEPROM writes, skip this step. For EEPROM reads (instruction READ), read data from EEDAT.