# TMS320C6474 Digital Signal Processor Silicon Revisions 2.1, 1.3, 1.2

# **Silicon Errata**

Literature Number: SPRZ283C October 2008–Revised March 2011

|            |           |                                                                                            | _  |

|------------|-----------|--------------------------------------------------------------------------------------------|----|

| 1 Intro    | duction   |                                                                                            | 5  |

| 1.1        | Device    | and Development Support Tool Nomenclature                                                  | 5  |

| 1.2        | 2 Packag  | ge Symbolization and Revision Identification                                               | 6  |

| 1.3        | 3 Silicon | Updates                                                                                    | 7  |

|            |           | on 2.1 Usage Notes and Known Design Exceptions to Functional                               | 8  |

| 2.1        | Silicon   | Revision 2.1 Usage Notes                                                                   | 8  |

|            | 2.1.1     | EMAC: SERDES PLL Lock                                                                      |    |

|            | 2.1.2     | User-Initiated Cache Coherence Operations Using Global Address Causes an Access Across SCR |    |

|            | 2.1.3     | Bootloader: Multicore Reset Control Enhancement                                            | 9  |

| 2.2        | 2 Silicon | Revision 2.1 Known Design Exceptions to Functional Specifications                          | 10 |

|            |           | on 1.3 Usage Notes and Known Design Exceptions to Functional                               | 32 |

| 3.1        | Silicon   | Revision 1.3 Usage Notes                                                                   | 32 |

|            | 3.1.1     | Bootloader: Multicore Boot Takes Core1 and Core 2 Out of Reset                             |    |

| 3.2        | 2 Silicon | Revision 1.3 Known Design Exceptions to Functional Specifications                          | 33 |

|            |           | on 1.2 Usage Notes and Known Design Exceptions to Functional                               | 56 |

| 4.1        | Silicon   | Revision 1.2 Usage Notes                                                                   | 56 |

| 4.2        | 2 Silicon | Revision 1.2 Known Design Exceptions to Functional Specifications                          | 56 |

| Appendix A | Revisio   | n History                                                                                  | 62 |

# List of Figures

| 1  | Lot Trace Code Examples for TMS320C6474 (ZUN Package)                 | 6  |

|----|-----------------------------------------------------------------------|----|

| -  |                                                                       |    |

| 2  | LOCK_CTL Register                                                     | 8  |

| 3  | L1D Cache Address Mapping                                             | 15 |

| 4  | Cache Line Operations Flow                                            | 16 |

| 5  | L1D Cache Address Mapping                                             | 25 |

| 6  | Sequence of Events                                                    | 26 |

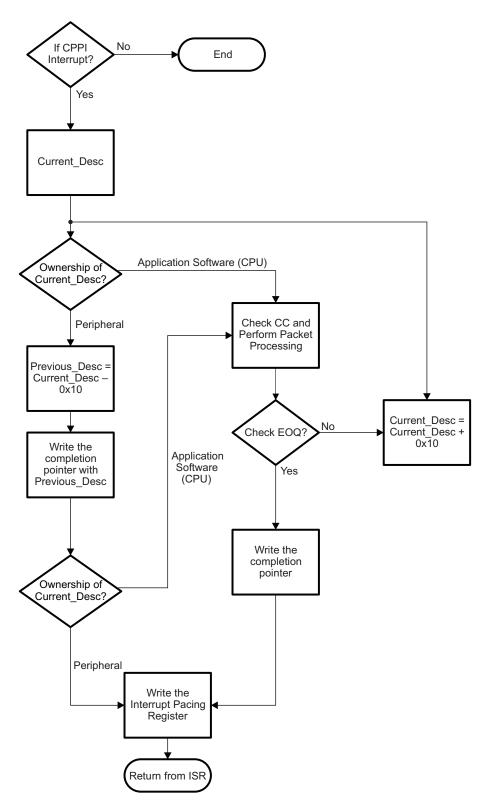

| 7  | ISR Workaround Flowchart                                              | 30 |

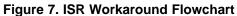

| 8  | IDMA, SDMA, and MDMA Paths                                            | 35 |

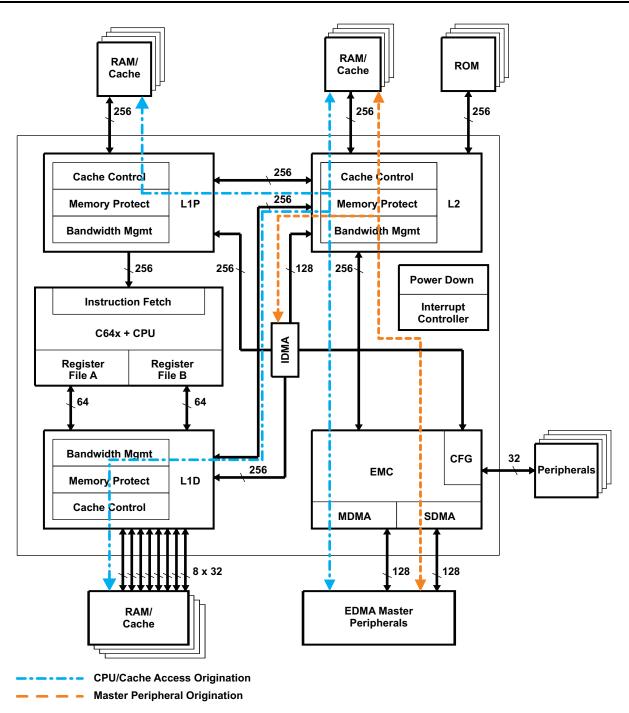

| 9  | SCR F Write Requests/Write Status                                     | 50 |

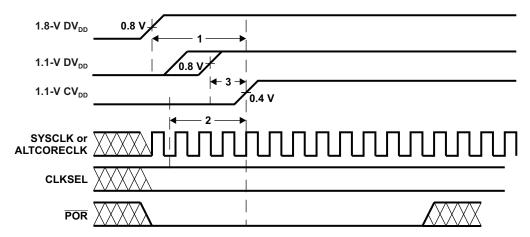

| 10 | Correct Device Input Clocks, Clock Selects, and Scaled Supply Timings | 58 |

| 11 | Prog Set Options Register                                             | 60 |

# List of Tables

| 1  | Lot Trace Codes                                  | 6  |

|----|--------------------------------------------------|----|

| 2  | Silicon Revision Variables                       | 6  |

| 3  | Silicon Revisions 1.2, 1.3, 2.1 Updates          | 7  |

| 4  | LOCK_CTL Register Field Descriptions             | 8  |

| 5  | Silicon Revision 2.1 Advisory List               | 10 |

| 6  | C6474 Default Master Priorities                  | 12 |

| 7  | C6474 Valid Priority Settings                    | 13 |

| 8  | C6474 UMAP1 Allocation                           | 14 |

| 9  | Value of X for L1D Cache                         | 15 |

| 10 | Value of X for L1D Cache                         | 25 |

| 11 | Silicon Revision 1.3 Advisory List               | 33 |

| 12 | GEM Transaction IDs                              | 48 |

| 13 | C6474 Default Master Priorities                  | 52 |

| 14 | C6474 Valid Priority Settings                    | 53 |

| 15 | Stall Conditions on Silicon Revisions            | 54 |

| 16 | UMAP0 and UMAP1 Address Ranges                   | 54 |

| 17 | Silicon Revision 1.2 Advisory List               | 56 |

| 18 | Device Input Clock Timing Parameter Descriptions | 57 |

| 19 | TC Registers Summary                             | 60 |

| 20 | C6474 Revision History                           | 62 |

|    |                                                  |    |

# TMS320C6474 DSP Silicon Revisions 2.1, 1.3, 1.2

# 1 Introduction

This document describes the silicon updates to the functional specifications for the TMS320C6474 digital signal processor; see the device-specific data manual, *TMS320C6474 Multicore Digital Signal Processor* (literature number <u>SPRS552</u>).

# 1.1 Device and Development Support Tool Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all DSP devices and support tools. Each DSP commercial family member has one of three prefixes: TMX, TMP, or TMS (e.g., TMS320C6474ZUN). Texas Instruments recommends two of three possible prefix designators for its support tools: TMDX and TMDS. These prefixes represent evolutionary stages of product development from engineering prototypes (TMX/TMDX) through fully qualified production devices/tools (TMS/TMDS).

Device development evolutionary flow:

- **TMX** Experimental device that is not necessarily representative of the final device's electrical specifications

- **TMP** Final silicon die that conforms to the device's electrical specifications but has not completed quality and reliability verification

**TMS** Fully-qualified production device

Support tool development evolutionary flow:

- **TMDX** Development-support product that has not yet completed Texas Instruments internal qualification testing

- TMDS

Fully-qualified development-support product

TMX and TMP devices and TMDX development-support tools are shipped against the following disclaimer:

"Developmental product is intended for internal evaluation purposes."

TMS devices and TMDS development-support tools have been characterized fully, and the quality and reliability of the device have been demonstrated fully. TI's standard warranty applies.

Predictions show that prototype devices (TMX or TMP) have a greater failure rate than the standard production devices. Texas Instruments recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

TMS320C64x+ is a trademark of Texas Instruments. RapidIO is a registered trademark of RapidIO Trade Association. All other trademarks are the property of their respective owners.

# 1.2 Package Symbolization and Revision Identification

The device revision can be determined by the lot trace code marked on the top of the package. The location of the lot trace code for the ZUN package is shown in Figure 1. Figure 1 also shows an example of C6474 package symbolization.

Lot have coue

Figure 1. Lot Trace Code Examples for TMS320C6474 (ZUN Package)

Silicon revision correlates to the lot trace code marked on the package. This code is of the format #xx-########. If xx is "21", then the silicon is revision 2.1. Table 1 lists the silicon revisions associated with each lot trace code for the C6474 device.

Each silicon revision uses a specific revision of the CPU and the TMS320C64x+<sup>™</sup> megamodule. The CPU revision ID identifies the silicon revision of the CPU. Table 2 lists the CPU and C64x+ megamodule revision associated with each silicon revision. The CPU revision can be read from the REVISION\_ID field of the CPU control status register (CSR). The C64x+ megamodule revision can be read from the REVISION field of the megamodule revision ID register (MM\_REVID) located at address 0181 2000h.

The VARIANT field of the JTAG ID register (located at 0288 0814h) changes between silicon revisions. Table 2 lists the contents of the JTAG ID register for each revision of the device. More details on the JTAG ID register can be found in the device-specific data manual, *TMS320C6474 Multicore Digital Signal Processor* (literature number <u>SPRS552</u>).

| LOT TRACE CODE ( xx) | SILICON REVISION | COMMENTS             |

|----------------------|------------------|----------------------|

| 21                   | 2.1              | Silicon revision 2.1 |

| 13                   | 1.3              | Silicon revision 1.3 |

| 12                   | 1.2              | Silicon revision 1.2 |

# Table 1. Lot Trace Codes

| SILICON REVISION CPU REVISI |                   | C64X+ MEGAMODULE REVISION | JTAG ID REGISTER VALUE |

|-----------------------------|-------------------|---------------------------|------------------------|

| 2.1 CPU_ID = 10h            |                   | Rev. 3.2                  | 0x4009 202Fh           |

| REVISION_ID = 05h           |                   | MM_REVID[REVISION] = 2h   | VARIANT = 0100b        |

| 1.3                         | CPU_ID = 10h      | Rev. 3.0                  | 0x2009 202Fh           |

|                             | REVISION_ID = 00h | MM_REVID[REVISION] = 0h   | VARIANT = 0010b        |

| 1.2                         | CPU_ID = 10h      | Rev. 3.0                  | 0x1009 202Fh           |

|                             | REVISION_ID = 00h | MM_REVID[REVISION] = 0h   | VARIANT = 0001b        |

# 1.3 Silicon Updates

Table 3 lists the silicon updates applicable to each silicon revision. For details on each advisory, see Section 2.2, Section 3.2, and Section 4.2 or click on the link below.

If the design exceptions are still applicable, the advisories have been moved up to the latest silicon revision section. Therefore, advisory numbering may not be sequential.

# Table 3. Silicon Revisions 1.2, 1.3, 2.1 Updates

|                                                                                               |                    | APPLIES TO SILICON REVISON |     |     |

|-----------------------------------------------------------------------------------------------|--------------------|----------------------------|-----|-----|

| SILICON UPDATE ADVISORY                                                                       | SEE                | 1.2                        | 1.3 | 2.1 |

| Potential Random E-fuse Blow                                                                  | Advisory 1.2.7     | Х                          | -   | -   |

| EDMA3CC COMPACTV Issue                                                                        | Advisory 1.2.9     | Х                          | -   | -   |

| DSP SDMA/IDMA: Unexpected Stalling of SDMA/IDMA Access to L2 SRAM                             | Advisory 1.3.1     | Х                          | х   | -   |

| Potential Data Corruption on SCR Bridge                                                       | Advisory 1.3.2     | Х                          | Х   | -   |

| Potential Insertion or Deletion of 2 Bits in SerDes Data Stream                               | Advisory 1.3.3     | Х                          | Х   | -   |

| MAC EOI Register Write Causes Potential CPU Lockup                                            | Advisory 1.3.4     | Х                          | Х   | -   |

| I2C: Slave Boot Aborts                                                                        | Advisory 1.3.6     | Х                          | Х   | -   |

| EMAC Boot Issue                                                                               | Advisory 1.3.7     | Х                          | Х   | -   |

| IP Block Containing CIC, CFGC, DTF, and IPC Registers Does Not Return Write Request Correctly | Advisory 1.3.8     | Х                          | х   | -   |

| DMA Access to L2 SRAM May Stall When the DMA Has Lower Priority Than the CPU                  | Advisory 1.3.9     | х                          | х   | -   |

| L2 Victim Traffic Due To L2 Block Writeback During Any<br>Pending CPU Request                 | Advisory<br>1.3.10 | х                          | х   | -   |

| Potential SerDes Clocking Issue                                                               | Advisory 2.1.1     | Х                          | Х   | Х   |

| SRIO OUTBOUND_ACKID Field Not Read Correctly                                                  | Advisory 2.1.2     | Х                          | Х   | Х   |

| SRIO Port 0 Reset Affects Other Ports                                                         | Advisory 2.1.3     | Х                          | Х   | Х   |

| DMA Access to L2 SRAM May Stall When the DMA and the CPU Command Priority is Equal            | Advisory 2.1.4     | Х                          | Х   | х   |

| DMA Corruption of External Data Buffer                                                        | Advisory 2.1.5     | Х                          | Х   | Х   |

| SPLOOP CPU Cross-Path Stall                                                                   | Advisory 2.1.6     | Х                          | Х   | Х   |

| DMA Corruption of L1D\$ Allocation                                                            | Advisory 2.1.7     | -                          | -   | Х   |

| Error Detection and Correction Incorrectly Reporting Error                                    | Advisory 2.1.8     | Х                          | Х   | Х   |

| SRIO May Fail to Send Interrupt for Completed TX or RX Message                                | Advisory 2.1.9     | Х                          | х   | х   |

| Serial RapidIO Internal Digital Loopback is Not Always Stable                                 | Advisory<br>2.1.10 | Х                          | Х   | х   |

# 2 Silicon Revision 2.1 Usage Notes and Known Design Exceptions to Functional Specifications

# 2.1 Silicon Revision 2.1 Usage Notes

Usage Notes highlight and describe particular situations where the device's behavior may not match presumed or documented behavior. This may include behaviors that affect device performance or functional correctness. These notes will be incorporated into future documentation updates for the device (such as the device-specific data manual), and the behaviors they describe will not be altered in future silicon revisions.

# 2.1.1 EMAC: SERDES PLL Lock

A LOCK\_CTL register is missing in the EMAC Subsystem SGMII Registers section of the TMS320C6474 DSP Ethernet Media Access Controller (EMAC)/ Management Data Input/Output (MDIO) User's Guide (literature number SPRUG08). The register is present in the device, but it is not documented.

The register is at address offset 0x88 in the EMAC Control Module Registers memory map (base address 0x02C8 1000). The LOCK\_CTL register is shown in Figure 2 and described in Table 4.

| 31       | 1 | 0       |

|----------|---|---------|

| Reserved |   | LOCK_EN |

| R-0      |   | R/W-0   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

# Figure 2. LOCK\_CTL Register

| Bit | Field    | Value | Description                                                                                                                                                                                 |  |

|-----|----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31  | Reserved |       | Reserved. Read as zero.                                                                                                                                                                     |  |

| 0   | LOCK_EN  |       | ock Enable. This bit controls enabling of the SERDES lock function.                                                                                                                         |  |

|     |          | 0     | SERDES lock function is disabled. The lock function does not asynchronously reset the SGMII<br>lock.                                                                                        |  |

|     |          | 1     | ERDES lock function is enabled. The lock function asynchronously resets SGMII block.                                                                                                        |  |

|     |          |       | The value of the LOCK bit of the SGMII status register is valid only if the lock function is enabled. If the lock function is disabled, then the value of the LOCK bit is always read as 1. |  |

# Table 4. LOCK\_CTL Register Field Descriptions

# The SGMII initialization has the following steps:

Uint32 \* lock\_ctl;

```

/* Soft reset SGMII and wait till the Reset is complete */

SGMII_REGS->SOFT_RESET = 0x00000001;

while (SGMII_REGS->SOFT_RESET != 0x00000000);

```

```

SGMII_REGS->CONTROL = 0x00000001;

SGMII_REGS->MR_ADV_ABILITY = 0x00000001;

SGMII_REGS->TX_CFG = 0x00000e21;

SGMII_REGS->RX_CFG = 0x00081021;

SGMII_REGS->AUX_CFG = 0x0000000b;

```

The SGMII AUX\_CFG register enables power for the SERDES PLL. After the SERDES PLL is powered up, it takes 1 µs (for SERDES PLL power regulator to stabilize) + 200 REFCLKP/N (1.6 µs for 125-MHz REFCLK) cycles to lock in the required frequency. So, software has to run a loop for checking the status of the PLL lock before proceeding. The SGMII status register provides the status of the SERDES PLL (the LOCK bit shows whether it is locked or not).

The LOCK signal is a field (single bit) of the SGMII status register. It is pulled high at reset and remains high until the LOCK\_EN field in the LOCK\_CTL register is disabled. Only after enabling the LOCK\_EN bit in the LOCK\_CTL register can the LOCK bit in the SGMII status register reflect the correct status of the SERDES PLL lock.

Silicon Revision 2.1 Usage Notes and Known Design Exceptions to Functional Specifications

# 2.1.2 User-Initiated Cache Coherence Operations Using Global Address Causes an Access Across the SCR

It has been found that if a user issues a manual writeback or writeback and invalidate command using the global address of the Core, a single 128-bit word access is issued out of the MDMA port across the SCR to the same core's SDMA port. Note that this does not happen on manual invalidate commands. Also, it does not happen when the local address is used instead of the global address.

# 2.1.3 Bootloader: Multicore Reset Control Enhancement

For silicon revisions 2.x on the C6474 device, an enhancement has been added to enable the user to control whether to take core1 and core2 out of reset in the bootloader.

Address 0x108FFFF8 is used as a flag to signal the bootloader whether to take core1 and core2 out of reset at the end of the boot. The bootloader initializes this address to 0. If this address is initialized to a non-zero value by the application code or the secondary bootloader after the bootloader finishes downloading the boot image, the first-level bootloader does not take core1 and core2 out of reset; otherwise, the first-level bootloader takes core1 and core2 out of reset.

If core1 and core2 are kept in the reset state after the first-level boot, the application code or the secondary bootloader in core0 can choose when to take core1 and core2 out of reset by setting the EVTPULSE4 bit (bit 4) of the C64x+ Megamodule core0's EVTASRT register to 1. This process is valid only once: writing 1, then writing 1 again does not bring core1 and core2 out of reset again. Core1 and core2 begin execution from their L2 RAM base address after this operation.

q

**NOTE:** This behavior violates Advisory 1.3.1, *DSP SDMA/IDMA: Unexpected Stalling of SDMA/IDMA Access to L2 SRAM.* If performing these operations, ensure that only local addresses are used. For further details, see the *Deadlock Avoidance* section in Workaround Method 3 of Advisory 1.3.1.

# 2.2 Silicon Revision 2.1 Known Design Exceptions to Functional Specifications

Table 5 lists the silicon revision 2.1 known design exceptions to functional specifications.

# Table 5. Silicon Revision 2.1 Advisory List

| Title                                                                                               | Page |

|-----------------------------------------------------------------------------------------------------|------|

| Advisory 2.1.1 — Potential SerDes Clocking Issue                                                    | 11   |

| Advisory 2.1.2 — SRIO OUTBOUND_ACKID Field Not Read Correctly                                       | 11   |

| Advisory 2.1.3 — SRIO Port 0 Reset Affects Other Ports                                              | 11   |

| Advisory 2.1.4 — DMA Access to L2 SRAM May Stall When the DMA and the CPU Command Priority is Equal | 12   |

| Advisory 2.1.5 — DMA Corruption of External Data Buffer                                             | 14   |

| Advisory 2.1.6 — SPLOOP CPU Cross-Path Stall                                                        | 22   |

| Advisory 2.1.7 — DMA Corruption of L1D\$ Allocation                                                 | 24   |

| Advisory 2.1.8 — Error Detection and Correction Incorrectly Reporting Error                         | 27   |

| Advisory 2.1.9 — SRIO May Fail to Send Interrupt for Completed TX or RX Message                     | 29   |

| Advisory 2.1.10 — Serial RapidIO Internal Digital Loopback is Not Always Stable                     | 31   |

| www.ti.com            | Silicon Revision 2.1 Usage Notes and Known Design Exceptions to Functional Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Advisory 2.1.1        | Potential SerDes Clocking Issue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Revision(s) Affected: | 2.1, 1.3, 1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Details:              | An issue has been found in the SerDes interfaces that causes a SerDes clocking problem in normal functional operation. This problem will not occur when external pull-down is applied on the TCK pin (JTAG controller clock). SerDes are used in the Ethernet interface (EMAC), Serial RapidIO <sup>®</sup> interface (SRIO) and the Antenna Interface (AIF).                                                                                                                                                                          |  |  |  |  |

|                       | The TCK pin (JTAG controller clock) is internally assigned to an internal signal that is used by the SerDes macro. For the SerDes macro to get proper clocking in the normal functional operation, it needs the internal signal to be held low. However, there is an internal pull-up on the TCK, creating problems for SerDes operation. This problem exists on all SerDes interfaces.                                                                                                                                                |  |  |  |  |

| Workaround:           | The TCK pin should be externally pulled down with an 1-k $\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Advisory 2.1.2        | SRIO OUTBOUND_ACKID Field Not Read Correctly                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Revision(s) Affected: | 2.1, 1.3, 1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Details:              | The OUTBOUND_ACKID field of the RIO_SP(n)_ACKID_STAT register should be<br>updated by hardware each time a packet is sent out. The value should reflect the ACKID<br>value to be used on the next transmit packet. This field is being updated by the hardware<br>as expected. The field can also be written by the software and these writes also<br>succeed. However, a hardware error prevents this field from being read. The<br>OUTBOUND_ACKID always reads as zero. This problem does not cause any impact to<br>link operation. |  |  |  |  |

| Workaround:           | There is no workaround for this advisory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Advisory 2.1.3        | SRIO Port 0 Reset Affects Other Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| Revision(s) Affected: | 2.1, 1.3, 1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Details:              | The SerDes for SRIO should allow the reset of individual 1X ports without affecting the state of the other operational ports. There are dedicated MMR bits to reset 1X ports, which are the BLKn_EN (n=58) at offsets 0x60 and 0x68. However, the BLK5_EN that controls reset for port 0 also resets all other ports. Therefore, it is impossible to reset port 0 without affecting all other ports.                                                                                                                                   |  |  |  |  |

| Workaround:           | There is no workaround for this advisory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

# Advisory 2.1.4 DMA Access to L2 SRAM May Stall When the DMA and the CPU Command Priority is Equal

**Revision(s) Affected:** 2.1, 1.3, 1.2

Details:

The L2 memory controller in the GEM has programmable bandwidth management features that are used to control bandwidth allocation for all requestors. There are two parameters to control this, command priority and arbitration counter MAXWAIT values. Each requestor has a command priority and the requestor with the higher priority wins. However, there are also counters associated with each requestor that track the number of cycles each requestor loses arbitration. When this counter reaches a threshold (MAXWAIT), which is programmed by the user (or default value), the losing requestor gets an arbitration slot and wins for that cycle. There are four such requestors: CPU, DMA (SDMA and IDMA), user cache coherency operation, and global cache coherence. Global-coherence operations are highest priority, while user-coherence operations are lowest priority. However, there is active arbitration done for the CPU and the DMA (SDMA/IDMA) commands. The priority for DMA commands comes from an external master as part of the SDMA command or a programmable register, IDMA1\_COUNT, in the GEM for IDMA commands. The priority for CPU accesses to L2 is in a programmable register, CPUARBU, in the GEM. For the default priority values, see Table 6.

More details on the bandwidth management feature can be found in the C64x+ DSP Megamodule Reference Guide (SPRU871).

| MASTER                                           | DEFAULT MASTER PRIORITIES<br>(0 = Highest priority,<br>7 = Lowest priority) | PRIORITY CONTROL                              |

|--------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------|

| EDMA3TCx                                         | 0                                                                           | QUEPRI.PRIQx (EDMA3 register)                 |

| SRIO (Data Access)                               | 0                                                                           | PER_SET_CNTL.CBA_TRANS_PRI<br>(SRIO register) |

| SRIO (Descriptor Access)                         | 1                                                                           | PRI_ALLOC.SRIO_CPPI                           |

| EMAC                                             | 1                                                                           | PRI_ALLOC.EMAC                                |

| C64x+ Megamodule (MDMA port)                     | 7                                                                           | MDMAARBE.PRI (C64x+ Megamodule register)      |

| C64x+ Megamodule (CPU Arbitration control to L2) | 1                                                                           | CPUARBU (C64x+ Megamodule register)           |

| C64x+ Megamodule (IDMA channel 1)                | 0                                                                           | IDMA1_COUNT (C64x+ Megamodule register)       |

Table 6. C6474 Default Master Priorities

**NOTE:** When the SDMA has finished sending all of its commands to the L2 controller, the C64x+ Megamodule drops the transfer priority down to 7 if no further commands are in the pipeline. This condition happens when there is a single-word access, a burst of <32B with no other SDMA commands pending or for the last 64B only of a burst that is >64B with no other SDMA commands pending. This effective priority level is what the L2 controller uses to arbitrate these SDMA commands with the CPU, irrespective of the master peripheral's actual programmed priority value. Therefore, priority 7 is not a valid priority level for the CPU. If, for any reason, this "demoted" transfer is still pending upon initiation of another transfer, it automatically inherits the priority of that new transfer.

| www.ti.com  | Silicon Revision 2.1 Usage Notes and Known Design Exceptions to Functional Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | The L2 memory controller is supposed to give equal bandwidth to the DMA and the CPU, by alternating between the two for arbitration. Instead, the L2 memory controller gives larger bandwidth allocation to the CPU accesses when the DMA and the CPU priorities are same. The CPU commands keep winning arbitration over the DMA as long as there are no other internal conditions (stalls, etc.) that force the DMA to win arbitration. This typically happens when CPU accesses keep the L2 memory controller busy every cycle, hence, the DMAs stall until the stream of CPU accesses completes. For example, if a continuous stream of L1D write misses to L2 keep the L2 memory controller busy every cycle, the DMAs stall for the entire duration of the write miss stream. |

| Workaround: | Ensure that the CPU is at a different priority than the DMA commands to L2. The priority for CPU accesses to L2 is in a programmable register, CPUARBU, in the GEM. However, lowering the CPU priority may impact the performance since, in case of contention, the CPU accesses to L2 can get stalled due to DMA accesses. The CPUARBU should not be set to 7 (see Note above).                                                                                                                                                                                                                                                                                                                                                                                                    |

The recommended workaround is to pick a single priority value for the CPU accesses to L2 only. That leaves the remaining 6 priority levels free for other accesses to L2 (see Table 7).

| CPU PRIORITY     | ALLOWED SDMA PRIORITIES |

|------------------|-------------------------|

| 0                | 1-7                     |

| 1                | 0, 2-7                  |

| 2                | 0-1, 3-7                |

| 3                | 0-2, 4-7                |

| 4                | 0-3, 5-7                |

| 5                | 0-4, 6-7                |

| 6                | 0-5, 7                  |

| 7 <sup>(1)</sup> | -                       |

Table 7. C6474 Valid Priority Settings

<sup>(1)</sup> Do not set CPU priority to 7.

# Advisory 2.1.5 DMA Corruption of External Data Buffer

**Revision(s) Affected:** 2.1, 1.3, 1.2

Details:

Under a specific set of circumstances, an L1D snoop-write updates an unintended L1D cache line. This leads to a corrupted line in L1D and can lead directly to program misbehavior. If the corrupted line is then modified by a CPU write access, a subsequent victim writeback from L1D could commit the corrupted line to lower levels of memory. Two key requirements for this issue are:

- The DMA writes to buffers in UMAP1 only (see below).

- This must be cached and unmodified in L1D (read by the CPU but not yet written to it).

The L2 memory is typically shared across the two unified memory access ports, UMAP0 and UMAP1. This issue occurs only if the buffer is located in UMAP1. For the UMAP1 allocation on the C6474 device, see Table 8.

| L2 CONFIGURATION | UMAP1 | ADDRESS RANGE | AFFECTED |

|------------------|-------|---------------|----------|

| Symmetric        | N/A   | N/A           | No       |

- The CPU reads from an external, cacheable address.

- UMAP0 and UMAP1 are the two ports on the C64x+ Megamodule used to connect the L2 Memory controller and the physical RAMs. For the UMAP1 allocation on the C6474 device, see Table 8

- For information on L1D cache coherence protocol, see section 3.3.6, Cache Coherence Protocol, in the C64x+ DSP Megamodule Reference Guide (SPRU871).

- DMA in the following description refers to all non-CPU requestors. This includes IDMA, EDMA, and any other master in the system.

Under the specific set of circumstances listed below, a snoop-write updates an L1D cache line other than the one intended. This leads to a corrupted line in L1D. Corruption only happens when the buffer in UMAP1 is cached in L1D while the CPU is consuming external, cacheable data.

The prerequisite before the window where the issue occurs is:

- The CPU reads an L2 location in UMAP1 and has not modified (written) to the same location before the window where the issue occurs.

- Because of this, a 64B cache line is allocated clean in L1D (referred to here as Cache Line A).

The following steps must all occur concurrently to see the issue (note that the concurrency is within the cache subsystem, so events visible at the CPU or the DMA are not occurring during the same exact cycle):

- 1. The L1D is currently processing a snoop request or some other request that prevents it from accepting new snoops. This could have been caused by any of the following that is still being processed from previous actions:

- DMA read/write

- L1D read/invalidate

- L1D read + victim

- 2. The DMA writes to Cache Line A, mentioned in the prerequisite above. This means that it is not necessarily the same exact address, but must be within the same 64B cache line.

- As a result, a snoop-write request is generated but it is blocked because the L1D is still busy with Step 1.

- 3. The CPU reads from a cacheable, external memory (e.g., DDR) that is a set match to Cache Line A (referred to here as Cache Line B).

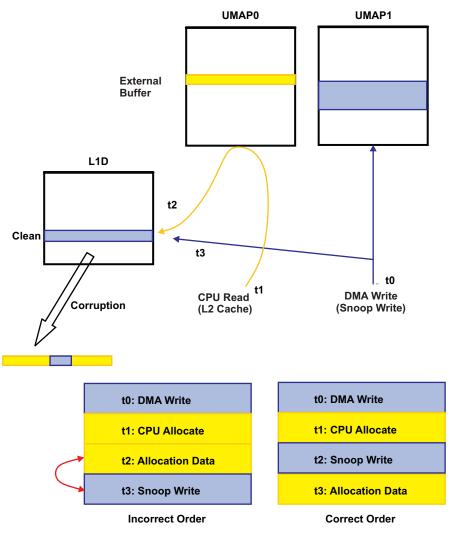

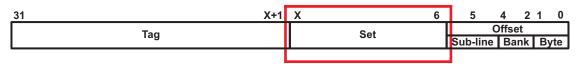

Determining if two addresses are a set match can be done by comparing certain bits

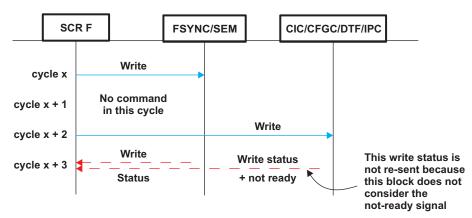

of two addresses. The mapping of an address to a location in L1D cache is shown in Figure 3.

| 31 | X+1 | X   | 6 | 5        | 4          | 2 | 1 0  |

|----|-----|-----|---|----------|------------|---|------|

| т  | ag  | Set | - | Sub-line | Offs<br>Ba |   | Byte |

|    |     |     |   |          |            |   |      |

The value X is determined by how large the L1D cache is in the particular application (see Table 9).

Figure 3. L1D Cache Address Mapping

| AMOUNT OF L1D CACHE | X BIT POSITION |

|---------------------|----------------|

| 0KB                 | N/A            |

| 4KB                 | 10             |

| 8KB                 | 11             |

| 16KB                | 12             |

| 32KB                | 13             |

| Table 9. Va | alue of X for | L1D Cache |

|-------------|---------------|-----------|

|-------------|---------------|-----------|

If you use the default configuration, 32KB, as an example, bits [13:6] are a set match if they are identical in two different addresses. Some examples of set matches are shown below:

- 0x0080 2A80 00000001000000010101010000000

- 0x8000 2A80 100000010000000010101010000000

- Ox0080 2A8A 000000010000000010101010001010

- This results in a cache miss from the CPU for an external address and sends a read request to L2 cache for the line (and possibly to the external source on an L2 cache miss or if no L2 cache is present).

The results of the above cause the following:

L2 sends both the return data for the L1D read miss request (response of Step 3 above) and the data for the snoop-write (response of Step 2 above). The L1D commits the snoop-write data after the L2 return data.

As a result, L1D now holds the wrong data for the external address (Cache Line B) and commits the data to cache. Cache Line B remains marked "clean." If the program does not write to the uncorrupted portion of the line and does not read the corrupted portion of the line, the corruption goes unnoticed. If the program writes to the uncorrupted portion of the line, the corrupted data gets written back to L2 cache and/or external memory. Otherwise, the corruption disappears when L1D discards the line.

Cache lines holding external addresses are the only cache lines that exhibit corruption. Corruption only happens when DMA buffers in UMAP1 get cached in L1D. Additionally, corruption only happens when the DMA buffer is clean, meaning that it gets discarded without generating a victim. Thus, this affects buffers where the DMA writes and the CPU reads. It does not affect buffers that the CPU only writes and/or DMA only reads.

One can identify this issue unambiguously by examining the corrupted memory range in CCStudio using the cache tag viewer. The corrupted data shows up in the include L1D view in a memory window, but not in the exclude L1D view. The cache tag viewer should indicate that the line is also "clean" and the corrupt data should also be visible in its intended destination, which must be in UMAP1 and map to the same L1D set as the corrupted line.

Figure 4 shows the flow of these operations, the incorrect order that causes the issue, and the correct order. The blue line is Cache Line A and the yellow line is Cache line B.

Figure 4. Cache Line Operations Flow

Workarounds:

In the issue described above, all of the conditions must be true for the issue to occur. The workarounds focus on picking one of the conditions and removing it so that you do not need to worry about the other conditions.

TI proposes starting with workaround 1 as an immediate fix. The other workarounds that follow may provide a solution with reduced overhead and/or simplified implementation, depending on the customer's system.

| www.ti.com | Silicon Revision 2.1 Usage Notes and Known Design Exceptions to Functional Specifications |

|------------|-------------------------------------------------------------------------------------------|

|            | Workaround 1: Write Back and Invalidate DMA Buffers                                       |

|            | 1.1D corruption occurs when the DMA writes to a huffer in LIMAP1 that is also eached in   |

L1D corruption occurs when the DMA writes to a buffer in UMAP1 that is also cached in L1D at the same time the L1D is discarding the buffer. Thus, this affects buffers where the DMA writes and the CPU reads. It does not affect buffers that the CPU only writes and/or the DMA only reads.

To prevent this sort of race condition, programs should discard inbound DMA buffers in UMAP1 immediately after use and keep a strict policy of "buffer ownership" such that a given buffer is owned only by the CPU or the DMA at any given time.

This model assumes the following:

- 1. The DMA fills the buffer during a period when the CPU does not access it.

- 2. The DMA engine or other mechanism signals to the CPU that it has finished filling the buffer.

- 3. The CPU operates on the buffer, reading and writing to it, as necessary. The DMA does not access the buffer at this time.

- 4. The CPU relinquishes control of the buffer so that DMA may refill it. (This may be an implicit step in many implementations if the period between refills is much longer than the time it takes the CPU to process the refilled buffer.)

To implement this workaround, programmers must write back and invalidate the buffer from L1D cache after Step 3 and before Step 4. This eliminates the prerequisite for the issue to occur should another DMA, in the future, be a set match to the reads that the CPU just performed.

There are multiple mechanisms for doing this, but the most straightforward is to use the L1D block cache writeback-invalidate mechanism via L1DWIBAR/L1DWIWC.

The recommended implementation of this workaround requires calling the I1d\_block\_wbinv.asm function (see the L1D Block Writeback-Invalidate Routine below). It can be invoked as follows:

void lld\_block\_wbinv(void \*base, size\_t byte\_count);

To writeback-invalidate a C array, one could then do:

/\* ... \*/

lld\_block\_wbinv(&array[0], sizeof(array));

Programmers should insert such a call whenever the code is done with a particular DMA buffer in UMAP1, before the DMA controller can refill it. The I1d\_block\_wbinv() function is non-interruptible. Its overhead is proportional to the size of the buffer.

**NOTE:** To ensure complete effectiveness, DMA buffers must always start on an L1D cache-line boundary (64-byte boundary) and occupy a multiple of 64 bytes. This may require increasing the size of some DMA buffers slightly. This is necessary to prevent accesses to an unrelated buffer or variable from bringing a portion of the DMA buffer back into the L1D cache.

# L1D Block Writeback-Invalidate Routine

```

;; ______

;; L1D Block Writeback-Invalidate

;;

;;

;;

lld_block_wbinv(void *base, size_t byte_count);

;;

;;

;;

;;

;; Performs a block writeback-invalidate from L1D to L2. It can be used

;;

;; on any address range (L2 or external), but it only operates on L1D

;;

;; cache.

;;

;;

;;

;; Maximum block size is 256K. Exact maximum byte count depends on the

;;

;; alignment of the block.

;;

;;

;;

ii Interrupts are disabled during the block writeback operation.

;;

;; ========================;;;

```

www.ti.com

| .asg 0x01844030, L1DWI<br>.global _l1d_block_wbinv<br>.text<br>.asmfunc<br>_l1d_block_wbinv:    | ; L1D Block Wb-Inv; BAR at 0, WC at 1                                                                                                           |

|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDK 0x10, B0<br>SHRU A4, 24, B2<br>CMPEQ B0, B2, B0                                            | <pre>; \_ Get global alias prefix ; / ; Get prefix from address ; Check if address prefix is global ; Remove global prefix from address ;</pre> |

| CLR A4, 0, 5, A1<br>   ADD A4, B4, B1                                                           | ; Align to L1D cache line boundary<br>; Compute end of buffer                                                                                   |

| ADDK 63, B1<br>CLR B1, 0, 5, B1                                                                 | ; \_ Round to next L1D cache line ; /                                                                                                           |

| SUB B1, A1, B1<br>   MVKH L1DWI, B6                                                             | ; Count cache-line span in bytes<br>;                                                                                                           |

| SHR B1, 2, B1<br>   DINT                                                                        | ; Convert to "word count"<br>; Disable interrupts                                                                                               |

| STW A1, *B6[0]<br>STW B1, *B6[1]                                                                | ; Store base address<br>; Store word count                                                                                                      |

| <pre>; Note: The following loop i ; interfering with the block loop: LDW *B6[1], B1 NOP 4</pre> | -                                                                                                                                               |

| [ B1] BNOP loop, 5                                                                              | ; Loop until done                                                                                                                               |

| RINT<br>RETNOP B3, 5                                                                            | ; Reenable interrupts<br>; Return to caller                                                                                                     |

| .endasmfunc                                                                                     |                                                                                                                                                 |

| ;; ====================================                                                         | ;;                                                                                                                                              |

#### ;; End of file: lld\_block\_wbinv.asm ;; ;; ==========;;

# Workaround 2: Make DMA Buffers Dirty After Use

The errant snoop-write occurs only when the DMA buffer in L1D has not been modified. This is due to the additional snoop-checking mechanisms associated with tracking victims as they leave L1D.

Therefore, another workaround is to mark DMA buffers as "dirty" before releasing them. This generates additional victims whenever the buffer gets pushed out of L1D. It also blocks the errant snoop-write.

This workaround assumes a similar model to Workaround 1, but uses the make\_dirty() function (see the Mark Buffer Dirty Routine below). The make\_dirty() function reads one byte from each cache line of the buffer and writes the same value back to it immediately.

The function is called as follows:

void make\_dirty(void \*base, size\_t byte\_count);

#### Mark Buffer Dirty Routine

```

;; ______;

;; Make a block of data "dirty" in L1D

;;

;;

;;

;;

make_dirty(void *base, size_t byte_count);

;;

;;

;;

;; =============================;;;

.global _make_dirty

.text

.asmfunc

```

Silicon Revision 2.1 Usage Notes and Known Design Exceptions to Functional Specifications

| _make_dirty:                            |   |

|-----------------------------------------|---|

|                                         |   |

| ADDK 63, B4                             |   |

| SHR B4, 6, B4                           |   |

| MVC B4, ILC                             |   |

| MVK 64, A5                              |   |

| MVK 64, B5                              |   |

| MV A4, B4                               |   |

| NOP                                     |   |

| SPLOOP 1                                |   |

| LDBU *A4++[A5], A1                      |   |

| NOP 4                                   |   |

| MV.L A1, B1                             |   |

| STB B1, *B4++[B5]                       |   |

| SPKERNEL                                |   |

| SEKEMIEL                                |   |

|                                         |   |

| RETNOP B3, 5                            |   |

|                                         |   |

| .endasmfunc                             |   |

|                                         |   |

| ;;===================================== | ; |

| ;; End of file: make_dirty.asm ;        | ; |

| ;; ==================================== | ; |

#### NOTE:

- This workaround is *not* acceptable if the DMA could be writing to the buffer at the same time make\_dirty() function gets called. The process of making the cache line dirty requires reading and writing within the buffer and, so, the CPU's writes could overwrite the inbound data from the DMA.

- 2. This workaround may cause the application to be affected by the issue described in Advisory 2.0.6, DMA Corruption of L2 RAM Data.

#### Workaround 3: Do Not Cache Data From External Memory in L1D

If your program only makes a small number of data accesses to external memory, consider marking the data portions of external memory as non-cacheable. This prevents caching copies of external memory in L1D cache.

Alternately, to prevent the line from allocating in L1D, freeze the L1D cache around each access to an external address. The long\_dist\_load\_word function (see the Long Distance Load Word Routine below) is suitable for isolated accesses. For larger accesses, such as reading a block, other techniques may be more appropriate.

The incorrect snoop-write only occurs when the L1D read miss involved is to an external address. The snoop-write corrupts the newly cached copy in L1D. If all accesses to external data memory are non-cacheable or occur while L1D is frozen, this prevents copies from being stored in L1D.

# Long Distance Load Word Routine

| ;; |                                                                        | ;; |

|----|------------------------------------------------------------------------|----|

| ;; | Long Distance Load Word                                                | ;; |

| ;; |                                                                        | ;; |

| ;; | int long_dist_load_word(volatile int *addr)                            | ;; |

| ;; |                                                                        | ;; |

| ;; | This function reads a single word from a remote location with the L1D  | ;; |

| ;; | cache frozen. This prevents L1D from sending victims in response to    | ;; |

| ;; | these reads, thus preventing the L1D victim lock from engaging for the | ;; |

| ;; | corresponding L1D set.                                                 | ;; |

| ;; |                                                                        | ;; |

| ;; | The code below does the following:                                     | ;; |

| ;; |                                                                        | ;; |

| ;; | 1. Disable interrupts                                                  | ;; |

| ;; | 2. Freeze L1D                                                          | ;; |

| ;; | 3. Load the requested word                                             | ;; |

| ;; | 4. Unfreeze L1D                                                        | ;; |

| ;; | 5. Restore interrupts                                                  | ;; |

| ;; |                                                                        | ;; |

| ;; | Interrupts are disabled while the cache is frozen to prevent affecting | ;; |

| ;; | the performance of interrupt handlers. Disabling interrupts during     | ;; |

|    |                                                                        |    |

# Silicon Revision 2.1 Usage Notes and Known Design Exceptions to Functional Specifications

www.ti.com

```

;; the long distance load does not greatly impact interrupt latency,

;;

;; because the CPU already cannot service interrupts when it's stalled by

;;

;; the cache. This function adds a small amount of overhead (~20 cycles)

;;

;; to that operation.

;;

;;

;;

;; =================;;;

.asg 0x01840044, L1DCC ; L1D Cache Control

.global _long_dist_load_word

.text

.asmfunc

; int long_dist_load_word(volatile int *addr)

_long_dist_load_word:

MVKL L1DCC, B4

MVKH L1DCC, B4

DINT

; Disable interrupts

MVK 1, B5

STW B5, *B4

LDW *B4, B5

; \_ Freeze cache

; /

NOP 4

SHR B5, 16, B5 ; POPER -> OPER

LDW *A4, A4 ; read value ren

LDW *A4, A4

; read value remotely

NOP 4

STW B5, *B4

; \_ Restore cache

RET B3

LDW *B4, B5

; /

NOP 4

RINT

; Restore interrupts

.endasmfunc

;; End of file: ldld.asm

;;

```

;; ==================================;;

#### Workaround 4: Allocate DMA buffers in L1D RAM or UMAP0

If possible, move DMA buffers that the CPU reads directly out of UMAP1 to either UMAP0 or L1D RAM. DMA buffers that the CPU does not access directly can remain in UMAP1 safely, as these do not generate snoops.

If your set of in-bound DMA buffers does not fit in L1D RAM and UMAP0 statically, consider paging buffers from UMAP1 to either UMAP0 or L1D RAM. That is, allow the DMA to write to buffers in UMAP1 freely, but never read them directly from the CPU. Instead, use the IDMA to copy a buffer from UMAP1 to either UMAP0 or L1D RAM before using it.

The IDMA1 utility functions (see the IDMA Channel 1 Block Copy Routine below) can be used for copying data with the IDMA controller.

# IDMA Channel 1 Block Copy Routine

| ;; |                                                                     | ;; |

|----|---------------------------------------------------------------------|----|

| ;; | TEXAS INSTRUMENTS INC.                                              | ;; |

| ;; |                                                                     | ;; |

| ;; | Block Copy with IDMA Channel 1                                      | ;; |

| ;; |                                                                     | ;; |

| ;; | REVISION HISTORY                                                    | ;; |

| ;; | 13-Feb-2009 Initial version J. Zbiciak                              | ;; |

| ;; |                                                                     | ;; |

| ;; | DESCRIPTION                                                         | ;; |

| ;; | The following macro functions are defined in this file:             | ;; |

| ;; |                                                                     | ;; |

| ;; | idmal_copy(void *dst, void *src, int word_count)                    | ;; |

| ;; | idmal_wait(IDMA_PEND or IDMA_ACTV)                                  | ;; |

| ;; |                                                                     | ;; |

| ;; | NOTE: The last arg is WORD count, not byte count. 1 word = 4 bytes. | ;; |

| ;; |                                                                     | ;; |

| ;; |                                                                     | ;; |

| ;; | Copyright ©) 2009 Texas Instruments, Incorporated.                  | ;; |

| ;; | All Rights Reserved.                                                | ;; |

| ;; |                                                                     | ;; |

|    |                                                                     |    |

|    | .asg 0x01820100, IDMA1_STATUS                                       |    |

|   | .asg 0x01820108, IDMA1_SOURCE                                                                            |

|---|----------------------------------------------------------------------------------------------------------|

|   | .asg 0x0182010C, IDMA1_DEST                                                                              |

|   | .asg 0x01820110, IDMA1_COUNT                                                                             |

|   | .asg 0x01820100, IDMA1_BASE                                                                              |

|   | .asg (IDMA1_STATUS - IDMA1_BASE), OFS_IDMA1_STATUS<br>.asg (IDMA1_SOURCE - IDMA1_BASE), OFS_IDMA1_SOURCE |

|   | .asg (IDMA1_DEST - IDMA1_BASE), OFS_IDMA1_DEST                                                           |

|   | .asg (IDMA1_COUNT - IDMA1_BASE), OFS_IDMA1_COUNT                                                         |

|   | ;;                                                                                                       |

|   | ;; IDMA1_COPY: Copy a block of words to dst from src with IDMA channel 1<br>;;                           |

|   | ; USAGE                                                                                                  |

| ; | ;; idmal_copy( <dest address="">, <source address=""/>, <word count="">)</word></dest>                   |

| ; | ;;                                                                                                       |

|   | ;; Both source and destination addresses must be word aligned.                                           |

|   |                                                                                                          |

|   | ;; The IDMA gets issued at top priority. Only bits 13:0 of the word                                      |

|   | ;; count are significant.<br>;;                                                                          |

|   | alobal idmal conv                                                                                        |

|   | .global _idmal_copy<br>.asmfunc                                                                          |

|   | _idmal_copy:                                                                                             |

|   | Point to IDMA channel 1's base                                                                           |

|   | RET B3 ; return; also protect from interrupts                                                            |

|   | MVKL IDMA1_SOURCE, A7                                                                                    |

|   | MVKH IDMA1_SOURCE, A7                                                                                    |

| ; | Write second argument to "source" register                                                               |

|   | STW B4, *A7++(IDMA1_DEST - IDMA1_SOURCE)                                                                 |

| ; | Write first argument to "destination" register                                                           |

|   | STW A4, *A7++(IDMA1_COUNT - IDMA1_DEST)                                                                  |

| ; | Write last argument to "count" register.                                                                 |

|   | EXTU A6, 18, 16, A6 ; truncate word count to 14 bits                                                     |

|   | STW A6, *A7                                                                                              |

|   | .endasmfunc                                                                                              |

|   | ;; Watte: Wait for IDMA "pond" or "agtu" alot to free up                                                 |

|   | ;; IDMA1_WAIT: Wait for IDMA "pend" or "actv" slot to free up.<br>;;                                     |

|   | ; USAGE                                                                                                  |

|   | ; idmal_wait(IDMA_PEND) Waits for just PEND to be 0                                                      |

|   | ;; idmal_wait(IDMA_ACTV) Waits for ACTV (and PEND) to be 0                                               |

|   |                                                                                                          |

| ; | ;; NOTE                                                                                                  |

|   | ;; IDMA_PEND = 2                                                                                         |

|   | ;; IDMA_ACTV = 3                                                                                         |

|   |                                                                                                          |

| ; | ;;global _idmal_wait                                                                                     |

|   | .asmfunc                                                                                                 |

| - | _idma1_wait:                                                                                             |

|   | MVKL IDMA1_STATUS, A6                                                                                    |

|   | MVKH IDMA1_STATUS, A6                                                                                    |

|   | WVK 1, A0                                                                                                |

| 1 | Loop?:<br>[ A0] LDW *A6, A0                                                                              |

| 1 | [ AU] LDW *A6, AU<br>  [ A0] BNOP.1 loop?, 4                                                             |

| ' | The 'AND' below is safe because IDMA never returns 10b in 2 LSBs                                         |

| , | AND.L A4, A0, A0                                                                                         |

|   | RETNOP B3, 5                                                                                             |

|   | .endasmfunc                                                                                              |

|   |                                                                                                          |

| ; | ;; ====================================                                                                  |

# Advisory 2.1.6 SPLOOP CPU Cross-Path Stall

Revision(s) Affected: 2.1 and earlier

**Details:**

If the following three rules are met, a stall is seen when an SPKERNEL instruction is executed.

- 1. **Cross-path instruction rule:** An instruction reading a register via the cross path in the first cycle after SPKERNEL instruction.

- 2. **Data dependence rule:** An instruction in the SPLOOP body that writes to the above cross-path read register. This instruction can be anywhere in the SPLOOP body.

- Functional unit rule: No instruction in parallel with the SPKERNEL instruction that uses the same functional unit as the cross-path read instruction mentioned in rule 1 above.

This results in a one CPU cycle stall for each iteration of the loop. The following are three examples of code that are affected by this issue:

#### Example 1

```

SPLOOP 1

MV .S1 A0, A1 ;stalls every iteration due to MV after loop

SPKERNEL

MV .S2X A1, B2

```

#### Example 2

```

PLOOP 14

MV .S1 A0, A1 ;stalls every iteration due to MV after loop

NOP 9

NOP 9

NOP 9

NOP 9

SPKERNEL

MV .S2X A1, B2

```

# Example 3

SMV .S1 A0, A1 ;stalls every iteration due to MV after loop SPKERNEL ||NEG .L2 B3, B4 ;Qualifies for rule 3, functional unit rule MV .S2X A1, B2

#### The following three examples are not affected by this issue:

#### Example 1

;No stalls: No cross path in instruction after SPKERNEL SPLOOP 1 MV .S1 A0, A1 SPKERNEL MV .S1 A1, A2

#### Example 2

;No stalls: A1 not written to in loop body SPLOOP 1 MV .S1 A0, A2 SPKERNEL MV .S2X A1, B2

#### Example 3

;No stalls: Instruction in parallel with SPKERNEL prevents bug since ;it's in the same unit as the instruction that uses the cross-path. SPLOOP 1 MV .S1 A0, A1 SPKERNEL ||NEG .S2 B3, B4 ;masks the bug MV .S2X A1, B2

| www.ti.com     | Silicon Revision 2.1 Usage Notes and Known Design Exceptions to Functional Specifications                                                                                                                                                                                                        |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Workaround(s): | The way SPLOOP code is scheduled is controlled by the compiler. Therefore, there are no direct workarounds for non-assembly source code. There are new revisions of the latest compilers that ensure that these three conditions are never met. The following compiler releases include the fix: |

|                | • 6.0.25 or later                                                                                                                                                                                                                                                                                |

|                | • 6.1.15 or later                                                                                                                                                                                                                                                                                |

|                | • 7.0.2 or later                                                                                                                                                                                                                                                                                 |

- 7.1.0B2 or later

- 7.2.0A or later.

# Advisory 2.1.7 DMA Corruption of L1D\$ Allocation

Revision(s) Affected: 2.1

# Details:

Under a specific set of circumstances, a snoop-write updates unintended data being allocated into L1D\$ from external, cacheable memory. This can lead directly to program misbehavior. If that line is then modified by CPU accesses, a subsequent victim writeback from L1D could commit this corrupted line to lower levels of memory. The key requirements for this issue are:

- Two clean lines in L1D\$.

- This means that a CPU has read two L2 or external, cacheable addresses and has not modified them.

- One more allocated line in L1D\$ that can be clean or dirty.

- Dirty means that a CPU has read and written to any L2 or external, cacheable address.

- Two more parallel CPU reads (occurring in the same CPU cycle).

- One of the reads must create an L2\$ hit (implying an external, cacheable address) and must be a set match to one of the clean lines already in L1D\$.

- The other can be from an L2 SRAM address or an external, cacheable address and must be a set match to the L1D\$ cache line mentioned above as clean or dirty.

- Two DMA writes to buffers in L2 SRAM that are a set match to the two clean lines in L1D\$.

# NOTE:

- For information on L1D cache coherence protocol, see section 3.3.6, Cache Coherence Protocol, in the C64x+ DSP Megamodule Reference Guide (SPRU871).

- The DMA in the following description refers to all non-CPU requestors. This includes IDMA, EDMA, and any other master in the system.

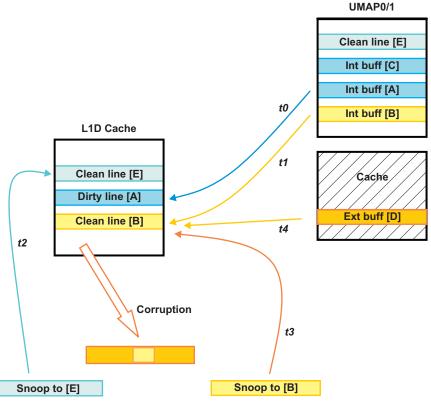

Under a specific set of circumstances listed below, a snoop-write results in data corruption of L1D\$. The issue occurs when there is a DMA to L2 for one of the allocated (clean) lines that is also in the process of being replaced by an allocation from external, cacheable memory (implying there was a set match between the two); this is along with another allocation and a DMA to the other allocated (clean) line. L2 sends the DMA requests as snoop-writes to the L1D cache. When the error occurs, the line the second snoop-write was destined for has already been replaced by the allocation from external, cacheable memory. The logic to kill the snoop-write did not get sensitized and the snoop-write ends up corrupting the line that was allocated. Subsequent writes to the corrupted line cause this to get committed to lower levels of memory.

The prerequisite before the window where the issue occurs is:

- The CPU reads two L2 locations that are not a set match to each other and have not been modified since then (CPU/DMA has not written to it). For a description on how to determine if you have a set match or not, see below.

- These are now two separate 64B cache lines allocated and clean in L1D (referred to here as Cache Lines B and E).

- The CPU reads another L2 location that is not a set match to Cache Lines B and E. It does not matter whether this particular cache line is modified or not before the issue window arrives.

- Because of this, another 64B cache line is allocated in L1D as clean or dirty (referred to here as Cache Line A).

- Note that both ways for this particular set must be occupied. It may require more than one read to this particular cache set.

# How to determine if two addresses are a set match:

Determining if two addresses are a set match can be done by comparing certain bits of two addresses. The mapping of an address to a location in L1D cache is shown in Figure 5.

The value X is determined by how large the L1D cache is in the particular application (see Table 10).

# Figure 5. L1D Cache Address Mapping

| AMOUNT OF L1D CACHE | X BIT POSITION |

|---------------------|----------------|

| 0KB                 | N/A            |

| 4KB                 | 10             |

| 8KB                 | 11             |

| 16KB                | 12             |

| 32KB                | 13             |

# Table 10. Value of X for L1D Cache

If you use the default configuration, 32KB, as an example, bits [13:6] are a set match if they are identical in two different addresses. Some examples of set matches are shown below:

- 0x0080 2A80 000000010000000010101010000000

- 0x8000 2A80 100000010000000010101010000000

- 0x0080 2A8A 000000010000000010101010001010

The following steps must all occur in a very tight window to see the issue:

- 1. The DMA writes to Cache Line E. This means that it is not necessarily the same exact address, but within the same 64B cache line.

- As a result, a snoop- write request is generated.

- 2. The DMA writes to Cache Line B. This means that it is not necessarily the same exact address, but within the same 64B cache line.

- As a result, a snoop-write request is generated but not immediately issued as it is blocked by the snoop-write issued in the previous Step 1.

- Once the snoop-write from Step 1 is complete, this snoop-write is processed.

- 3. The CPU reads from any address in external, cacheable memory that is a set match to Cache Line B. This must also create an L2\$ hit (referred to here as Cache Line D).

- This results in a cache miss from the CPU and sends a read request to L2 cache for the line.

- Assuming this was also mapped to the same way as Cache Line B, this results in a replacement of Cache Line B since it was clean in L1D\$.