## **TI Designs** 700–2700-MHz Dual-Channel Receiver With 16-Bit ADC and 100 MHz of IF Bandwidth

# **W** Texas Instruments

## **TI Designs**

TI Designs provide the foundation that you need including methodology, testing, and design files to guickly evaluate and customize the system. TI Designs help you accelerate your time to market.

#### **Design Resources**

| TIDA-00360    | Tool Folder Containing Design Files |

|---------------|-------------------------------------|

| TSW16DX370EVM | Product Folder                      |

| TRF37B32      | Product Folder                      |

| LMH6521       | Product Folder                      |

| ADC16DX370    | Product Folder                      |

| LMK04828      | Product Folder                      |

| LMX2581       | Product Folder                      |

#### **Design Features**

- Implements a RF Super-Heterodyne Receiver Subsystem with 700-2700-MHz Input Range, Wide 100-MHz IF Bandwidth and 16-Bit ADC

- Evaluate this Reference Design Effortlessly With • Supported Data Capture and Analysis Tools

- This Reference Design is Tested and Includes an Evaluation Module (EVM), Configuration Software, and User's Guide

#### **Featured Applications**

Accelerate the Design Time of a Wireless Communications, Software-Defined Radio, Military, or Test and Measurement Application With a Proven IF Signal Chain

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

All trademarks are the property of their respective owners.

A

2

#### www.ti.com

#### 1 Introduction

**Block Diagram**

The increasing demand on wireless networks to provide faster data links to customers has driven transceiver hardware to increasingly demanding performance with enough bandwidth to support the largest standardized multi-carrier frequency bands (with band aggregation in some cases) and enough receiver sensitivity and dynamic range to function in the presence of the strong blocking signals common in busy environments.

Receivers in these difficult applications have pushed beyond the 75-MHz node and are on to 100-MHz nodes and beyond. The large bandwidth demands frequency-flexible mixers, high sampling rates, and good distortion performance through the whole signal chain up to higher intermediate frequencies (IF). Increased data rate also requires a standard serialized data interface to minimize the data bus real estate.

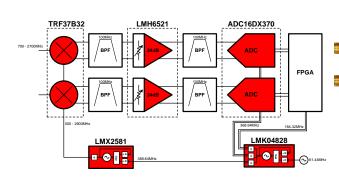

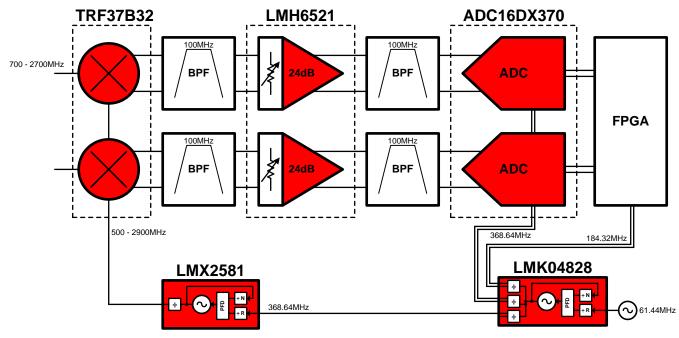

This TI Design describes a RF receiver subsystem reference design (TSW16DX370EVM) including a down-converting mixer, digitally-controlled variable gain amplifier (DVGA), high speed pipelined analog-to-digital converter (ADC), Local Oscillator (LO) RF synthesizer, and jitter-cleaning clock generator. The dual-signal path subsystem also connects to a field programmable gate array (FPGA) across a JESD204B standard interface. The frequency plan of the design accommodates a wide RF input range from 700–2700-MHz and more than 100-MHz of bandwidth with an intermediate frequency of 276-MHz. Figure 1 shows the block diagram.

Figure 1. TSW16DX370EVM Block Diagram

www.ti.com

#### **3 Block Descriptions**

The TRF37B32 is a dual-channel, down convert receive mixer. It provides high-linearity over wide RF and IF bandwidths while also consuming low power. The device covers an extremely wide frequency band and can operate with either low side injection (LSI) or high side injection (HSI). The device consists of a passive mixer core buffered by an LO amplifier and a high-linearity IF amplifier. There is an on-chip LDO to regulate VCC to the voltages required for the small-geometry SiGe BiCMOS components. The single-ended RF and LO inputs each have a wideband internal balun. Table 1 shows the performance metrics for this device.

| BLOCK                 | FEATURE                    | VALUE                        | CONDITIONS            |

|-----------------------|----------------------------|------------------------------|-----------------------|

|                       | Gain                       | 10 dB                        |                       |

|                       | NF                         | 9.5 dB                       |                       |

|                       | IIP3                       | 34 dBm                       | - RF Input = 1800 MHz |

| Down-conversion mixer | P1dB                       | 10.5 dB                      |                       |

| (TRF37B32)            | RF input frequency range   | 700–2700 MHz                 |                       |

|                       | LO input frequency range   | 500–2900 MHz                 |                       |

|                       | IF output frequency range  | 30–600 MHz                   |                       |

|                       | Input and output impedance | 50 $\Omega$ and 200 $\Omega$ |                       |

#### Table 1. TRF37B32 Device Performance

4

The LMH6521 is a dual, digitally-controlled variable gain amplifier (DVGA) designed for narrowband or wideband, intermediate-frequency sampling applications. The LMH6521 is optimized for accurate 0.5-dB gain steps with exceptional gain and phase matching between channels combined with low distortion products. The gain matching error is less than  $\pm 0.05$  dB and the phase matching error is less than  $\pm 0.5$ degrees over the entire attenuation range. The LMH6521 is ideal for driving ADC converters where high linearity is necessary. Table 2 shows the performance metrics for this device.

| BLOCK          | FEATURE                    | VALUE          | CONDITIONS                                      |

|----------------|----------------------------|----------------|-------------------------------------------------|

|                | Max voltage gain           | 24 dB          |                                                 |

|                | Min voltage gain           | –7.5 dB        |                                                 |

|                | Gain step                  | 0.5 dB         |                                                 |

| DVGA (LMH6521) | NF                         | 7.3 dB         | Attenuation = 0 dB 200-Ω<br>source              |

|                | OIP3                       | 43 dBm         | Input frequency = 276 MHz                       |

|                | P1dB                       | 17 dBm         | Input power = 4 dBm/tone<br>Attenuation = 16 dB |

|                | Input and output impedance | 200 Ω and 20 Ω | Low impedance output                            |

#### Table 2. LMH6521 Device Performance

The ADC16DX370 device is a monolithic, dual-channel, high performance ADC converter capable of converting analog input signals into 16-bit digital words with a sampling rate of 370-million samples per second (MSPS). This converter uses a differential pipelined architecture with integrated input buffer to provide excellent dynamic performance while maintaining low power consumption. The output digital data is provided through a JESD204B subclass 1 interface at up to 7.4 Gb/s. Table 3 shows the performance metrics for this device.

#### Table 3. ADC16DX370 Device Performance

| BLOCK            | FEATURE                | VALUE          | CONDITIONS                             |

|------------------|------------------------|----------------|----------------------------------------|

|                  | Sampling rate          | 368.64 MSPS    |                                        |

|                  | Input BW               | > 800 MHz      |                                        |

|                  |                        | –152.7 dBFS/Hz | Small signal                           |

|                  | Noise spectral density | –151.7 dBFS/Hz | Input = -3 dBFS, 325 MHz               |

| ADC (ADC16DX370) | SFDR                   | -85 dBFS       | Input = -3 dBFS, 325 MHz               |

|                  | IMD3                   | -92 dBc        | Input = -10 dBFS/tone,<br>145/155 MHz  |

|                  | Input impedance        | 100 Ω          | Includes external 200-Ω<br>termination |

|                  | Output data lane rate  | 7.4 Gb/s       | One lane per channel                   |

The LMK04828 is a dual phase-locked loop (PLL) clock conditioner, multiplier, and distributer with JEDEC JESD204B support. The 14 clock outputs can be configured to drive seven JESD204B converters or other logic devices using device and SYSREF clocks. The high phase noise performance combined with features like the ability to trade off between power or performance, dual VCOs, dynamic digital delay, holdover, and glitch-less analog delay make the LMK04828 ideal for providing flexible high performance clocking trees. Table 4 shows the performance metrics for this device.

| BLOCK                       | FEATURE                          | VALUE         | CONDITIONS                                                      |

|-----------------------------|----------------------------------|---------------|-----------------------------------------------------------------|

|                             | Input reference frequency        | 61.44 MHz     |                                                                 |

|                             |                                  |               | LVPECL16, 240 Ω, VCO0<br>Freq = 245.76 MHz (example)<br>Offset: |

| System clock PLL (LMK04828) | Clock output phase noise         | –124.3 dBc/Hz | 1 kHz                                                           |

|                             |                                  | –134.7 dBc/Hz | 10 kHz                                                          |

|                             |                                  | –136.5 dBc/Hz | 100 kHz                                                         |

|                             |                                  | –148.4 dBc/Hz | 1 MHz                                                           |

|                             |                                  | –160.8 dBc/Hz | 10 MHz                                                          |

|                             | Total jitter, ADC sampling clock | 93 fs         | LVPECL16, BW = 12 kHz to 20 MHz                                 |

#### Table 4. LMK04828 Device Performance

The LMX2581 is a low noise wideband frequency synthesizer that integrates a delta-sigma fractional N PLL, multiple core VCO, programmable output divider, and two different output buffers. The VCO frequency range is from 1880 through 3760 MHz and can be sent directly to the output buffers or divided down by even values from 2 to 38. Each buffer is capable of output power from –3- to 12-dBm at 2700 MHz. Integrated LDOs are used for superior noise immunity and consistent performance. Table 5 shows the performance metrics for this device.

#### Table 5. LMX2581 Device Performance

| BLOCK                                 | FEATURE                   | VALUE         | CONDITIONS     |

|---------------------------------------|---------------------------|---------------|----------------|

| Fractional-N synthesizer<br>(LMX2581) | Input reference frequency | 368.64 MHz    |                |

|                                       |                           |               | Freq = 2.7 GHz |

|                                       |                           | -81.7 dBc/Hz  | 10 kHz         |

|                                       | Internal VCO phase noise  | –112.2 dBc/Hz | 100 kHz        |

|                                       |                           | –136.0 dBc/Hz | 1 MHz          |

|                                       |                           | –153.1 dBc/Hz | 10 MHz         |

The two IF Bandpass Filters are 10-pole, maximally flat designs with a standard LC architecture. Both filters target a -1-dB, 100-MHz bandwidth centered at 276 MHz. The first filter in the signal path is designed for a 200- $\Omega$  source and load, whereas the second filter is designed for 100  $\Omega$ . The filter footprint is designed to be compact and flexible to support custom filter designs. Table 6 shows the performance metrics for these filters.

#### Table 6. IF Bandpass Filter Performance

| BLOCK              | FEATURE              | VALUE     | CONDITIONS      |

|--------------------|----------------------|-----------|-----------------|

|                    | Bandwidth            | 100 MHz   |                 |

| IF bandpass filter | Passband flatness    | 1 dB      |                 |

|                    | Center frequency     | 276 MHz   |                 |

|                    | Stopband attenuation | < -22 dBc | Input = 450 MHz |

#### 4 Frequency Plan

The sub-system is synchronous to a 61.44-MHz crystal oscillator module reference clock provided on the board. From the reference clock, the LMK04828 generates the 368.64-MHz ADC sampling clock, 184.32-MHz reference for the FPGA, 11.52-MHz SYSREF clock for the FPGA, and 368.64-MHz reference for the LMX2581. The LMX2581 then uses the reference to generate a flexible LO frequency from 500 to 2600 MHz.

| REFERENCE                      | FREQUENCY    | NOTES                                              |

|--------------------------------|--------------|----------------------------------------------------|

| System reference               | 61.44 MHz    | Onboard XO                                         |

| ADC conversion clock frequency | 368.64 MHz   | Equal to sampling rate                             |

| FPGA SERDES reference clock    | 184.32 MHz   | Must be ≤ 250 MHz                                  |

| FPGA SYSREF clock              | 11.52 MHz    | Equal to 368.64 / 32                               |

| LO reference clock             | 368.64 MHz   | Equal to ADC sampling rate to prevent system spurs |

| LO frequency                   | 500–3800 MHz | Generated by Fractional-N synthesizer              |

#### Table 7. Frequency Plan Summary

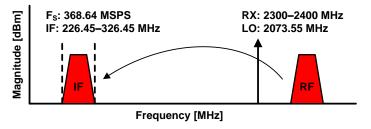

The 368.64-MSPS ADC sampling clock provides 184.32 MHz of un-aliased bandwidth, which can support up to an approximate 130 MHz of signal bandwidth depending on the desired system performance and IF filter complexity. This design utilizes LC bandpass filters (BPF) centered in the middle of the second Nyquist zone at 276 MHz that have a 100-MHz, -1-dB bandwidth. Figure 2 shows an example where the receiver is mixing the standard cellular 3GPP band 40 from 2300–2400 MHz down to the intermediate frequency with an LO frequency of 2073.55 MHz.

Figure 2. Frequency Plan for 3GPP Band 40

This centering of the IF frequency in the second Nyquist zone allows simple IF to complex digital baseband conversion. The signal band occupies most of the Nyquist zone, so frequency planning around harmonics is not an option. The super-heterodyne architecture does allow for the filtering of harmonics and IMD2 products created by the device prior to the ADC. This filtering is in contrast to a direct conversion (zero IF) receiver, which cannot filter out harmonic content before sampling.

## 5 Measured Signal Path Performance

## 5.1 Bench Measurement Setup

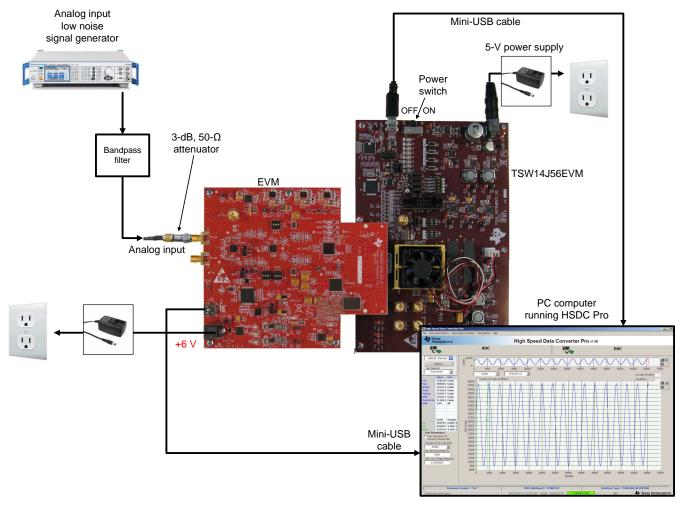

Figure 3 shows how the reference design was evaluated in the bench setup. A low-noise spectrum analyzer is used to generate a 1-tone or 2-tone signal (using a second generator and power combiner in the latter case). A signal path filter is optional for signal generators with good noise performance because the reference design achieves enough anti-aliasing protection to eliminate signal generator harmonics. A small signal path attenuator is used to improve the gain flatness across the frequency when connecting the input cable transmission line to the input of the TRF37B32 device. No additional clock sources are required for testing because the EVM has an onboard reference clock.

The TSW16DX370EVM connects to the TSW14J56EVM data capture platform and uploads data to a computer that is running the High Speed Data Converter Pro Software (1), which analyzes the data.

Figure 3. Bench Evaluation Setup

#### www.ti.com

#### 5.2 Noise and Distortion

The noise and distortion performance closely matches the expected signal path performance. Table 8 shows the summary of measured performance.

| PARAMETER   | CONDITION                                      | RESULT        | NOTES                                  |  |

|-------------|------------------------------------------------|---------------|----------------------------------------|--|

| Gain        | DVGA att. 0 dB                                 | 28.7 dB       |                                        |  |

| Gain        | DVGA att. 24 dB                                | 4.7 dB        |                                        |  |

|             | Fin = 1710/1700, -9 dBFS/tone, DVGA att. 0 dB  | 36.1 dBm      | IMD = -79 dBc, IIP3 = 7.4 dBm          |  |

| OIP3        | Fin = 1710/1700, -9 dBFS/tone, DVGA att. 24 dB | 30 dBm        | IMD = -66.7 dBc, IIP3 approx. 25.3 dBm |  |

| OIF3        | Fin = 1790/1800, -9 dBFS/tone, DVGA att. 0 dB  | 35.2 dBm      | IMD = -77.4 dBc, IIP3 approx. 5.5 dBm  |  |

|             | Fin = 1790/1800, -9 dBFS/tone, DVGA att. 24 dB | 27.3 dBm      | IMD = -61.4 dBc, IIP3 approx. 22.6 dBm |  |

| NF          | DVGA att. 0 dB                                 | 11 dB         |                                        |  |

| INF         | DVGA att. 24 dB                                | 25.9 dB       |                                        |  |

|             | 100 kHz                                        | -114.4 dBc/Hz |                                        |  |

|             | 200 kHz                                        | -121.4 dBc/Hz |                                        |  |

|             | 500 kHz                                        | –128.9 dBc/Hz | DVGA att. 24 dB. frequencies above     |  |

| Phase noise | 1 MHz                                          | -136.4 dBc/Hz | 1 MHz influenced significantly by      |  |

|             | 2 MHz                                          | -140.4 dBc/Hz | broadband noise of ADC and LMH.        |  |

|             | 5 MHz                                          | -143.4 dBc/Hz |                                        |  |

|             | 10 MHz                                         | -144.4 dBc/Hz |                                        |  |

#### **Table 8. System Performance Summary**

#### 5.3 Selectivity

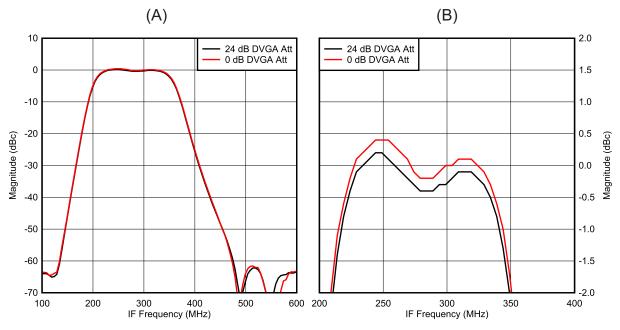

The selectivity of the sub-system is set by two 10-pole LC bandpass filters, one filter following the mixer and the other filter following the DVGA while acting as the noise anti-aliasing filter. The first filter is designed for a 200- $\Omega$  source and load. The second filter is designed for a 100- $\Omega$  source and load, too; however, both filters are designed for a similar frequency response. Figure 4 shows the measured composite total sensitivity of both filters.

Figure 4. TSW16DX370EVM Selectivity Ch.A—Total Selectivity of IF Sub-System (A) and (B)

www.ti.com

#### 6 Design Files

#### 6.1 Schematics

To download the schematics, see the design files at TIDA-00360.

## 6.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-00360.

## 6.3 Layer Plots

To download the layer plots, see the design files at TIDA-00360.

#### 6.4 Cadence/Allegro Files

To download the Cadence/Allegro files, see the design files at TIDA-00360.

#### 6.5 Gerber Files

To download the Gerber files, see the design files at TIDA-00360.

## 6.6 Assembly Drawings

To download the assembly drawings, see the design files at <u>TIDA-00360</u>.

#### 6.7 Software Files

To download the software files, visit the TSW16DX370EVM <u>product page</u> and the High Speed Data Converter Pro Software <u>product page</u>.

#### **IMPORTANT NOTICE FOR TI REFERENCE DESIGNS**

Texas Instruments Incorporated ("TI") reference designs are solely intended to assist designers ("Buyers") who are developing systems that incorporate TI semiconductor products (also referred to herein as "components"). Buyer understands and agrees that Buyer remains responsible for using its independent analysis, evaluation and judgment in designing Buyer's systems and products.

TI reference designs have been created using standard laboratory conditions and engineering practices. **TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design.** TI may make corrections, enhancements, improvements and other changes to its reference designs.

Buyers are authorized to use TI reference designs with the TI component(s) identified in each particular reference design and to modify the reference design in the development of their end products. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY THIRD PARTY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT, IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS ARE PROVIDED "AS IS". TI MAKES NO WARRANTIES OR REPRESENTATIONS WITH REGARD TO THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, EXPRESS, IMPLIED OR STATUTORY, INCLUDING ACCURACY OR COMPLETENESS. TI DISCLAIMS ANY WARRANTY OF TITLE AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, QUIET ENJOYMENT, QUIET POSSESSION, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS WITH REGARD TO TI REFERENCE DESIGNS OR USE THEREOF. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY BUYERS AGAINST ANY THIRD PARTY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON A COMBINATION OF COMPONENTS PROVIDED IN A TI REFERENCE DESIGN. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, SPECIAL, INCIDENTAL, CONSEQUENTIAL OR INDIRECT DAMAGES, HOWEVER CAUSED, ON ANY THEORY OF LIABILITY AND WHETHER OR NOT TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES, ARISING IN ANY WAY OUT OF TI REFERENCE DESIGNS OR BUYER'S USE OF TI REFERENCE DESIGNS.

TI reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques for TI components are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

Reproduction of significant portions of TI information in TI data books, data sheets or reference designs is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards that anticipate dangerous failures, monitor failures and their consequences, lessen the likelihood of dangerous failures and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in Buyer's safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed an agreement specifically governing such use.

Only those TI components that TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components that have **not** been so designated is solely at Buyer's risk, and Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2015, Texas Instruments Incorporated