TI 高精度设计: 经验证的设计 针对最低功耗进行优化的 18 位,每秒百万次采样 (MSPS) 数据 采集 (DAQ) 块

### TI 高精度设计

TI 高精度设计是由 TI 模拟产品专家创建的模拟解决方案。 经验证的设计提供理论、元件选择、仿真、完整的印刷电路板 (PCB) 电路原理图 & 布局布线、物料清单和有用电路的测试性能。 还讨论了有助于满足替代设计要求的修改电路。

#### 设计资源

| 设计存档     | 全部设计文件     |

|----------|------------|

| TINA-TI™ | SPICE 仿真工具 |

| ADS8881  | 产品文件夹      |

| OPA2320  | 产品文件夹      |

| REF5045  | 产品文件夹      |

| OPA2333  | 产品文件夹      |

| THS4281  | 产品文件夹      |

|          |            |

#### 电路描述

这个电路描述了一个数据采集 (DAQ) 块,此采集块包含一个 18 位逐次逼近型 (SAR) 模数转换器 (ADC); ADC 输入的前端驱动电路; ADC 基准输入的一个外部基准和驱动电路。这个设计已经被优化,以便使用一个频率为 10kHz 的满量程正弦波输入信号在功耗最低时,实现良好的动态性能。 差分输入信号依次通过由低噪声、低功耗放大器实现的单位增益缓冲器和低通 RC 滤波器,然后进入 ADC。

请咨询模拟产品专家 WEBENCH® C设计中心 TI 高精度设计库

## 1 设计汇总

TI 高精度设计的主要目标是设计一个优化的数据采集系统,此系统使用 1MSPS 的 18 位 ADS8881,针对 频率为 10kHz 的满量程正弦输入信号,可用最低功耗实现出色的交流性能。针对这个块的设计要求是:

TINA-TI is a trademark of Texas Instruments. WEBENCH is a registered trademark of Texas Instruments.

设计汇总 www.ti.com.cn

- 系统电源电压: 5V 直流

- ADC 电源电压: 3.3V 直流

- ADC 采样速率: 1MSPS

- ADC 基准电压 (V<sub>REF</sub>): 4.5V 直流

- ADC 输入信号: 幅度 V<sub>PK</sub>=4.3V (-0.4dBFS 以避免削波), 频率 f<sub>IN</sub>= 10kHz 的差分正弦信号输入到ADC

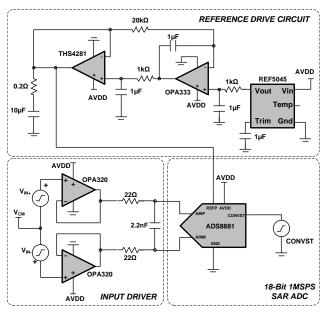

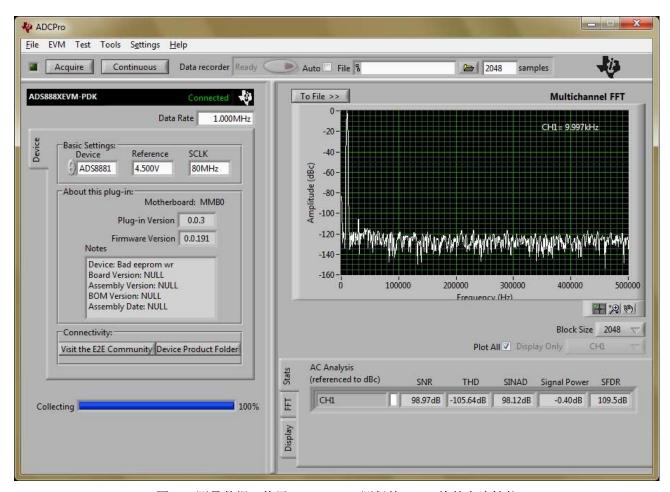

表 1中总结了设计目标和性能。 如图 1中所示,使用 TI 的 ADCPro™ 工具测量的该 DAQ 块的交流性能。

表 1. 设计目标、仿真和测量性能之间的比较

| 参数               | 目标值    | 仿真值    | 测量值     |

|------------------|--------|--------|---------|

| 总功率 (mW)         | < 35   | 不可用(1) | 28.61   |

| 信噪比 - SNR(dB)    | ≥ 98   | 不可用(2) | 98.97   |

| 总谐波失真 - THD (dB) | ≤ -105 | 不可用(2) | -105.64 |

| 信纳比 - SINAD (dB) | ≥ 98   | 不可用(2) | 98.12   |

| 有效位数 ENOB        | 16     | 不可用(2) | 16.01   |

- (1) SAR ADC 的功耗未在 TINA-TI™ 模型中准确地建模

- <sup>(2)</sup> 因为 TINA-TI™ 的 SAR ADC 模型中不包含噪声和失真信息,ADC 动态性能不能用 TINA-TI™ 仿真。

图 1. 测量数据 - 使用 ADCPro™ 测得的 DAQ 块的交流性能

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

www.ti.com.cn 操作理论

## 2 操作理论

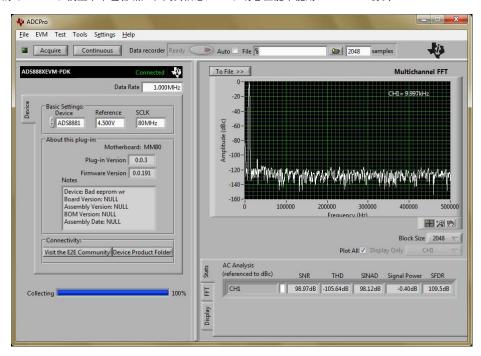

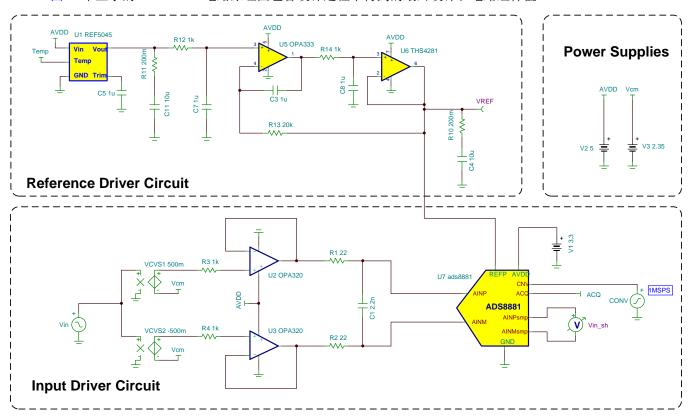

实现高分辨率 SAR ADC 性能的两个主要设计考虑是输入驱动电路和基准驱动电路。图 2显示了一个包含有关键模拟电路的方框图,应该仔细地设计此电路以实现一个 18 位 1MSPS DAQ 块的设计规格。 这个图包括按照设计优先级排序的每个模拟电路的最重要的技术规格。 由于每个电路模块的设计标准取决于所期望的 ADC 性能以及输入信号类型,所以这很重要。

这个设计使用一个数据吞吐量为 1MSPS 的 18 位 SAR ADC,并针对频率为 10kHz 的满量程差分正弦输入信号进行了优化。 为了实现本设计的性能指标,应该遵循下面的设计步骤:

- 步骤 1:选择一个具有充足小信号带宽和低功耗的合适放大器,可以大大降低 ADC 的噪声和失真性能。

- 步骤 2:设计一个低通抗混叠 RC 滤波器来限制前端电路的噪声,同时注意驱动放大器的稳定性。

- 步骤 3:设计一个高精度基准驱动电路,提供低失调、低漂移和低噪声的基准电压值 V<sub>REF</sub>。

图 2. 方框图强调了本 DAQ 块的主要设计标准

操作理论 www.ti.com.cn

## 2.1 理解 ADC 动态性能

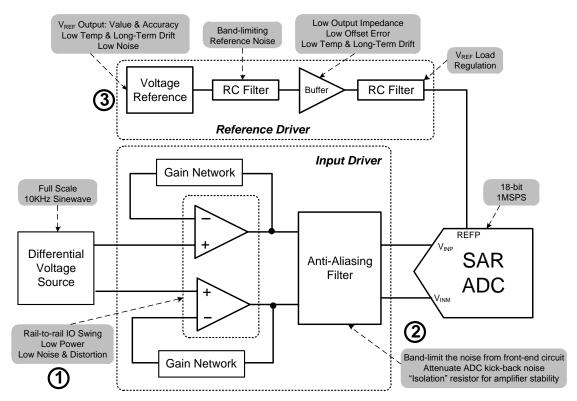

在这个 TI 高精度设计中,主要针对一个纯粹的正弦输入到数据采集模块、实现输出数据良好的动态性能,同时大大降低系统的总体功耗。 这个设计考虑的主要交流技术规格是 THD,SNR,SINAD 和 ENOB。 本质上,所有这些参数都是基于快速傅里叶变换 (FFT) 分析利用不同的方式来量化 ADC 的噪声和失真性能。图 3中显示了一个 ADC 的典型 FFT 曲线图。

图 3. 针对一个数据采集系统的典型 FFT 曲线图

总谐波失真(THD) 的定义是全部谐波分量(通常使用 9 个谐波)的和方根 (rss) 与基频信号功率的比值。 通常指定一个输入信号接近满量程 (FS),但是在本设计中,输入保持在 FS 下方 0.4dB 以防止模拟前端的削波。 如果输入信号的均方根 (rms) 值用  $V_{SIG\_RMS}$ 表示,并且  $n^{th}$ 谐波中的功率用  $V_{HAR\_n\_RMS}$ 表示,那么总谐波失真 ( $V_{HAR\_TOT\_RMS}$ ) 和 THD 可表示为:

$$V_{HAR\_TOT\_RMS} = \sqrt{V_{HAR\_1\_RMS}^2 + V_{HAR\_2\_RMS}^2 + \dots + V_{HAR\_9\_RMS}^2}$$

(1)

$$THD = \frac{V_{SIG\_RMS}}{V_{HAR\_TOT\_RMS}}$$

(2)

信噪比(SNR) 体现了系统的总体噪声水平。 数据采集系统的总体噪声是前端放大器噪声 ( $V_{n\_AMP\_RMS}$ ) 和 ADC 噪声 ( $n\_ADC\_RMS$ ) 的rss值。 ADC 噪声包括量化噪声以及 ADC 内部电路引入的噪声或 ADC的输入引入噪声。来自这些噪声源的总噪声,用  $V_{n\_TOT\_RMS}$ 表示,折算到 ADC 的输入端,用于计算系统总体的 SNR (SNR $_{SYS}$ )。

$$V_{n\_TOT\_RMS} = \sqrt{V_{n\_AMP\_RMS}^2 + V_{n\_ADC\_RMS}^2}$$

(3)

$$SNR_{SYS} = \frac{V_{SIG\_RMS}}{V_{n\_TOT\_RMS}}$$

(4)

www.ti.com.cn 操作理论

信纳比(SINAD) 结合了谐波失真和噪声的影响,以提供一个系统总体动态性能的累积测量。

$$SINAD_{SYS} = \frac{\sqrt{V_{n_{TOT_{RMS}}}^2 + V_{HAR_{TOT_{RMS}}}^2}}{\sqrt{V_{n_{TOT_{RMS}}}^2 + V_{HAR_{TOT_{RMS}}}^2}}$$

(5)

*有效位数*(ENOB) 是对于一个 ADC 数字量化的有效测量,定义为高于噪底的位数。 对于一个只有量化噪声的理想 N 位 ADC, SNR(单位为 dB)可被计算为:

$$SNR = 6.02 \times N + 1.76$$

(6)

$$\Rightarrow N = \frac{SNR - 1.76}{6.02} \tag{7}$$

可用这个公式来定义一个系统的 ENOB,如公式 8中所示。 如果用 SINAD<sub>sys</sub>替代 SNR, 那么该ENOB 可以更好地体现数据采集块的总体动态性能。

$$ENOB = \frac{SINAD_{SYS} - 1.76}{6.02} \tag{8}$$

虽然 ENOB 是 ADC 动态性能的良好体现,但是它没有描述不同操作频率和输入信号时,转换器的整体性能。此外,ENOB 不包括诸如 offset error 和 gain error 等 ADC 直流指标。 因此,根据使用 ADC 的应用,其他转换器技术规格也很重要。

#### 2.2 输入驱动电路设计

## 2.2.1 输入放大器设计

2.1 节中解释的分析很明确的表示出,为了大大增加高精度 ADC 的性能,将来自前端电路的噪声和失真保持在极低的水平十分重要。 然而,由于这个 TI Design 的主要目标是尽可能降低系统的功耗,首先为输入驱动电路选择一个具有足够低噪声和失真的低功耗放大器变得极其重要。 下面将会解释前端电路噪声对总体系统性能的影响。

**系统噪声分析:** 这个部分分析前端电路的噪声对一个高精度 ADC 的总体动态性能的影响。 出于简化的目的,以单端输入级进行分析(请参考图 4),随后,同样的概念被扩展至差分输入 ADC。

图 4. 单端 ADC 输入级的经简化电路原理图

在这个电路原理图中,RC 滤波器的 3dB 带宽,表示为  $BW_{RC}$ ,对于频带限制来自放大器的宽频带噪声很关键。 由于输入驱动器被配置为单位增益放大器,只有来自放大器的噪声对前端噪声产生影响。 放大器噪声被大体上分为低频闪烁或 1/f 噪声(0.1Hz 至 10Hz)和更高频宽带噪声,宽带噪声通常定义为宽频率范围内的一个噪声频谱密度  $(e_{n,RMS})$ 。

操作理论 www.ti.com.cn

放大器的噪声增益表示为  $N_G$ 。 那么,RC 滤波器的带宽能够限制放大器宽带噪声  $(V_{n\_RMS})$  折算到 ADC 输入端的噪声,如公式 9中所示:

$$V_{n\_RMS} = N_G \times e_{n\_RMS} \times \sqrt{\frac{\pi}{2}} \times BW_{RC}$$

(9)

放大器的闪烁噪声被指定为峰峰值噪声 ( $V_{1f\_AMP\_PP}$ ),这个值应该被首先转换为 rms 噪声,之后与噪声增益  $N_G$ 相乘,以计算闪烁噪声的影响。

$$V_{1/f-AMP-RMS} = N_G \times \frac{V_{1/f-AMP-PP}}{6.6}$$

(10)

因此,一个单端系统中前端电路引入的总体噪声影响,可以通过对来自放大器的宽带噪声和闪烁噪声取均方根来计算,如公式 **11**中所示。

$$V_{n\_AMP\_RMS} = N_{G} \times \sqrt{\left(\frac{V_{1/f\_AMP\_PP}}{6.6}\right)^{2} + e_{n\_RMS}^{2} \times \frac{\pi}{2} \times BW_{RC}}$$

(11)

同样的概念也可扩展至差分输入 ADC。 对于差分 ADC,唯一的区别是,两个输入驱动放大器将会增加系统的噪声。 因此,一个  $\sqrt{2}$  的因数与公式 11中计算出的噪声相乘。

$$V_{n\_AMP\_RMS} = N_G \times \sqrt{2 \times} \sqrt{\left(\frac{V_{f\_AMP\_PP}}{6.6}\right)^2 + e_{n\_RMS}^2 \times \frac{\pi}{2} \times BW_{RC}}$$

$$(12)$$

然而,应该注意的是,如果 ADC 前端电路具有一定的增益或衰减,那么电阻器的热噪声影响  $(\sqrt{4kTR\times BW_{RC}})$  也应该被计算在总体噪声计算中。 在这个表达式中,k 是波耳兹曼常数,T 是绝对温度,而 R 是前端增益网络中使用的电阻值。

对于一个具有输入满量程范围  $V_{FSR}$ 的 ADC,可以使用公式 13,根据数据表中 SNR 值来计算折算到 ADC 输入端的噪声:

$$V_{n\_ADC\_RMS} = \frac{V_{FSR}}{2\sqrt{2}} \times 10^{\frac{-SNR(dB)}{20}}$$

(13)

因此,为了对系统的 SNR 产生最小的影响,放大器的总体噪声影响应该至少比 ADC 的输入噪声低 5 倍。针对一个具有良好噪声技术规格的特定放大器,设计标准设定了 RC 滤波器的最大带宽限值 (BW<sub>RC</sub>)。

$$V_{n\_AMP\_RMS} \le \frac{1}{5} \times V_{n\_ADC\_RMS}$$

(14)

对于差分输入 ADC, 针对放大器噪声和 RC 滤波器带宽的值应该满足以下标准:

$$N_{G} \times \sqrt{2} \times \sqrt{\left(\frac{V_{f-AMP-PP}}{6.6}\right)^{2} + e_{n\_RMS}^{2} \times \frac{\pi}{2} \times BW_{RC}} \leq \frac{1}{5} \times \frac{V_{FSR}}{2\sqrt{2}} \times 10^{-\frac{SNR(dB)}{20}}$$

$$\tag{15}$$

www.ti.com.cn 操作理论

根据公式 15中的表达式,放大器的宽频带噪声密度 (e<sub>n\_RMS</sub>) 应该保持在尽可能低的水平以实现最佳的系统性能。 应该注意的是,在大多数情况下,相对于 RC 滤波器带宽内的宽带噪声,闪烁噪声的影响可忽略不计。 放大器引入的失真影响,也应该保持在极低的水平。 然而,噪声和失真的代价是增加放大器的功耗。 因此,选择适当的低功耗和低噪声放大器应该是针对这个系统设计的第一步。 选择放大器时应该考虑的另外几个重要指标:

- **轨到轨输入和输出摆幅**以支持满量程正弦信号输入到 ADC。

- 放大器的小信号带宽应该尽可能的高,这样,放大器的反馈环路能够纠正较高频率上的失真。

#### 2.2.2 RC 滤波器设计

完成一个合适的放大器选择之后,下一步是为 ADC 输入设计一个合适抗混叠 RC 滤波器。 滤波器带宽 (BW<sub>RC</sub>) 应该被保持窄带宽以限制来自前端电路的噪声影响,同时也应该足够高以防止引起输入信号的失直。

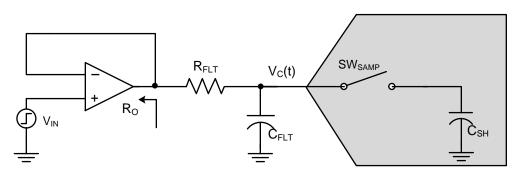

电容  $C_{FLT}$ 有助于减少 ADC 输入端的采样电荷注入,并且提供一个电荷库,在采样过程期间为采样电容  $C_{SH}$  快速充电。 应该选择电容  $C_{FLT}$ 的值,这样,当开关  $SW_{SAMP}$ 关闭时, $C_{FLT}$ 上的压降 ( $\Delta V_{FLT}$ ) 少于输入电压的 5%。

ADC 采样电容所需的电荷由公式 16给出:

$$Q_{IN} = C_{SH} \times V_{REF}$$

(16)

滤波器电容提供的电荷由公式 17给出:

$$Q_{FLT} = C_{FLT} \times \Delta V_{FLT} \leq C_{FLT} \times (0.05 \times V_{REF})$$

(17)

根据电荷守恒原理,采样电容需要的电荷应该等于滤波电容提供的电荷。 因此,可得出以下的方程式:  $\mathbf{Q}_{\mathsf{IN}} = \mathbf{Q}_{\mathsf{FIT}}$

$$\Rightarrow C_{FLT} \times (0.05 \times V_{REF}) \ge C_{SH} \times V_{REF}$$

$$\Rightarrow C_{\mathsf{FLT}} \ge 20 \times C_{\mathsf{SH}} \tag{18}$$

在这一点上,理解选择  $C_{FLT}$ 和  $R_{FLT}$ 值时的平衡取舍很重要。 如果  $C_{FLT}$ 的值高,它将在采样开关关闭时提供对电荷注入噪声的更好衰减。 然而, $C_{FLT}$ 不能被随意地定的过高,否则将降低驱动放大器的相位裕量,使之变得不稳定。 串联电阻  $R_{FLT}$ 运行为隔离电阻,这有助于稳定驱动放大器,正如 [1]和 [2]中解释的那样。 一个较高的  $R_{FLT}$ 值有助于放大器稳定性,但是较高的  $R_{FLT}$ 值会由于与 ADC 的非线性输入阻抗相互作用而增加失真。 失真随着源阻抗、输入信号频率和输入信号振幅的增加而增加。 因此, $R_{FLT}$ 的选择需要平衡设计的稳定性和失真之间的关系。

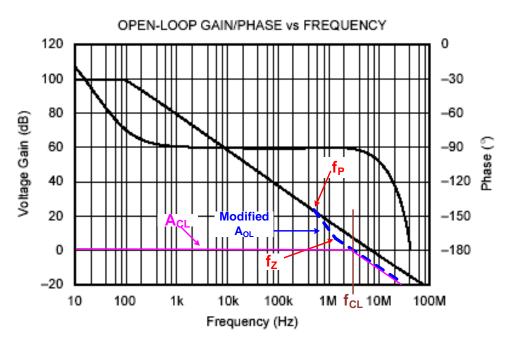

$R_{FLT}$ 的最小值取决于放大器的输出阻抗和其稳定性需求。 如果驱动放大器的输出阻抗等于  $R_o$ ,可通过评估放大器的开环增益  $(A_{OL})$  响应上的  $R_o$ , $R_{FLT}$ 和  $C_{FLT}$ 的影响来保持放大器稳定的  $R_{FLT}$ 的最小值,如图 5中所示。 在这个图中,针对为 1 的增益的放大器闭环响应被表示为  $A_{CL}$ ,而单位增益带宽被表示为  $f_{CL}$ 。

操作理论 www.ti.com.cn

图 5. 使用 AoL响应来分析 RC 滤波器对运算放大器稳定性的影响

$R_0$ , $R_{FLT}$ 和  $C_{FLT}$ 的组合在放大器的开环响应中引入了一个极点, $f_P$ (公式 19) 和一个零点, $f_Z$ (公式 20),下方给出了针对这一情况的拐点频率:

$$f_{P} = \frac{1}{2\pi (R_{O} + R_{FLT})C_{FLT}}$$

(19)

$$f_Z = \frac{1}{2\pi R_{FLT} C_{FLT}} \tag{20}$$

为了确保零点的相位变化抵消了极点引起的相位变化,极点和零点之间的频率距离必须少于或等于一个十倍 频程。

$$\log\left(\frac{f_Z}{f_P}\right) \le 1 \tag{21}$$

将公式 19和公式 20代入公式 21, 可得出 R<sub>FLT</sub>的最小值为:

$$R_{FLT} \ge \frac{R_0}{9} \tag{22}$$

为了实现稳定性, $f_z$ 的影响必须在一个低于放大器的闭环增益带宽的频率 ( $f_{cL}$ ) 上出现。 这是因为,对于放大器电路的稳定性,开环和闭环增益曲线间的闭合率应该不大于每十倍频程 20dB。 为了将与放大器性能相关的制造工艺变化计算在内,一个好的做法就是选择  $f_z$ ,放大器的闭环增益带宽, $f_{cL}$ 至少为零点频率的两倍。

$$\frac{f_{CL}}{f_Z} \ge 2 \tag{23}$$

节 3.1.2和4.1 节中描述的与运算放大器稳定性相关的绝大部分讨论以及相应的结果,在 [1]中进行了详细介绍。

www.ti.com.cn 操作理论

## 2.3 基准驱动设计

如果 ADC 没有内部基准或者内部基准的准确度不足以满足系统性能目标的要求,那么在数据采集系统中将使用外部电压基准。 这些电路为 ADC 基准输入提供低漂移和十分精确的电压。 然而,大多数基准的输出宽频带噪声大约为几百  $\mu V_{RMS}$ ,这降低了高精度 ADC 的噪声和线性性能,这是因为高精度 ADC 的典型噪声大约为几十  $\mu V_{RMS}$ 。 因此,为了优化 ADC 性能,电压基准的输出必须被适当地滤波和缓冲。

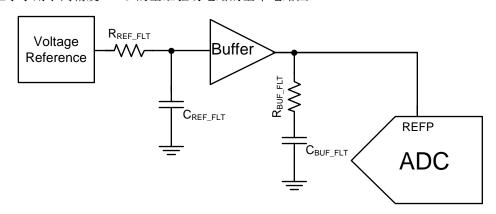

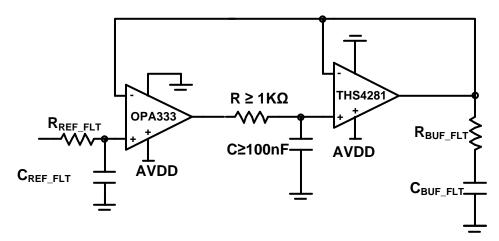

图 6中显示了用于高精度 ADC 的基准驱动电路的基本电路图。

图 6. 基准驱动电路的经简化电路原理图

基准噪声可被分为两大类:

- 低频,从 0.1Hz 至 10Hz 的峰峰值山闪烁或 1/f 噪声 (V<sub>1/f REF PP</sub>)

- 较高频宽带噪声,通常被指定为宽频率范围内的一个噪声频谱密度 (e<sub>n REF RMS</sub>)。

来自基准电路的宽带输出噪声受到一个输出上的 RC 滤波器的 3dB 截止频率 (f<sub>REF\_3dB</sub>) 的限制。 所以,此滤波器设计的主要目的是保持带宽足够低,这样,基准的固有噪声不会降低 ADC 的性能。 对于一个具有 V<sub>FSR</sub>输入动态范围的高精度 ADC,可以使用公式 24,根据数据表中 SNR 的值来计算输入引入噪声的均方根 (rms) 值:

$$V_{n\_ADC\_RMS} = \frac{V_{FSR}}{2\sqrt{2}} \times 10^{\frac{SNR(dB)}{20}}$$

(24)

因此,来自基准的总集成噪声  $(V_{n\_REF\_RMS})$  应该至少保持在 ADC 噪声的三分之一以防止系统性能的下降,如公式 **25**中所示。

$$V_{n\_REF\_RMS} \le \frac{V_{n\_ADC\_RMS}}{3}$$

(25)

对于一个 RC 滤波器,有效噪声带宽等于  $\pi/2$  和 3dB 截止频率的乘积。 来自参考电路的总噪声影响值  $V_{n\_REF\_RMS}$ ,由闪烁噪声和宽带噪声的和方根 (rss)计算得出,如公式 26中所示

$$V_{n\_REF\_RMS} = \sqrt{\left(\frac{V_{\int_{f\_REF\_pp}}}{6.6}\right)^2 + e_{n\_REF\_RMS}^2 \times \frac{\pi}{2} \times f_{REF\_3dB}}$$

(26)

将公式 24和公式 26代入公式 25, 我们得到:

$$\sqrt{\left(\frac{V_{1_{f}-REF\_pp}}{6.6}\right)^{2} + e_{n\_REF\_RMS}^{2} \times \frac{\pi}{2} \times f_{REF\_3dB}} \le \frac{1}{3} \times \frac{V_{FSR}}{2\sqrt{2}} \times 10^{-\frac{SNR(dB)}{20}}$$

(27)

操作理论 www.ti.com.cn

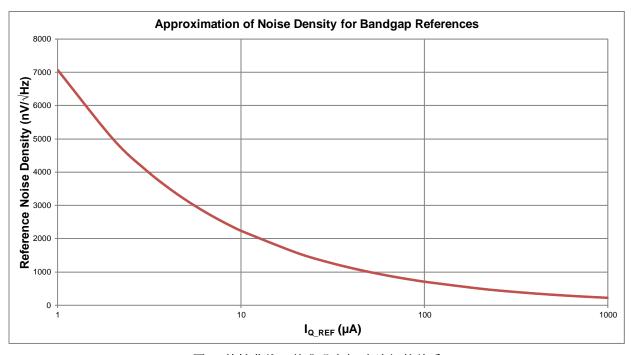

100nV/√Hz 至 10000nV/√Hz 的电压基准范围内的宽带噪声密度的变化,取决于基准的类型和功耗。 总的来说,基准噪声与其静态电流 (I<sub>Q\_REF</sub>) 成反比。 由于宽带噪声并不是一直包含在电压基准数据表内,在公式 28 中提供了针对带隙基准电路的噪声密度的近似值

$$e_{n\_REF\_RMS} \approx \frac{10000nV}{\sqrt{\text{Hz}}} \times \frac{1}{\sqrt{2 \times I_{Q\_REF}(\text{in } \mu A)}}$$

(28)

根据输出噪声密度与几个 TI 基准电路的静态电流间测得的特性,可得到公式 28,如图 7中所示。

图 7. 特性曲线: 基准噪声与 电流间的关系

通过使用公式 27和公式 28, 可得到 f<sub>REF 3dB</sub>的最大值,如公式 29中所示。

$$f_{REF\_3dB} \leq \frac{2 \times I_{Q\_REF}(\mu A)}{\left(10000 \text{ nV} / \sqrt{Hz}\right)^2} \times \frac{2}{\pi} \times \left[ \frac{1}{9} \times \frac{V_{FSR}^2}{8} \times 10^{-\frac{SNR(dB)}{10}} - \left( \frac{V_{1/f\_REF\_pp}}{6.6} \right)^2 \right]$$

(29)

用于 RC 滤波器的电容值应该保持高于 100nF 以使其热噪声保持在低于  $0.2\mu V_{RMS}$ 的水平上。 使用  $C_{REF\_FLT}$  和  $f_{REF\_3dB}$ 选择的值,可使用公式 29来计算  $R_{REF\_FLT}$ 的值,如公式 30中所示。

$$R_{REF\_FLT} = \frac{1}{2\pi f_{REF\_3dB} \times C_{REF\_FLT}}$$

(30)

www.ti.com.cn 操作理论

在参考块的噪声被频带限制后,下一个重要的步骤就是确保此基准能够驱动由 ADC 基准输入引起的动态负载。 基准缓冲器必须控制电压,使得  $\Delta V_{REF}$ 在每次转换开始时,保持在 1LSB 误差范围内。 这个要求需要在缓冲放大器的输出上使用一个电容 ( $C_{BUF\_FLT}$ ) 来驱动 ADC 基准引脚。 下方给出了确定  $C_{BUF\_FLT}$ 大小的计算:

对于一个分辨率为 N 的 ADC,两个转换间  $V_{REF}$ 的差异在公式 31中给出:

$$\Delta V_{REF} \le \frac{V_{REF}}{2^N} \tag{31}$$

让每次转换期间消耗的电荷总量为  $Q_{REF}$ 。由于基准缓冲器的配置, $C_{BUF\_FLT}$ 电容提供了快速转换过程期间大部分电荷,其余电荷由缓冲放大器提供。总的来说,可以有把握地认为此电容在快速转换过程期间提供了多于三分之二的电荷。因此,调节基准电压所需的  $C_{REF\_ELT}$ 最小值由公式 32给出:

$$C_{\text{BUF\_FLT}} = \frac{2}{3} \times \frac{Q_{\text{REF}}}{\Delta V_{\text{REF}}} \ge \frac{2}{3} \times \frac{Q_{\text{REF}} \times 2^{N}}{V_{\text{REF}}} \tag{32}$$

可使用 ADC 数据表中指定的最大 ADC 转换时间 ( $T_{CONV\_MAX}$ ) 和基准输入电流 ( $I_{REF}$ ) 的平均值来计算  $Q_{REF}$ 的 平均值,如公式 33中所示。

$$Q_{REF} = I_{REF} \times T_{CONV\_MAX}$$

(33)

公式 31,公式 32和公式 33的组合生成公式 34中得到的 C<sub>BUF FLT</sub>最小值的表达式:

$$C_{BUF\_FLT} \ge \frac{2}{3} \times \frac{I_{REF} \times T_{CONV\_MAX} \times 2^{N}}{V_{REF}}$$

(34)

从公式 34中得出的电容值足够高,使得驱动放大器不稳定,所以建议使用一个串联电阻, $R_{BUF\_FLT}$ 来隔离放大器输出,并使其稳定。  $R_{BUF\_FLT}$ 的值取决于驱动放大器的输出阻抗以及信号频率。  $R_{BUF\_FLT}$ 的典型值在  $0.1\Omega$  至  $2\Omega$  之间,并且可使用 SPICE 仿真器来找到准确值。 应该注意的是,较高的  $R_{BUF\_FLT}$ 值会在基准引脚上导致高电压尖峰,从而影响转换准确度。

电容  $C_{BUF_FLT}$ 影响驱动放大器的稳定性,因此建议使用一个串联电阻, $R_{BUF_FLT}$ 来隔离放大器输出,并使其稳定。  $R_{BUF_FLT}$ 的值取决于驱动放大器的输出阻抗以及信号频率。  $R_{BUF_FLT}$ 的典型值在  $0.1\Omega$  至  $2\Omega$  之间,并且可使用 SPICE 仿真器来找到其准确值。 建议使用尽可能小的  $R_{BUF_FLT}$ 值,以避免基准引脚上的任何电压尖峰,这有可能影响转换准确度。

在针对频带限制基准电路噪声设计了适当的无源滤波器后,下一步选择一个合适的放大器来用作一个参考缓冲器。 在选择基准缓冲器时要考虑的关键技术规格是:

- **开环输出阻抗**的值对于一个基准缓冲器来说应该保持在尽可能低的水平上,这是因为转换期间 **ADC** 从基准引脚汲取的电流以及导致的基准电压的压降直接与驱动缓冲器的输出阻抗成正比。 阻抗还有助于在驱动一个大电容负载 (**C**<sub>BUF FLT</sub>) 时保持放大器稳定。

- 输入偏移: 应该尽量减少初始输入偏移, 以确保驱动 ADC 的基准电压十分准确。

- *偏移漂移*:参考缓冲器的偏移温度漂移应该尽可能的低,以确保 ADC 的基准电压不会在温度范围内变化 太大。

组件选择 www.ti.com.cn

## 3 组件选择

这个设计重视优化 DAQ 系统的性能,以便在 TI 的低功耗、高分辨率 18 位 SAR ADC,即 ADS8881 1MSPS 的最高采样率上使用这款器件时,大大降低 DAQ 系统的功耗。 这个设计在 ADC 的差分输入上使用了一个频率为 10kHz 的满量程正弦波信号。 这个部分解释了为本设计选择不同电路组件的过程。

## 3.1 针对输入驱动电路的组件选择

## 3.1.1 放大器选择

为了满足这个设计目标,第一步是选择一个合适的放大器来驱动 ADC 输入。 由于这个设计被指定在满量程正弦输入信号上运行,运算放大器应该支持轨到轨输入和输出 (RRIO) 摆幅。 为了满足这个应用的性能目标,另外一个应该考虑的关键技术规格是低功耗、低噪声和高小信号带宽以减少高频时的信号失真。

OPA320 CMOS 放大器是一款高精度、低功耗和低噪声放大器,此放大器针对具有轨到轨输入输出的低压、单电源运行进行了优化。在这应用中,此输入是一个 10kHz 正弦波信号,此信号的振幅等于这个放大器 (由单个 5V 电源供电运行) 轨到轨输入摆幅的 ADC 的满量程输入范围。 这个放大器以 1.85mA 的极低静态电流(最大值)提供一个低噪声 (7nV/√Hz) 和高带宽。 这使得它成为驱动诸如 ADS8881 的高性能 ADC 输入并在系统功耗最低时实现最高动态性能的理想选择。

#### 3.1.2 RC 滤波器无源组件选择

针对这个设计的关键无源组件是用于 ADC 输入上 RC 滤波器的电阻 (C<sub>FLT</sub>) 和电容 (C<sub>FLT</sub>)。 所选电阻的耐受值可选择为 1%,这是因为输入端差分电容的使用平衡了由任一电阻不匹配所导致的影响。 然而,在为这个应用选择一个合适的电容类型是应该特别注意,这是因为它将有助于大大减小 ADC 输入上的信号失真。 由于它们的高 Q 值、低温度系数和变化的电压、频率和时间内稳定的电气特性,COG(NPO) 电容适非常合于这个应用。

所以根据公式 18, 这个用于 ADS8881 的输入电容的额定值为 59pF。

$$C_{FLT} \ge 20 \times C_{SH}$$

$$\Rightarrow$$

C<sub>FLT</sub>  $\ge$  1.18nF (35)

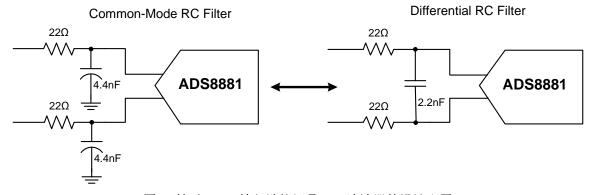

如果此滤波器被设计用于图 8中显示的共模配置中,为 ADC 的每个输入选择的电容值被设定为稍稍高于经计算出的4.4nF的电容值。然而,这个设计针对 RC 滤波器使用一个差分配置,所以一个2.2nF电容被连接在 ADC 的差分输入。

图 8. 针对 ADC 输入端抗混叠 RC 滤波器的设计配置

www.ti.com.cn 组件选择

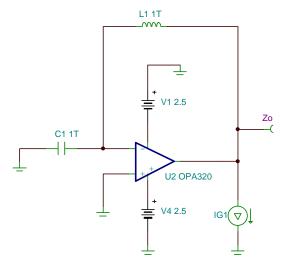

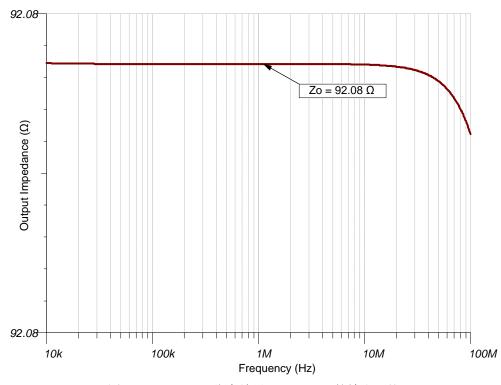

选择了电阻  $R_{FLT}$ 的值以保持驱动放大器的稳定性,并且如公式 22中解释的那样,与驱动放大器的输出阻抗无关。 已经使用 TINA-TITM Spice 工具仿真了 OPA320 的输出阻抗,如图 9中所示。 图 10中显示的仿真结果表示  $R_0$ 的值在所需的频率上等于 92.08 $\Omega$ 。

图 9. TINA-TI™ 电路图: 测量 OPA320 的输出阻抗

图 10. TINA-TI™ 仿真结果: OPA320 的输出阻抗

利用公式 22, 计算出在使用 OPA320 的 Ro时 RFLT的最小电阻值为:

$$R_{FLT} \ge \frac{92}{9} \approx 10\Omega$$

(36)

为了实现最佳的系统性能,为 ADC 的每条通道所选择的  $R_{FLT}$ 值为 $22\Omega$ 。

组件选择 www.ti.com.cn

## 3.2 针对基准驱动器电路的组件选择

#### 3.2.1 无源组件选择

这个设计中用来驱动 ADS8881 的外部基准为 TI 生产的 REF5045。 这个基准已经被选中,这是因为它在只有一个 5V 电源的系统中提供 4.5V 的最高可能基准电压。 正如 REF5045 的数据表中提到的那样,为了实现稳定,在  $V_{\rm felt}$ 引脚上,需要一个  $10\mu F$  的电容值。  $0.2\Omega$  的串联电阻与  $10\mu F$  电容一同使用以实现基准的平滑加电。

根据2.3 节中进行的讨论,来自基准的噪声带宽应该通过在基准输出上设计一个低通 RC 滤波器来进行限制。根据公式 29,这个的滤波器的 3dB 带宽的最大值应该计算为:

$$f_{REF\_3dB} \leq \frac{2 \times I_{Q\_REF}(\mu A)}{\left(10000 \text{ nV} / \sqrt{\text{Hz}}\right)^2} \times \frac{2}{\pi} \times \left[\frac{1}{9} \times \frac{V_{FSR}^2}{8} \times 10^{-\frac{SNR(dB)}{10}} - \left(\frac{V_{1/f\_REF\_pp}}{6.6}\right)^2\right]$$

$$\Rightarrow f_{REF\_3dB} \leq 1.75 \text{ kHz}$$

(37)

电容  $C_{REF_FLT}$ 选**1µF**以将电容的热噪声保持为一个较低的值。 标准电容的下一个较高的值为 **10µF**。 由于这些电容非常大并且十分昂贵,在一个设计中除非绝对必要,否则很少使用。  $R_{REF_FLT}$ 的最小值可使用公式 **37** 计算为:

$$R_{REF\_FLT} \ge \frac{1}{2\pi \times 1.75 \times 10^3 \times 10^{-6}} = 91 \,\Omega$$

(38)

针对这个设计, $R_{REF_FLT}$ 可选**1k** $\Omega$ 。 为这个电阻选择的值远远高于计算得出的最小值以进一步减少滤波器的带宽,这样,来自基准的宽带噪声影响可忽略不计。

参考设计中的下一个重要无源元件是电容  $C_{BUF\_FLT}$ ,它有助于在动态负载条件下调节 ADC 基准引脚上的电压。 根据 ADS8881 数据表,汲取进入基准引脚的平均电流  $(I_{REF})$  为 350 $\mu$ A,对于 1MSPS 的最大数据吞吐量, $T_{CONV\ MAX}$ 等于 710ns。 因此,根据公式 34, $C_{BUF\ FLT}$ 可计算为:

$$C_{\text{BUF\_FLT}} \geq \frac{2 \times 350 \times 10^{-6} \times 710 \times 10^{-9} \times 2^{18}}{3 \times 4.5} = 9.65 \mu \text{F} \tag{39}$$

对于这个设计, $C_{BUF\ FLT}$ 的值选 $10\mu F$ 。

www.ti.com.cn 组件选择

#### 3.2.2 放大器选择

如2.3 节中解释的那样,为高精度 ADC 设计一个基准缓冲器时所考虑的主要放大器技术规格是低偏移、低漂移、宽带宽和低输出阻抗。 虽然有可能选择一个符合全部这些要求的放大器,但是这样做的代价是过多的功耗。 例如,OPA350 是一款具有 0.5mV 漂移和 4μV/℃ 低温漂的 38MHz 放大器,但是它消耗的静态电流为 5.2mA,这个值对于本设计来说太高。 这是因为偏移和温漂是直流技术规格,而带宽、输出阻抗和高电容驱动能力是交流技术规格。 因此,在一个放大器中实现全部性能需要供电。 降低功耗的一个更加有效的方法是使用一个复合基准缓冲器。 它在直流高精度放大器的反馈环路中采用一个具有出色高频技术规格的放大器来在两方面都兼顾地获得更低的功耗。

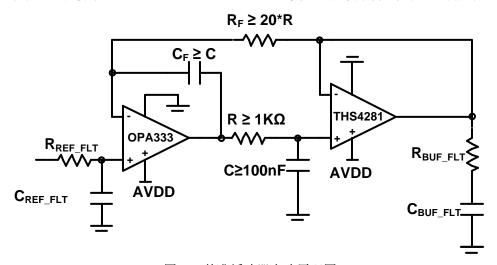

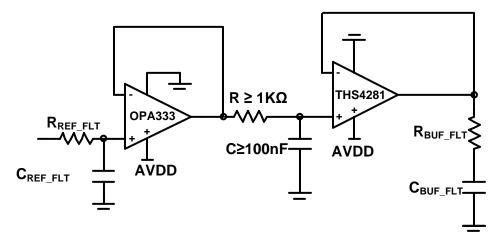

在这个设计中,基准缓冲器由 THS4281 和 OPA333 组成复合双反馈架构,如图 11中所示。

图 11. 基准缓冲器电路原理图

针对 1MHz 运行,THS4281 在增益为 1 时有一个 90MHz 的宽 3dB 带宽和 1 $\Omega$  的输出阻抗,此时的最大静态电流仅为 1mA。 这使得它非常适合于驱动高值电容  $C_{BUG\_FLT}$ 并且控制 ADC 基准输入上的电压。 然而,THS4281 的偏移较大(最大值 2.5mV)和漂移(最大值  $7\mu V/^{\circ}C$ )。技术规格的影响。 为了改进基准缓冲器的直流技术规格,OPA333 被用作一个直流校正放大器。 OPA333 是一个零漂移(最大值 0.05 $\mu V/^{\circ}C$ )和低偏移(最大值 10 $\mu V$ )放大器,最大静态电流只有 25 $\mu A$ 。 因此,为了实现与基准精度和负载调节相关的好很多的性能,相对于一个单个放大器缓冲器,这两个放大器方法只消耗 20% 的电能。

在这基准缓冲器设计中,直流放大器 (OPA333) 的噪声技术规格并不是十分重要,这是因为它被其输出上的低频 RC 滤波器深度过滤。 C 值选择大于 100nF 以将电容的热噪声保持在少于  $0.2\mu V_{RMS}$ 的水平上,并 R 值被选择为大于  $1k\Omega$  以避免由高电容负载所造成的稳定性问题。

这个放大器在这个设计中使用一个双反馈,其中的一个反馈在直流运行时有效,而另外一个反馈在更高频率的交流运行时有效。 直流运行期间的有效反馈,如图 12中所示,显示了电路的直流模型,其中  $R_F$ 表现为一个短路,这是因为那个分路没有电流流过,并且  $C_F$ 表现为一个开路。 这个反馈将 THS4281 的输出直接接至 OPA333 的输入,这在之后校正了其偏移和漂移。  $R_F$ 的值应该至少比 R 大 20 倍以避免任何稳定性问题。

组件选择 www.ti.com.cn

图 12. 基准缓冲器的直流等效电路原理图

图 13中显示了较高频运行期间的有效反馈连接。 在这样的运行频率上, $R_F$ 运行为开路连接; $C_F$ 运行为一个短路,而两个放大器被连接为隔离式单位增益缓冲器。  $C_F$ 的值应该等于或大于 C 以避免任何稳定性问题。

图 13. 基准缓冲器电路的高频等效电路原理图

## 4 仿真

图 14中显示的 TINA-TITM 电路原理图包含设计过程中得到的最终设计和电路组件值。

图 14. TINA-TI™ 电路原理图 - 完整的数据采集块

使用 ADS8881 的 TINA-TI™ SPICE 模型来评估整个信号链的性能。 使用 ADC 的 SPICE 模型准确地仿真 ADC 输入端的采样保持电路,对于设计一个合适的前端输入驱动电路十分重要。 它还包含 REFP 输入引脚的动态负载。 这在优化外部参考驱动器电路中有所帮助。 ADC 模型输出两个被称为 "AINPsmp" 和 "AINMsmp" 的信号,这两个信号代表 ADC 内部采样保持级的输出。 采样期间,这两个信号跟踪相应的输出信号,而在转换期间,这些信号被保持在一个由 ADC 转换的输入信号值上。

上面的电路使用一个 10kHz 正弦波信号进行瞬态分析仿真,以检验每次转换开始前,ADC 输入稳定至足够的准确度。 使用同样的电路来仿真每次转换开始时基准输入电压的准确度。 下面的部分提供了仿真详细信息和结果。

仿真 www.ti.com.cn

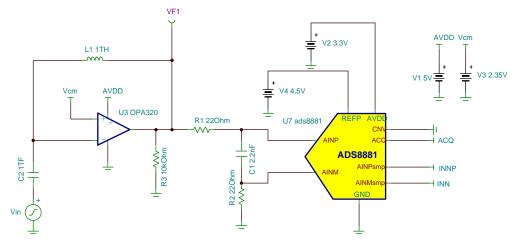

## 4.1 输入驱动放大器的稳定性

使用图 15中显示的 TINA-TITM 电路原理图来检验驱动 ADC 输入的放大器的稳定性。 尽管在设计组件选择期间已经注意了输入放大器的稳定性,但在仿真中首先检验放大器稳定性也很重要。 如果输入放大器不稳定或边界稳定,那么应该重新进行组件选择,以使得此设计在稳定性方面鲁棒性更高。

图 15. TINA-TI™ 电路原理图 - 检验输入放大器的稳定性

这个电路仿真输入驱动器的环路增益以确定相位裕量从而确定放大器的稳定性。一个值为 1TH 的大电感器被连接在放大器的反馈环路中,所以它的运行方式与高于直流频率上的开关配置相类似。 考虑到只有差分输入结构的一半电路,此电路已经被简化。 为了适当的加载放大器输出,使用 "CNV" 引脚将 ADC 接地,这样,它将一直采样输入。

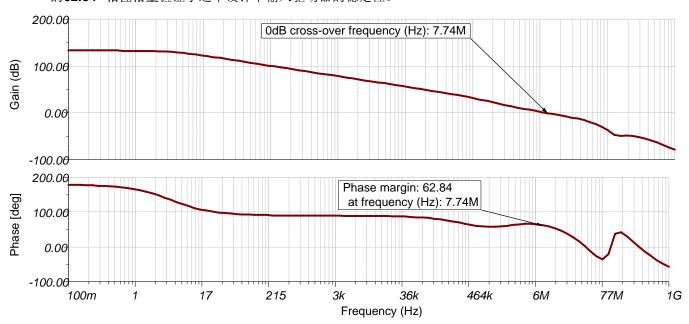

图 16中显示了针对这个电路环路增益的直流振幅 & 相位响应。 在 7.74MHz 的 0dB 分频频率上获得的62.84<sup>9</sup> 相位裕量验证了这个设计中输入驱动器的稳定性。

图 16. TINA-TI™ 仿真结果 - 针对输入驱动器稳定性的环路增益幅度 & 相位曲线图

## 4.2 ADC 输入电路的瞬态仿真

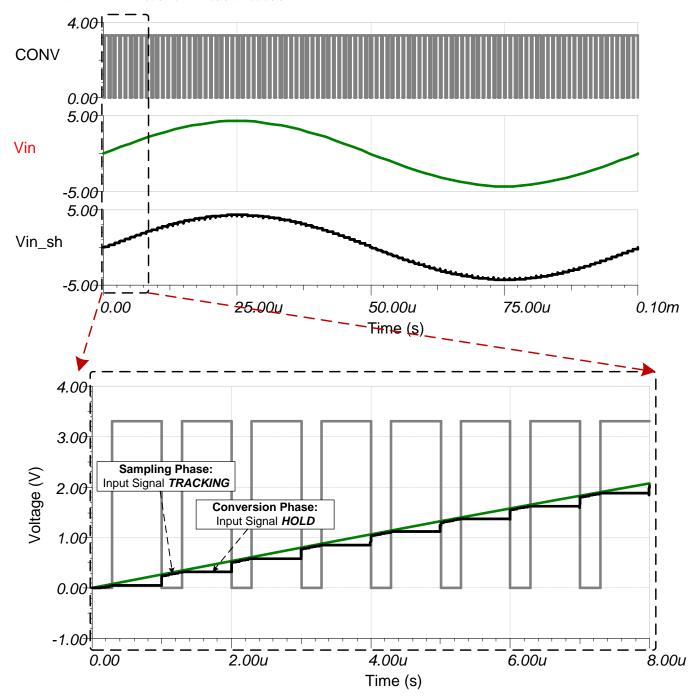

使用图 14中显示的 TINA-TITM 电路原理图来检验采样阶段期间 ADC 输入上正弦信号的准确稳定。图 17中显示了此电路的仿真时域响应。顶部的瞬态曲线图显示了施加到 ADS8881 差分输入上振幅为 ±4.63V 的一个 10kHz 正弦波周期。如4 节中所解释的那样,信号 "Vin" 代表 ADC 差分输入上的实际输入信号,而信号 "Vin\_sh" 显示了 ADC 输入采样保持电路的输出。为了获得更详细的信息,较低位置上的曲线图显示了在时间刻度上放大的同一波形。这些曲线在一起进行比较以显示被采样的信号在采样期间准确地跟踪输入信号,而在 ADC 处于转换中时,停留在保持状态。

图 17. TINA-TI™ 仿真结果 - 显示了 ADC 采样 & 保持的输入正弦波的数字化

仿真 www.ti.com.cn

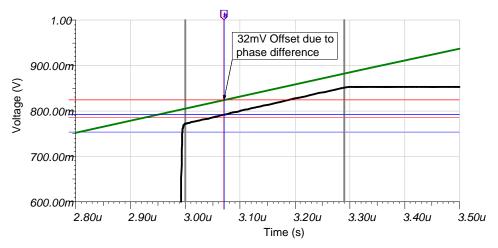

输入信号和经采样信号的进一步放大版本 (图 18) 显示了两个信号之间的一个相位延迟,这完全是由驱动电路和 ADC 输入级的前端的传播延迟引起的。

图 18. TINA-TI™ 仿真结果 - 输入和经采样信号间的相移

## 4.3 ADC 基准输入的稳定响应

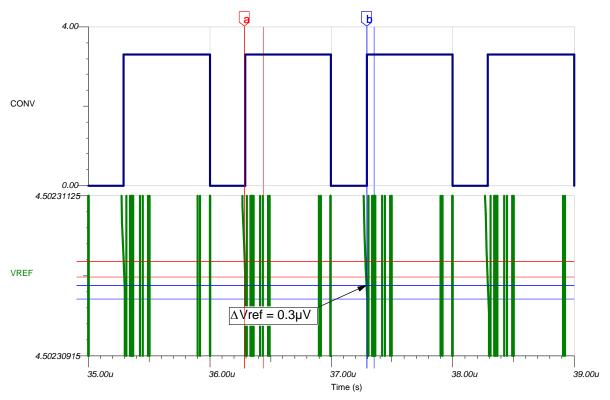

使用图 14中显示的 TINA-TITM 电路原理图来检验驱动 ADS8881 REFP 引脚的基准缓冲输出的稳定。 如2.3 节中解释的那样,基准引脚上的电压应该稳定在少于 ADC 用于保持总体系统性能所需的 LSB。 对于使用  $V_{REF}$  = 4.5V 的 ADS8881 的 LSB 的大小等于 34.3 $\mu$ V。 根据图 19中显示的瞬态仿真曲线图,两个连续转换 之间 REFP 引脚上的电压误差等于  $\Delta V_{REF}$  = 0.3 $\mu$ V,这大大少于 LSB 的大小。 这证明了基准电压已经稳定至 保持这个设计性能所需的足够准确度。

图 19. TINA-TI™ 仿真结果 - ADC 基准稳定

www.ti.com.cn PCB 设计

## 5 PCB 设计

可在10 节中找到 PCB 电路原理图和物料清单。

## 5.1 PCB 布局布线

对于这个 DAQ 块,在设计 PCB 布局布线时最重要的注意事项讨论如下:

- 从基准缓冲器电路(REF5045,THS4281 和 OPA333)至 ADC 的 REFP 输入引脚的迹线长度应该保持 尽可能的小以大大减少会导致不稳定性和基准电压准确稳定潜在问题的迹线电感。

- 包含 OPA320 缓冲器的输入驱动电路应该位于尽可能靠近 ADC 输入的位置以大大减少环路面积,从而使得布局布线对于 EMI/RFI 抑制更加稳健耐用。 相似的,ADC 输入上抗混叠滤波器的电阻和电容应该尽可能的靠近在一起并且靠近于 ADC 的输入以大大减少环路面积。

- 将来自电源的差分输入电压向上馈入 ADC 差分输入的迹线应该保持对称而没有任何明显的转弯。

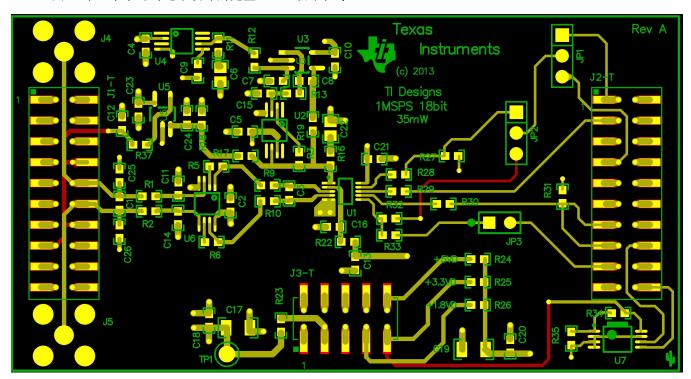

图 20中显示了针对这个设计的完整 PCB 布局布线。

图 20. PCB 布局布线

验证和测得的性能 www.ti.com.cn

## 6 验证和测得的性能

在这个部分中列出了这个 TI Design 用于验证的测量结果。

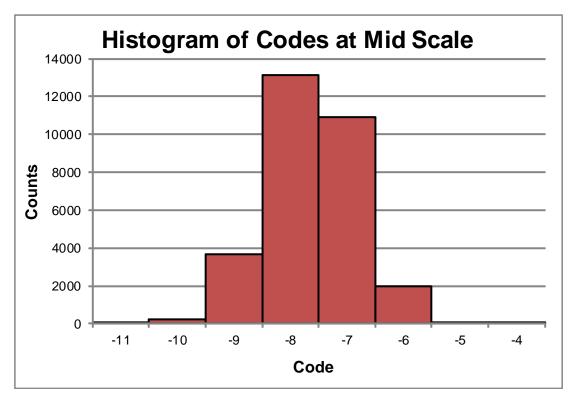

## 6.1 直流噪声测量

所有 ADC 电路都会或多或少的受到内部电阻、电容和其它电路所导致的固有宽带噪声的影响,这个噪声由 ADC 的输入引入。 前端电路也会对系统产生一些噪声,也可由 ADC 输入引入。 累积噪声,通常称为 ADC 的输入引入噪声,对于总体系统性能有很大的影响。 标记这个噪声最常用的方法是使用一个恒定直流电压作为输入信号并且采集大量 ADC 输出代码。 然后,可以绘制一个柱状图来显示输出代码的分布,这可用来说明噪声对总体系统性能的影响。 在这个设计中,通过将两个输入驱动放大器的输入短接至一个共模电压来测量直流噪声, $V_{CM}=1/2\times V_{REF}=2.25V$ ,这样 ADC 输入上的差分电压等于  $V_{DIFF}=0V$ 。 图 21中显示了得到的输出代码柱状图。

图 21. 测量数据 - 显示直流噪声的柱状图 (中量程)

输出代码的分布看起来像一个高斯分布,这表示一个正确的系统设计。 然而,如果输出代码分布具有大峰值和波谷而明显不是高速分布的话,那么它表示 ADC 中严重的 DNL 误差或者与系统设计有关的问题,像不充分的电源去耦合,不适当的接地连接和/或其它糟糕的 PCB 布局布线影响。 对于一个理论上完美的 ADC 系统,输出代码的柱状图将是一个简单垂直的条状图,这是因为对于一个直流输入电压,ADC 输出将始终如一。 然而,ADC 和前端电路的噪声影响将导致一个输出代码的分布,这提供了一个总体系统直流噪声的测量方法。 代码  $(N_{PP})$  与代码标准偏差  $(N_{G})$  之间峰峰值差异的测量值在表 2中列出。

www.ti.com.cn 验证和测得的性能

一个 ADC 的无噪声分辨率被定义为上面转换器稳定输出位的数量,真不太可能在单个代码转换之间进行区分。 这是一个极其保守的 ADC 性能测量方法, 这是因为无噪声分辨率的公式得自峰峰值代码噪声,这取决于采样的总数量。

一个更加可靠的方法是在计算 ADC 的 有效分辨率中使用输出代码的标准偏差  $(N_o)$ 。 请注意的是,表 2中显示的结果在计算与峰峰值的标准偏差中为采用一个基于高斯的公式,这是因为总体直流噪声与 LSB 的大小相当。 对于一个这个设计中使用的 18 位 ADC,测得的有效分辨率的值也等于 18 位,这表明噪声的影响并未对转换器的性能产生影响。

请注意的是,不应该把6.2 节中显示的有效分辨率和有效位 (ENOB)相混淆,因为它们是两个完全不同的实体。 使用一个交流正弦输入信号来测量针对 ADC 的 ENOB,并且 ENOB 包含由量化噪声和失真项值所导致的结果,而此结果对于直流测量没有影响。

表 2. 直流噪声的测量结果

| 参数                           | 公式                                             | 测得的值  |

|------------------------------|------------------------------------------------|-------|

| 平均输出代码                       | 不可用                                            | -7.64 |

| 峰值到峰值代码噪声 (N <sub>PP</sub> ) | 最大值 输出代码 - 最小值 输出代码 + 1                        | 8     |

| 代码的标准偏差 (。)                  | 不可用                                            | 0.82  |

| 无噪声分辨率                       | $\log_2\!\!\left(\frac{2^{18}}{N_{PP}}\right)$ | 15    |

| 有效分辨率                        | $\log_2\left(\frac{2^{18}}{N_{\sigma}}\right)$ | 18    |

验证和测得的性能 www.ti.com.cn

## 6.2 ADC 动态性能测量

这份文档中解释的 TI Design 已经针对以 1MSPS 的数据吞吐量用最低的功耗实现 ADS8881 的最大输出性能进行了优化。然而,这个系统还实现了出色的交流噪声和失真性能,如表 3中列出的那样。 已经使用一个 10kHz 正弦输入信号执行了测量。图 22显示了一个 TI 的 ADCProTM 工具的屏幕截图,此截图显示了测得的系统交流性能。 此数据表技术规格基于  $V_{REF}=5V$  的情况,但是这些测量结果指出了  $V_{REF}=4.5V$  时 ADC 的性能,这表示测得的值比实际的 ADC 针对 SNR,THD 和 SINAD 的性能值少大约 0.9dB。 尽管这个调节,这个系统测得的 THD 劣于 ADC8881 的额定 THD,这是因为这个设计使用 OPA320 作为输入驱动放大器,这大大增加了系统失真。 输入驱动器的选择主要受到 OPA320 以受限单位增益带宽为代价获得的低功耗的影响,正是由于这个原因,放大器不能校正系统的较高频失真。

| 参数               | ADS8881 数据表技术规格              | 测得的值    |

|------------------|------------------------------|---------|

| 信噪比 - SNR (dB)   | 99 @ V <sub>REF</sub> = 5V   | 98.97   |

| 总谐波失真 - THD (dB) | -112 @ V <sub>REF</sub> = 5V | -105.64 |

| 信纳比 - SINAD (dB) | 98.8 @ V <sub>REF</sub> = 5V | 98.12   |

| 有效位数 - ENOB      | 不可用                          | 16.01   |

表 3. 针对 ADC 交流性能的测量结果

图 22. 测量数据 - 使用 ADCPro™ 测得的 DAQ 块的交流性能

www.ti.com.cn 验证和测得的性能

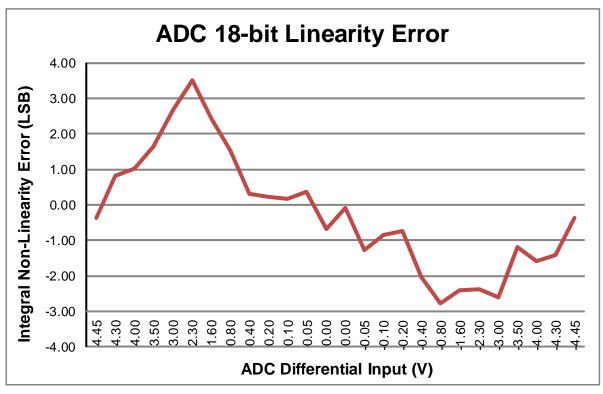

## 6.3 ADC 线性测量

通过以 26 个电压步长扫描 -4.45V 至 4.45V 范围内的差分输入电压来测量此系统的线性,而积分非线性 (INL) 误差在抵消来自响应的偏移和增益误差后绘出。 图 23中显示了这个 26 点 INL 曲线图。 这个 DAQ 块不提供最佳的线性性能,这是因为它已经针对最低功耗和低噪声进行了优化。 前端驱动器 (OPA320) 中使用的放大器具有一个由其低功率导致的相对高的输出阻抗,这导致了一个较高的隔离电阻 (R<sub>FLT</sub>) 的值以保持放大器稳定。 这个较高的隔离电阻的值增加了针对满量程输入信号的总体失真,这直接影响了系统的线性性能。

图 23. 测量数据 - ADC INL 曲线图 (26 点)

表 4. 针对线性测试的测量结果

| 参数                       | ADS8881 数据表技术规格 | 测得的值   |

|--------------------------|-----------------|--------|

| 偏移误差 (mV)                | ±4mV(最大值)       | -0.277 |

| 增益误差 (% FSR)             | ±0.03%(最大值)     | 0.0014 |

| INL <sub>最小值</sub> (LSB) | -3              | -2.78  |

| INL <sub>最大值</sub> (LSB) | 3               | 3.5    |

修改 www.ti.com.cn

## 7 修改

为满足这个设计要求,选择的组件已被优化,并在开始设计时的1 节中提到。 选择一个诸如 OPA320 的具有轨到轨输入和输出 (RRIO) 的低功耗和低噪声放大器有助于实现在由 5V 直流模拟电源供电时功耗少于 35mW 的设计目标,而同时仍然实现了针对满量程 10kHz 正弦输入信号上良好动态性能的目标。 表 5中的比较显示了 TI 产品系列中具有更低功耗和更低噪声 RRIO 的放大器,曾经考虑将这些器件用于这个设计。 很明显的是,OPA350 具有更好的带宽,可进一步减少电路中的较高频率失真,但是由于其高功耗而未被选中。 这个设计中考虑的较低功耗 RRIO 放大器包括 OPA376 和 OPA364。 这些放大器具有较低带宽和较高的宽带噪声密度,这使得它们不适合用于这个设计。

最大值 10 1/f 噪声 - 0.1Hz 至 10Hz 噪声密度 @ 10kHz 单位增益带宽 运算放大器 (nV/√Hz)  $(\mu V_{PP})$ (MHz) (mA) 1.85 7 **OPA320** 2.8 20 7 **OPA350** 7.5 未指定 38 **OPA376** 1 8.0 7.5 5.5 **OPA364** 10 7 1.4 17

表 5. 针对驱动 ADS8881 输入的运算放大器技术规格比较

然而,有很多应用不具有满量程正弦信号作为到系统的输入。 这些设计不需要使用一个 RRIO 放大器来驱动 ADC 输入。表 6列出了 TI 产品系列中更多放大器之间的比较,这些放大器可被用作针对这些应用的输入驱动器。

| 运算放大器  | 最大值 I <sub>Q</sub><br>(mA) | 1/f 噪声 - 0.1Hz 至 10Hz<br>(μV <sub>PP</sub> ) | 噪声密度 @ 10kHz<br>(nV/√Hz) | 单位增益带宽<br>(MHz) |

|--------|----------------------------|----------------------------------------------|--------------------------|-----------------|

| OPA836 | 1.5                        | 未指定                                          | 4.6                      | 205             |

| OPA835 | 0.365                      | 未指定                                          | 9.3                      | 56              |

| OPA300 | 12                         | 40                                           | 3                        | 150             |

表 6. 针对已修改系统要求的 ADC 输入驱动器的简单比较

## 8 关于作者

Vinay Agarwal 是亚利桑那州图森市德州仪器 (TI) 公司高精度模拟,SAR ADC 团队的一名产品定义工程师。 在任这个职位之前,他已经在 TI 从事高精度数据转换器和放大器设计。 Vinay 从 Medford 的 Tufts 大学获得理科硕士学位,从印度 Kharagpur 的印度理工学院获得理科学士学位(荣誉学士)。

## 9 参考文献和致谢

- 1. Tim Green; 运算放大器稳定性 部分 1-11, 2008 年 11 月, 可从http://www.engenius.net/site/zones/acquisitionZONE/technical\_notes/acqt\_050712内下载

- 2. Bonnie C. Baker, Miro Oljaca; http://www.electro-tech-online.com/custompdfs/2013/05/6602451.pdf

- 3. Tim Green; 为高精度 CDAC SAR A/D 选择一个合适的放大器- 内部剪报, 2008 年 2 月

- 4. 感谢 Rafael Ordonez 在设计 PCB 电路板电路原理图 & 布局布线和获取全部测量数据方面所做的工作。

附录 www.ti.com.cn

#### 附录 10

# 10.1 电气原理图和物料清单

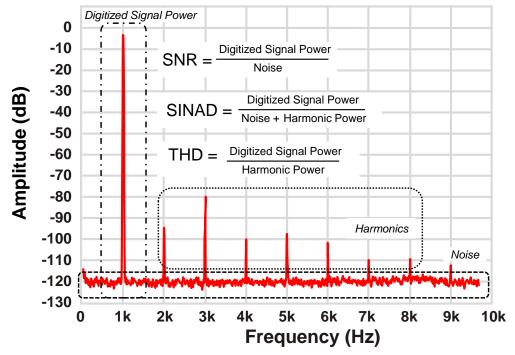

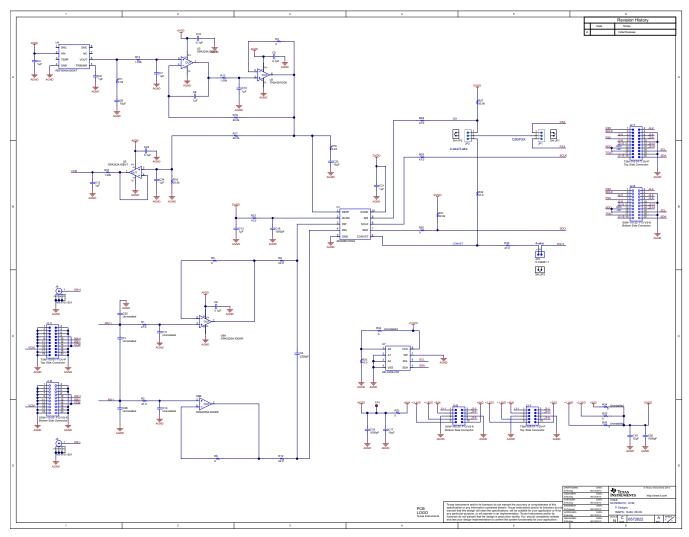

针对这个设计的电气原理图和物料清单分别显示在图 24和图 25中。

图 24. 电气原理图

27

附录 www.ti.com.cn

| ITEM    | OTY   | MFG               | MFG PART#            | REF DES                           | DESCRIPTION                                            | VALUE or FUNCTION |

|---------|-------|-------------------|----------------------|-----------------------------------|--------------------------------------------------------|-------------------|

| II LIVI | Q I I | TBD by TI         | IWI O I AICI#        | INCI DEG                          | DESONI HON                                             | VALUE OF FORCHOR  |

|         |       | (TURNKEY)         |                      |                                   |                                                        |                   |

|         |       | TBD by TI         | 6572622A             |                                   | ASSEMBLY                                               |                   |

|         | REF   | I DU DY II        | 6572622A             | -                                 | SCHEMATIC                                              | Ī                 |

|         |       | TDD by T          | 6572622A<br>6572622A | -                                 | FABRICATION                                            | Ī .               |

|         | REF   | TBD by TI         |                      | -                                 |                                                        | Ī .               |

| -       | KEF   | -                 | 6572622A             | -                                 | ARTWORK                                                | -                 |

| 1       | 2     | Emerson Network   | 142-0701-201         | J4, J5                            | Connector, TH, SMA                                     |                   |

| l'      | ľ     | Power             | 142-0701-201         | 34, 33                            | Connector, 111, SWA                                    |                   |

| 2       | 1     | Samtec. Inc.      | SSW-105-22-F-D-VS-K  | J3-B                              | Connector, Header, 10-Pos (10x2), Receptacle, 100x100- |                   |

|         | l .   |                   |                      |                                   | mil Pitch                                              |                   |

| 3       | 2     | Samtec, Inc.      | TSM-110-01-T-DV-P    | J1-T, J2-T                        | Header, 100mil, 10x2, SMD                              |                   |

| 4       |       | Samtec, Inc.      | SSW-110-22-F-D-VS-K  | J1-B, J2-B                        | Connector, Receptacle, 100mil, 10x2, Gold plated, SMD  |                   |

| 5       |       | Samtec, Inc.      | TSM-105-01-T-DV-P    | J3-T                              | Header, 100mil, 5x2, SMD                               |                   |

| 6       |       | MuRata            | GRM31CR71C106KAC7L   | C17, C19                          | CAP, CERM, 10uF, 16V, +/-10%, X7R, 1206                |                   |

| 7       | 2     | Sullins Connector | PBC03SAAN            | JP1, JP2                          | Header, TH, 100mil, 1x3, Gold plated, 230 mil above    |                   |

|         |       | Solutions         |                      | , ,                               | insulator                                              |                   |

| 8       | 2     | MuRata            | GRM21BR71A106KE51L   | C6, C22                           | CAP, CERM, 10uF, 10V, +/-10%, X7R, 0805                |                   |

| 9       | 3     | Kemet             | C0603C102J5GAC       | C16, C18, C20                     | CAP, CERM, 1000pF, 50V, +/-5%, C0G/NP0, 0603           |                   |

| 10      | 1     | Keystone          | 5000                 | TP1                               | Test Point, Miniature, Red, TH                         |                   |

| 11      | 9     | MuRata            | GRM188R71A105KA61D   | C4, C7, C8, C9, C12, C13, C15,    | CAP, CERM, 1uF, 10V, +/-10%, X7R, 0603                 |                   |

|         |       |                   |                      | C21, C24                          |                                                        |                   |

| 12      | 2     | Panasonic         | ERJ-3RQFR22V         | R11, R16                          | RES, 0.22 ohm, 1%, 0.1W, 0603                          |                   |

| 13      | 1     | TDK               | C1608C0G1H222J       | СЗ                                | CAP, CERM, 2200pF, 50V, +/-5%, C0G/NP0, 0603           |                   |

| 14      | 3     | 3M                | 969102-0000-DA       | SH-JP1, SH-JP2, SH-JP3            | Shunt, 100mil, Gold plated, Black                      |                   |

| 15      | 1     | Vishay-Dale       | CRCW060310R0FKEA     | R22                               | RES, 10.0 ohm, 1%, 0.1W, 0603                          |                   |

| 16      | 3     | Vishay-Dale       | CRCW06031K00FKEA     | R12, R13, R37                     | RES, 1.00k ohm, 1%, 0.1W, 0603                         |                   |

| 17      |       | Vishay-Dale       | CRCW060320K0FKEA     | R17, R18, R19, R27, R31           | RES, 20.0k ohm, 1%, 0.1W, 0603                         |                   |

| 18      | 4     | AVX               | 06033C104KAT2A       | C2, C5, C10, C23                  | CAP, CERM, 0.1uF, 25V, +/-10%, X7R, 0603               |                   |

| 19      | 2     | Yageo America     | RC0603FR-0722RL      | R9, R10                           | RES, 22.0 ohm, 1%, 0.1W, 0603                          |                   |

|         | 6     | Panasonic         | ERJ-3GEY0R00V        | R3, R5, R6, R23, R25, R30         | RES, 0 ohm, 5%, 0.1W, 0603                             |                   |

| 21      |       | Yageo America     | RC0603FR-0747RL      | R1, R2, R28, R29, R32, R33, R35   | RES, 47.0 ohm, 1%, 0.1W, 0603                          |                   |

| 22      | 1     | Microchip         | 24LC256-I/ST         | U7                                |                                                        |                   |

| 23      | 1     | Texas Instruments | ADS8881IDGS          | U1                                | ADC 1MSPS 18bit Fully-Diff MSOP-10                     |                   |

| 24      | 1     | TE Connectivity   | 5-146261-1           | JP3                               | Header, 100mil, 2x1, Gold plated, TH                   |                   |

| 25      | 1     | Texas Instruments | THS4281DGK           | U2                                | IC OpAmp GP R-R 90MHz SGL MSOP-8                       |                   |

|         | 2     | Texas Instruments | OPA333AIDBVT         | U3, U5                            | OpAmp, Low Power, Low Drift, 1.8V                      |                   |

| 27      | 1     | Texas Instruments | OPA2320AIDGKR        | U6                                | OpAmp, RRIO, 0.9pA IB, 20MHz                           |                   |

| 28      | 8     |                   | N/A                  | C1, C11, C14, C25, C26, R24, R26, | Uninstalled                                            |                   |

|         | l     |                   | 1                    | R34                               |                                                        |                   |

| 29      | 1     | Texas Instruments | REF5045AIDGKT        | U4                                | VREF PREC 4.5V MSOP-8                                  | 1                 |

图 25. 物料清单

www.ti.com.cn 修订历史记录

# 修订历史记录

| 修订版本           | 页  | 说明                  |

|----------------|----|---------------------|

| SLAU513 最初发布版本 |    | 最初发布版本              |

| SLAU513A       | 11 | 更新了针对参考驱动器设计的操作原理   |

| SLAUSTSA       | 14 | 更新了针对 ADS8881 的基准电流 |

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### 针对 TI 参考设计的重要声明

德州仪器公司 ("TI") 参考设计只用于帮助设计人员 ("客户") 开发包含 TI 半导体产品的系统 (在这里也指"组件")。 客户理解并同意他们对设计客户系统和产品中的独立分析、评估和判断负责。

TI 参考设计已经使用标准实验室条件和工程实践创建。 TI 未采取任何测试,除非那些在已发布文档中针对一个特定参考设计所专门描述的测试。TI 也许会对它的参考设计进行修正、提高、改进和其它改变。

客户被授权使用具有每个特定参考设计中确认的 TI 组件的 TI 参考设计,并且在他们的终端产品开发中修改参考设计。然而,在这里不授予任何其它 TI 知识产权的直接或隐含,默许或其它方式的许可,和任何第三方技术或知识产权的许可,其中包括但不只限于任何专利权、版权、屏蔽作品权、或者与采用了 TI 产品或服务的任何集成、机器或工艺相关的知识产权。 TI 所发布的与第三方产品或服务有关的信息,不能构成使用这些产品或服务的许可、授权、或认可。 使用此类信息可能需要获得第三方的专利权或其它知识产权方面的许可,或是 TI 的专利权或其它知识产权方面的许可。

TI 参考设计"按原样"提供。对于参考设计(包括其精度和完整性)或是参考设计的使用,TI 不作出任何直接、隐含或者法律规定的保证或声明。TI 不作出任何权利保证,不对任何隐含的适销性、针对特定用途的适用性、平静受益权、无干扰享用权,以及与TI 参考设计或其使用相关的任何第三方知识产权的非侵权作出任何保证。TI 不应对任何与TI 参考设计中提供的产品组合相关的或基于这些产品组合的第三方侵权声明负责,并且不应为客户提供辩护或赔偿。不论是何原因造成任何实际的、特殊的、意外的、相应发生的或间接的损坏,并且不论TI 是否已经告知了TI 参考设计的任何使用或TI 参考设计的客户使用所造成的此类损坏的可能性,TI 都不应对此负责。

TI 保留根据 JESD46 最新标准, 对所提供的半导体产品和服务进行更正、增强、改进或其它更改的权限,并有权根据 JESD48 最新标准中止 提供任何产品和服务。 客户在下订单前应获取最新的相关信息,并验证这些信息是否完整且是最新的。 所有产品的销售都遵循在订单确认时 所提供的 TI 销售条款与条件。

TI 保证其所销售的组件的性能符合产品销售时 TI 半导体产品销售条件与条款的适用规范。 仅在 TI 保证的范围内,且 TI 认为有必要时才会使用测试或其它质量控制技术。 除非适用法律做出了硬性规定,否则没有必要对每种产品的所有参数进行测试。

TI 对应用帮助或客户产品设计不承担任何义务。 客户应对其使用 TI 组件的产品和应用自行负责。 为尽量减小与客户产品和应用相关的风险,客户应提供充分的设计与操作安全措施。

对于 TI 数据手册、数据表或参考设计中的 TI 信息,仅在没有对内容进行任何篡改且带有相关授权、条件、限制和声明的情况下才允许进行复制。 TI 对此类篡改过的文件不承担任何责任。 第三方信息可能受到其它限制条件的制约。

客户认可并同意,尽管任何应用相关信息或支持仍可能由TI 提供,但他们将独立负责满足与其产品及在其应用中使用TI 产品相关的所有法律、法规和安全相关要求。客户声明并同意,他们具备制定与实施安全措施所需的全部专业技术和知识,并且这些安全措施能够可预见故障的危险后果、监测故障及其后果、降低有可能造成人身伤害的故障的发生机率并采取适当的补救措施。客户将全额赔偿因在客户的安全关键应用中使用任何TI 组件而对TI 及其代理造成的任何损失。

在某些场合中,为了推进安全相关应用有可能对 TI 组件进行特别的促销。借助于这样的组件,TI 的目标是帮助客户设计和创立其特有的可满足适用的功能安全性标准和要求的终端产品解决方案。 尽管如此,此类组件仍然服从这些条款。

TI 组件未获得用于 FDA Class III(或类似的生命攸关医疗设备)的授权许可,除非各方授权官员已经达成了专门管控此类使用的特别协议。

只有那些 TI 特别注明属于军用等级或"增强型塑料"的 TI 组件才是设计或专门用于军事/航空应用或环境的组件。 客户认可并同意,对还未指定面向军事或航空航天用途的 TI 组件进行军事或航空航天方面的应用,其风险由客户单独承担,并且由客户独力负责满足与此类使用相关的所有法律和法规要求。

TI 己明确指定符合 ISO/TS16949 要求的产品,这些产品主要用于汽车。 在任何情况下,因使用非指定产品而无法达到ISO/TS16949 要求,TI 将不承担任何责任。

邮寄地址: 上海市浦东新区世纪大道1568 号,中建大厦32 楼邮政编码: 200122 Copyright © 2013, 德州仪器半导体技术(上海)有限公司

#### 重要声明

德州仪器(TI) 及其下属子公司有权根据 JESD46 最新标准, 对所提供的产品和服务进行更正、修改、增强、改进或其它更改, 并有权根据 JESD48 最新标准中止提供任何产品和服务。客户在下订单前应获取最新的相关信息, 并验证这些信息是否完整且是最新的。所有产品的销售都遵循在订单确认时所提供的TI 销售条款与条件。

TI 保证其所销售的组件的性能符合产品销售时 TI 半导体产品销售条件与条款的适用规范。仅在 TI 保证的范围内,且 TI 认为 有必要时才会使用测试或其它质量控制技术。除非适用法律做出了硬性规定,否则没有必要对每种组件的所有参数进行测试。

TI 对应用帮助或客户产品设计不承担任何义务。客户应对其使用 TI 组件的产品和应用自行负责。为尽量减小与客户产品和应 用相关的风险,客户应提供充分的设计与操作安全措施。

TI 不对任何 TI 专利权、版权、屏蔽作品权或其它与使用了 TI 组件或服务的组合设备、机器或流程相关的 TI 知识产权中授予 的直接或隐含权限作出任何保证或解释。TI 所发布的与第三方产品或服务有关的信息,不能构成从 TI 获得使用这些产品或服 务的许可、授权、或认可。使用此类信息可能需要获得第三方的专利权或其它知识产权方面的许可,或是 TI 的专利权或其它 知识产权方面的许可。

对于 TI 的产品手册或数据表中 TI 信息的重要部分,仅在没有对内容进行任何篡改且带有相关授权、条件、限制和声明的情况 下才允许进行复制。TI 对此类篡改过的文件不承担任何责任或义务。复制第三方的信息可能需要服从额外的限制条件。

在转售 TI 组件或服务时,如果对该组件或服务参数的陈述与 TI 标明的参数相比存在差异或虚假成分,则会失去相关 TI 组件 或服务的所有明示或暗示授权,且这是不正当的、欺诈性商业行为。TI 对任何此类虚假陈述均不承担任何责任或义务。

客户认可并同意,尽管任何应用相关信息或支持仍可能由 TI 提供,但他们将独力负责满足与其产品及在其应用中使用 TI 产品 相关的所有法律、法规和安全相关要求。客户声明并同意,他们具备制定与实施安全措施所需的全部专业技术和知识,可预见 故障的危险后果、监测故障及其后果、降低有可能造成人身伤害的故障的发生机率并采取适当的补救措施。客户将全额赔偿因 在此类安全关键应用中使用任何 TI 组件而对 TI 及其代理造成的任何损失。

在某些场合中,为了推进安全相关应用有可能对 TI 组件进行特别的促销。TI 的目标是利用此类组件帮助客户设计和创立其特 有的可满足适用的功能安全性标准和要求的终端产品解决方案。尽管如此,此类组件仍然服从这些条款。

TI 组件未获得用于 FDA Class III(或类似的生命攸关医疗设备)的授权许可,除非各方授权官员已经达成了专门管控此类使 用的特别协议。

只有那些 TI 特别注明属于军用等级或"增强型塑料"的 TI 组件才是设计或专门用于军事/航空应用或环境的。购买者认可并同 意,对并非指定面向军事或航空航天用途的 TI 组件进行军事或航空航天方面的应用,其风险由客户单独承担,并且由客户独 力负责满足与此类使用相关的所有法律和法规要求。

TI 己明确指定符合 ISO/TS16949 要求的产品,这些产品主要用于汽车。在任何情况下,因使用非指定产品而无法达到 ISO/TS16949 要求,TI不承担任何责任。

|               | 产品                                 |              | 应用                       |

|---------------|------------------------------------|--------------|--------------------------|

| 数字音频          | www.ti.com.cn/audio                | 通信与电信        | www.ti.com.cn/telecom    |

| 放大器和线性器件      | www.ti.com.cn/amplifiers           | 计算机及周边       | www.ti.com.cn/computer   |

| 数据转换器         | www.ti.com.cn/dataconverters       | 消费电子         | www.ti.com/consumer-apps |

| DLP® 产品       | www.dlp.com                        | 能源           | www.ti.com/energy        |

| DSP - 数字信号处理器 | www.ti.com.cn/dsp                  | 工业应用         | www.ti.com.cn/industrial |

| 时钟和计时器        | www.ti.com.cn/clockandtimers       | 医疗电子         | www.ti.com.cn/medical    |

| 接口            | www.ti.com.cn/interface            | 安防应用         | www.ti.com.cn/security   |

| 逻辑            | www.ti.com.cn/logic                | 汽车电子         | www.ti.com.cn/automotive |

| 电源管理          | www.ti.com.cn/power                | 视频和影像        | www.ti.com.cn/video      |

| 微控制器 (MCU)    | www.ti.com.cn/microcontrollers     |              |                          |

| RFID 系统       | www.ti.com.cn/rfidsys              |              |                          |

| OMAP应用处理器     | www.ti.com/omap                    |              |                          |

| 无线连通性         | www.ti.com.cn/wirelessconnectivity | 德州仪器在线技术支持社区 | www.deyisupport.com      |

|               |                                    |              |                          |

邮寄地址: 上海市浦东新区世纪大道1568 号,中建大厦32 楼邮政编码: 200122 Copyright © 2014, 德州仪器半导体技术(上海)有限公司