## TI Designs: TIDA-01498 具有宽输入电压范围的 4W PLC 电源参考设计

# TEXAS INSTRUMENTS

## 说明

此参考设计展示了非隔离式 PLC 电源产生稳定输出电 压(该电压介于最小和最大输入电压之间)的一种替代 方法。虽然降压/升压拓扑更为常用,但是耦合电感器单 端初级电感转换器(通常称为 SEPIC)的效率会高得 多,成本也更低。

## 资源

TIDA-01498 LM5001NISOEVAL LM5001 设计文件夹 工具文件夹 产品文件夹

## 特性

- 功率高达 4W

- 效率高达 91%

- 宽 V<sub>IN</sub> 范围: 8V 至 36V

- 精确电压输出: 24V ± 2%

- 外形小巧

- 部件数量少

- 短路保护

- 支持软启动

## 应用

- 通信模块

- CPU (PLC 控制器)

- 特殊功能模块

53

该 TI 参考设计末尾的重要声明表述了授权使用、知识产权问题和其他重要的免责声明和信息。

#### System Description

## 1 System Description

Factory automation equipment operates sometimes in rough environments with input voltages that vary in a wide range. One reason could be that the system is connected to a power supply through a very long power supply line; 2-mile (or 3.5-km) connections are not rare. There are cases where the system specification might want to support a wide input voltage range to enable powering applications off a vehicle battery. This battery could have 12 V or 24 V. Internally, the system needs a stable power supply—in many cases 24 V. Typical topologies to use for this type of challenge are:

- Flyback

- Fly-Buck<sup>™</sup>

- Buck-boost

- Boost with separate buck

- SEPIC

This reference design evaluates the SEPIC topology in a special form. The two inductors of the SEPIC topology are implemented here as a coupled inductor with a 1:1 winding ratio on the same core.

CPU modules for smaller PLCs and communication modules for remote I/O systems have a similar build. Both modules are designed around a CPU or MPU, can drive a backplane, and have ideally some form of industrial ethernet on board. Therefore, at an equivalent system size, these modules have similar CPU performance and in particular power requirements. A third module category with similar power requirements are the special function modules. They can have a wide variety of functionality and include in many cases a local MPU, CPU, or FPGA/ASIC. A special function module offloads the main CPU by executing critical functions in local firmware. Local execution reduces the amount of communication over the backplane or over an industrial communication link. It also improves the response time in time sensitive control situations. It is the complexity of a special function module which sets the power requirement into the same range as the one from CPU and communication modules. Therefore, these modules are in many cases individually field powered.

All of these module types can benefit from a stable internal main power rail. A constant and defined internal voltage simplifies the design of onboard isolating converters and point-of-load regulators. If the system must run in a harsh environment with a variable field input supply voltage, this reference design can help to create the required stable internal power supply voltage.

## 1.1 Key System Specifications

| SYMBOL           | PARAMETER              | CONDITIONS                                   | SPECIFICATION |     |                   | UNIT | DETAILS |

|------------------|------------------------|----------------------------------------------|---------------|-----|-------------------|------|---------|

|                  |                        |                                              | MIN           | TYP | MAX               | UNIT | DETAILS |

| V <sub>IN</sub>  | Input voltage          |                                              | 8             | 24  | 36 <sup>(1)</sup> | V    | 2.3 节   |

| Ι <sub>Q</sub>   | Quiescent current      | $I_{OUT} = 0$                                | 4             | 6   | 10                | mA   |         |

| V <sub>OUT</sub> | Output voltage         | 0 < I <sub>OUT</sub> < I <sub>OUT(max)</sub> | 23.5          | 24  | 24.5              | V    | 3.1 节   |

| I <sub>OUT</sub> | Output current         | 8 V < V <sub>IN</sub> < 36 V                 | 0             |     | 180               | mA   |         |

|                  |                        | 9 V < V <sub>IN</sub> < 36 V                 | 0             |     | 200               | mA   |         |

| h                | Efficiency             | P <sub>OUT</sub> >10%                        | 80            | 90  |                   | %    | 3.2 节   |

| Та               | Ambient<br>temperature | V <sub>IN</sub> = 24 V                       | -40           | 25  | 125               | °C   | 节 3.2.4 |

## 表 1. Key System Specifications

<sup>(1)</sup> Transients on V<sub>IN</sub> must not exceed 75 V – V<sub>OUT</sub>. In this reference design, the absolute max for V<sub>IN</sub> is 51 V.

## 2 System Overview

## 2.1 Block Diagram

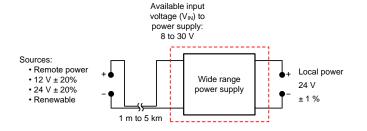

1 shows a typical use case for this type of power supply. Mobile equipment like cars, trucks, or diesel generators can have 12 V or 24 V available. The unit can also receive its power through a long supply wire or from renewable energy sources. In all these cases, a variable input voltage needs to be converted into a fixed output voltage. This reference design performs the task effectively and in a small form factor.

图 1. Typical Use Case

## 2.2 Highlighted Products

## 2.2.1 LM5001

The LM5001 high-voltage switch-mode regulator features all of the functions necessary to implement efficient high-voltage boost, flyback, SEPIC, and forward converters, using few external components. This easy-to-use regulator integrates a 75-V N-Channel MOSFET with a 1-A peak current limit. Current mode control provides inherently simple loop compensation and line-voltage feed-forward for superior rejection of input transients. The switching frequency is set with a single resistor and is programmable up to 1.5 MHz. The oscillator can also be synchronized to an external clock. Additional protection features include:

- Current limit

- Thermal shutdown

- Undervoltage lockout

- Remote shutdown capability

## 2.3 System Design Theory

The SEPIC can convert a wide range of input voltage to a fixed output voltage where the input voltage can range from below to above the output voltage.

Classical SEPIC implementations require two inductors that are quite difficult to control. The output inductor can easily get into resonance with the primary-to-secondary coupling capacitor. This resonance has then to be eliminated by the feedback and compensation network.

Off-the-shelf coupled inductors eliminate these problems. Such inductors have a similar cost structure as the standard single inductors. When the SEPIC is constructed with a coupled inductor, the coupling makes the inductor behave like the one of a boost converter. The inductor then has a reduced tendency to resonate and the feedback scheme gets much simpler. The only possible resonances left are circulating currents in the coupling capacitor in combination with the leakage inductance of the inductors, both of which reduce efficiency.

System Overview

www.ti.com.cn

To avoid this effect, keep the parallel resonance of the coupling capacitor and the leakage inductance significantly below the switching frequency. A feasible starting point is to use a coupling capacitor, which resonates with the leakage inductance of the coupled inductor at less than half of the switching frequency. A very detailed analysis of the coupled inductor SEPIC can be found in the article "Designing DC/DC converters based on SEPIC topology" within the *Analog Applications Journal of Fourth Quarter, 2008.*

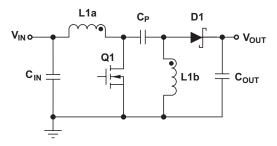

图 2 shows the principle circuit diagram of a SEPIC.

图 2. Principle Circuit Diagram of Coupled Inductor SEPIC

The advantage of the SEPIC is its simpler structure compared to a buck-boost converter and its more deterministic behavior under different load and input voltage conditions. The SEPIC has a better cost structure and efficiency because only one transistor is switching compared to four in a buck-boost converter. Therefore, the real estate is smaller when doing a higher power implementation with discrete transistors. A side effect is that there is no primary snubber network for the leakage inductance needed like it would be in a flyback. The energy in the primary leakage inductance can discharge through capacitor  $C_P$  into the secondary side and is therefore reused. The lack of a snubber increases efficiency. For the same reason, there is also no snubber needed for the rectifier diode on the secondary side, which further improves efficiency.

The design of this SEPIC controller depends on the optimization target priorities. The SEPIC can be optimized to a combination of the following targets:

- High efficiency

- Low output ripple

- Fast load transient response

- $V_{OUT}$  to  $V_{IN}$  ratio

- Small form factor

- Low cost

The tradeoffs are the inductance, the switching current, the switching losses, the mechanical size of the inductor, the output capacitance, and indirectly cost. If maximum efficiency is the main goal, then the frequency must be as low as possible to keep switching losses in the LM5001 low and reduce the core losses in the inductor. Lower frequency results in larger inductance to keep peak currents low. This frequency also results in a larger output capacitor value to keep output ripple in the required range, which in turn has an impact on the load transient response behavior of the circuit. A larger inductance at same load current finally has an impact on the mechanical size and cost. A larger V<sub>OUT</sub> to V<sub>IN</sub> ratio affects the inductor and the switcher because it increases the switching current. For example (assuming 100% efficiency), if the circuit has a V<sub>IN</sub> of 24 V and a V<sub>OUT</sub> of 24 V, then the average switcher current during ontime is 2× the output current. The inductor sees the same current. If the circuit gets 18 V, then this current becomes 2.33× the output current. Once V<sub>IN</sub> reaches 12 V, this current is already 3× the output current, and at V<sub>IN</sub> of 8 V, it is 4×. The maximum possible input current depends on the minimum peak current of the LM5001 regulator. For a low input voltage under 8 V, the maximum output power in this reference design drops below 4 W.

## 3 Hardware, Testing Requirements, and Test Results

## 3.1 Required Hardware

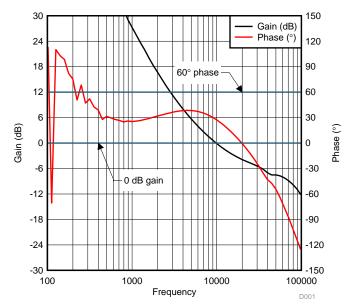

TI published an EVM that can be modified in a few steps to implement a coupled inductor SEPIC. Find more details about the board on TI.com by entering the search term "Im5001nisoeval". All the documentation is available and the board can be ordered in the TI store.

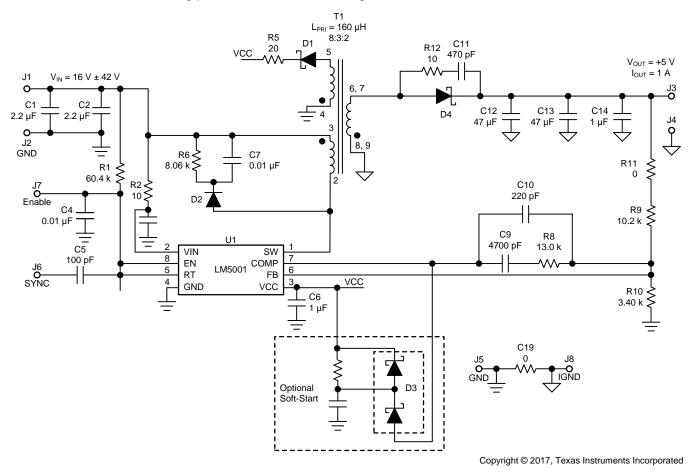

图 3. Circuit Diagram of Non-Isolating Flyback Evaluation Board

## 3.1.1 Build Instructions

The following step-by-step instructions convert the EVM into a coupled inductor SEPIC with a  $V_{IN}$  range from 8 V to 36 V and a fixed output voltage of 24 V.

- 1. Remove components: R3, D2, R12

- 2. Change components: R10 = 562  $\Omega,$  C12 = C13 = 4.7  $\mu F$  at 35 V, C14 = 0.1  $\mu F$  at 35 V, D4 = 60-V Schottky

- Replace T1 with a 220-µH coupled inductor from Würth (744870221) or Coilcraft (KLMSD1260-224) and add a 1-µF at 60-V low ESR capacitor from the primary-side switching node (pin 1 U1) to the secondary-side switching node (Schottky anode).

- 4. (Optional) To see the minimum components, if no transients > 75 V are expected on V<sub>IN</sub>, replace R2 with 0  $\Omega$  and remove C3. R1, R5, R6, C7, C11, and D1 can be removed as well.

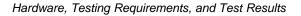

The modifications look clean and tidy. Do not cut the traces. With four wires and one capacitor soldered on the inductor, the effort for the modifications is limited. The loop compensation built from C9, C10, and R8 is left unchanged for the first tests.

The coupled inductor has to be connected as per [8] 4.

图 4. Photo of EVM After Modification

With these modifications, the board can now convert from 8 V to 36 V on J1, J2 into a stable 24 V on J3, J4. The board is short circuit proof and can be overloaded significantly without damage.

In  $\ddagger$  3.1.2, the power supply has to be optimized with regards to stability and regulation speed against load transients. This step involves the components C9, C10, and R8.

## 3.1.2 Loop Optimization

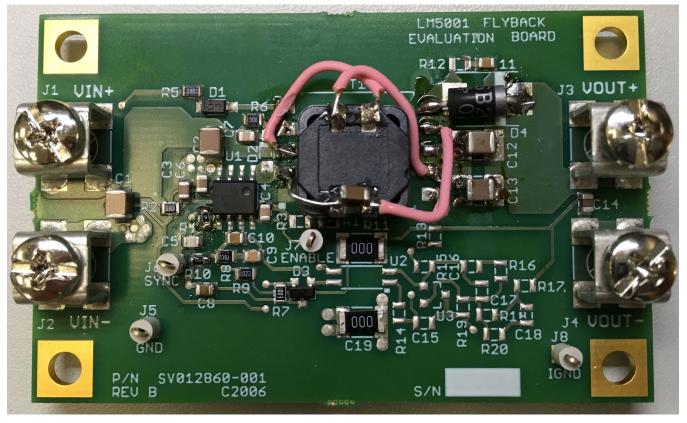

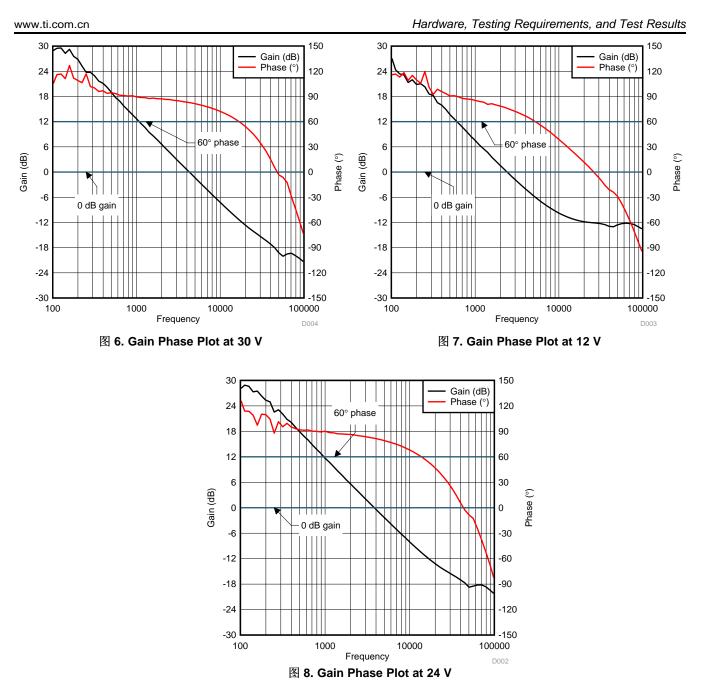

A SEPIC converter must optimize the feedback loop to get stability over the range of specified input voltages and loads. This optimization can be done by injecting a distortion into the feedback loop and checking the response on the generated output voltage. The measurement instrument used for this purpose is a Venable Instruments 3120 frequency response analyzer. 🛛 5 shows the gain and phase before loop optimization.

## 图 5. Gain Phase Plot Recorded by Frequency Response Analyzer From Venable Instruments

S shows that the phase margin at a 0-dB gain is only 30 degrees. A good phase margin for stability over load variances, component tolerances, temperature, and aging is 60 degrees. The change of R8 from 13 kΩ to 4.02 kΩ reduces the gain by a factor of 3, which corresponds to a down shift of the gain plot by 8 dB. Increasing C9 gradually from 4.7 nF to 220 nF shifts the filter zero to lower frequencies and shows a continuous improvement on the phase margin. The next three diagrams show the phase and gain at different input voltage conditions. With C9 set at 220 nF, the margin is always greater than 60 degrees at a 0-dB gain. The loop bandwidth is now 2.5 kHz at V<sub>IN(min)</sub>.

A margin of greater than 60 degrees satisfies the requirement for stable operation. This margin provides enough guardband for aging, temperature variation, and component variations. If the amount of guardband is not needed, then increase the gain up to 6 dB for a faster transient response.

## 3.1.3 Calculations and Inductor Selection

This section shows the calculations for the critical components. These formulas create a starting point to optimize the design. The main prerequisite for this reference design is using an off-the-shelf coupled inductor with a 1:1 winding ratio. Any circuit change for one of the various optimizations requires a revisit of the loop optimization.

### Hardware, Testing Requirements, and Test Results

For the best reliability and low electromagnetic influence (EMI), it is essential to select an inductor with a saturation current larger than the current limit of the switching device. When the inductor is saturated, the current can rise very quickly because only leakage inductance is present. The LM5001 has a response time of 200 ns. The resulting peak current can be calculated with the equation below.  $I = t \times V L$ (1)

With an input voltage of 36 V and a leakage inductance of 1 µH the current increases up to 7 A within 200 ns. Such a current transient can induce undesired voltages on traces and within the device. Therefore, it must be avoided during normal operation.

The following is a list of possible optimization targets as shown in 2.3  $\ddagger$ :

- High efficiency

- Low output ripple

- Fast load transient response ٠

- V<sub>OUT</sub> to V<sub>IN</sub> ratio

- Small form factor

- Low cost

The following calculations are for the different optimization targets. This reference design uses the LM5001, which has a maximum current limit of 1200 mA and a minimum current limit of 0.8 A. All optimizations except the input range optimization use a minimum input voltage of 8 V and a maximum input voltage of 36 V. The output voltage is 24 V and the maximum output current is 0.2 A. Input voltage and output voltage determine together the switching duty cycle:  $\mathsf{D} = \mathsf{V} \mathrel{\mathsf{O}} \mathrel{\mathsf{U}} \mathsf{T} \mathrel{\mathsf{V}} \mathrel{\mathsf{I}} \mathrel{\mathsf{N}} + \mathsf{V} \mathrel{\mathsf{O}} \mathrel{\mathsf{U}} \mathsf{T}$ (2)

Subsequent calculations need the minimum and maximum duty cycle based on the input voltage range. The duty cycle at  $V_{\text{IN}(\text{min})}$  calculates as 0.75 and at  $V_{\text{IN}(\text{max})}$  it is 0.4.

At an output power of 4 W (24 V × 0.167 A), the input current at minimum input voltage of 8 V is 0.5 A. At a maximum input voltage of 36 V, the current is 0.11 A. With IAVG=IOUT1-D (3)

the average inductor current  $I_{AVG}$  is 0.67 A at  $V_{IN(min)}$  and 0.28 A at  $V_{IN(max)}$ .

#### 3.1.3.1 **Optimization for Efficiency**

If the main goal is efficiency, then keep the frequency low and the current ripple ratio (r) between 0.3 and 0.5. This ratio minimizes switching losses and core losses. The calculation starts with a frequency of 200 kHz with (4)

IRIP=r × IPK

The ripple current can have a value of 320 mA based on an LM5001 minimum peak current of 0.8 A and r = 0.4.

The average inductor current based on the peak current is IAVG=IPK-IRIP2=IPK-r×IPK2=IPK×1-r2

and has 0.64 A. This measurement is below the required inductor current for a maximum power of 4 W at a minimum input voltage of 8 V. Therefore, it is not possible to achieve maximum efficiency and supporting V<sub>IN(min)</sub> = 8 V at a power level of 4 W. For this optimization target, the specification of V<sub>IN(min)</sub> needs an increase to 10 V. At V <sub>IN(min)</sub> = 10 V, the required average inductor current is only 0.57 A. The difference from 0.57 A to 0.64 A is large enough for a stable output voltage at 89% efficiency.

(5)

(7)

(8)

(11)

(14)

The next step is to calculate the on- and off-times based on the cycle time and duty cycle. The calculation is only needed for  $V_{IN(min)}$  because at this input voltage the inductor current can become critical: t C Y C = 1 f S W (6)

The on-time of the switch is: t O N = D x t C Y C

The off-time of the switch is: t O F F = 1 - D x t C Y C

With these equations, it is possible to calculate the required inductance:  $L = t O N \times V I N I R I P = D \times t C Y C \times V I N r \times I P K = V I N \times V O U T V I N + V O U T f s w \times r \times I P K$ (9)

An inductance of 110  $\mu$ H is required for r = 0.4. The ideal output power is then 4.5 W at V<sub>IN</sub> = 10 V, or 4 W assuming efficiency of 90%. An r of 0.44 allows this design to use a standard inductor of 100  $\mu$ H and still maintain the output power at 4 W.

## 3.1.3.2 Optimization for Transient Response

If the desired design behavior is fast load transient response, then the energy transfer per switching cycle must be maximized. In this case, the switching circuit can quickly add energy if the load increases. If the load decreases, the regulation goes faster if less energy is in the inductor. Therefore, the stored energy in the inductor must be minimized. Both cases can be achieved at the same time by increasing the current ripple ratio. The transient response improves further if the switching frequency is higher as well.

This method has a negative side effect. A larger current ripple ratio decreases the average inductor current because the peak current is capped. Therefore, the minimum input voltage must increase for a given power level. The calculations start with r = 1 and a power level of 4 W. The increased ripple current requires an increased switching frequency by the same factor for a constant output voltage ripple. f N E W r N E W = f O L D r O L D (10)

A frequency of 500 kHz is needed to fulfil the equation for r = 1. Alternatively, the output capacitor can increase.

公式 11 shows that with r = 1 the average inductor current can be maximum 0.4 A. I A V G = I P K × 1 - r 2

To achieve 4.5 W (which is needed for 4-W output power at 90% efficiency), a certain  $V_{IN(min)}$  is needed. IOUT = POUTVOUT; IAVG = IOUT1-D; D = VOUTVOUT + VIN (12) VIN = IAVG × VOUT2IAVG × VOUT - POUT (13)

For r = 1 and P<sub>OUT</sub> = 4.5 W, V<sub>IN(min)</sub> is 21.2 V. The required inductor value is based on  $\Delta$  $<math> \pm$  14, which calculates to 28  $\mu$ H. Relaxing r slightly to 0.9 requires V<sub>IN(min)</sub> of 18 V, a switching frequency of 450 kHz, and an inductor value of 31.8  $\mu$ H.

If  $V_{IN(min)}$  and  $P_{OUT}$  are given, then  $\Delta \vec{x}$  15 calculates the largest possible current ripple ratio. r = 2 - 2 × P O U T V O U T × I P K × 1 - V O U T V O U T + V I N (15)

For example, with a  $V_{IN(min)}$  of 15 V, r can be up to 0.78.

The faster transient response requires one final step. These optimizations shift the so-called right half plane zero (RHPZ) to a higher frequency. Because of this, the loop filter bandwidth can also increase, which leads to the better transient response.

#### 3.1.3.3 **Optimization for Output Ripple**

The amount of output ripple depends on the current flow in the output capacitor, the capacitor value and the on-time (during which is no energy transfer into the output capacitor). This relationship is shown in  $\Delta$ 式 16:

$VCAP = VRIP = IOUT \times tONC$

The output voltage ripple reduces at a given output current if ton decreases or if the output capacitance increases. For less ripple, one option is to increase the frequency to reduce efficiency. The designer can also increase the output capacitor value, which increases size and cost. The following formulas present these two options.

$$t O N = C \times V R I P I O U T$$

If the design uses a load capacitor value of 10 µF and needs to support a ripple of less than 25 mV at an output current of 188 mA (4.5 W), then the on-time needs to be less than 1.3 µs. For V<sub>IN(min)</sub>, this corresponds to a switching frequency of 580 kHz. (18)

$C = tON \times IOUTVRIP$

For a switching frequency of 200 kHz, an output current of 188 mA (4.5 W), and a required ripple of less than 25 mV at V<sub>IN(min)</sub>, a capacitor value of 28 µF is needed. With a value of 3 × 10 µF, the ripple voltage is less than 23 mV.

(17)

(16)

## 3.1.3.4 Optimization for Large V<sub>OUT</sub> to V<sub>IN</sub>

There are different possibilities for a larger ratio from  $V_{IN}$  to  $V_{OUT}$ . For a given inductor peak current, it is possible to decrease the current ripple ratio (r). This adjustment elevates the average current in the inductor so the input voltage can decrease maintaining the same power level. The decreased r can stem from increased inductance or increased switching frequency. The drawback of an increased inductance is the reduced transient response.

The only viable alternative with this reference design is to accept a lower power level when  $V_{\rm IN}$  approaches  $V_{\rm IN(min)}.$

r = 2 - 2 × P O U T V O U T × I P K × 1 - V O U T V O U T + V I N

With  $P_{OUT} = 4.5 \text{ W}$ ,  $I_{PK} = 0.8 \text{ A}$ ,  $V_{OUT} = 24 \text{ V}$ , and  $V_{IN} = 8 \text{ V}$ , r is 0.125. Reducing  $V_{IN}$  from 8 V to 7.8 V gives an r value of 0.088. This result shows that the ratio  $V_{IN(min)}$  versus  $V_{OUT}$  is at the limit for this switching device.

Based on r, it is now possible to calculate the inductor or the frequency. The inductor value for an r of 0.088 at 200 kHz is:

$L = V | N \times V O U T V | N + V O U T f s w \times r \times | P K$

(20)

(21)

(19)

which results in 420  $\mu$ H. The frequency for an r of 0.088 with an inductance of 100  $\mu$ H f s w = V I N × V O U T V I N + V O U T L × r × I P K

would be 820 kHz. The same with r = 0.125 gives 294  $\mu$ H or 580 kHz. If V<sub>IN(min)</sub> needs to be significantly below 8 V, then a stronger switching solution is necessary. A combination of switching controller and external MOSFET transistor provides the required high current at the cost of slightly more complexity.

## 3.1.3.5 Optimization for Form Factor

The optimization for a smaller form factor follows the same rules as  $\ddagger$  3.1.3.6.

## 3.1.3.6 Optimization for Low Cost

Main cost drivers are the size and quality of the output capacitor and the dimensions of the inductor. To reduce cost, make the inductance and the capacitance as small as possible. The switching frequency and r need to increase. As a consequence, the minimum voltage needs to increase or the power level must decrease. In all cases, efficiency lowers because of the higher switching speed. 公式 20 also be used for this optimization:

$L = V | N \times V O U T V | N + V O U T f s w \times r \times | P K$

With a switching frequency of 500 kHz and an r of 0.8, the inductor size reduces from 100  $\mu$ H to 15  $\mu$ H and V<sub>IN(min)</sub> increases from 8 V to 16 V. The size of the inductor can then shrink from 12.5 mm × 12.5 mm × 8.5 mm to 8 mm × 8 mm × 2 mm. With the higher frequency, the output capacitor can get smaller from 10  $\mu$ F to 4  $\mu$ F.

## 3.2 Testing and Results

## 3.2.1 Input Voltage and Output Load Test

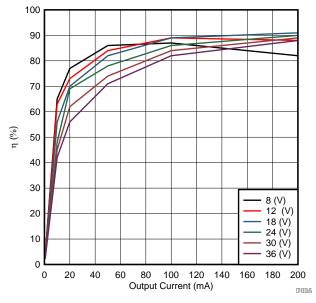

In this test, six different input voltages are applied to the board: 8 V, 12 V, 18 V, 24 V, 30 V, and 36 V. At each voltage, an output load current in six steps is applied: 0 mA, 10 mA, 20 mA, 50 mA, 100 mA, and 200 mA. For each of the input voltage and output load combinations, the input current and output voltage is measured. 🛛 9 shows the measurement results.

图 9. Efficiency versus Output Current

## 3.2.2 Input Voltage and Maximum Load Test

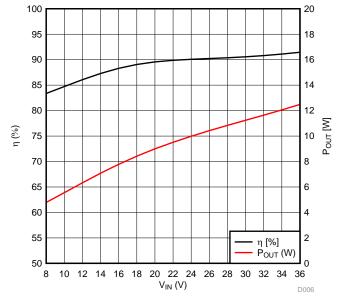

In this test, the input voltage is varied from 8 V to 36 V in 2-V steps. For each step, the maximum power is measured and the corresponding efficiency.

$\boxtimes$  10. Maximum Power and Efficiency versus V<sub>IN</sub>

The result of this test shows that the design can also be used for higher power if the input minimum voltage is increased. For a minimum voltage of 17 V, the design delivers 8 W with an efficiency of 88%.

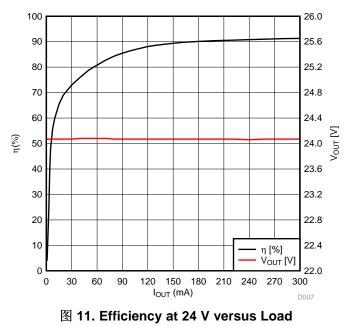

## 3.2.3 Output Current and Efficiency Test

In this test, the input voltage is set to a fixed 24 V. The output current is varied from 0 to 300 mA in 20-mA steps.

At a  $V_{IN}$  of 24 V, the design shows greater than 80% efficiency at an output current of more than 60 mA (36% of maximum load). At this  $V_{IN}$ , it is possible to overload up to 10 W without degradation.

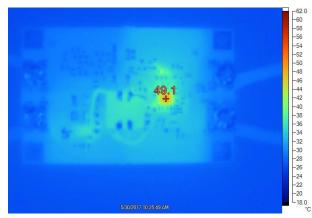

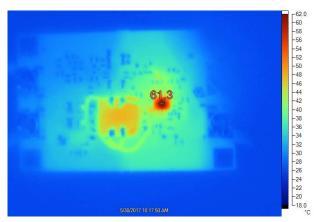

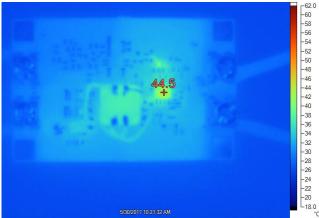

## 3.2.4 Thermal Images

The following images show the heat distribution on the test board. The main contributor of heat is the LM5001 device. At the maximum load and minimum input voltage  $V_{IN}$ , the switching transistor in the device has maximum current. This current is visible in the thermal image plots as the warmest spot. The environment temperature is 25°C, which means the device had a temperature rise of 36.3°C in this measurement. The first two images show the thermal behavior of the circuit at the upper and lower extremes of  $V_{IN}$ , which are 36 V and 8 V, respectively. The third image shows the measurement at a nominal  $V_{IN}$  of 24 V. At the higher voltages, the switching current of the device is lower, so the temperature rise is smaller as well.

图 12. Thermal Image at  $V_{IN}$  = 36 V

图 13. Thermal Image at  $V_{IN} = 8 V$

图 14. Thermal Image at V<sub>IN</sub> = 24 V

The thermal images also show the possibility for improvement at light load conditions. The one warm spot above the device is the resistor of the output divider, which has the highest voltage drop. Increasing this resistance can lift the light load (10% load) efficiency.

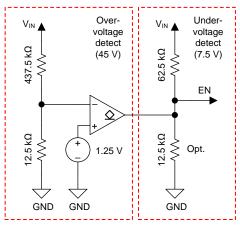

## 4 Design Notes

The sum of input voltage and output voltage in this reference design is limited to the maximum switch voltage. This voltage is 75 V in the LM5001 regulator. For an output voltage of 24 V, the input voltage must therefore be lower than 51 V. It is possible to make this design immune against destruction from voltages between 51 V and 75 V. For this immunity, the switch must stop switching while the input voltage is too large. A circuit like the one in 🚯 15 can disable the switch above a certain input voltage (in this case, 45 V). The circuit checks V<sub>IN</sub> against a reference voltage (in this case, 1.25 V) and pulls its open drain output low when V<sub>IN</sub> is too high. This disables the LM5001 regulator.

For proper operation, a pullup resistor is required if the output leakage current of the comparator is larger than the built-in 6-µA current source of the LM5001 regulator. The pullup resistor can be part of the undervoltage lockout circuit. The designer must consider a time for the disable circuit to become effective. This time is approximately the duration of one clock cycle in the LM5001 plus the time the comparator needs to detect the overvoltage condition. For a 250-kHz switching frequency, this takes around 5 µs assuming a 1-µs detection time. With a disable threshold set at 45 V, the circuit can then protect against overvoltage conditions, which have less than a 1-V/µs rising voltage slope. This slope is sufficient for standard PLC power supplies.

The LM5001 has two built-in undervoltage lockout circuits. One has a fixed  $V_{IN}$  voltage threshold level of 2.8 V (typical). The other one is programmable with an external voltage divider. These circuits can help to prevent abnormal high input currents on  $V_{IN}$  associated with low input voltage conditions. When the voltage ramps during start-up, the current can be higher than at normal operation because the device tries to pull the full power needed to generate the output voltage. The designer has two options to limit this increased current:

- 1. Soft start: This option generates a defined voltage ramp at the output of the converter. If this ramp is aligned with the input ramp, then excessive currents do not occur. This method works best when the designer knows the exact input and output conditions. For more details, see *LM5001x High-Voltage Switch-Mode Regulator*.

- 2. Undervoltage lockout: This option starts the LM5001 only once a certain input voltage level is available. This method helps to prevent operation at input voltage levels where too high currents are needed to achieve load regulation. It is simple to implement in the LM5001 regulator. 图 15 shows the circuit.

图 15. Principle Circuit for Disabling LM5001 at  $V_{IN}$  > 45 V and  $V_{IN}$  < 7.5 V

### Design Files

## 5 Design Files

This reference design comes with a set of design files to enable a quick and flawless conversion into other designs. These design files are located in the TIDA-01498 design folder.

The design files consist of schematics, BOM, an Altium Designer project, and the Gerber files of the LM5001 flyback evaluation board.

## 6 Related Documentation

- 1. Texas Instruments, *Designing DC/DC converters based on SEPIC topology*, Article from Analog Applications Journal 4Q 2008

- 2. Texas Instruments, LM5001 Non-Isolated Flyback Evaluation Board User's Guide

## 6.1 商标

E2E, Fly-Buck are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

## 7 About the Author

**INGOLF FRANK** is a systems engineer in the Texas Instruments Factory Automation and Control Team, focusing on PLC I/O modules. Ingolf works across multiple product families and technologies to leverage the best solutions possible for system level application design. Ingolf earned his electrical engineering degree (Dipl. Ing. (FH)) in the field of information technology at the University of Applied Sciences Bielefeld, Germany in 1991.

#### 有关 TI 设计信息和资源的重要通知

德州仪器 (TI) 公司提供的技术、应用或其他设计建议、服务或信息,包括但不限于与评估模块有关的参考设计和材料(总称"TI 资源"),旨在 帮助设计人员开发整合了 TI 产品的 应用; 如果您(个人,或如果是代表贵公司,则为贵公司)以任何方式下载、访问或使用了任何特定的 TI 资源,即表示贵方同意仅为该等目标,按照本通知的条款进行使用。

TI 所提供的 TI 资源,并未扩大或以其他方式修改 TI 对 TI 产品的公开适用的质保及质保免责声明;也未导致 TI 承担任何额外的义务或责任。 TI 有权对其 TI 资源进行纠正、增强、改进和其他修改。

您理解并同意,在设计应用时应自行实施独立的分析、评价和 判断, 且应全权负责并确保 应用的安全性, 以及您的 应用 (包括应用中使用 的所有 TI 产品))应符合所有适用的法律法规及其他相关要求。你就您的 应用声明,您具备制订和实施下列保障措施所需的一切必要专业知 识,能够 (1) 预见故障的危险后果,(2) 监视故障及其后果,以及 (3) 降低可能导致危险的故障几率并采取适当措施。您同意,在使用或分发包 含 TI 产品的任何 应用前, 您将彻底测试该等 应用 和该等应用所用 TI 产品的 功能而设计。除特定 TI 资源的公开文档中明确列出的测试 外,TI 未进行任何其他测试。

您只有在为开发包含该等 TI 资源所列 TI 产品的 应用时, 才被授权使用、复制和修改任何相关单项 TI 资源。但并未依据禁止反言原则或其他 法理授予您任何TI知识产权的任何其他明示或默示的许可,也未授予您 TI 或第三方的任何技术或知识产权的许可,该等产权包括但不限于任 何专利权、版权、屏蔽作品权或与使用TI产品或服务的任何整合、机器制作、流程相关的其他知识产权。涉及或参考了第三方产品或服务的信 息不构成使用此类产品或服务的许可或与其相关的保证或认可。使用 TI 资源可能需要您向第三方获得对该等第三方专利或其他知识产权的许 可。

TI 资源系"按原样"提供。TI 兹免除对 TI 资源及其使用作出所有其他明确或默认的保证或陈述,包括但不限于对准确性或完整性、产权保证、 无屡发故障保证,以及适销性、适合特定用途和不侵犯任何第三方知识产权的任何默认保证。

TI 不负责任何申索,包括但不限于因组合产品所致或与之有关的申索,也不为您辩护或赔偿,即使该等产品组合已列于 TI 资源或其他地方。 对因 TI 资源或其使用引起或与之有关的任何实际的、直接的、特殊的、附带的、间接的、惩罚性的、偶发的、从属或惩戒性损害赔偿,不管 TI 是否获悉可能会产生上述损害赔偿,TI 概不负责。

您同意向 TI 及其代表全额赔偿因您不遵守本通知条款和条件而引起的任何损害、费用、损失和/或责任。

本通知适用于 TI 资源。另有其他条款适用于某些类型的材料、TI 产品和服务的使用和采购。这些条款包括但不限于适用于 TI 的半导体产品 (http://www.ti.com/sc/docs/stdterms.htm)、评估模块和样品 (http://www.ti.com/sc/docs/sampterms.htm) 的标准条款。

> 邮寄地址:上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2018 德州仪器半导体技术(上海)有限公司