# TI Designs: TIDA-01633

适用于交流/伺服驱动器的紧凑可编程 4mA 至 20mA 和 ±10V 模拟输出参考设计

# TEXAS INSTRUMENTS

#### 说明

本参考设计实现了一个适用于交流逆变器驱动器和伺服驱动器的小型双通道可配置模拟电压和电流输出模块。与使用多个运算放大器以及无源组件相比,使用集成式工业输出驱动器 XTR305 有助于实现小外形尺寸。您可以使用主机 MCU(如 C2000™MCU)将输出编程至±10V或 4mA 至 20mA,也可以使用跳线进行手动配置。错误标志和输出负载监控功能使其成为一款稳健的设计。同一通道还可配置为±10V或 4mA 至 20mA 的模拟输入。该接口适用于 C2000 Launchpad。

#### 资源

| TIDA-01633 | 设计文件夹 |

|------------|-------|

| XTR305     | 产品文件夹 |

| TVS1400    | 产品文件夹 |

| TLV431A    | 产品文件夹 |

| LMZM23601  | 产品文件夹 |

咨询我们的 E2E™ 专家

## 特性

- 两个单端可编程模拟电压和电流输出或电压输入

- 准确的 ±10V 电压输出和 0mA 至 20mA 电流输出 (在 -40°C 至 +85°C 温度范围内的典型校准误差低于 0.1%)

- ±10V 模拟输入(典型校准误差低于 1%)。必须使用外部 500Ω 电阻器将 4mA 至 20mA 电流输入转化为电压

- 保护、诊断和监控 特性:

- 通过 MCU 反馈实现稳健的短路电流限制输出以及短路和开路负载故障检测

- 可通过输出负载监控实现预测性维护

- 高 EMC 抗扰性: 满足针对 4kV ESD、2kV EFT 和 1kV 浪涌电流的 IEC61800-3 EMC 抗扰性要求(A 标准)

- 主机 MCU 接口支持 DAC 模拟输入信号和 PWM 输入信号

#### 应用

- 交流逆变器和变频驱动器

- 伺服、CNC 和机器人

- PLC 模拟输出模块

- 工业机器人 IO 模块

- 混合 IO 模块

System Description www.ti.com.cn

该 TI 参考设计末尾的重要声明表述了授权使用、知识产权问题和其他重要的免责声明和信息。

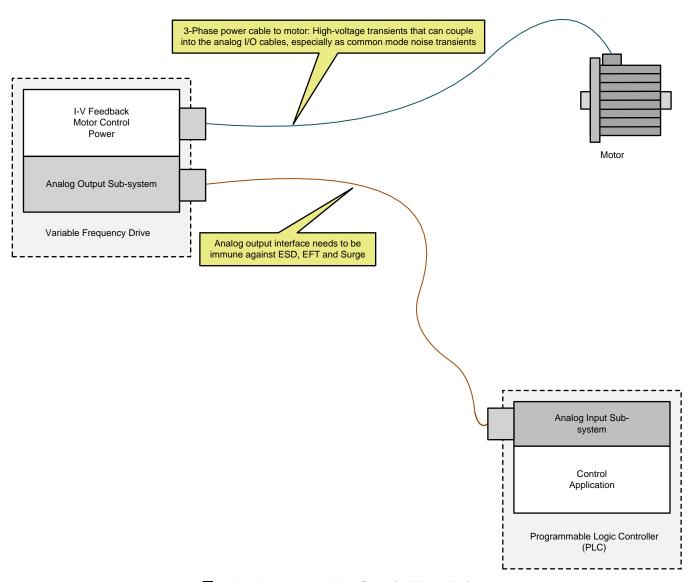

## 1 System Description

It is shows the components for a generic, analog output use-case. The motor is coupled to a load setup which requires an application specific torque speed profile. The application can be a fan, compressor, pump, conveyor system, machine tool, elevator system, and so forth. The variable frequency drive (VFD) controls the motor whose torque speed output has to match the load requirement. The VFD continuously monitors the speed and torque of the motor and provides feedback to the programmable logic controller (PLC). The PLC then closes the control loop by providing control set points to the VFD. This communication between the VFD and PLC occurs through analog signals. The analog output from the drive is connected to the analog input terminals of the PLC. Typically in a VFD, the analog output is either a 0-V to 10-V, ±10 V, or 4-mA to 20-mA signal. The connection is generally created by using shielded, twisted pair cables. The VFD analog output can also be programmed to transmit parameters such as motor phase current, DC-link voltage, motor shaft position, and so forth.

In an industrial environment the analog output cables run in close proximity to the motor power cables, high-voltage switchgear, and other electrical noise generating equipment. Opening and closing of contactors, startup of motors, short circuit failures, arc faults, and lightning strike surges can cause transient noise (EFT, Surge) to get coupled into the analog output cables. Handling cables, such as connecting and disconnecting cables from the analog output connectors, can cause ESD strikes. The analog output interface must be robust and capable of handling the noise transients.

www.ti.com.cn System Description

图 1. Analog Output Use Case in Motor Drives

System Description www.ti.com.cn

图 2. Discrete and Partially Discrete Analog Output Implementation Example

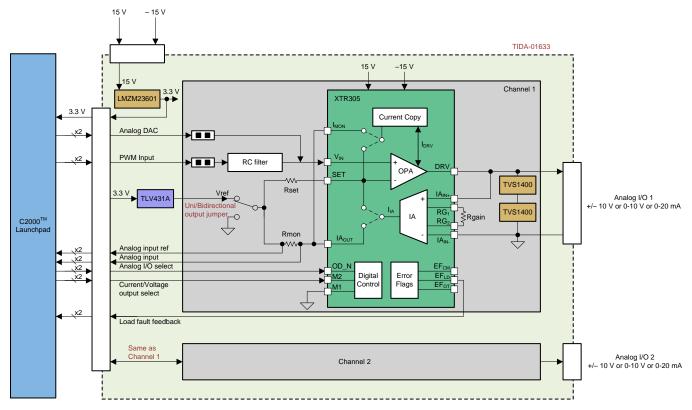

This TI Design implements a fully integrated solution using XTR305 analog output driver as shown in ₹ 3. The integrated solution enables a smaller solution form factor and reduced bill of material (BOM) size. There is no need for precise current sensing shunt resistors and shunt voltage measurement with high common-mode rejection amplifiers for the current output. The same analog output pin can be software programmed to current or voltage output without additional analog multiplexers. The inbuilt over-current limit protection and advanced diagnostic features enable detection of short circuit and open load faults which increases the drive reliability. It is also possible to use the same channel as analog input instead of output by disabling the XTR305 output drive stage and using the feedback channel of the device, which increases the functional flexibility of a single pin.

www.ti.com.cn System Description

图 3. XTR305 Based Fully Integrated Solution

This reference design demonstrates the following:

- · Small form factor and reduced BOM

- · Programmable analog voltage or current output

- Accurate output performance over temperature range

- High EMC immunity: Meets IEC61000-4-2 (ESD), IEC61000-4-4 (EFT) and IEC61000-4-5 (Surge) according to IEC61800-3

- Protection and diagnostic features

System Description www.ti.com.cn

## 1.1 Key System Specifications

## 表 1. TIDA-01633 Specifications

| SUB-SECTION                                | PARAMETER                                                | SPECIFICATIONS                                                                         | COMMENT                                                                                                                                                                    |  |

|--------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin Mode Selection                         | election Programmable Voltage or Current Output or Input |                                                                                        | Using 3.3-V CMOS/TTL interface to host MCU ovia jumpers (节 2.3.4)                                                                                                          |  |

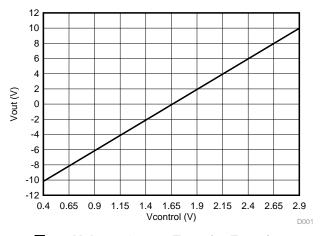

|                                            | Voltage Range                                            | ±10 V (图 23)                                                                           | Corresponds to input control voltage of 0.4 V to 2.9 V with gain of 8 V/V                                                                                                  |  |

|                                            | % FSR Error                                              | < 0.1% typical calibrated (图 25)                                                       | At 25°C                                                                                                                                                                    |  |

| Voltage Output                             | Temperature Drift                                        | < 175 ppm/K                                                                            | Mainly dominated by 1.65-V reference setting resistors. Selection of 25-ppm resistors will reduce drift to <100 ppm/K                                                      |  |

|                                            | Bandwidth                                                | 800 Hz (图 31)                                                                          |                                                                                                                                                                            |  |

|                                            | Rise Time                                                | ~ 1 ms (图 28)                                                                          | Faster rise time is possible by changing compensation capacitor and feedback capacitor                                                                                     |  |

|                                            | Current Range                                            | 0 mA to 20 mA (图 36)                                                                   | Corresponds to input control voltage of 1.65 V to 2.9 V with a gain of 16 mA/V                                                                                             |  |

|                                            | %FSR Error                                               | < 0.1% typical calibrated (图 38)                                                       | At 25°C                                                                                                                                                                    |  |

| Current Output                             | Temperature Drift                                        | <175 ppm/K                                                                             | Mainly dominated by 1.65-V reference setting resistors. Selection of 25-ppm resistors reduces the drift to <100 ppm/K                                                      |  |

|                                            | Bandwidth                                                | 800 Hz (图 44)                                                                          |                                                                                                                                                                            |  |

|                                            | Rise Time                                                | ~ 1 ms (图 41)                                                                          | Faster rise time is possible by changing compensation capacitor and feedback capacitor                                                                                     |  |

| Vallana lanut                              | Voltage Range                                            | ±10 V (₹ 53)                                                                           |                                                                                                                                                                            |  |

| Voltage Input                              | % FSR Error                                              | < 1% typical calibrated (图 55)                                                         |                                                                                                                                                                            |  |

| Power Supply                               | Voltage                                                  | ±15 V Nominal                                                                          | Can use ±12 V. Ensure that the maximum outpr<br>voltage swing is within the compliance voltage<br>swing range for the operating conditions                                 |  |

|                                            | Output Current Monitor<br>Feedback                       | ±1.238 V corresponding to ±20-mA load current                                          | During voltage output mode                                                                                                                                                 |  |

| Feedback                                   | Output Voltage Monitor<br>Feedback                       | 0 V to +1.238 V corresponding to 0 V to 10 V across the load                           | During current output mode                                                                                                                                                 |  |

| Interface to Controller                    | C2000 Launchpad Interface                                | 表 4 and 表 5 for pin assignments                                                        | LAUNCHXL-F28379D used for EMC testing                                                                                                                                      |  |

| Operating Conditions                       | Temperature Range                                        | -40 to +85°C                                                                           | The XTR305 is specified over the -40°C to<br>+85°C industrial temperature range and is<br>operational over the extended industrial<br>temperature range of -55°C to +125°C |  |

| Protection Features                        | Short Circuit Detection<br>Threshold                     | ±20 mA nominal                                                                         | During voltage output mode                                                                                                                                                 |  |

|                                            | Open Load Detection                                      | Output saturation into supply rails                                                    | During current output mode                                                                                                                                                 |  |

|                                            | Load Monitoring                                          | Output current and voltage feedback enables load monitoring for predictive maintenance |                                                                                                                                                                            |  |

| EMC (Shielded Cable)                       | ESD                                                      | 4 kV CD (节 3.2.5.1)                                                                    | Tested according to IEC61000-4-2                                                                                                                                           |  |

|                                            | EFT                                                      | 2 kV (节 3.2.5.2)                                                                       | Tested according to IEC61000-4-4                                                                                                                                           |  |

|                                            | Surge                                                    | 1 kV (节 3.2.5.3)                                                                       | Tested according to IEC61000-4-5                                                                                                                                           |  |

| Printed-Circuit Board (PCB)<br>Information | PCB Layer Stack                                          | 4 layer, 1-oz copper                                                                   |                                                                                                                                                                            |  |

|                                            | Laminate                                                 | FR4, high Tg                                                                           |                                                                                                                                                                            |  |

|                                            | PCB Thickness                                            | 1.6 mm                                                                                 |                                                                                                                                                                            |  |

|                                            | PCB Size                                                 | 25.4 mm × 24.13 mm                                                                     | Solution size - Area of PCB containing XTR305 circuit. Not including launchpad interface connectors                                                                        |  |

## 2 System Overview

#### 2.1 Block Diagram

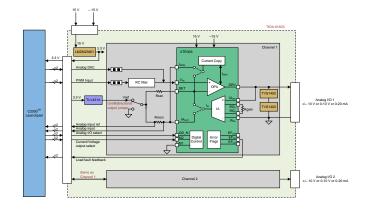

图 4. TIDA-01633 Block Diagram

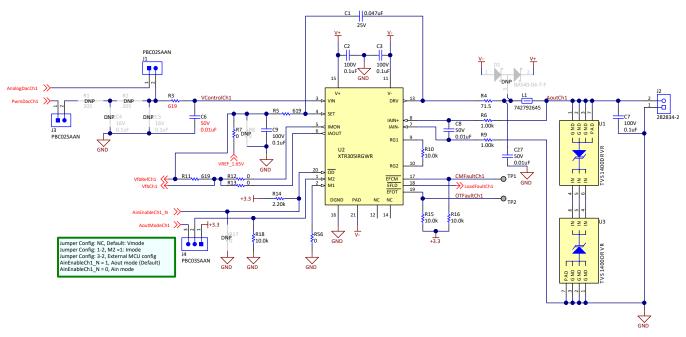

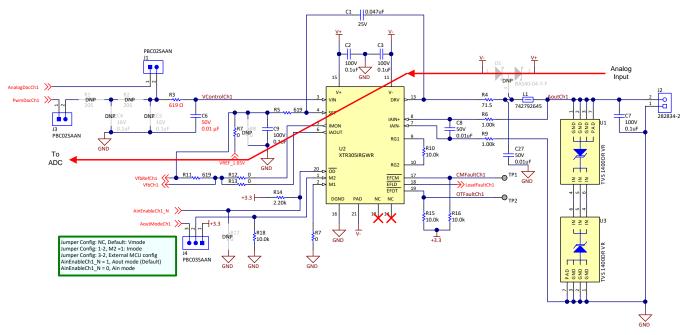

This reference design is a two-channel configurable current and voltage analog output.

4 shows channel 1 in detail and channel 2 with minimal detail, however, it is the same as channel 1. The key part is the XTR305, which is an industrial analog current or voltage output driver. The XTR305 takes an analog input control signal and drives a proportional analog output. The output is configured as current output if M2 is high, M1 is low, and voltage output if M2, M1 are low. In this design M1 is hardwired to ground and M2 can be driven either digitally through a C2000 Launchpad GPIO or is manual jumper configurable. The input to output gain of the XTR305 is set by Rset and Rgain. The gain components in this design are selected for ±10-V or ±20-mA output. Two TVS1400 transient voltage suppressor diodes are used in bidirectional configuration for protecting the analog output from surge and ESD strikes.

The input control voltage to the XTR305 can be an analog DAC or a PWM signal which can be selected through jumpers. If a PWM signal is selected it is converted to a DC signal by passing through a 3rd order RC filter before connecting to the device. An unipolar input signal drives a bipolar analog output, this requires the input stage of the XTR305 to be biased to an intermediate reference voltage Vref. This is generated by shunt regulator TLV431A from a 3.3-V input.

The load fault monitor output of the XTR305 is routed to the connector. This signal indicates a short-circuit fault on the output during current and voltage modes and an open-load fault during current output mode. The XTR305 is also capable of monitoring analog output load. The output current can be sensed on the analog feedback signal during voltage output mode and the output voltage is sensed during the current output mode.

If one of the analog output channels is not used, then it can be configured as an analog input channel. This is done by pulling the output disable pin OD\_N low which disables the XTR305 output drive and puts it in high-impedance mode. The M2 pin is made high to connect the instrumentation amplifier output IAout to the analog feedback channel. Analog voltage inputs (±10 V) can be sensed directly but the analog current inputs need to be converted to voltage by adding an external burden resistor. This feature improves the flexibility of a single analog I/O pin.

The pin allocation of the connectors is compatible with a C2000 Launchpad. The board requires an external ±15-V supply for powering the XTR305, which drives the analog outputs. An LMZM23601 DC/DC converter module is used to generate 3.3 V from 15 V. This 3.3 V is used for powering the Launchpad, if used, and for interfacing the open collector fault monitor signals to the Launchpad GPIO's.

## 2.2 Highlighted Products

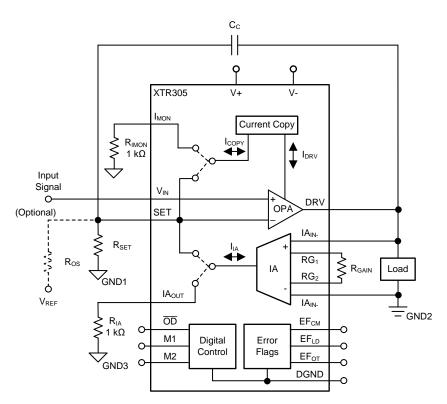

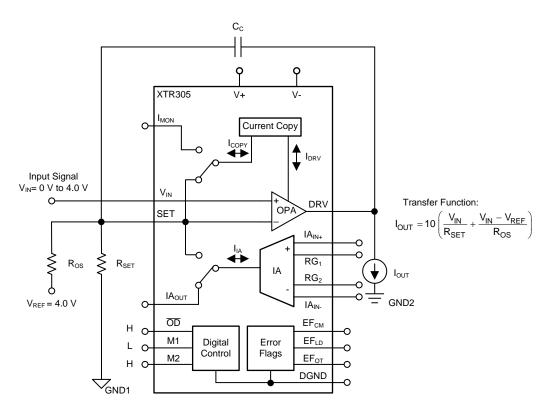

#### 2.2.1 XTR305

The XTR305 is a complete output driver for cost-sensitive industrial and process control applications. The output can be configured as current or voltage by the digital I/V select pin. No external shunt resistor is required. Only external gain-setting resistors and a loop compensation capacitor are required.

The separate driver and receiver channels provide flexibility. The instrumentation amplifier can be used for remote voltage sense or as a high-voltage, high-impedance measurement channel. In voltage output mode, a copy of the output current is provided, allowing calculation of load resistance.

The digital output-selection capability, error flags, and monitor pins make remote configuration and troubleshooting possible. Fault conditions on the output and on the IA input, as well as over-temperature conditions are indicated by error flags. The monitoring pins provide continuous feedback about load power or impedance. For additional protection, the maximum output current is limited and thermal protection is provided.

图 5. Functional Block of XTR305

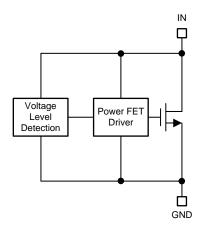

#### 2.2.2 TVS1400

The TVS1400 robustly shunts up to 43 A of IEC 61000-4-5 fault current to protect systems from high-power transients or lightning strikes. The device offers a solution to the common industrial signal line EMC requirement to survive up to  $\pm 2$  kV IEC61000-4-5 open circuit voltage coupled through 42- $\Omega$  impedance. The TVS1400 uses a unique feedback mechanism to ensure precise flat clamping during a fault, assuring system exposure below 20 V. The tight voltage regulation allows designers to confidently select system components with a lower voltage tolerance, lowering system costs and complexity without sacrificing robustness.

The TVS1400 is available in a small 2 mm × 2 mm SON footprint which is designed for space constrained applications offering a 70% reduction in size compared to industry standard SMA and SMB packages. The extremely low device leakage and capacitance has a minimal effect on the protected line.

图 6. Functional Block of TVS1400

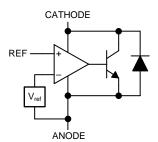

#### 2.2.3 TLV431A

The TLV431A device is a low-voltage, 3-terminal adjustable voltage reference with specified thermal stability over applicable industrial and commercial temperature ranges. The typical output impedance is  $0.25~\Omega$ , and the output voltage can be set to any value between Vref (1.24 V) and 6 V with two external resistors. The devices are excellent replacements for low-voltage Zener diodes in many applications, including on-board regulation and adjustable power supplies, because of its active output circuitry, which provides a sharp turn-on characteristic.

图 7. Functional Block of TLV431A

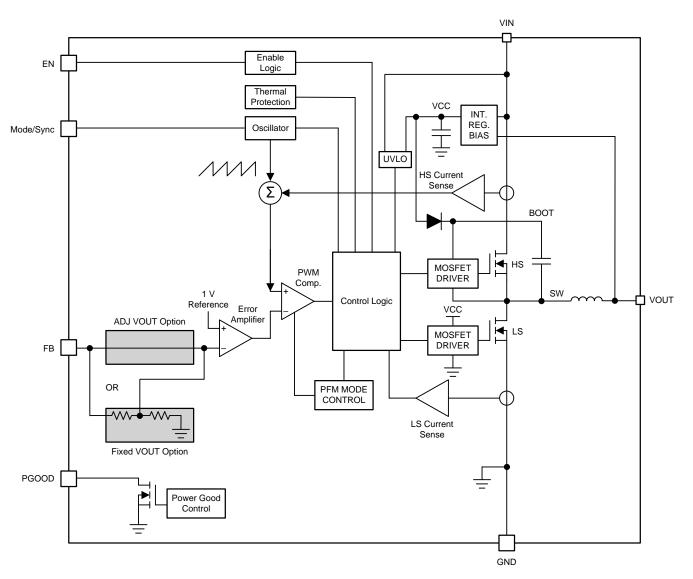

#### 2.2.4 LMZM23601

This device is a nano module specifically designed for space-constrained industrial applications and is available in fixed output voltage options of 5 V and 3.3 V or an adjustable output voltage option with a range of 2.5 V to 15 V. The LMZM23601 supports an input voltage range of 4 V to 36 V and can deliver up to 1000 mA of output current. This nano module is extremely easy to use, requiring only two external components for a 5-V or 3.3-V output design. All aspects of the LMZM23601 are optimized for performance driven industrial applications with space constrained needs. An open drain, Power Good option provides a true indication of the system status. This feature negates the requirement for an additional supervisory component, saving cost and board space. Seamless transition between PWM and PFM modes along with a no-load supply current of only 30  $\mu$ A ensures high efficiency and superior transient response for the entire load current range.

The device in this design powers the TLV431A based reference generation circuit, the pullups for XTR305 open collector signals, and the launchpad which can be used to control the analog output card.

图 8. Functional Block of LMZM23601

## 2.3 System Design Theory

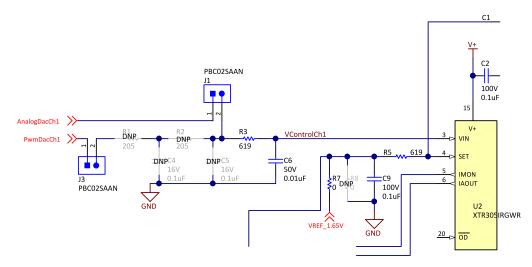

The XTR305 provides two basic functional blocks: an instrumentation amplifier (IA) and a driver that is a unique operational amplifier (OPA) for current or voltage output. During the current output mode a precision current mirror generates an exact 1/10th copy of the output current and this current is routed to the summing junction of the OPA to close the feedback loop. In the voltage output mode the IA amplifier senses the output voltage and feedback a current equal to 2 Vout/Rgain to the summing junction of the OPA to close the feedback loop.

- Select R5 for current output transfer function

- Select R10 for the voltage output transfer function

- Select EMC protection components

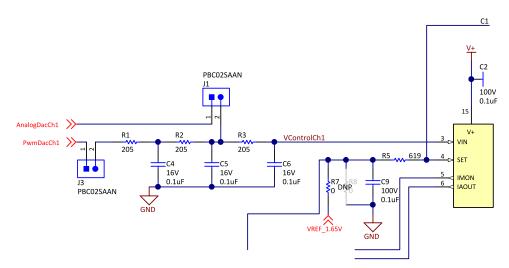

图 9. Analog Output Circuit

## 2.3.1 Current Output Mode

For this design a 0.4-V to 2.9-V control input is converted to a ±20-mA current output. As the output is bipolar and the input is unipolar, a reference bias voltage Vref is required on the input stage of the XTR305. The bias voltage selected is 1.65 V which means that ±1.25 V around 1.65 V translates to a ±20-mA current output.

The transconductance gain is set by R5 according to 公式 1

$$R5 = \left(\frac{10}{I_{outFSR}}\right) \times V_{inFSR} = \left(\frac{10}{40 \text{ mA}}\right) \times 2.5 = 625 \Omega$$

(1)

Select R5 = 619  $\Omega$  which gives an loutFSR of 40.38 mA (±20.19 mA)

The transfer function is given by equation: lout =  $(10/R5) \times (Vin-Vref)$

$$lout = \left(\frac{10}{R5}\right) \times \left(Vin - Vref\right)$$

(2)

During the current output mode it is possible to monitor the output load voltage, see 节 2.3.7.

## 2.3.2 Voltage Output Mode

A 0.4-V to 2.9-V control input is translated to a ±10-V voltage output. For unipolar to bipolar translation a 1.65-V bias voltage has been selected. This means that ±1.25 V around 1.65 V translates to a ±10-V output

The gain is set by R5 and R10 as per 公式 3

$$R10 = \frac{2 \times V_{outFSR} \times R5}{V_{inFSR}} = \frac{2 \times 20 \times 619}{2.5} = 9904 \Omega$$

(3)

Select R10 = 10 k $\Omega$  which gives an VoutFSR of 20.19 V (±10.10 V)

The transfer function is given by 公式 4

$$Vout = \frac{R10 \times (Vin - Vref)}{(2 \times R5)}$$

During the voltage output mode it is possible to monitor the output load current, see 节 2.3.7.

#### 2.3.3 EMC Protection Components

A drive analog output is typically connected to a PLC or motion controller using long cables in an industrial environment. These cables run along motor power cables and other noise generating sources like electrical contactors. The analog output has to be immune to transient noise signals like ESD, EFT and surge events which get coupled into the cable. The immunity to these noise transients can be quantified by passing tests as prescribed in IEC61800-3 (*Adjustable Speed Electrical Power Drive Systems – Part 3: EMC requirements and specific test methods*). IEC61800-3 points to IEC61000-4 for EMC test methods.

During each of these IEC61800-4 tests, the equipment under test (EUT) is monitored for performance deviations or total failure. Results are assigned to one of the four classes, see 表 2.

| GRADE   | DESCRIPTION                                                                                                                                                                         |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Class A | The EUT must continue to operate as intended. No loss of function or performance even during the test.                                                                              |

| Class B | Temporary degradation in performance during the test. The EUT continues to operate as expected after the test is complete.                                                          |

| Class C | Temporary degradation in performance during the test. The EUT needs to be manually restarted or put through a power off-on cycle to operate as expected after the test is complete. |

| Class D | Loss of function due to destruction of hardware.                                                                                                                                    |

表 2. EMC Test Performance Criterion

The IEC61000-4 transients have two main components:

- High frequency component (ESD, EFT) ESD events are typically caused by a person or insulator

touching the connector terminals or the cable. These are temporary fast transients and the energy

content is very low. EFT events are caused by sparks in the air due to the contactor closing and

opening; other sources are VFD motor power cables in which the voltage switches rapidly between

±DC bus voltage. These are typically a burst of fast transient pulses with low energy content which get

coupled into the cable.

- High energy component (Surge) Surge strikes get coupled into the cable during motor startup, lightning strikes, and so forth. These are slower transients with high energy content.

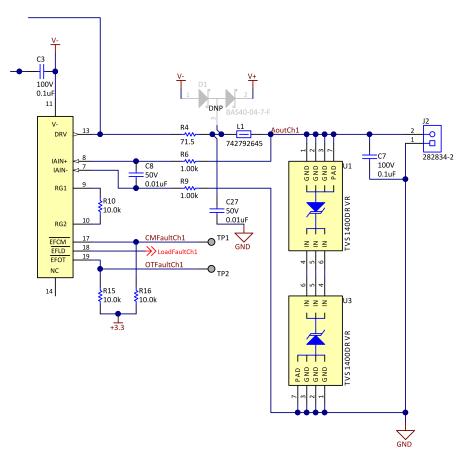

The goal of protection components is to attenuate and divert the transients from damaging the sensitive electronic components. This design uses a combination of transient energy attenuation and diversion, see 10.

(4)

图 10. Output EMC Protection Components

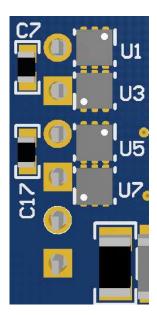

- Capacitor C7 0.1 μF capacitor is placed on the output terminal. This capacitor is the first line of defense which attenuates and slows down the transient noise signals entering the PCB in combination with the transient generators source impedance.

- TVS U1, U3 A bidirectional TVS diode is used to divert high voltage transients to earth. This design uses a symmetrical ±15-V supply voltage for the analog output driver. Therefore, two unidirectional TVS1400 diodes are placed back to back with opposite polarity. The working voltage of this diode is 14 V and the clamping voltage is ~18.4 V. A working voltage of 14 V means that during normal ±10-V operation the TVS diode does not interfere with the output. The output voltage increases to > 14 V only during fault conditions and this only increases the output leakage current into the TVS diode without deteriorating the TVS or reducing its reliability. The leakage current returns back to normal once the fault condition is removed. Increase in leakage current during fault conditions is not an issue with the analog output performance. The advantage of using TVS1400 is that it offers ~ 70% reduction in size when compared to standard SMB, SMA packages. The small size allows the device to be kept close to the input connector lowering the length of path fault current will take through the system when compared to larger protection solutions. It has extremely low leakage and capacitance which ensures minimal interference during normal operation. The clamping performance is extremely flat when compared to standard TVS diodes. The flat clamping voltage ensures that the downstream components are stressed to a lower extent which increases the system reliability. The TVS1400 clamping voltage has better stability across temperature when compared to standard TVS diodes. The TVS1400 has an IEC61000-4-2 contact discharge rating of ±21 kV and IEC61000-4-5 (8/20 us) surge rating of 43 A

Ferrite bead L1 – It has a DC resistance of 0.2 Ω and an impedance of 470 Ω at 100 Mhz. The ferrite

bead does not interfere in the normal analog output operating frequency region, which is typically <1

kHz, but provides a high impedance to high-frequency transients.</li>

- Capacitor C27 This 10 nF capacitor along with the ferrite bead further filters the noise transients.

- Resistor R4 If even after attenuation and diversion of transient energy there remains some residual energy this can be handled by the internal rail to rail clamp diodes on the DRV pin of XTR305. R4 limits the current into the clamping diodes. The clamping diodes can take a peak current of 50 mA. Therefore this resistor is selected to be (18.5 15.7)/50 mA = 56 Ω. A 71.5-Ω resistor is selected to provide sufficient margin.

- Schottky diode D1 This external rail-to-rail clamping schottky diode is not populated in this design. It

can be used if harsher EMC requirements are to met than tested in this design.

- Resistors R6 and R9 The instrumentation amplifier inputs are also connected directly to the output connector. The inputs have rail-to-rail clamping diodes inside the device. In case of overvoltage transients, the diodes clamp to the ±15-V power rails. The current is limited by external 1-kΩ resistors R6 and R9. Equal values cancel the offset due to instrumentation amplifier input bias currents.

- Capacitor C8 This additional 10-nF capacitor filters transient noise in the input signal to the instrumentation amplifier.

- R47, C33 and C34 are connected in parallel between the PCB ground and Earth terminals. These

components provide a low-impedance path for the high frequency transient currents to flow into the

earth but act as high impedance for the analog output operating frequency region.

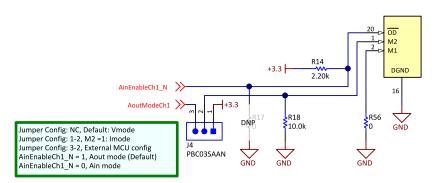

#### 2.3.4 Mode Selection

The analog output channel can be configured either digitally through MCU control or manually using jumpers according to 表 3. In this design, M1 is hardwired to GND and M2 is configurable.

**M2** М1 MODE **DESCRIPTION** L Vout Voltage output mode, Isc = 20 Н L lout Current output mode, Isc = 32 L Ext IA and IMON on external pins, Н Isc = 20 mAН IA and IMON on external pins, Н Ext

表 3. Analog Output Mode Selection

**Manual configuration:** By default the output is in voltage output mode as R18 pulls down M2 low. Connect J4 pins 1 and 2 for connecting M2 to 3.3 V, which changes output to current mode.

**MCU configuration:** Connect J4 pins 3 and 2 together. The mode is now controlled by signal AoutModeCh1, which is connected to Launchpad GPIO.

图 11. Analog Output Pin Mode Selection

#### 2.3.5 Analog Output Control Methods

The analog output magnitude can be controlled either by analog input control signal or a PWM signal. The default use case in this design is through analog control signal for which the pins 1 and 2 of connector J1 have to be jumpered together. The AnalogDacCh1 signal gets connected to the Vin pin of XTR305 through RC filter comprising of R3 and C6. R3 is selected to be equal to R5 to cancel out offsets due to input bias current of the XTR305 device.

图 12. Analog DAC Based Control of Analog Output

If the use case is PWM control then pins 1 and 2 of connector J3 have to be jumpered together. The PwmDacCh1 gets connected to the Vin pin of XTR305 through a third order cascaded RC filter comprising of (R1, C4), (R2, C5) and (R3, C6). In this case select R1 = R2 = R3 = R5/3 and C4 = C5 = C6 = 100 nF. The PWM frequency is 100 kHz. A duty cycle variation from 12.12% to 87.87% corresponds to 0.4 V to 2.9 V at the Vin pin.

图 13. PWM Control of Analog Output

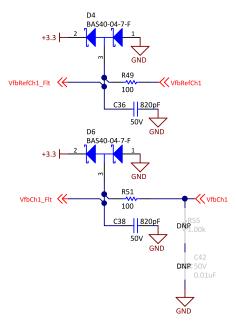

## 2.3.6 Analog Input

If an analog output channel is not used in the system it is possible to configure it as analog input. To do this pull down OD\_N control pin to low and make M2 low. This disables the output DRV pin and connects the instrumentation amplifier output IAout to R11. The voltage across R11 is sensed by a pseudo differential ADC.

图 14. Analog Input Circuit

If the analog input is voltage it can be directly sensed through J2. If the input is current then it has to be converted into voltage by using an external burden resistor connected across J2. A 500- $\Omega$  resistor will convert the 0-mA to 20-mA current input to 0 V to 10 V.

The transfer function for the analog input is given by 公式 5

$$(VfbCh1 - VfbRefCh1) = \left(\frac{2 \times Voltage \ across \ J2 \ pins}{R10}\right) \times R11$$

(5)

Which means that a ±10-V analog input translates to ±1.238 V at the ADC around the 1.65-V reference.

RC filters comprising of R51, C38 and R49, C36 are used on the ADC inputs. The capacitance is selected to be 100 times the input parasitic capacitance of the ADC. In this design the LAUNCHXL-F28379D ADC pins ADCINB5 and ADCINC5 are used, which have an input parasitic capacitance of  $\sim$ 5 pF. C38 and C36 are selected to be 820 pF. As the XTR305 is powered by  $\pm$ 15-V rails, it is possible that the IAout can become more than 3.3 V during fault conditions. The rail-to-rail clamping diodes D4 and D6 are used to clamp the ADC input to 3.3 V and GND.

图 15. RC Filters on ADC Input

Note: By default the OD\_N pin is pulled up to 3.3 V through R14, which configures the XTR305 device in analog output mode.

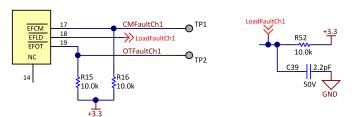

#### 2.3.7 Diagnostic Features

**Fault detection:** The XTR305 device has inbuilt diagnostic features to detect overload, short-circuit load, over temperature of IC, and common-mode over voltage range on the instrumentation amplifier inputs.

图 16. Error Flags

**IA Common-Mode Over Voltage Range (EFcm):** This flag goes low as soon as the input of the IA reach the limits of the linear operation for the input voltage. This can be monitored on test point TP1.

**Over temperature Flag (Efot):** This flag goes low if the chip temperature reaches 140°C and resets as soon as it cools down to 125°C. The flag can be monitored on test point TP2.

**Load error (EFId):** Indicates fault conditions driving voltage or current into the load. In voltage output mode, it monitors the voltage limits of the output swing and the current limit condition caused from short or low load resistance. In current output mode, it indicates a saturation into the supply rails from a high-load resistance or open load. In this design, this fault flag is connected to the Launchpad GPIO. The fault flag helps in detecting if the analog output wire is broken or shorted. This improves the reliability of the analog output function. In case of short-circuit load, the output current is limited to ±20 mA in the voltage output mode and ±32 mA in the current output mode.

All three fault flags are open collector and therefore need pullup resistors. Pullup resistors R15, R16 and R52 =  $10 \text{ k}\Omega$ . C39 = 2.2 pF is a noise filter placed on the output for connecting to Launchpad.

Analog output monitor: During the current output mode IA output is connected to R11 through IAOUT pin and IMON is internally disconnected. IAOUT is proportional to the output voltage given by 公式 6. This current is converted into voltage across R11 which is sensed by a pseudo differential ADC. This enables to monitor the output power delivered to the load. If the load resistance is known then the output current can be calculated inside the Launchpad and compared with the commanded value.

$$IAout = \frac{2 \times Vout}{R10}$$

(6)

During the voltage output mode 1/10th of the output drive current is mirrored onto the IMON pin and IAOUT is internally disconnected. The IMON pin is connected to R11. The voltage across R11 is sensed by a pseudo differential ADC. If the output load is known, then the output voltage can be calculated and compared with the commanded value. The output power delivered to the load can also be calculated.

Output monitor functions helps detect load changes enabling predictive maintenance which increase reliability of the Aout function

#### 2.3.8 Power Supplies and Reference

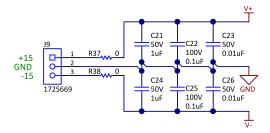

The XTR305 is powered from ±15-V supplies which have to be provided externally to the PCB through connector J9. C21 and C24 are local bulk capacitors on the PCB and C22, C23, C25 and C26 are noise decoupling capacitors.

图 17. ±15-V External Supply

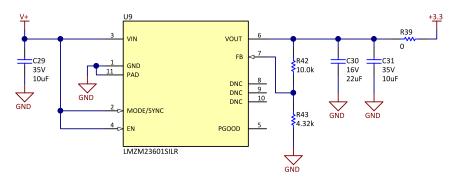

A C2000 launchpad can be used to control the TIDA-01633 PCB. In this case, a 3.3-V supply is required to power the Launchpad. This 3.3-V supply is generated from a 15-V supply using LMZM23601 DC/DC converter module. The output voltage is configured by R42 and R43 using 公式 7

$$Vout = \frac{Vfb \times (R43 + R42)}{R43}$$

• Where reference voltage, Vfb = 1 V

(7)

R42 is selected as 10 k $\Omega$ . For 3.3-V output, R43 is calculated to be 4.34 k $\Omega$ . Select R43 = 4.32 k $\Omega$

Low ESR ceramic capacitors are required on the output. For 3.3-V output, the LMZM23601 data sheet recommends a minimum value of 22  $\mu$ F. C30 = 22  $\mu$ F and C31 = 10  $\mu$ F are used in this design. A 10- $\mu$ F capacitor: C29 is used on the device input. The device is always enabled by connecting enable pin (EN) to VIN. The control mode is set to forced PWM mode by connecting MODE pin to VIN. In this mode the device switches at the internal clock frequency. The pad of the device is connected to GND plane for good heat sinking.

图 18. 15-V to 3.3-V Conversion

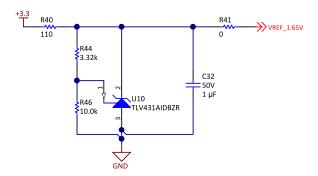

A 1.65-V reference bias Vref is required on the XTR305 input stage. This is to ensure bipolar output with a unipolar input. TLV431A adjustable precision shunt regulator is used in this design to generate the reference from a 3.3-V input. The reference voltage is set by R44 and R46 according to 公式 8

$$Vref = \frac{V1 \times (R46 + R44)}{R46}$$

Where V1 = 1.24 V is the device internal reference voltage at pin 1

(8)

R46 is selected as 10 k $\Omega$ . For 1.65 V reference, R44 is calculated to be 3.306 k $\Omega$ . Select R44 = 3.32 k $\Omega$

图 19. 1.65-V Reference Generation

## 3 Hardware, Software, Testing Requirements, and Test Results

#### 3.1 Hardware

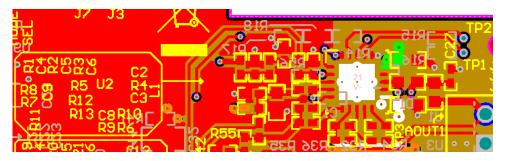

#### 3.1.1 TIDA-01633 PCB Overview

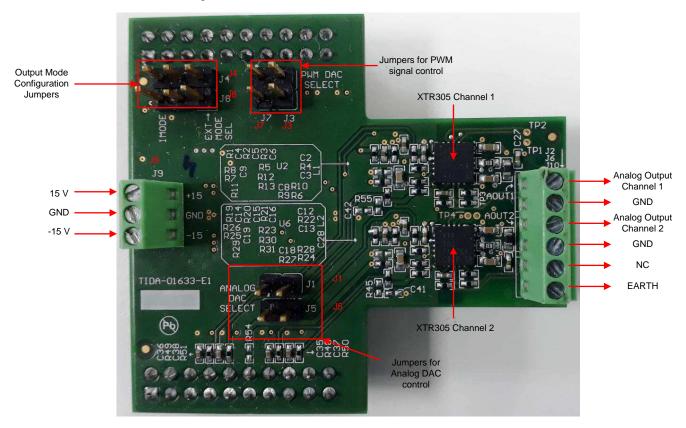

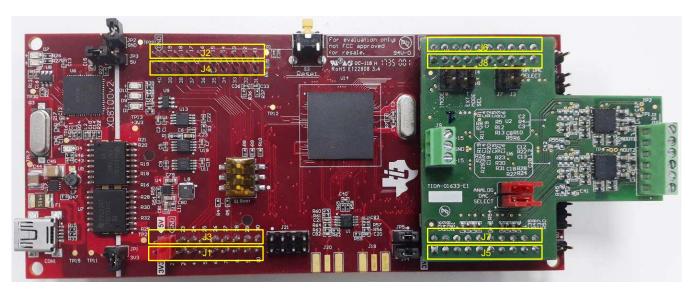

The ±15-V DC supply and the analog outputs are connected to the TIDA-01633 PCB as shown in № 20. J4 and J8 are used to configure the analog output mode of operation. By default the output is in voltage mode. To manually change to current output mode, a jumper has to be placed between the center pin and the right side pin. If MCU control of the output is required then a jumper is placed between the center pin and the left side pin. Jumper J3, J7, J1 and J5 are used to select the control input signal source. Placing jumpers on J1 and J5 enables output control using analog DAC signals. Placing jumpers on J7 and J3 enables output control using PWM signal. Note that for PWM control component changes are required, see schematic file in design tool folder.

图 20. Top View of TIDA-01633

#### 3.1.2 Controller Interface

图 21. Launchpad Interface to TIDA-01633

## 表 4. TIDA-01633 J11 Interface to Launchpad J5, J7

| TIDA-01633<br>FUNCTION | LAUNCHPAD<br>FUNCTION USED | J5 PIN | J7 PIN | LAUNCHPAD<br>FUNCTION USED | TIDA-01633<br>FUNCTION |

|------------------------|----------------------------|--------|--------|----------------------------|------------------------|

| 3.3 V                  | 3.3 V                      | 41     | 61     |                            |                        |

|                        |                            | 42     | 62     | GND                        | GND                    |

|                        |                            | 43     | 63     |                            |                        |

|                        |                            | 44     | 64     | ADCINC5                    | VfbRefCh1_Flt          |

|                        |                            | 45     | 65     | ADCINB5                    | VfbCh1_Flt             |

|                        |                            | 46     | 66     |                            | ExtRef                 |

| RESERVED               | SPICLKB                    | 47     | 67     | ADCINC4                    | VfbRefCh2_Flt          |

| AinEnableCh2_N         | GPIO52                     | 48     | 68     | ADCINB4                    | VfbCh2_Flt             |

|                        |                            | 49     | 69     |                            | AnalogDacCh2           |

|                        |                            | 50     | 70     | DACOUTB                    | AnalogDacCh1           |

## 表 5. TIDA-01633 J13 Interface to Launchpad J8, J6

| TIDA-01633<br>FUNCTION | LAUNCHPAD<br>FUNCTION USED | J8 PIN | J6 PIN | LAUNCHPAD<br>FUNCTION USED | TIDA-01633<br>FUNCTION |

|------------------------|----------------------------|--------|--------|----------------------------|------------------------|

|                        |                            | 41     | 61     | GND                        | GND                    |

|                        |                            | 42     | 62     | SPISTEB_N                  | Reserved               |

|                        |                            | 43     | 63     | GPIO131                    | AoutModeCh2            |

|                        |                            | 44     | 64     | GPIO130                    | AoutModeCh1            |

|                        |                            | 45     | 65     |                            |                        |

| PwmDacCh2              | EPWM8A                     | 46     | 66     | SPISIMOB                   | Reserved               |

| PwmDacCh1              | EPWM8B                     | 47     | 67     | SPISOMIB                   | Reserved               |

|                        |                            | 48     | 68     | GPIO26                     | AinEnableCh1_N         |

|                        |                            | 49     | 69     | GPIO27                     | LoadFaultCh2           |

|                        |                            | 50     | 70     | GPIO25                     | LoadFaultCh1           |

For more information on C2000 launchpads go to: C2000 Tools and Software

For further technical support on C2000 go to e2e forum: https://e2e.ti.com/support/microcontrollers/c2000/

## 3.2 Testing and Results

The focus of the tests is to evaluate the functionality and performance of the XTR305 based analog output module. The accuracy of the circuit, diagnostic features, and EMC immunity performance are characterized.

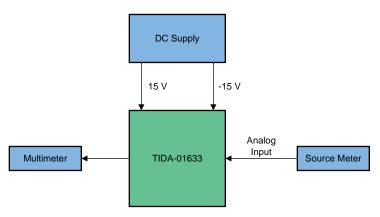

## 3.2.1 Voltage Output Mode

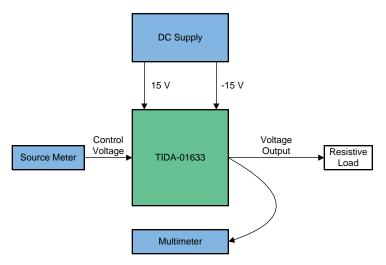

The TIDA-01633 is configured in the voltage output mode. A ±15-V external supply powers the board. The control input voltage is provided by a source meter. A resistive load is connected on the voltage output. A multimeter connected in parallel to the load measures the output voltage.

图 22. Test Setup for Voltage Output Mode

#### 3.2.1.1 Transfer Function

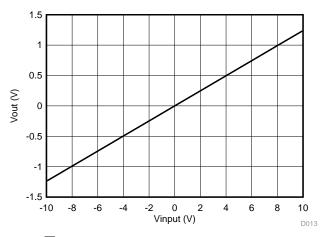

图 23. Voltage Output Transfer Function

## 3.2.1.2 Output Voltage Accuracy

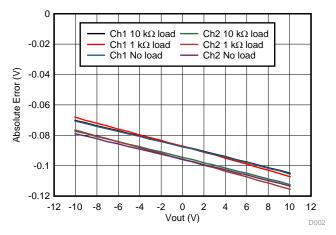

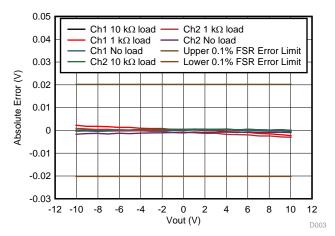

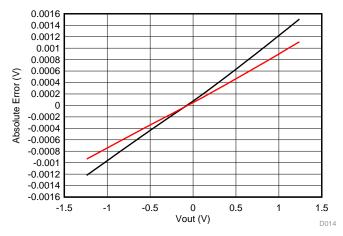

The deviation from the expected output value is plotted for 10 k $\Omega$ , 1 k $\Omega$  and no load case for both channel 1 and 2 in  $\boxtimes$  24.

图 24. Uncalibrated Measurement Error vs Output Voltage at Different Loads

The values plotted in  $\ 24$  are calibrated using a 2 point calibration method at 25°C with 10-k $\Omega$  load. Calibration eliminates the offset and gain errors. The same correction factors are applied for 1 k $\Omega$  load and no load. The calibrated results are plotted in  $\ 25$ .

图 25. 2-Point Calibrated Measurement Error vs Output Voltage at Different Loads

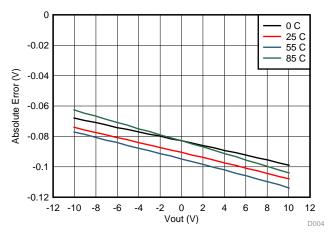

The measurement error drift at different temperatures is plotted in  $\ 26$ . This measurement is done with a 10-k $\$ 0 load and the temperature is set at 0°C, 25°C, 55°C, and 85°C.

图 26. Measurement Error vs Output Voltage at Different Temperatures

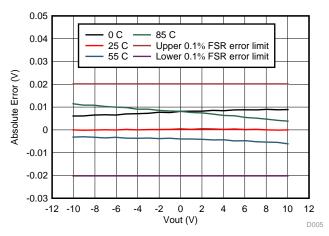

The plots in 图 26 are 2-point calibrated at 25°C and the correction factor applied to all the temperatures. The result is shown in 图 27.

图 27. 2-Point Calibrated Measurement Error vs Output Voltage at Different Temperatures

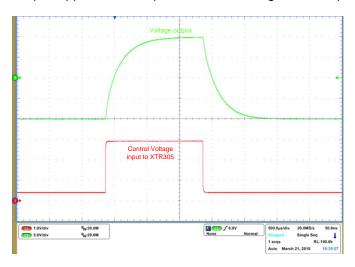

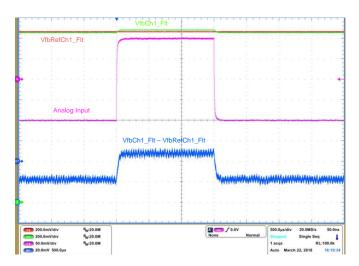

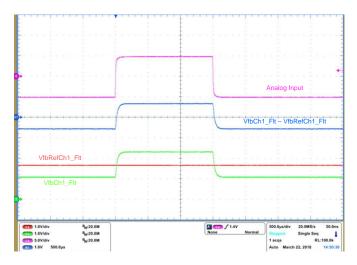

#### 3.2.1.3 Step Response

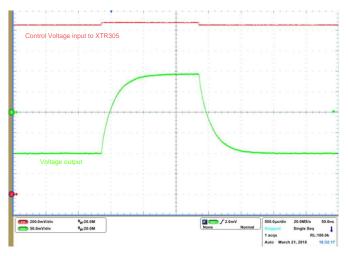

A small signal step of  $\pm 12$  mV around 1.65 V is applied to the input of channel 1 using a function generator. The resulting small signal step response is plotted in  $\boxtimes$  28. The rise and fall time is ~1 ms. The load used for this test is 10 k $\Omega$ .

图 28. Small Signal Step Response

A 0.4-V to 2.9-V input step is applied to the input and the resulting ±10-V output step is plotted in 图 29.

图 29. Large Signal Step Response

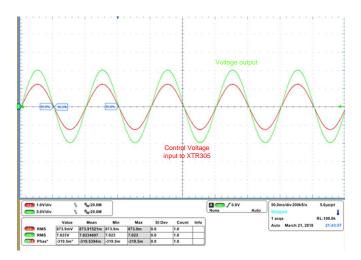

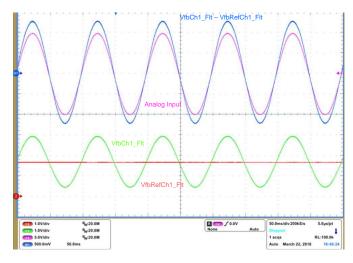

A 10-Hz sine input is applied at the input and the resulting output sine wave is plotted in \( \bar{\bar{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\tin}\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\tetx{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\texi}\text{\text{\text{\texi}\text{\text{\text{\text{\text{\tex

图 30. Input and Output Sine Voltages at 10 Hz

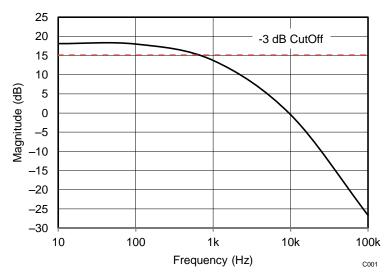

#### 3.2.1.4 Bandwidth

The gain vs frequency plot for the voltage output was measured using a sine wave input of constant amplitude and varying frequency. The output voltage magnitude was measured with a multimeter. Values were plotted at 10, 100, 1000, 10 khz, and 100 khz. From \$\mathbb{g}\$ 31, the bandwidth is ~800 Hz.

图 31. Bode Plot for Voltage Output

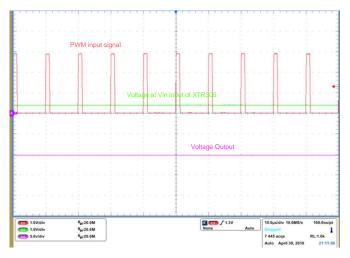

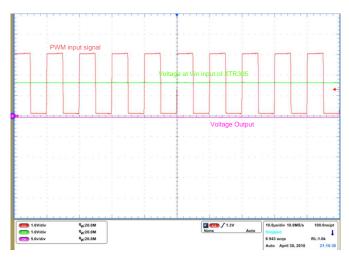

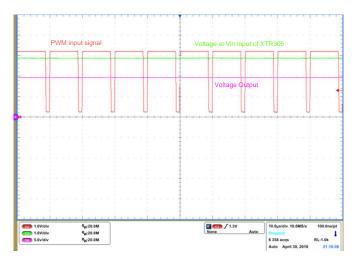

## 3.2.1.5 PWM Input Signal Control of Voltage Output

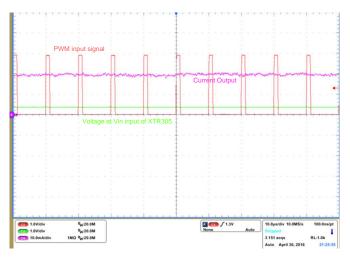

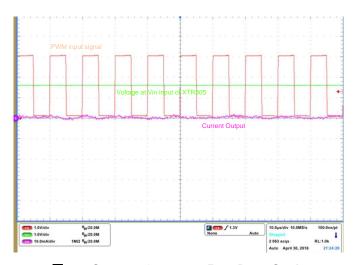

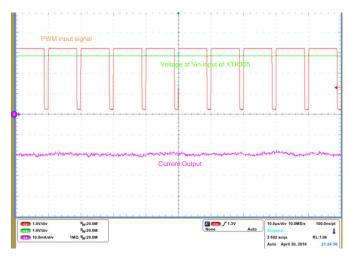

The voltage output can be controlled by a PWM input signal. For PWM control variant of TIDA-01633 and BOM changes refer schematic and CAD files. A 100-kHz PWM signal is used for testing the board. Changing the PWM duty cycle from 12.12% to 87.87% corresponds to full scale swing of the voltage output as shown in 图 32 to 图 34.

图 32. Voltage Output at 12.12% Duty Cycle

图 33. Voltage Output at 50% Duty Cycle

图 34. Voltage Output at 87.87% Duty Cycle

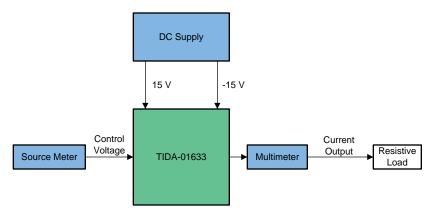

## 3.2.2 Current Output Mode

The TIDA-01633 is configured in the current output mode. A ±15-V supply powers the board. The control input voltage is provided by a source meter. A resistive load is connected on the voltage output. A multimeter connected in series with the load measures the output current.

图 35. Test Setup for Current Output Mode

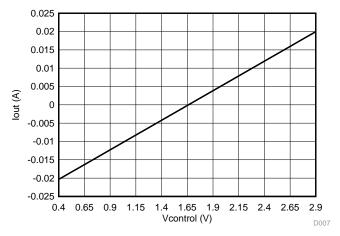

#### 3.2.2.1 Transfer Function

A 0.4-V to 2.9-V input voltage (±1.25 V around 1.65-V reference) provides a −20 mA to +20-mA output current. The transfer functions for both analog output channels are plotted in 图 36

图 36. Current Output Transfer Function

## 3.2.2.2 Output Current Accuracy

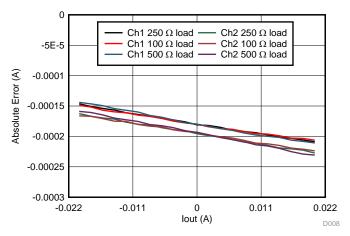

The deviation from the expected output value is plotted for 250- $\Omega$ , 500- $\Omega$  and 100- $\Omega$  loads for both channel 1 and 2 in  $\mathbb{Z}$  37.

图 37. Uncalibrated Measurement Error vs Output Current at Different Loads

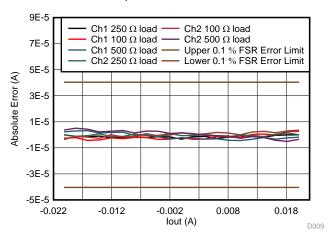

图 38. 2-Point Calibrated Measurement Error vs Output Current at Different Loads

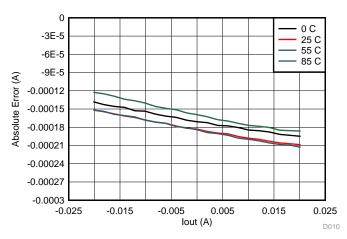

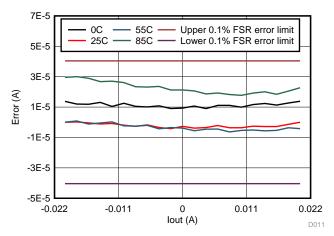

The measurement error drift at different temperatures is plotted in  $\boxtimes 39$ . This measurement is done with a 250– $\Omega$  load and the temperature is set at 0°C, 25°C, 55°C, and 85°C.

图 39. Measurement Error vs Output Current at Different Temperatures

The plots in 图 39 are 2-point calibrated at 25°C and the correction factor applied to all the temperatures. The result is shown in 图 40.

图 40. 2-Point Calibrated Measurement Error vs Output Current at Different Temperatures

#### 3.2.2.3 Step Response

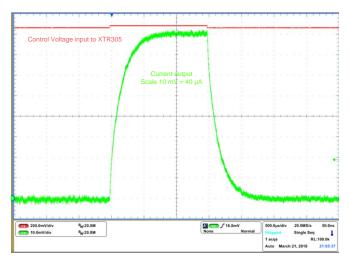

A small signal step of 0 mV to 20 mV is applied to the input of channel 1 using a function generator. The resulting small signal output step response of 0  $\mu$ A to 320  $\mu$ A is plotted in  $\boxed{8}$  41 (Note: The output current is measured across 250- $\Omega$  load, 0 mV to 80 mV corresponds to 0  $\mu$ A to 320  $\mu$ A). The rise and fall time is ~1 ms.

图 41. Small Signal Step Response

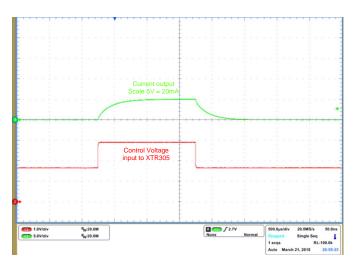

A 1.65-V to 2.9-V input step is applied to the input and the resulting 0-mA to 20-mA output step is plotted in 图 42.

图 42. Large Signal Step Response

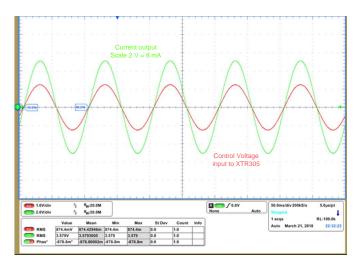

The 10-Hz sine signal is applied on the input and the resulting sine wave output is plotted in ₹ 43. Both waveforms are AC coupled scope captures.

图 43. Input Sine Voltage and Output Sine Current at 10 Hz

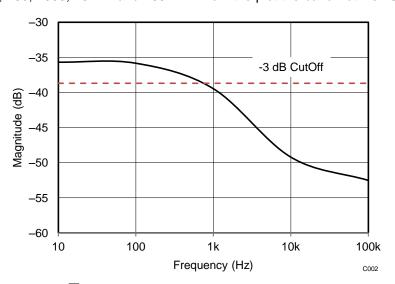

#### 3.2.2.4 Bandwidth

The gain vs frequency plot for the current output was measured using a sine wave input of constant amplitude and varying frequency. The output current magnitude was measured with a multimeter. Values were plotted at 10, 100, 1000, 10 khz and 100 khz. From the plot the bandwidth is ~800 Hz.

图 44. Bode Plot Current Output Mode

## 3.2.2.5 PWM Input Signal Control of Current Output

The current output can be controlled by a PWM input signal. For PWM control variant of TIDA-01633 and BOM changes see the schematic and CAD files. For testing the board a 100-kHz PWM signal is used. Changing the PWM duty cycle from 12.12% to 87.87% corresponds to full scale swing of the current output as shown in 图 45 to 图 47. The actual current polarity is inverse of the current polarity shown in the graphs as the current probe was connected in the reverse direction.

图 45. Current Output at 12.12% Duty Cycle

图 46. Current Output at 50% Duty Cycle

图 47. Current Output at 87.87% Duty Cycle

## 3.2.3 Output Protection

The XTR305 faulty load detection function is tested in # 3.2.3.

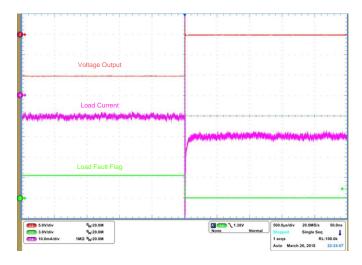

#### 3.2.3.1 Short-Circuit Detection

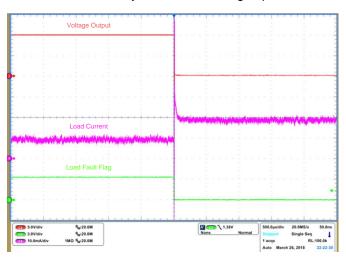

During the voltage output mode if the output gets shorted because of a faulty load connected, the XTR305 limits the output current to 20 mA and pulls the load fault output flag low. The microcontroller can then take appropriate action based on the fault flag.

In  $\boxtimes$  48 a 10-V output is connected to a 1-k $\Omega$  load which drives 10 mA into the load initially. The load is then shorted. When the short event occurs the XTR305 pulls down the output voltage to ~0 V and limits the output current to 20 mA. Simultaneously the load fault flag is pulled low.

图 48. Load Short Detection - Initial Vout is +10 V

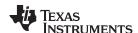

In  $\boxtimes$  49 a –10-V output is connected to a 1-k $\Omega$  load with –10 mA driven into the load initially. In this case on load short the output current is limited to –20 mA.

图 49. Load Short Detection - Initial Vout is -10 V

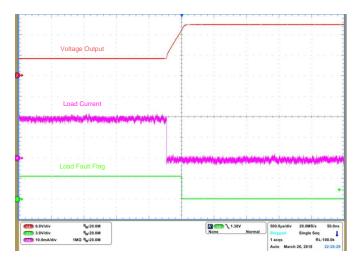

#### 3.2.3.2 Open Load Detection

In the current output mode if the output opens due to faulty wiring, the XTR305 output rises to the compliance voltage limit and once this is reached it pulls the load fault output flag low. The controller can then take appropriate action based on the fault flag.

In  $\boxtimes 50$  a 20-mA output is connected to a 250- $\Omega$  load which is suddenly opened. The output current becomes 0 immediately and the output voltage rises towards the positive rail. As soon as the compliance output voltage limit is reached the load fault flag is pulled low.

图 50. Open Load Fault Detection - Initial lout is +20 mA

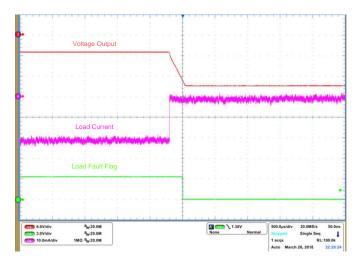

In  $\boxtimes$  51 a –20-mA initial output current is driven into a 250- $\Omega$  load before the output open event. In this case the output voltage is driven towards the negative rail.

图 51. Open Load Fault Detection - Initial lout is -20 mA

#### 3.2.4 Analog Input

The TIDA-01633 can also be configured as an analog input. For testing this configuration a source meter is connected on the terminal connectors and a multimeter is connected on the analog feedback channels. The analog feedback channel is measured with respect to the 1.65-V reference.

图 52. Test Setup for Analog Input Mode

## 3.2.4.1 Transfer Function

A -10-V to +10-V analog input voltage provides  $\pm 1.238$  V across 1.65-V reference. The transfer function is plotted in  $\boxed{8}$  53.

图 53. Analog Input Transfer Function

## 3.2.4.2 Analog Input Accuracy

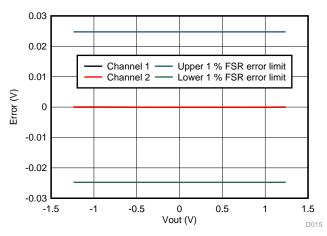

The deviation from the expected measurement values is plotted in ₹ 54. An external burden resistor has to be used for using current as an analog input.

图 54. Uncalibrated Measurement Error vs Analog Input Voltage

The values plotted in ₹ 54 are calibrated using a 2-point calibration method. Calibration eliminates the offset and gain errors. The calibrated results are plotted in ₹ 55.

图 55. 2-Point Calibrated Measurement Error vs Analog Input Voltage

## 3.2.4.3 Step Response

A small signal step of −100 mV to +100 mV is applied using a function generator. The resulting small signal step response is plotted in ₹ 56.

图 56. Small Signal Step Response

A −10-V to +10-V input step is applied and the resulting large signal step response is plotted in \( \bar{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\tilde{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\te}\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\text{\texi}\text{\text{\text{\text{\text{\text{\text{\texi}\text{\text{\texi{\text{\text{\texi}\texi{\text{\texi{\texi}\text{\texi{\texi{\texi{\texi{\texi{\t

图 57. Large Signal Step Response

The sine analog input (10 Hz) and its response is plotted in ₹ 58.

图 58. Sine Input and Output at 10 Hz

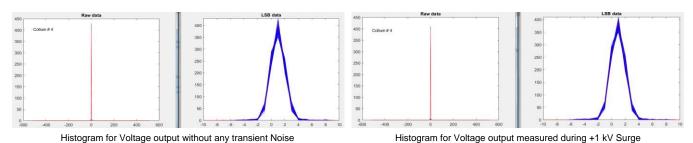

# 3.2.5 EMC Immunity Tests

The TIDA-01633 has been tested as per IEC61000-4-2, IEC61000-4-4 and IEC61000-4-5 (ESD, EFT and Surge) with the test levels and performance criterion specified in the standard IEC61800-3: *EMC Immunity Requirements and Specific Test Method Applicable in Adjustable Speed, Electrical Power Drive Systems.*

The performance criterion is defined in 表 2

#### **General Test procedure:**

- Set up the EMC test equipment and EUT as shown in corresponding section for each of the tests

- Measure histogram before EMC test

- · Apply transient noise and measure histogram during the test

- Compare both the histograms to determine the test class

Capturing Histograms: The analog output is monitored using the analog feedback channel. For channel 1 the analog feedback channel comprises of the signals VfbCh1 and VfbRefCh1. VfbRefCh1 is the 1.65-V reference and VfbCh1 is proportional to the analog output. Both of these signals are connected to simultaneous sampling channels of ADC. The difference (VfbCh1 - VfbRefCh1) is then stored in memory. For creating the histogram sampling is done at 1 ksps for 2 minutes. For each sample the error from the initial reference measurement is calculated and sorted into LSB bins. This is now plotted in a graph with the LSB bins on the X-axis and the number of samples with error falling into LSB bins plotted on the Y-axis. The EMC transients have to be applied within this 2-minute interval. An example histogram for voltage output before EMC and during EMC is shown in § 59.

图 59. Histogram Before EMC Transients and During EMC Transient

The performance criterion A is often customer specific and the expected accuracy is depending system requirements. In TIDA-01633 the performance criterion is class A if the measurement accuracy remains within the maximum worst case 0.2% FSR accuracy range. The EMC test results are summarized in 表 6.

| IEC61800-3 EMC IMMUNITY REQUIREMENTS FOR SECOND ENVIRONMENT AND MEASURED VOLTAGE LEVELS AND CLASS |                                  |                       |                                                                                                | TIDA-01633 MEASUREMENTS<br>(STANDARD TEST VOLTAGE<br>LEVELS) |          | TIDA-01633 MEASUREMENTS (EXTENDED TEST VOLTAGE LEVELS) |      |          |                                  |

|---------------------------------------------------------------------------------------------------|----------------------------------|-----------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------|--------------------------------------------------------|------|----------|----------------------------------|

| PORT                                                                                              | PHENOME<br>NON                   | BASIC<br>STANDAR<br>D | LEVEL                                                                                          | PERFORM<br>ANCE<br>CRITERIO<br>N                             | LEVEL    | PERFORM<br>ANCE<br>CRITERIO<br>N                       | TEST | LEVEL    | PERFORM<br>ANCE<br>CRITERIO<br>N |

| Enclosure<br>Ports                                                                                | ESD                              | IEC61000-<br>4-2      | ±4 kV CD                                                                                       | В                                                            | ±4 kV CD | Α                                                      | Pass | ±8 kV CD | В                                |

| Ports for<br>control<br>lines and<br>DC<br>auxiliary<br>supplies<br>(<60 V)                       | Fast<br>transient<br>burst (EFT) | IEC61000-<br>4-4      | ±2 kV/5<br>khz<br>capacitive<br>clamp                                                          | В                                                            | ±2 kV    | A                                                      | Pass | ±4 kV    | В                                |

|                                                                                                   | Surge<br>1.2/50 us,<br>8/20 us   | IEC61000-<br>4-5      | ±1 kV;<br>because<br>shielded<br>cable >20<br>m direct<br>coupling to<br>shield (2<br>Ω/500 A) | В                                                            | ±1 kV    | A                                                      | Pass | ±2 kV    | A                                |

表 6. IEC61800-3 EMC Immunity Requirements

#### 3.2.5.1 ESD Test Results

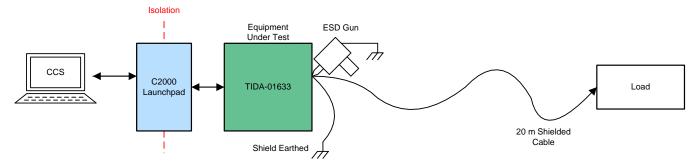

图 60. ESD Test Setup Diagram

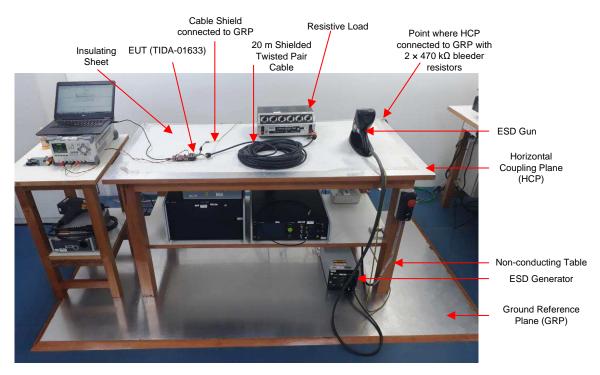

图 61. Lab Test Setup

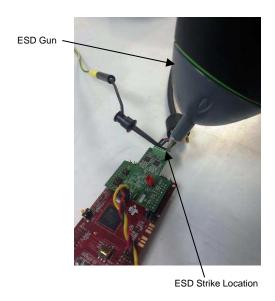

图 62. EUT (TIDA-01633) Connections

图 63. ESD Strike Location

表 7. ESD Test Results

| ESD PULSES | PERFORMANCE ACHIEVED |                |  |  |

|------------|----------------------|----------------|--|--|

| ESD FOLSES | VOLTAGE OUTPUT       | CURRENT OUTPUT |  |  |

| +4 kV      | Class A              | Class A        |  |  |

| -4 kV      | Class A              | Class A        |  |  |

| +6 kV      | Class A              | Class B        |  |  |

| -6 kV      | Class A              | Class A        |  |  |

| +8 kV      | Class A              | Class B        |  |  |

| -8 kV      | Class A              | Class B        |  |  |

#### 3.2.5.2 EFT

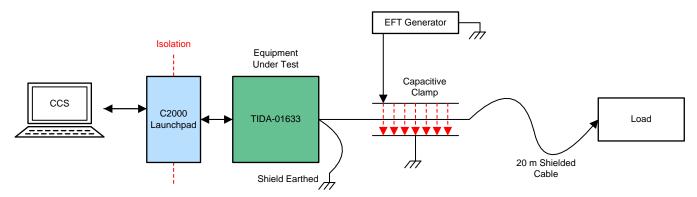

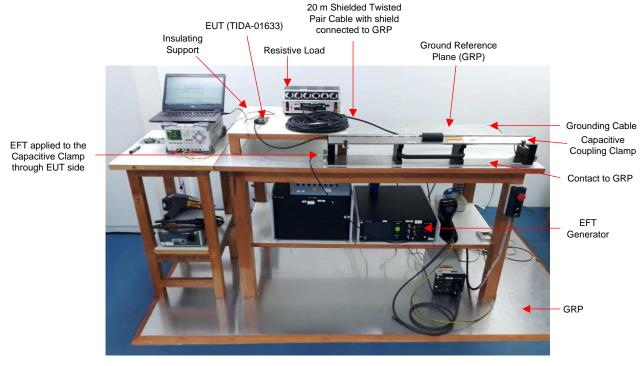

The TIDA-01633 is connected to a resistive load through a 20-m shielded twisted pair cable. EFT is coupled into this cable through a capacitive clamp as shown in 图 65. For the EFT test the table reference and the ground reference are shorted to each other.

图 64. EFT Test Setup Diagram

图 65. Lab EFT Test Setup

表 8. EFT Test Results

| EFT PULSES | PERFORMANCE ACHIEVED |                |  |  |

|------------|----------------------|----------------|--|--|

| EFT FOLSES | VOLTAGE OUTPUT       | CURRENT OUTPUT |  |  |

| +2 kV      | Class A              | Class A        |  |  |

| -2 kV      | Class A              | Class A        |  |  |

| +4 kV      | Class B              | Class B        |  |  |

| -4 kV      | Class B              | Class B        |  |  |

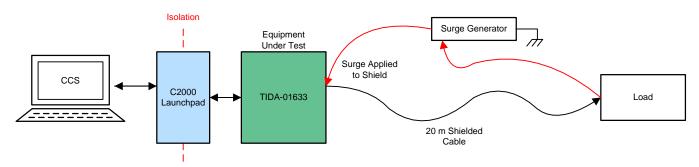

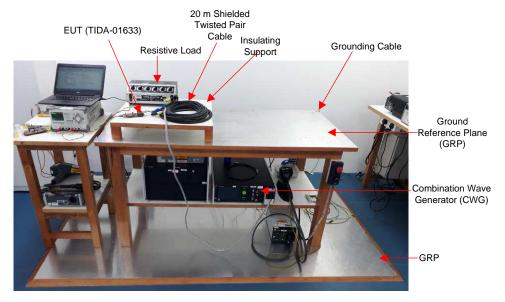

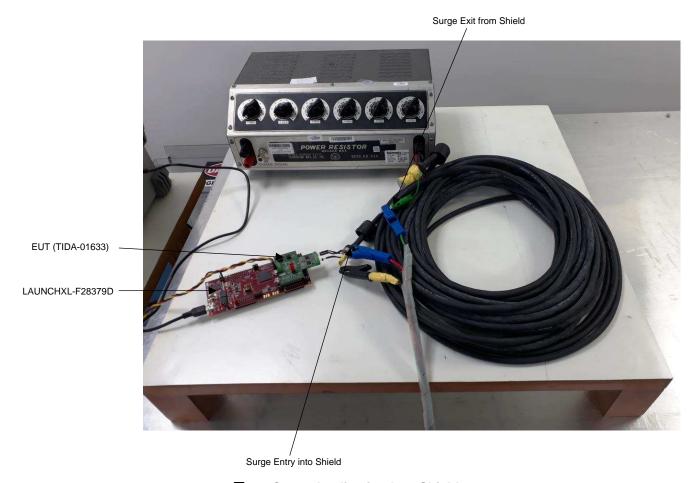

#### 3.2.5.3 Surge

For surge testing the surge is directly inserted into the shield of the cable at the EUT end.

图 66. Surge Test Setup Diagram

图 67. Lab Surge Test Setup

图 68. Surge Application Into Shield

# 表 9. Surge Test Results

| SURGE | PERFORMANCE ACHIEVED |                |  |  |

|-------|----------------------|----------------|--|--|

| SURGE | VOLTAGE OUTPUT       | CURRENT OUTPUT |  |  |

| +1 kV | Class A              | Class A        |  |  |

| -1 kV | Class A              | Class A        |  |  |

| +2 kV | Class A              | Class A        |  |  |

| -2 kV | Class A              | Class A        |  |  |

www.ti.com.cn Design Files

## 4 Design Files

#### 4.1 Schematics

To download the schematics, see the design files at TIDA-01633.

#### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01633.

# 4.3 PCB Layout Recommendations

## 4.3.1 XTR305

- Place supply bypass capacitors C2, C3 close to device supply pins

- R5, C1, R3 and C6 are placed at the input of the OPA inside XTR305. The trace length should be minimized to avoid noise coupling into the input

- R6, R9, C8 and R10 are placed at the input of the IA inside XTR305. Trace lengths should be minimized to avoid noise coupling

- · The instrumentation amplifier ground connection from R9 resistor must be at the connector pins

- The power pad of the XTR305 is connected to the internal ground planes through multiple vias for good thermal performance

图 69. XTR305 Layout guidelines

## 4.3.2 TVS1400

- The small form factor of the TVS1400 device enables placement below the connector close to the terminal pins when compared to standard SMA and SMB packages

- Close placement with short traces shunts the transient noise right at the connector without coupling into other net connections

Design Files www.ti.com.cn

图 70. Placement of TVS1400

## 4.3.3 Layout Prints

To download the layer plots, see the design files at TIDA-01633.

# 4.4 Altium Project

To download the Altium Designer® project files, see the design files at TIDA-01633.

## 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-01633.

# 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01633.

## 5 Related Documentation

- 1. Texas Instruments, Single-Channel Industrial Voltage and Current Output Driver, Isolated, EMC/EMI Tested

- 2. Texas Instruments, LAUNCHXL-F28379D OVerview User's Guide

- 3. IEC61800-3 Edition 2.0 (2004-08) Adjustable Speed Electrical Power Drive Systems Part 3: *EMC Requirements and Specific Test Methods*

- 4. IEC61000-4-2 Edition 2.0 (2008-12) Electromagnetic compatibility (EMC) Part 4-2 : Testing and Measurement Techniques Electrostatic Discharge Immunity Test

- 5. IEC61000-4-4 Edition 3.0 (2012-04) Electromagnetic compatibility (EMC) Part 4-4: Testing and Measurement Techniques Electrical Fast Transient/burst Immunity Test

- 6. IEC61000-4-5 Edition 3.0 (2014-05) Electromagnetic compatibility (EMC) Part 4-5 : Testing and Measurement Techniques Surge Immunity Test

www.ti.com.cn About the Author

## 5.1 商标

C2000, E2E are trademarks of Texas Instruments.

Altium Designer is a registered trademark of Altium LLC or its affiliated companies.

All other trademarks are the property of their respective owners.

## 6 About the Author

**Pawan Nayak** is a System Engineer at Texas Instruments, where he is responsible for developing reference design solutions for the Motor Drive segment within Industrial Systems.

**Martin Staebler** is a System Architect in the Industrial Systems Motor Drive team at Texas Instruments, responsible for specifying and developing reference designs for industrial drives.

# 6.1 Recognition

The author would like to recognize excellent contributions from **Kristen Mogensen** during the test of the design.

#### 有关 TI 设计信息和资源的重要通知

德州仪器 (TI) 公司提供的技术、应用或其他设计建议、服务或信息,包括但不限于与评估模块有关的参考设计和材料(总称"TI 资源"),旨在帮助设计人员开发整合了 TI 产品的 应用; 如果您(个人,或如果是代表贵公司,则为贵公司)以任何方式下载、访问或使用了任何特定的 TI 资源,即表示贵方同意仅为该等目标,按照本通知的条款进行使用。

TI 所提供的 TI 资源,并未扩大或以其他方式修改 TI 对 TI 产品的公开适用的质保及质保免责声明;也未导致 TI 承担任何额外的义务或责任。 TI 有权对其 TI 资源进行纠正、增强、改进和其他修改。

您理解并同意,在设计应用时应自行实施独立的分析、评价和 判断, 且应全权负责并确保 应用的安全性, 以及您的 应用 (包括应用中使用的所有 TI 产品))应符合所有适用的法律法规及其他相关要求。你就您的 应用声明,您具备制订和实施下列保障措施所需的一切必要专业知识,能够 (1) 预见故障的危险后果,(2) 监视故障及其后果,以及 (3) 降低可能导致危险的故障几率并采取适当措施。您同意,在使用或分发包含 TI 产品的任何 应用前, 您将彻底测试该等 应用 和该等应用所用 TI 产品的 功能而设计。除特定 TI 资源的公开文档中明确列出的测试外,TI 未进行任何其他测试。

您只有在为开发包含该等 TI 资源所列 TI 产品的 应用时, 才被授权使用、复制和修改任何相关单项 TI 资源。但并未依据禁止反言原则或其他法理授予您任何TI知识产权的任何其他明示或默示的许可,也未授予您 TI 或第三方的任何技术或知识产权的许可,该等产权包括但不限于任何专利权、版权、屏蔽作品权或与使用TI产品或服务的任何整合、机器制作、流程相关的其他知识产权。涉及或参考了第三方产品或服务的信息不构成使用此类产品或服务的许可或与其相关的保证或认可。使用 TI 资源可能需要您向第三方获得对该等第三方专利或其他知识产权的许可。

TI 资源系"按原样"提供。TI 兹免除对 TI 资源及其使用作出所有其他明确或默认的保证或陈述,包括但不限于对准确性或完整性、产权保证、无屡发故障保证,以及适销性、适合特定用途和不侵犯任何第三方知识产权的任何默认保证。

TI 不负责任何申索,包括但不限于因组合产品所致或与之有关的申索,也不为您辩护或赔偿,即使该等产品组合已列于 TI 资源或其他地方。 对因 TI 资源或其使用引起或与之有关的任何实际的、直接的、特殊的、附带的、间接的、惩罚性的、偶发的、从属或惩戒性损害赔偿,不管 TI 是否获悉可能会产生上述损害赔偿,TI 概不负责。

您同意向 TI 及其代表全额赔偿因您不遵守本通知条款和条件而引起的任何损害、费用、损失和/或责任。

本通知适用于 TI 资源。另有其他条款适用于某些类型的材料、TI 产品和服务的使用和采购。这些条款包括但不限于适用于 TI 的半导体产品 (http://www.ti.com/sc/docs/stdterms.htm)、评估模块和样品 (http://www.ti.com/sc/docs/sampterms.htm) 的标准条款。

邮寄地址: 上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2018 德州仪器半导体技术(上海)有限公司