# TI Designs: TIDA-060017 通过 LVDS 接口传输 SPI 信号参考设计

# TEXAS INSTRUMENTS

# 说明

该 TI 设计演示了如何解决和优化信号完整性难题,通常 在嘈杂环境中的同一 PCB 上或通过 PCB 向另一块板远 距离发送 SPI 信号(通过 LVDS 接口传输 SPI 信号) 时会遇到这些难题。此概念具有高抗噪性能、更低的 EMI 辐射和更宽的共模输入范围。该 TI 设计:

- 通过低电压差动信号 (LVDS) 接口发送 SPI 信号, 从而显著提高信号质量。

- 包括详细的时序分析,详细说明距离和 LVDS 接口 对 SPI 通信速度的影响

- 演示通过将 SCLK 路由回 SPI 主站或通过使用所选 TI 器件中提供的增强 SPI 功能来解决 SPI 时序难题 的解决方案

- 提供用于评估不同 SPI 外设以及 LVDS 驱动器和接收器的选项

# 资源

| TIDA-060017      | ť |

|------------------|---|

| SN65LVDS31-33EVM | Г |

| ADS8910BEVM-PDK  | Г |

| 设计文件夹 |  |

|-------|--|

| 工具文件夹 |  |

| 工具文件夹 |  |

咨询我们的 E2E™ 专家

# 特性

- 使用 LVDS 接口提高 SPI 总线的抗噪性能并增大其 距离

- 使用 LVDS 上的 SPI 可实现至少 3 米的通信距离, 而使用标准 SPI 只能实现 0.5 米的通信距离

- 采用相关技术,通过将 SCLK 路由回 SPI 主站,降 低传播延迟并提高 SPI 通信速度或扩大其距离

- 功耗仅为其他差动信号 (RS-422/RS-485) 解决方案 的十分之一

- -4V 至 5V 共模输入电压范围可提供很高的地弹抗扰 性能

# 应用

- 半导体测试设备

- 数据采集

- 实验室仪表

- 超声波扫描仪

- CT 扫描仪

- 保护继电器

- 终端装置

## System Description

杰

该 TI 参考设计末尾的重要声明表述了授权使用、知识产权问题和其他重要的免责声明和信息。

# 1 System Description

Serial peripheral interface (SPI) is found in numerous applications as the communication method between processor and peripheral devices. SPI was initially designed for short distance communication between devices on the same PCB. However, there is increasing demand for longer range SPI communication on the same PCB or from board to board. As distance increases, external noise and crosstalk between SPI signals becomes an issue. Furthermore, increased distance limits the data rate due to propagation delay, and affects the signal quality due to potential ground shift between boards. In this design guide, designer shows how to migrate the challenge posed when trying to extend SPI communication range and send SPI signals from board to board over long distance.

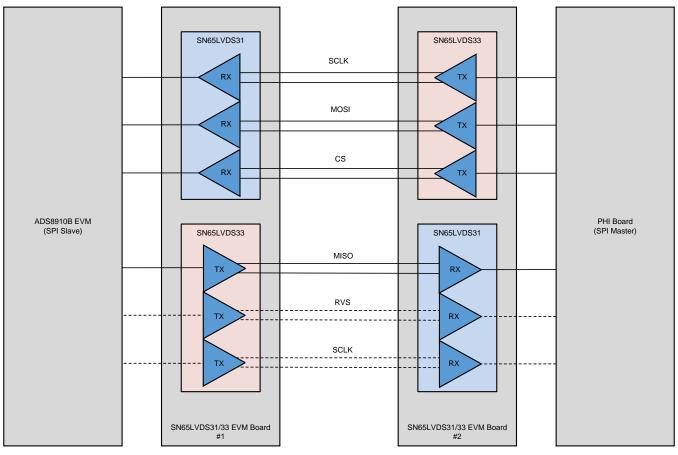

图 1. System Diagram

# 1.1 Key System Specifications

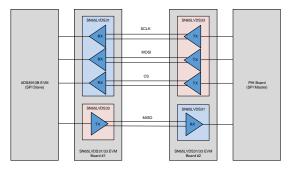

This reference design is configured to transmit single-ended SPI signals through LVDS driver and receiver. An ADC ADS8910B is used as the SPI slave device, and the PHI Controller is used as the SPI master device. Two quad channel LVDS drivers and two quad channel LVDS receivers are selected to drive the single-ended SPI signals from board to board.

1 gives the key system specifications. Following the system design consideration in 2.3 , this reference design can be easily configured and extended for different applications using SPI interface.

| PARAMETER                                  | SPECIFICATIONS             |  |

|--------------------------------------------|----------------------------|--|

| Power Supply for SN65LVDS31-33EVM          | 3.3V                       |  |

| Power Supply for ADS8910B                  | 5.5V and 3.3V              |  |

| SN65LVDS                                   | 31-33EVM Information       |  |

| Standard                                   | ANSI TIA/EIA -644 Standard |  |

| Number of LVDS Drivers                     | 4                          |  |

| Number of LVDS Receivers                   | 4                          |  |

| Driver Input Type                          | LVTTL/LVCMOS               |  |

| Receiver Output Type                       | LVTTL/LVCMOS               |  |

| Typical Output Voltage Rise and Fall Times | 500 ps (400 Mbps)          |  |

| Operating temperature                      | -40°C to +85°C             |  |

| Power Consumption                          | 25 mW Typical at 200 MHz   |  |

| Form Factor                                | 10-mm × 6-mm SOIC16        |  |

| ADS89                                      | 910B Information           |  |

| Number of Channels                         | Single                     |  |

| Input Type                                 | Differential               |  |

| Input Range                                | +/- 5V differential        |  |

| Resolution                                 | 18 bits                    |  |

| Sample Rate                                | 1-MSPS                     |  |

| SPI Clock Speed                            | Up to 70MHz                |  |

| Operating temperature                      | -40°C to +125°C            |  |

| Power Consumption                          | 21-mW at 1-MSPS            |  |

| Form Factor                                | 4-mm × 4-mm VQFN           |  |

# 表 1. Key System Specifications

System Overview

www.ti.com.cn

# 2 System Overview

# 2.1 Block Diagram

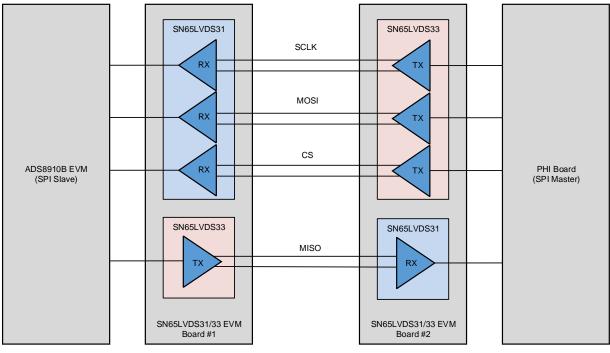

图 2. TIDA-060017 Block Diagram

图 2 shows the setup block diagram of this design.

# 2.2 Highlighted Products

The system features the device SN65LVDS31/SN65LVDS33 EVM, and ADS8910B EVM.

# 2.2.1 SN65LVDS31 and SN65LVDS33 EVM

SN65LVDS31 and SN65LVDS33 EVM includes a pair of LVDS quad channel driver SN65LVDS31 and receiver SN65LVDS33. Both devices are TIA/EIA-644 standard compliant LVDS driver and receiver. The SN65LVDS33 receiver incorporates an enhanced common-mode input voltage range of -4 V to 5 V, as well as an active-failsafe circuit that provides operation over the entire input common-mode range. This wide common-mode input feature is showcased in the design as a solution to combat potential ground shift present in high noise, high power switching environments.

# 2.2.2 ADS8910B EVM

The ADS8910B EVM includes both the SPI master device (PHI controller) and the SPI slave device (ADS8910B). The ADS8910B is a high-speed, single-channel, high-precision, 18-bit successive approximation register (SAR) analog to digital convertors (ADCs) with an integrated reference buffer and integrated low-dropout (LDO) regulator. The ADS8910B boost analog performance while maintaining high-resolution data transfer by using TI's enhanced-SPI feature, thereby making this device an excellent choice for applications involving FPGAs, DSPs.

# 2.3 System Design Theory

This design guide uses analog to digital converter, a common device that uses SPI interface, as an example, and focuses on maximizing the signal integrity of SPI interface by sending SPI signals over LVDS interface. As the signal integrity improvement is provided by the LVDS interface and is independent of the SPI peripherals, other SPI host and the SPI peripheral could be used to fit different application needs. Alternative LVDS driver and receiver such as DS90LV011A, DS90LV012A, DS90LV047A, and DS90LV048A can be used as well if wide common-mode input range is not necessary. These four LVDS drivers and receivers offer lower propagation delay compare to SN65LVDS31/33.

<sup>⋕</sup> 2.3.1 detail the timing challenges presented by extending the SPI communication distance. When these performance limiting characteristics are understood, two solutions are highlighted, one using novel design consideration for general SPI interfaces and another one using key feature of TI's ADC device.

With the elimination of timing challenges, solution for improving signal integrity when transmitting SPI signals from board to board is presented in  $\ddagger 2.3.3$ .

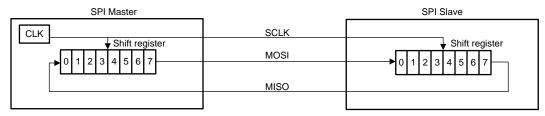

# 2.3.1 Timing Analysis

SPI is a preferred communication method between processor and peripheral devices due to its high speed and bidirectional nature; however, it was intended for very short distance applications. There is an inherent timing challenge when implementing a long distance SPI solution. This challenge and a detailed analysis of its impact with examples are described in the following sections.

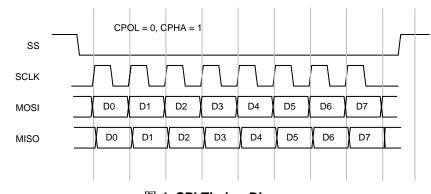

# 2.3.1.1 Effect of Propagation Delay on SPI Clock Speed

As depicted in 🕅 4, the SPI master expects the valid data before the clock falling edge. The total round trip propagation delay must be less than half the SCLK period to avoid missing bits. Hence, the theoretical maximum SPI clock can be calculated as:

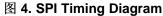

$$SCLK_{Max} = \frac{1}{2 \times t_{Period}}$$

The equation assumes that there is no change in the waveform shape. However, digital signals are analog in nature as they have finite rise-fall times, which result in waveform deformities that cause pulse width distortion (PWD) as they propagate through different signal chain elements. The pulse width of the clock or the data line changes due the different threshold voltages and rise-fall times of the digital devices in the path. 🔀 5 shows a datasheet example of propagation delay and PWD that can be found in various devices.

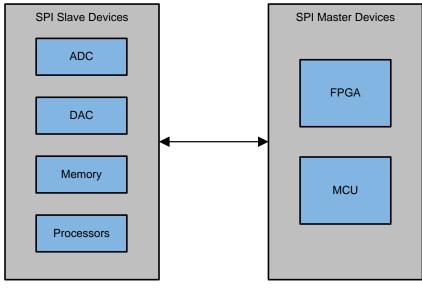

图 3. SPI Block Diagram

| 6.6 | Switching Characteristics, V_{cc} = 3.3 V $\pm$ 0.3 V |  |

|-----|-------------------------------------------------------|--|

|-----|-------------------------------------------------------|--|

| PARAMETER        | FROM    | то       | OUTPUT                 | ٦          | <sub>A</sub> = 25°C |      | -40°C to | 85°C | –40°C to | 125°C | UNIT |    |

|------------------|---------|----------|------------------------|------------|---------------------|------|----------|------|----------|-------|------|----|

| PARAMETER        | (INPUT) | (OUTPUT) | CAPACITANCE            | MIN        | TYP                 | MAX  | MIN      | MAX  | MIN      | MAX   | UNIT |    |

| t <sub>PLH</sub> |         | v        | C <sub>1</sub> = 15 pF |            | 5                   | 7.1  | 1        | 8.5  | 1        | 9.5   |      |    |

| t <sub>PHL</sub> | A       | '        | T                      | CL = 15 pF |                     | 5    | 7.1      | 1    | 8.5      | 1     | 9.5  | ns |

| t <sub>PLH</sub> |         | v        | C <sub>1</sub> = 50 pF |            | 7.5                 | 10.6 | 1        | 12   | 1        | 13    |      |    |

| t <sub>PHL</sub> | A       | ř        | CL = 50 PF             |            | 7.5                 | 10.6 | 1        | 12   | 1        | 13    | ns   |    |

# 图 5. Propagation Delay and PWD

A detailed timing analysis is required to calculate the maximum SPI clock rate by considering the SPI propagation delay and PWD.

# 2.3.1.2 Determining Maximum SPI Clock (SCLK) vs. Distance

In a low latency system, the data in peripheral device should be made available to the host system with minimum delay. There are three major delay contributors in a typical system — SPI peripheral, data link device, and transmission media. Both the SPI peripheral and the data link device have fixed delay; however, the delay in transmission media increases as communication distance increases. In this section, an example on determining the maximum SPI clock speed vs communication distance is shown.

The individual devices used in the calculation are listed in  $\frac{1}{2}$  2

| 表 2. Devices Used in Example | 表 | 2. | Devices | Used in | Example |

|------------------------------|---|----|---------|---------|---------|

|------------------------------|---|----|---------|---------|---------|

| No. | Device     | Description   |

|-----|------------|---------------|

| 1   | SN65LVDS31 | LVDS Driver   |

| 2   | SN65LVDS33 | LVDS Receiver |

| 3   | ADS8910B   | ADC           |

表 3 lists the associated timing parameter values taken from respective device datasheet.

# 表 3. Timing Parameters

| Parameter       | Delay(ns) | Comments                        |

|-----------------|-----------|---------------------------------|

| SN65LVDS31      | 4         |                                 |

| SN65LVDS33      | 3.5       |                                 |

| ADS8910B        | 6.4       | 70MHz clock with 45% duty cycle |

| Cable/PCB trace | 5         | Delay per meter                 |

The equation on finding the maximum SPI clock speed is:

$$SCLK_{Max} = \frac{1}{\left(\left(TX_{Delay} + RX_{Delay} + Cable_{Delay} \times Cable Length\right) \times 2 + ADC_{Delay}\right) \times 2}$$

$$\textcircled{B} 6. Max SPI Speed vs Cable Length$$

Without LVDS interface and if 10cm PCB trace is assumed, then the maximum SPI clock speed achievable for ADS8910B is 67.6MHz. If the distance is increased to 3m for longer range communication, the maximum SPI clock speed is lowered to 13.74MHz under worst conditions.

With LVDS interface and 10cm PCB trace, the maximum SPI clock speed is 22.3MHz. If the distance is increased to 3m for longer range communication, the maximum SPI clock speed is lowered to 9.7MHz under worst conditions.

As distance increase, the propagation delay contributed from cable or trace cannot be ignored.

# 2.3.2 Eliminating Round-Trip Delay

In this section, two solutions are presented to effectively eliminate round trip delay. One solution is a novel design that feeds the SCLK back to the SPI master. The other solution utilize enhanced SPI interface offered in selective TI devices such as ADS8910B ADC.

图 7. Eliminating Round-Trip Delay Block Diagram

# 2.3.2.1 Feed SCLK back to SPI Master

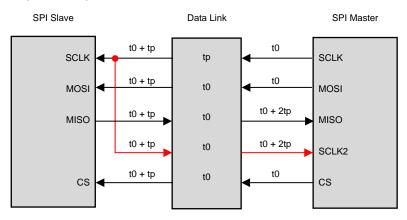

As the SPI host expect to receive data within the same clock cycle, longer propagation delay will cause the returned slave data out of sync with the clock. The solution for restoring synchronicity between the slave data and the clock while maintaining a high data rate is to feed the clock signal from the slave back to the SPI master. A clarifies the benefit of this solution. Here  $t_0$  represents the first rising clock edge, or the start of a data transmission, and  $t_P$  is the data-link propagation delay. After traversing the data link, both the master clock (SCLK) and the master data (MOSI) remain in sync. Feeding back the master clock signal synchronizes the clock with the slave data so that both arrive equally delayed at the master. The only requirement is that the master provide two independent SPI ports, one configured as a master (SPI1) and the other configured as a slave (SPI2). Most modern microcontrollers possess two or more SPI ports, so this requirement poses no problem.

图 8. Feed SCLK back to SPI Master

# 2.3.2.1.1 Timing Analysis when SCLK is routed back to SPI master

If the user can route the returned SCLK signal and the MISO signal at equal length, the delay from cable or trace is effectively eliminated. The equation on calculating the maximum SPI clock speed becomes:

$$SCLK_{Max} = \frac{1}{\left(\left(TX_{Delay} + RX_{Delay}\right) + Cable Length Mismatch + ADC_{Delay}\right) \times 2}$$

Using the same parameter detailed in  $\ddagger$  2.3.1.2, the maximum SCLK speed achievable with LVDS interface is 37MHz under worst condition.

# 2.3.2.2 Enhanced SPI feature offered by Selective TI Devices.

Selective TI Devices such as ADS8910B ADC offers an enhanced SPI interface that offers multiple solutions to effectively eliminate the timing challenge posed by long distance SPI applications.

There are several ways that the enhanced SPI feature could help solving the SPI propagation delay issue.

- Early Data Launch (EDL)

- Increase SPI Bus Width

- Source-Synchronous Protocol

In Early Data Launch mode, the device launches the output data on MISO data pins half a clock earlier compared to the standard SPI protocol, therefore reduce the total delay present in the SPI bus.

ADS8910B also has the option to increase the MISO data bus width from one bit to two bits or four bits. By increasing the MISO data bus, same data rate can be achieved with lower SCLK rate which in turn increases the SPI communication distance. Free LVDS driver and receiver pairs in the quad channel LVDS devices can be used to support the increased data bus width.

In Source-Synchronous mode, the ADS8910B is able to generate clock signal that's synchronize to the SCLK signal and transmit the generated clock signal back to the SPI master. This mode further eliminates the delay by synchronizing the data on MISO bus and the clock signal.

Further detailed implementation of enhanced SPI interface can be viewed in ADS8910B datasheet.

# 2.3.3 Signal Integrity Considerations

In the previous sections, we have detailed ways to extend SPI communication range. As range increase, sending SPI signals from board to board become possible. However, now signal integrity becomes a big concern due to reflections caused by unterminated signal lines. The characteristic impedance of the transmission media and termination impedance will differ substantially, causing an impedance mismatch on the bus. Due to the nature of single-ended signals lines, any external noise will be coupled on the signal line which causes communication errors. Electromagnetic interference (EMI) is also a concern as the high-frequency portion of the SPI signal radiates outward, allowing the signal to couple onto adjacent signals.

This TI design guide presents a solution to address the signal integrity and EMI issue by sending SPI signal over Low Voltage Differential Signaling (LVDS) interface. LVDS has great advantages for handling noise and EMI issue due to its differential signaling nature. Typically the differential pair connecting LVDS driver and receiver is closely coupled. When external noise is present in the environment, both wires will receive nearly equal amount of noise. Since the receiver only cares about the voltage difference between the two wires, the external noise will be canceled out. This is a very important advantage over single ended technology. This property enables LVDS to have a very high signal to noise ratios, and is one of the reasons why LVDS technology is robust.

As a differential circuit, LVDS driver and receiver radiate substantially less electromagnetic wave to the environment than single-ended circuits. As complementary current runs in the differential pair, both line will generate magnetic fields but in the opposite direction. In turn, the magnetic field partially cancels each other. The SN65LVDS31 and SN65LVDS33 LVDS driver and receiver also offers wide common-mode input range from -4V to 5V. It allows a +/-3V ground potential difference to combat ground bounce typically found in high power, high switching environment.

# 3 Hardware, Software, Testing Requirements, and Test Results

# 3.1 Required Hardware and Software

# 3.1.1 Hardware

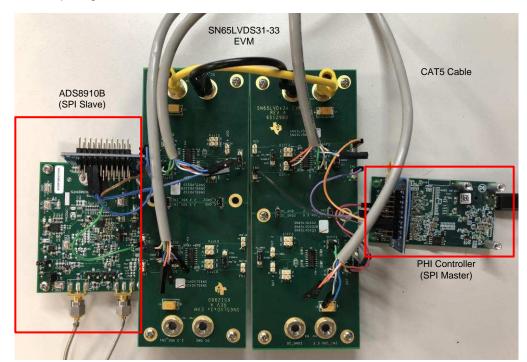

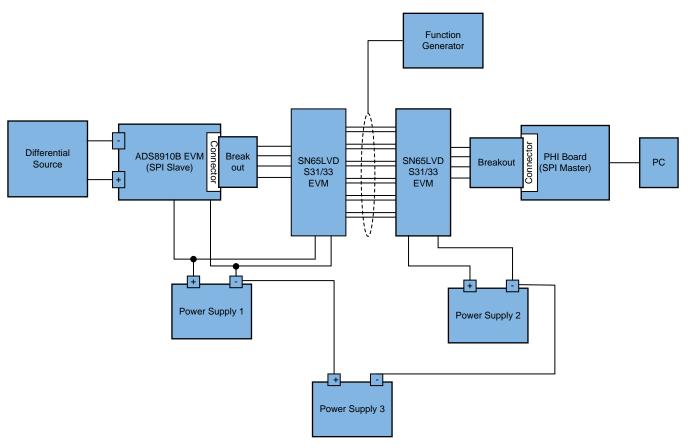

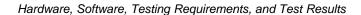

This reference design is realized by combining two SN65LVDS31-33 EVM and one ADS8910B EVM. [3] 9 shows the setup diagram.

图 9. Hardware Setup

# 3.1.2 Software

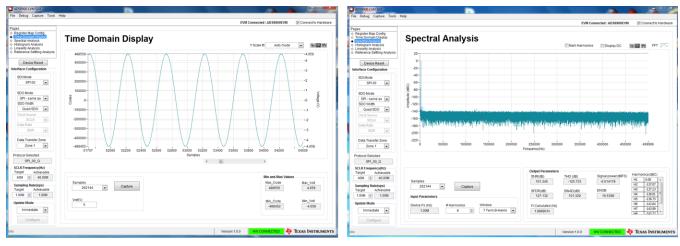

The PHI GUI software, which is based on the LabVIEW<sup>™</sup> platform, validates the TIDA-060017. 图 10 shows the available test options in the PHI GUI.

PHI GUI software can be found at http://www.ti.com/tool/ads8910bevm-pdk

# Hardware, Software, Testing Requirements, and Test Results

图 10. PHI GUI

# 3.2 Testing and Results

# 3.2.1 Test Setup

Three testings was performed to evaluate and compare the performance difference between single-ended SPI communication and SPI communication over LVDS Interface. The input differential source to the ADS8910B ADC is a 2KHz, 2V differential sine wave. The overall test setup for SPI over LVDS is shown as 🕅 11. The overall test setup for single-ended SPI is shown as 🕅 12. A set of breakout boards are used connect Samtec QTH/QSH connectors on ADS8910B EVM to SN65LVDS31/33 EVM. CAT5 cable are used to connect the two SN65LVDS31/33EVM.

图 11. SPI Over LVDS Test Setup

图 12. Single-ended SPI Test Setup

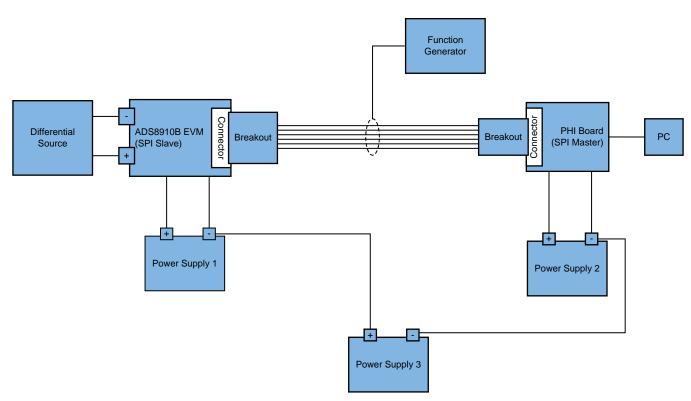

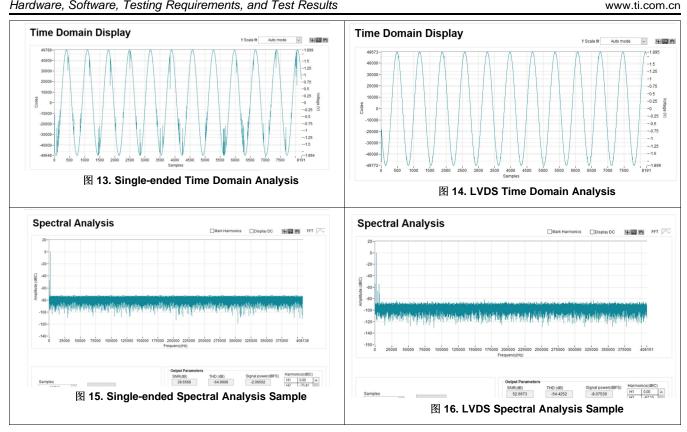

# 3.2.1.1 Noise Immunity Test

The goal of this test is to compare the performance difference between single-ended application, and with LVDS driver and receivers when external noise is coupled on the SPI bus. A signal generator is used to generate controlled transient noise. The amplitude of the generator is adjusted so that the noise applied is kept at 1Vpp, and the frequency is varied. The results are show in  $\frac{1}{8}$  4, and sample time domain analysis and spectral analysis are shown in  $\frac{1}{8}$  13.

| Noise Coupled | Cable Length(m) | Single-ended SPI SNR (dB) | SPI over LVDS SNR (dB) |

|---------------|-----------------|---------------------------|------------------------|

| No Noise      | 0.5             | 101                       | 101                    |

|               | 3               | Fail <sup>(1)</sup>       | 101                    |

| 10KHz         | 0.5             | 99                        | 99                     |

|               | 3               | Fail                      | 97                     |

| 100KHz        | 0.5             | 82                        | 83                     |

|               | 3               | Fail                      | 71                     |

| 500KHz        | 0.5             | 67                        | 69                     |

|               | 3               | Fail                      | 67                     |

| 1MHz          | 0.5             | 58                        | 68                     |

|               | 3               | Fail                      | 59                     |

| 5MHz          | 0.5             | 39                        | 61                     |

|               | 3               | Fail                      | 49                     |

| 10MHz         | 0.5             | 31                        | 52                     |

|               | 3               | Fail                      | 45                     |

表 4. Noise Immunity (varying noise frequency)

<sup>(1)</sup> Single-ended SPI application cannot support 3m cable length.

Hardware, Software, Testing Requirements, and Test Results

A similar test was performed, only this time noise amplitude is increased to 2Vpp, and the frequency is fixed at 10KHz. SPI over LVDS application is able to withstand the higher noise amplitude with a minimum of 45dB SNR. Single-ended SPI application cannot support the increased noise amplitude.

#### 3.2.1.2 Ground Bounce Immunity Test

The goal of the test is to compare ground bounce immunity between single-ended SPI application and LVDS SPI application. The LVDS receiver SN65LVDS33 has a common-mode input range of -4V to 5 V. The test creates a ground potential difference between the ADC board, and the host board. The potential difference is increased while monitoring the signal SNR.

| 表 5. Ground Bounce | Immunity Results |

|--------------------|------------------|

|--------------------|------------------|

|                         | Single-ended SPI | SPI Over LVDS |

|-------------------------|------------------|---------------|

| Ground Bounce Tolerance | -0.1V to +0.1V   | -4V to 5V     |

#### 3.2.1.3 SPI Interface Range Extension Test

The goal of this test is to extend the SPI communication distance, and compare the performance difference between single-ended cables and with LVDS driver and receivers. The effect of cable length on SPI communication is observed by monitoring the signal SNR, and a minimal of 40dB SNR is considered pass. Four different length of CAT5 cables are used to perform this test. Both single-ended and LVDS application transmit data successfully over 0.2m and 0.5m CAT5 cable, and SPI over LVDS application can support 1m and 3m CAT5 cable. However, single-ended SPI application cannot support 1m and 3m cable length due to crosstalk from adjacent signals and energy reflection from unterminated lines.

Hardware, Software, Testing Requirements, and Test Results

# 表 6. Cable Length Tested

| Cable Length | Single-ended SPI | SPI over LVDS |

|--------------|------------------|---------------|

| 0.2m         | Pass             | Pass          |

| 0.5m         | Pass             | Pass          |

| 1m           | Fail             | Pass          |

| 3m           | Fail             | Pass          |

## Design Files

# 4 Design Files

# 4.1 Schematics

To download the schematics, see the design files at TIDA-060017.

# 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-060017.

# 4.3 PCB Layout Recommendations

# 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-060017.

# 4.4 Altium Project

To download the Altium Designer® project files, see the design files at TIDA-060017.

# 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-060017.

# 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-060017.

# 5 Related Documentation

- 1. Texas Instruments, LVDS Owner's Manual, Application Report (SNLA187)

- 2. Texas Instruments, LVDS Design Notes, Application Report (SLLA014)

- 3. Texas Instruments, SN65LVDS31-33EVM User's Guide, Application Report (SLLU016)

- 4. Texas Instruments, ADS8910B EVM User's Guide, Application Report (sbau268)

- 5. Texas Instruments, SN65LVDS31 Data Sheet, Application Report (SLLS261)

- 6. Texas Instruments, SN65LVDS33 Data Sheet, Application Report (SLLS490)

- 7. Texas Instruments, *ADS8910B Data Sheet*, Application Report (SBAS707)

# 5.1 商标

E2E is a trademark of Texas Instruments. Altium Designer is a registered trademark of Altium LLC or its affiliated companies. All other trademarks are the property of their respective owners.

### 有关 TI 设计信息和资源的重要通知

德州仪器 (TI) 公司提供的技术、应用或其他设计建议、服务或信息,包括但不限于与评估模块有关的参考设计和材料(总称"TI 资源"),旨在 帮助设计人员开发整合了 TI 产品的 应用; 如果您(个人,或如果是代表贵公司,则为贵公司)以任何方式下载、访问或使用了任何特定的 TI 资源,即表示贵方同意仅为该等目标,按照本通知的条款进行使用。

TI 所提供的 TI 资源,并未扩大或以其他方式修改 TI 对 TI 产品的公开适用的质保及质保免责声明;也未导致 TI 承担任何额外的义务或责任。 TI 有权对其 TI 资源进行纠正、增强、改进和其他修改。

您理解并同意,在设计应用时应自行实施独立的分析、评价和 判断, 且应全权负责并确保 应用的安全性, 以及您的 应用 (包括应用中使用 的所有 TI 产品))应符合所有适用的法律法规及其他相关要求。你就您的 应用声明,您具备制订和实施下列保障措施所需的一切必要专业知 识,能够 (1) 预见故障的危险后果,(2) 监视故障及其后果,以及 (3) 降低可能导致危险的故障几率并采取适当措施。您同意,在使用或分发包 含 TI 产品的任何 应用前, 您将彻底测试该等 应用 和该等应用所用 TI 产品的 功能而设计。除特定 TI 资源的公开文档中明确列出的测试 外,TI 未进行任何其他测试。

您只有在为开发包含该等 TI 资源所列 TI 产品的 应用时, 才被授权使用、复制和修改任何相关单项 TI 资源。但并未依据禁止反言原则或其他 法理授予您任何TI知识产权的任何其他明示或默示的许可,也未授予您 TI 或第三方的任何技术或知识产权的许可,该等产权包括但不限于任 何专利权、版权、屏蔽作品权或与使用TI产品或服务的任何整合、机器制作、流程相关的其他知识产权。涉及或参考了第三方产品或服务的信 息不构成使用此类产品或服务的许可或与其相关的保证或认可。使用 TI 资源可能需要您向第三方获得对该等第三方专利或其他知识产权的许 可。

TI 资源系"按原样"提供。TI 兹免除对 TI 资源及其使用作出所有其他明确或默认的保证或陈述,包括但不限于对准确性或完整性、产权保证、 无屡发故障保证,以及适销性、适合特定用途和不侵犯任何第三方知识产权的任何默认保证。

TI 不负责任何申索,包括但不限于因组合产品所致或与之有关的申索,也不为您辩护或赔偿,即使该等产品组合已列于 TI 资源或其他地方。 对因 TI 资源或其使用引起或与之有关的任何实际的、直接的、特殊的、附带的、间接的、惩罚性的、偶发的、从属或惩戒性损害赔偿,不管 TI 是否获悉可能会产生上述损害赔偿,TI 概不负责。

您同意向 TI 及其代表全额赔偿因您不遵守本通知条款和条件而引起的任何损害、费用、损失和/或责任。

本通知适用于 TI 资源。另有其他条款适用于某些类型的材料、TI 产品和服务的使用和采购。这些条款包括但不限于适用于 TI 的半导体产品 (http://www.ti.com/sc/docs/stdterms.htm)、评估模块和样品 (http://www.ti.com/sc/docs/sampterms.htm) 的标准条款。

> 邮寄地址:上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2018 德州仪器半导体技术(上海)有限公司