## TI 设计: TIDA-01525 8 通道 16 位 200mA 电流输出数模转换器参考设计

# TEXAS INSTRUMENTS

### 说明

多系统,如激光器驱动 应用,要求具备灵活、精确的高 通道数电流源此外,随着所需通道的增加,行业正向更 小尺寸解决方案的方向发展。该参考设计结合了 DAC80508 8 通道 16 位 DAC 小体积、高性能的优点, 同时具备精确的运算放大器,可创建高密度、精确的电 流源解决方案。参考设计的最大输出电流为 200mA,允 许最小 PVDD 供电电压,以降低功耗,实现高效率。该 参考设计还 具有 电流噪声输出低的特点,这得益于 DAC80508 的低参考电压噪声和 OPA2376 的低电压和 电流噪声。

#### 资源

| TIDA-01525 | 设计文件夹 |

|------------|-------|

| DAC80508   | 产品文件夹 |

| OPA2376    | 产品文件夹 |

| CSD13381F4 | 产品文件夹 |

| CSD23285F5 | 产品文件夹 |

|            |       |

### 特性

- 8 通道可编程电流, 200mA 范围

- 16 位分辨率

- 高通道密度

- < 120µA 失调电压错误

- 总体未调整误差 < 1.5%

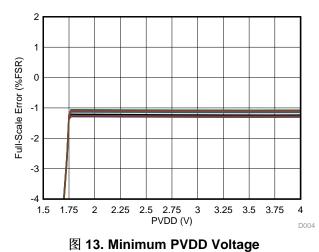

- 1.75V 最小PVDD供电

- 3.4µA<sub>RMS</sub> 带宽限制电流噪声

- 10 nA/√Hz10 kHz 电流噪声

### 应用

- 光学模块激光器驱动

- 光学模块可调激光器

该 TI 参考设计末尾的重要声明表述了授权使用、知识产权问题和其他重要的免责声明和信息。

### 1 System Description

The objective of this reference design is to demonstrate a compact high-side current-source design that can be implemented with a multichannel DAC, op amps, and discrete components. This design uses components that offer a high level of flexibility, and can be used in many different environments. The key component of the design is the DAC80508 device. The device features eight DAC channels at 16-bit resolution that can be set to either a 1.25-V, 2.5-V, or 5-V range while using the internal reference. This DAC is a voltage-output device, so an external voltage-to-current (V/I) stage is added to the design. To implement the V/I stage, create an accurate reference current that is amplified using a current mirror.

Laser-diode applications generally require a precisely controlled current to regulate the output power. An adjustable current is advantageous because the laser output-power can shift over temperature. For this reason, a DAC can be used to dynamically update the forward current. In addition, use a low-noise source to reduce the intensity noise (instability in the output power) of a laser output. The DAC 16-bit resolution allows the power to be fine-tuned, but the same design could be used with the 14-bit DAC70508 and 12-bit DAC60508 devices, which are pin-for-pin compatible with the DAC80508.

### 1.1 Key System Specifications

| PARAMETER                                | SPECIFICATIONS                                     | DETAILS   |

|------------------------------------------|----------------------------------------------------|-----------|

| Current-source supply voltage            | 2 V, nominal                                       | 节 2.2.3   |

| DAC80508 and OPA2376 supply voltage      | 5 V                                                | 节 2.2.1   |

| DAC resolution and performance           | 16-bit, ±1 LSB INL/DNL                             | 节 2.3.1   |

| Current-source full-scale output current | 200 mA                                             | 节 2.2.3   |

| Total unadjusted error                   | < 1.5% FSR at 25°C                                 | 节 3.2.2.1 |

| Current-noise density                    | 10 nA/ $\sqrt{Hz}$ at 10 kHz and full-scale output | 节 3.2.2.2 |

| Bandwidth limited RMS current noise      | 3.4 µA <sub>RMS</sub> at midscale output           | 节 3.2.2.3 |

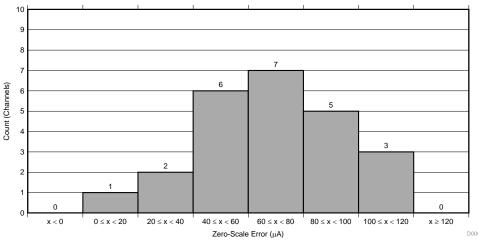

| Zero-scale error                         | < 120 µA                                           | 节 3.2.2.4 |

| Minimum PVDD supply voltage              | 1.75 V at full-scale output                        | 节 3.2.2.5 |

### 表 1. Key System Specifications

### 2 System Overview

### 2.1 Block Diagram

图 1 shows a block diagram of the system.

图 1. TIDA-01525 Block Diagram

### 2.2 Design Considerations

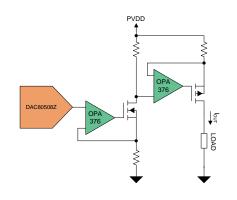

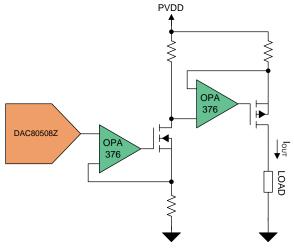

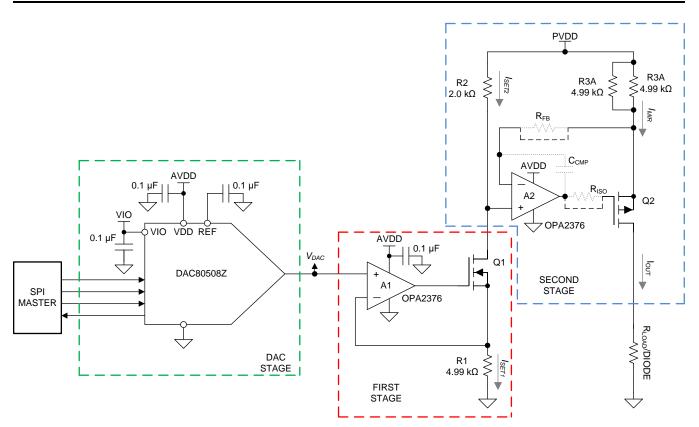

This section describes the system, and the major subcircuits in the design. The system design can be considered to be made up of three main sections: the DAC stage, the V/I converter first stage, and the V/I converter second stage, as shown in  $\bigotimes$  2.

图 2. TIDA-01525 Theory of Operation

8 通道 16 位 200mA 电流输出数模转换器参考设计

ZHCU595-November 2018

4

System Overview

### 2.2.1 DAC Output Stage

For this design, the DAC is configured externally with an SPI master. The voltage level of the communication is determined by VIO, which is supplied externally at 3.3 V. The analog portion of the DAC is powered with AVDD, which is also shared with the op amps. For the purpose of the device testing, 5 V is used for AVDD. The DAC80508 allows for 2.7 V minimum, whereas the OPA2376 can operate as low as 2.2 V. Therefore, power consumption of AVDD can be reduced by operating at 2.7 V.

The DAC80508 is configured to use the internal reference, which has an external  $0.1-\mu$ F capacitor that helps filter noise generated by the reference. The internal reference is the primary source of noise in the system, so an external, low-noise reference provides superior noise performance. However, an external low-noise reference adds additional cost and board space to the system, so the external reference was not featured in this design.

The DAC80508 features a reference attenuator that divides the reference by two. This setting is used by the system to allow the maximum output range of the DAC to be 1.25 V. This lower voltage allows the PVDD supply to be minimized, and reduces the power dissipated by the output MOSFET, Q2.

### 2.2.2 First Op Amp Stage

$I_{SET1} = V_{DAC} \div R1$

(1)

(2)

(3)

System Overview

注: The absolute value of the R1 influences the final output gain of the circuit, and any difference between the real and ideal value appears as a gain error on the final output current. For this reason, make sure to select a precise resistor.

The current generated by this stage does not contribute to the final output current; therefore, minimizing this current is critical for optimizing the efficiency of the system. Power dissipated in the R1 can be calculated using  $\Delta \chi 2$

$$P_{R1} = V_{DAC}^{2} / R1$$

For this design, R1 is set to be 4.99 kΩ. When the DAC is at full-scale output voltage,  $I_{SET1}$  is calculated to be approximately 250 µA, as shown in 23 3:

$I_{\text{SET1 FULL-SCALE}} = 1.25 \text{ V} \div 4.99 \text{ k}\Omega = 250.5 \text{ }\mu\text{A}$

### 2.2.3 Second Op Amp Stage

The second stage of the system is a precision current-mirror with a gain set by R2 and R3. The voltage across resistor R2 is determined by the reference current created by the first stage. Current  $I_{SET2}$  is ideally the same as  $I_{SET1}$ , and creates a voltage drop across R2. The voltage across R2 is the same voltage across R3 because amplifier A2 uses p-channel MOSFET Q2 to draw the current from PVDD to make sure that the input nodes are the same potential. This relationship is shown in  $\Delta$  4:

$I_{SET1} \times R2 = I_{MIR} \times R3$ (4)

The current gain of this system is then expressed by  $\Delta \pm 5$ :

Current Gain =  $I_{MIR} \div I_{SET1} = R2 \div R3$

(5)

(6)

(7)

In this system, R2 is selected to be 2 k $\Omega$  and R3 is selected to be 2.495  $\Omega$ . This value is created in the application by using two resistors in parallel, which allows smaller resistors with lower power ratings to be used.  $\Delta$  $<math> \pm$  6 shows the current gain given these resistor values.

Current Gain = 2 k $\Omega$  ÷ 2.495  $\Omega$  = 801.6 A/A

The gain of the system can now be express using  $\Delta \pm 7$ :

$I_{OUT} = (V_{DAC} \times R2) / (R1 \times R3)$

8 通道 16 位 200mA 电流输出数模转换器参考设计

Using the values selected for the system, the full-scale output current can be calculated as shown in 23.

| R1 = 4.99 kΩ, R2 = 2 kΩ, R3 = 2.495 Ω                                | (8)  |

|----------------------------------------------------------------------|------|

| $I_{OUT-MAX} = (1.25 V \times 2 k\Omega) / (4.99 kΩ \times 2.495 Ω)$ | (9)  |

| I <sub>OUT-MAX</sub> = 200.801 mA                                    | (10) |

There are a few sources of error in this stage. Firstly, the gain error of the stage is determined by how well resistors R2 and R3 are proportionally matched; for this reason, use precision resistors. Secondly, amplifier A2 contributes to error with the voltage offset of the inputs. The offset results in a voltage across R2 that is not the same as the voltage across R3. This offset ultimately looks like an offset error on the output, and necessitates the selection of an amplifier that has low offset voltage. Finally, the bias current of the amplifier causes the current flowing through R2,  $I_{SET2}$ , to not exactly match the reference current,  $I_{SET1}$ . This mismatch also results in an offset error on the output. Selecting an amplifier with a a bias current that is much lower than the reference current minimizes this error. The bias current also impacts the  $I_{MIR}$  current, but as that current is already very large, the impact is only a small offset error.

For the reasons discussed, the OPA2376 is selected because this device has low bias current and offset, while still being a small package and capable of rail-to-rail operation.

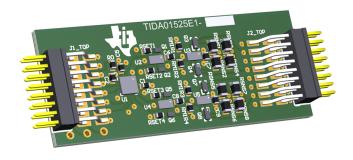

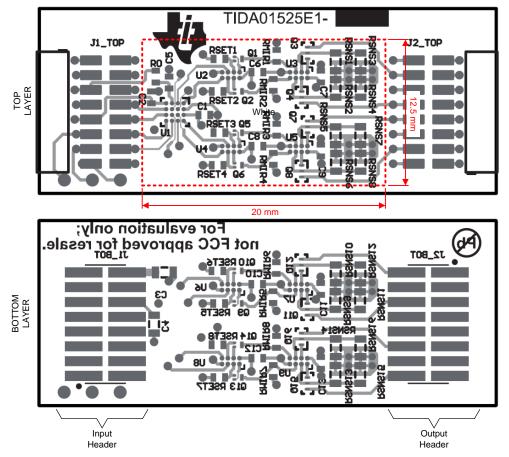

### 2.2.4 PCB Design

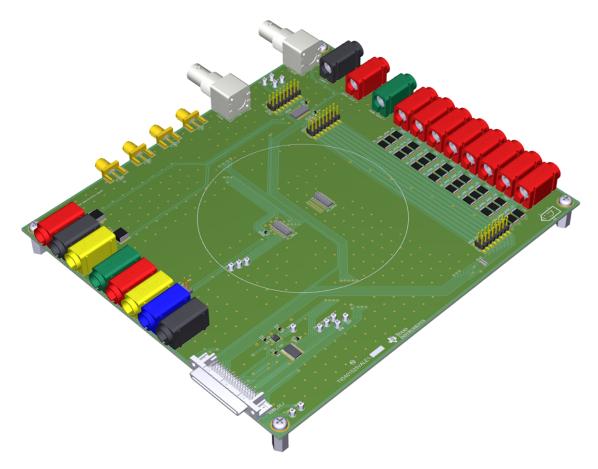

S shows the printed circuit board (PCB) layout of the TIDA-01525 design top and bottom layer. This board has two internal layers: a ground layer and supply layer for PVDD. A majority of the PCB is dedicated to input and output headers that are necessary to improve the usability of the design during testing. The denoted box on the figure show the approximate area that was used on the top and bottom layer to implement all eight channels of the design. The selection of small components and compact layout result in a high-density design.

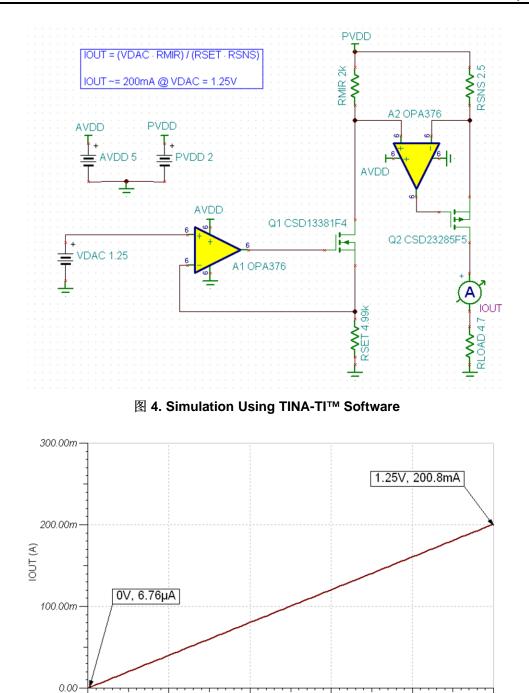

### 2.2.5 TINA-TI<sup>™</sup> Simulation Software

The output transfer function can be verified using the TINA-TI<sup>™</sup> simulation software. 🕅 4 shows the simulation. The DAC80508 is simulated with an ideal voltage source for this experiment. Accurate models for the OPA2376 and both MOSFETs are available at the product pages for those devices. 🕅 5 shows the simulated results, and verifies that the transfer function result is the expected full-scale output current.

VDAC (V)

. 500.00m

. 250.00m

### 2.3 Highlighted Products

0.00

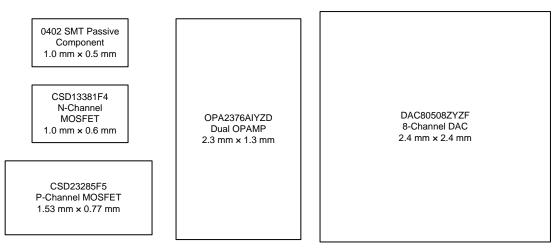

The following highlighted products are used in this reference design. The key features for selecting the devices for this reference design are outlined in the following subsections. For the complete details of the highlighted devices, refer to the respective product data sheets. As many laser drive applications require a high channel density, a major factor in the component selection for this reference design is a small package size. If 6 shows a relative comparison of the size of the major components of the system.

1.00

1.25

9

750.00m

图 6. Package Size Comparison

### 2.3.1 DAC80508

The DAC80508 is a pin-compatible family of low-power, eight-channel, buffered voltage-output, digital-toanalog converters (DACs) with 16-bit resolution. The DAC80508 includes a 2.5-V, 5-ppm/°C internal reference that eliminates the need for an external precision reference in most applications. A userselectable gain configuration provides full-scale output voltages of 1.25 V (gain =  $\frac{1}{2}$ ), 2.5 V (gain = 1) or 5 V (gain = 2). The device operates from a single 2.7-V to 5.5-V supply, is specified monotonic, and provides high linearity of ±1 LSB INL.

Communication to the DAC80508 is performed through a serial interface that operates at clock rates of up to 50 MHz. The VIO pin enables serial interface operation from 1.7 V to 5.5 V. The flexible interface of the DAC80508 enables operation with a wide range of industry-standard microprocessors and microcontrollers.

The DAC80508 incorporates a power-on-reset circuit that powers up and maintains the DAC outputs at either zero scale or midscale until a valid code is written to the device. The device consumes low current of 0.6 mA/channel at 5.5 V, making the device suitable for battery-operated equipment. A per-channel power-down feature reduces the device current consumption to 15  $\mu$ A.

The DAC80508 is characterized for operation over the temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C, and is available in a 2.4-mm × 2.4-mm WCSP package. This small package size makes this device an excellent choice for high-density applications.

### 2.3.2 OPA2376

The OPA2376 is a dual, low-noise, e-trim<sup>TM</sup> operational amplifier that offers outstanding dc precision and dc performance. Rail-to-rail input and output, low offset (25  $\mu$ V, maximum), low noise (7.5 nV/ $\sqrt{\text{Hz}}$ ), quiescent current of 950  $\mu$ A (maximum), and a 5.5-MHz bandwidth make this device very attractive for a variety of precision and portable applications. The PVDD supply used for the laser is often minimized to reduce power consumption of the MOSFET and resistor on the output stage of the design. Therefore, the rail-to-rail output feature of the device makes it an excellent choice for the high-side current source for laser-drive applications. This dual op amp is offered in a small, 2.3-mm x 1.3-mm DSBGA package.

### 2.3.3 CSD13381F4 and CSD23285F5

The FemtoFET<sup>TM</sup> MOSFETs in this design are selected because of their very small package size. The CSD13381F4 is a 140-m $\Omega$ , 12-V N-channel MOSFET designed and optimized to minimize the footprint in many handheld and mobile applications. The N-channel MOSFET is offered in a 1.0-mm × 0.6-mm package. The CSD23285F5 is a 29-m $\Omega$ , -12-V, P-Channel MOSFET that features a 1.53-mm × 0.77-mm package.

### 3 Hardware, Software, Testing Requirements, and Test Results

### 3.1 Required Hardware

### 3.1.1 Hardware

图 7. Test Board

### Hardware, Software, Testing Requirements, and Test Results

### 3.2 Testing and Results

### 3.2.1 Test Setup

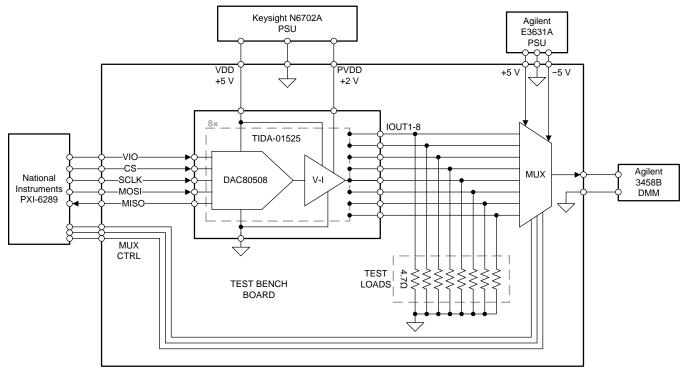

The test setup for this design features four pieces of external equipment.

The National Instrument PXI-6289 features digital I/O used to generate the SPI data that control the DAC80508 device on the TIDA-01525 board. In addition, the digital I/O is used to control the MUX featured on the test board that connects the IOUT signals to external meters. Although not shown in 🕅 8, the PXI-6289 18-bit ADC analog inputs are also connected to the IOUT signals. This connection allows for fast parallel measurement of the IOUT signals, although higher levels of averaging must be implemented to achieve very accurate measurements.

The meter in this system is the Agilent 3458B, an 8.5-digit, digital multimeter (DMM). For the majority of the tests, the 3458B is configured to operate in a 1-V range, with two power-line cycles per acquisition. For some of the test, the DMM was removed from the system and replaced with an oscilloscope or spectrum analyzer.

The system is powered by two supplies. The first supply, an Agilent E3631A triple-rail supply, is used to power the onboard MUX. To provide accurate measurements of the IOUT pins, the MUX needs additional negative headroom, so the negative supply input of the MUX is connected to a -5-V potential. The other supply is a Keysight N6702A modular power supply mainframe. This supply sources the nominal +5-V input for the DAC80508 and OPA2376s featured in the design. The high-current PVDD supply was also sourced from the N6702A. Take care to select a supply that can source the maximum expected current of 1.6 A (8 channels × 200 mA).

**8** shows that 4.7- $\Omega$  load resistors are used on the IOUT signals to convert the current output to a voltage for easy measurement with the 3458B. Given that our expected maximum current is approximately 200 mA, a load of 4.7  $\Omega$  has a maximum voltage differential of 940 mV. This output range is optimized for the DMM high-precision 1-V range.

图 8. Test Setup Block Diagram

### 3.2.2 Test Results

This section describes the test measurements accomplished on the system, and describes the setup and configuration used to realize them.

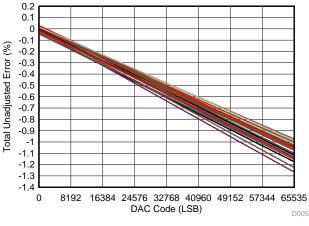

### 3.2.2.1 Total Unadjusted Error

### 3.2.2.1.1 Total Unadjusted Error Test Configuration

Total unadjusted error is measured on the system using the configuration shown in 🖄 9. Total unadjusted error, or TUE, is the difference between the actual measured transfer function of the system and the ideal transfer function as calculated. This error is unadjusted; therefore, error from sources like resistor mismatch, reference inaccuracy, and DAC nonlinearity are not removed from the calculation.

The resistive values of the test loads must be accurately known, so that any error in those resistors is not represented in the measurement. To validate this condition, the individual resistance values were directly measured on the board and logged. The resistors must be directly measured so that the ON resistance of the MUX is not added to the resistor values. In addition, care must be taken to insulate these resistors from temperature change during the test.

The data for the measurement is collected by using the PXI-6289 to sweep the DAC80508 input code for all channels. After each code is sent to the DAC, the PXI-6289 sets the MUX to each channel, and the 3458A measures the value. This value is then divided by the known resistor value of the test loads, and the calculated current value is then logged. Make sure to allow a short time delay after changing the MUX input to allow the output to settle.

### 3.2.2.1.2 Total Unadjusted Error Measurement Results

8 9 shows the total unadjusted error for three systems, all channels. There are two main components to the error, offset error and gain error. The offset error is mostly the result of the DAC itself, with some additional offset contributed by the V<sub>os</sub> of the two amplifiers. The gain error can be attributed to the errors in the resistor values, with the DAC reference also contributing a small portion. An external reference for the DAC improves the accuracy, but at the expense of board space and additional cost.

图 9. Total Unadjusted Error

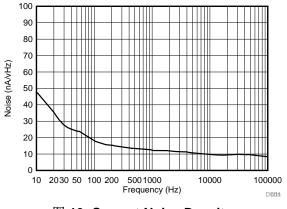

### 3.2.2.2 Current Noise Density

### 3.2.2.2.1 Current Noise Density Measurement Setup

The current noise density is measured with the National Instruments PXI-5922, a high-precision oscilloscope. For this test configuration, the DAC80508 is programmed by the PXI-6289 to the full-scale output current, 200 mA. The test board is configured to connect a channel through the MUX to the PXI-5922, taking the place of the 3458B DMM. The PXI-5922 is then used to capture many thousands of samples for a few seconds, which are then processed by a program to generate a FFT of the data. This result was also scaled back to a current value and converted to the power domain.

### 3.2.2.2.2 Current Noise Density Results

The current noise density is measured from 10 Hz to 100 kHz. The noise in the system is dominated by the DAC80508 internal voltage reference. Using the internal reference results in the system being less complex, and allows for cost savings; however, noise can be improved by using an external reference.

图 10. Current Noise Density

### 3.2.2.3 Bandwidth-Limited RMS Current Noise

### 3.2.2.3.1 Bandwidth-Limited RMS Current Noise Setup

The bandwidth-limited RMS noise is measured in the same fashion as 图 10, with additional measurements at one-quarter scale and half scale. The RMS noise value is calculated from the noise spectral density. This calculation is achieved by integrating the square of the current noise spectral density over the bandwidth of interest to calculate noise power. The RMS noise current is the square-root of the noise power, which is the integral of the square of the noise density, as shown in 公式 11. In this case, the bandwidth of the measurement is limited from 10 Hz to 100 kHz.

Noise Current =

$$\sqrt{\text{Noise Power}} = \sqrt{\int_{f_1}^{f_2} i_n^2} df$$

(11)

### 3.2.2.3.2 Bandwidth-Limited RMS Current Noise Measurement

$\frac{1}{8}$  2 shows the calculated current noise based from the noise spectrum measurements at the different DAC output values.

| DAC Output Code (LSB) | Approximate Current Output (mA) | Current Noise (µA <sub>RMS</sub> ) |

|-----------------------|---------------------------------|------------------------------------|

| 0x4000                | 50                              | 3.1                                |

| 0x8000                | 100                             | 3.4                                |

| 0xFFFF                | 200                             | 4.3                                |

表 2. Bandwidth-Limited RMS Current Noise

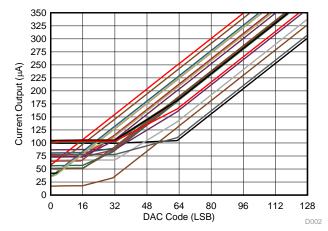

### 3.2.2.4 Zero-Scale Error

Zero-scale error (ZSE) is the output current when the DAC is outputting the lowest possible value. The DAC80508 features a unipolar supply input, meaning that the device does not have a negative supply. As a result, the output at code zero is not 0 V, but rather the closest voltage the output buffer can supply with respect to ground. ZSE can be critical in current-source applications, specifically laser-drive, because the zero-scale current can be considered wasted energy or even enable some low-power output state to occur.

### Hardware, Software, Testing Requirements, and Test Results

### 3.2.2.4.1 Zero-Scale Error Setup

The zero-scale error is measured by using the PXI-6289 to configure the DAC80508 device to the 1.25-V output range and configure the DAC values to code zero. The DMM is then used to measure the current on the output of each channel. The ZSE is calculated as the difference between the real output current and the ideal output current. The ZSE is easy to calculate because the ideal current at code zero is 0 A, so any current measured is entirely error.

### 3.2.2.4.2 Zero-Scale Error Measurement

The output behavior of the system is seen in  $\mathbb{X}$  11. As discussed previously, the DAC cannot output 0 V, and requires a minimum headroom for the output buffer to accurately drive the output voltage.  $\mathbb{X}$  11 shows that the system requires approximately 64 LSB before the DAC can operate in the linear region.  $\mathbb{X}$  12 shows the distribution of the zero-scale error for all eight channels of three systems. The maximum voltage measured is below 120  $\mu$ A of error.

图 12. Zero-Scale Error Measurement

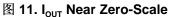

### 3.2.2.5 Minimum PVDD Supply Voltage

Any voltage headroom that is not necessary for the voltage drop across the load or diode and the voltage across R3 results in extra power dissipation across the P-channel MOSFET. Therefore, a key design goal for high-side current-sources in laser drive applications is to minimize the PVDD supply. However, minimizing PVDD can result in extra heat generation and general inefficiency. The minimum supply voltage is the lowest PVDD voltage the system can use while still being able to source the desired full-scale current.

### 3.2.2.5.1 Minimum PVDD Supply Voltage Setup

The minimum supply voltage was measured by using the PXI-6289 to set the DAC output to the full-scale value, 0xFFFF, or approximately 200 mA on the current output. While in this state, the DMM is used to measure the current output, while the N6702A is used to incrementally lower the PVDD supply. The full-scale current error is calculated at each point. At some point, the system cannot source the correct current and the FSE rapidly changes.

### 3.2.2.5.2 Minimum PVDD Supply Voltage Measurement

图 13 shows the FSE as the PVDD is varied from 1.5 V to 4 V. 图 13 shows that the FSE is relatively constant until the PVDD supply becomes less than 1.75 V. This This supply voltage is the minimum required headroom voltage for the system. The voltage across R1 will be 1.25 V unless the DAC range is modified, and the reference current created induces a voltage of approximately 500 mV across R2. These two voltages make the required 1.75 V, as shown in 图 13. If lower voltage (and power dissipation) is desired, scale back the resistor values of R2 and R3 to a lower value, while still maintaining the same ratio.

### 4 Design Files

### 4.1 Altium Files

### 4.1.1 Schematics

To download the schematics, see the design files at TIDA-01525.

### 4.1.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01525.

### 4.1.3 PCB Layout Recommendations

When designing the PCB for the reference circuit, consider the following layout recommendations:

- Place the capacitor for the DAC80508 reference output close to the pin in order to minimize external noise from being coupled into the reference voltage.

- Bypass all power supply pins to ground with a low ESR ceramic bypass capacitor. The typical recommended bypass capacitance is 0.1-μF to 0.22-μF ceramic with a X7R or NP0 dielectric.

- Use wider trace widths for the current output path that can accommodate the full-scale current.

- Connect R3 to a large copper area to assist in heat dissipation.

### 4.1.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-01525.

### 4.2 Gerber Files

To download the Gerber files, see the design files at TIDA-01525.

### 4.3 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01525.

### 5 Related Documentation

- 1. High-Side Voltage-to-Current (V-I) Converter Design Guide

- 2. High-Density DACs Offer Superior Noise And Accuracy Performance in Laser-Drive Applications Application Brief

### 5.1 商标

TINA-TI, e-trim, FemtoFET are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

### 6 About the Author

**Paul Frost** is an Applications Engineer with the Digital to Analog Converters team supporting catalog, industrial, and audio DACs. He earned his BSCE from University of Arizona.

#### 重要声明和免责声明

TI 均以"原样"提供技术性及可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证其中不含任何瑕疵,且不做任何明示或暗示的担保,包括但不限于对适销性、适合某特定用途或不侵犯任何第三方知识产权的暗示担保。

所述资源可供专业开发人员应用TI产品进行设计使用。您将对以下行为独自承担全部责任:(1)针对您的应用选择合适的TI产品;(2)设计、验证并测试您的应用;(3)确保您的应用满足相应标准以及任何其他安全、安保或其他要求。所述资源如有变更,恕不另行通知。TI对您使用所述资源的授权仅限于开发资源所涉及TI产品的相关应用。除此之外不得复制或展示所述资源,也不提供其它TI或任何第三方的知识产权授权许可。如因使用所述资源而产生任何索赔、赔偿、成本、损失及债务等,TI对此概不负责,并且您须赔偿由此对TI及其代表造成的损害。

TI所提供产品均受TI的销售条款 (http://www.ti.com.cn/zh-cn/legal/termsofsale.html) 以及ti.com.cn上或随附TI产品提供的其他可适用条款的约束。TI提供所述资源并不扩展或以其他方式更改TI 针对TI 产品所发布的可适用的担保范围或担保免责声明。

邮寄地址:上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2018 德州仪器半导体技术(上海)有限公司

#### 重要声明和免责声明

TI 均以"原样"提供技术性及可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证其中不含任何瑕疵,且不做任何明示或暗示的担保,包括但不限于对适销性、适合某特定用途或不侵犯任何第三方知识产权的暗示担保。

所述资源可供专业开发人员应用TI产品进行设计使用。您将对以下行为独自承担全部责任:(1)针对您的应用选择合适的TI产品;(2)设计、验证并测试您的应用;(3)确保您的应用满足相应标准以及任何其他安全、安保或其他要求。所述资源如有变更,恕不另行通知。TI对您使用所述资源的授权仅限于开发资源所涉及TI产品的相关应用。除此之外不得复制或展示所述资源,也不提供其它TI或任何第三方的知识产权授权许可。如因使用所述资源而产生任何索赔、赔偿、成本、损失及债务等,TI对此概不负责,并且您须赔偿由此对TI及其代表造成的损害。

TI所提供产品均受TI的销售条款 (http://www.ti.com.cn/zh-cn/legal/termsofsale.html) 以及ti.com.cn上或随附TI产品提供的其他可适用条款的约束。TI提供所述资源并不扩展或以其他方式更改TI 针对TI 产品所发布的可适用的担保范围或担保免责声明。

邮寄地址:上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2018 德州仪器半导体技术(上海)有限公司