# TMS320x281x DSP External Interface (XINTF) Reference Guide

Literature Number: SPRU067C May 2002 Revised November 2004

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from TI under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address:

Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

# **Contents**

| 1 | Func         | tional Description                                               | 9  |

|---|--------------|------------------------------------------------------------------|----|

|   | 1.1          | Accessing XINTF Zones                                            |    |

|   | 1.2          | Write-Followed-by-Read Pipeline Protection                       | 13 |

| 2 | XINT         | F Configuration Overview                                         | 15 |

|   | 2.1          | Procedure to Change the XINTF Configuration and Timing Registers |    |

|   | 2.2          | XINTF Clocking                                                   |    |

|   | 2.3          | Write Buffer                                                     |    |

|   | 2.4          | XINTF Access Lead/Active/Trail Wait-State Timing Per Zone        |    |

|   | 2.5          | XREADY Sampling For Each Zone                                    |    |

|   | 2.6          | Bank Switching                                                   |    |

|   | 2.7          | Effects of the XMP/MC Signal on the XINTF                        | 20 |

| 3 | Conf         | iguring Lead, Active, and Trail Wait States                      | 21 |

| 4 | XINT         | F Registers                                                      | 26 |

|   | 4.1          | XINTF Timing Registers                                           |    |

|   | 4.2          | XINTF Configuration Register                                     | 31 |

|   | 4.3          | XBANK Register                                                   |    |

|   | 4.4          | XREVISION Register                                               | 35 |

| 5 | Signa        | al Descriptions                                                  | 36 |

| 6 | Wave         | eforms                                                           | 38 |

| 7 | Exter        | nal DMA Support (XHOLD, XHOLDA)                                  | 43 |

| Α | Revis<br>A.1 | sion History A<br>Changes Made in This Revision A                |    |

# Figures

| 1.  | External Interface Block Diagram                  | 10 |

|-----|---------------------------------------------------|----|

| 2.  | Zone 0/Zone 1 Chip-Enable Logic                   | 12 |

| 3.  | Zone 7 Memory Map                                 | 13 |

| 4.  | Access Flow Diagram                               | 16 |

| 5.  | Relationship Between XTIMCLK and SYSCLKOUT        | 17 |

| 6.  | XTIMING0/1/2/6/7 Register Layout                  |    |

| 7.  | XINTCNF2 Register                                 | 31 |

| 8.  | XBANK Register                                    | 34 |

| 9.  | XREVISION Register Layout                         |    |

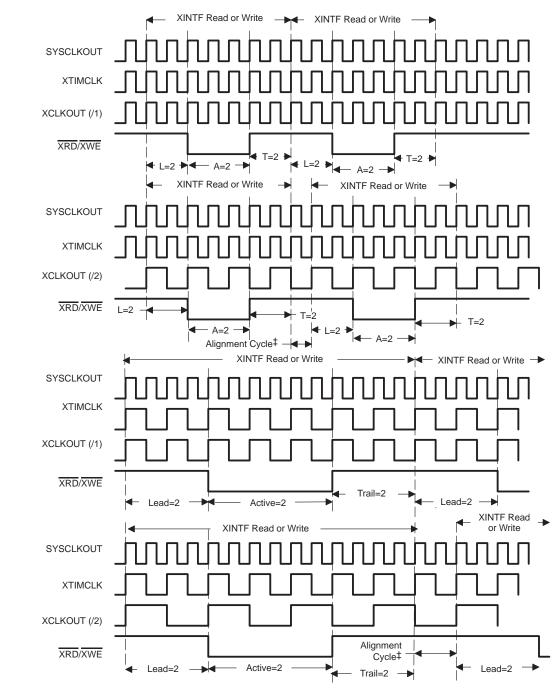

| 10. | XTIMCLK and XCLKOUT Mode Waveforms                | 39 |

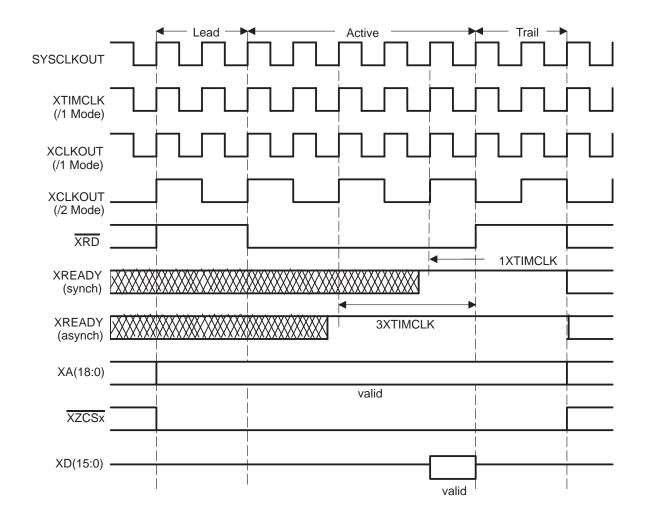

| 11. | Generic Read Cycle (XTIMCLK = SYSCLKOUT mode)     | 40 |

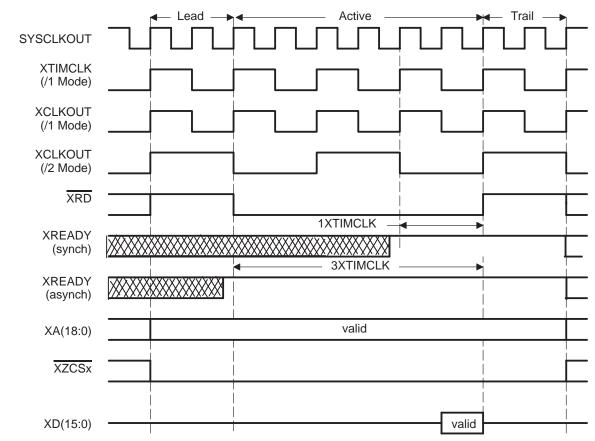

| 12. | Generic Read Cycle (XTIMCLK = 1/2 SYSCLKOUT mode) | 41 |

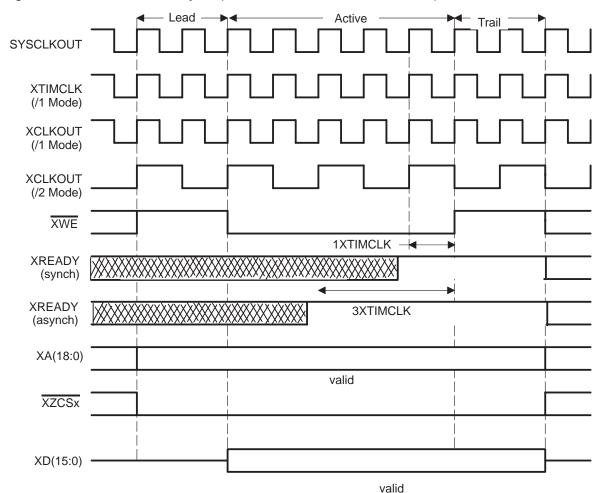

| 13. | Generic Write Cycle (XTIMCLK = SYSCLKOUT mode)    | 42 |

# **Tables**

| 2. | Pulse Duration in Terms of XTIMCLK Cycles                                          | 23 |

|----|------------------------------------------------------------------------------------|----|

|    | XINTF Configuration and Control Register Mapping         XINTF Signal Descriptions |    |

This page is intentionally left blank.

The external interface (XINTF) is a nonmultiplexed asynchronous bus, similar to the C240x external interface.

This reference guide is applicable for the XINTF found on the TMS320x281x family of processors. This includes all Flash-based, ROM-based, and RAM-based devices within the 281x family.

### 1 Functional Description

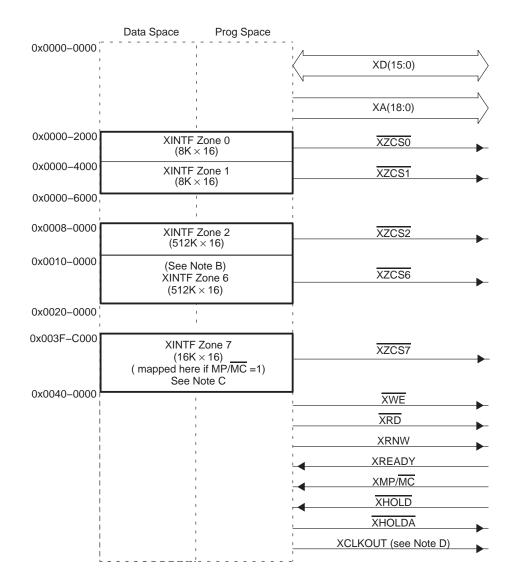

The XINTF on the 2812 is mapped into five fixed memory-mapped zones as defined in Figure 1.

Each of the 28x XINTF zones has a chip-select signal that is toggled when an access is made to that particular zone. On some devices the chip-select signals for two zones may be internally ANDed together to form a single shared chip select. In this manner, the same memory is connected to both zones or external decode logic can be used to separate the two.

Each of the five zones can also be programmed with a specified number of wait states, strobe signal set-up and hold timing. The number of wait states, set-up and hold timing is separately specified for a read access and a write access. In addition, each zone can be programmed for extending wait states externally using the XREADY signal or not. The programmable wait-state, chip-select and programmable strobe timing enables glueless interface to external memories and peripherals.

You specify the set-up/hold and access wait states for each XINTF zone by configuring the associated XTIMINGx registers. The access timing is based on an internal clock called XTIMCLK. XTIMCLK can be set to the same rate as the SYSCLKOUT or to one-half of SYSCLKOUT. The rate of XTIMCLK applies to all of the XINTF zones. XINTF bus cycles begin on the rising edge of XCLKOUT and all timings and events are generated with respect to the rising edge of XTIMCLK.

# Figure 1. External Interface Block Diagram (See Note A)

- NOTES: A. Each zone can be programmed with different wait states, setup and hold timings, and is supported by zone chip selects (XZCS0AND1, XZCS2, XZCS6AND7), that toggle when an access to a particular zone is performed. These features enable glueless connection to many external memories and peripherals.

- B. Zones 3 5 are reserved for future expansion.

- C. The mapping of XINTF Zone 7 is dependent on the XMP/MC device input signal and the MP/MC mode bit (bit 8 of XINTCNF2 register). Zones 0, 1, 2, and 6 are always enabled.

- D. XCLKOUT is also pinned out on the devices without the rest of the XINTF.

10 External Interface (XINTF)

# 1.1 Accessing XINTF Zones

As shown in Figure 1, an XINTF zone is a region in the 28x memory map that is directly connected to the external interface. Memory or peripheral registers within each of these zones can be accessed directly with the 28x CPU or Code Composer Studio.

Each XINTF zone can be individually configured with unique read and write access timing and each has an associated zone chip-select signal. This chip-select signal is pulled low so that an access to that zone is currently taking place.

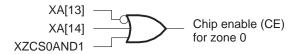

On the 2812 devices, some zone chip-select signals are shared between zones. Zone 0 and Zone 1 share  $\overline{XZCS0AND1}$  and Zone 6 and Zone 7 share  $\overline{XZCS6AND7}$ .

The external address bus, XA, on the 281x is 19 bits wide and is shared by all of the zones. What external addresses are generated depends on which zones are being accessed, as follow:

Zone 2 and Zone 6

Zone 2 and Zone 6 share identical external addresses. The external address bus is 0x00000 when the CPU accesses the first location in either Zone 2 or Zone 6. Likewise, XA is 0x7FFFF when the CPU accesses the last location of Zone 2 or Zone 6. The only difference between accesses to these two zones is which zone chip-select signal goes low:  $\overline{XZCS2}$  or  $\overline{XZCS2AND7}$ .

Since Zone 2 and Zone 6 use distinct chip-select signals, these two zones can be easily used to access memories with different timing requirements. In this case, you can use just the chip-select signal to distinguish between an access to Zone 2 and Zone 6 and additional address decoding is not required.

Zone 0 and Zone 1

Zone 0 and Zone 1 share the same chip-select signal, but use distinct external addresses. Zone 0 uses XA addresses 0x2000h - 0x3FFF and Zone 1 uses XA addresses of 0x4000 - 0x5FFF. In this case, additional logic can be used, if required, to distinguish between an access to Zone 0 and one to Zone 1. XA[13] is high for all Zone 0 accesses and low for all Zone 1 accesses. Likewise, XA[14] is low for all Zone 0 accesses and high for all Zone 1 accesses. Using this information, the logic in Figure 2 can be used to generate separate chip enable signals for memory or peripherals attached to Zone 0 and Zone 1. Figure 2. Zone 0/Zone 1 Chip-Enable Logic

Zone 0 chip enable logic

Zone 1 chip enable logic

Accesses to Zone 1 are also affected by an additional feature called the write-followed-by-read pipeline protection. This feature, which is detailed in section 1.2, makes Zone 1 especially well suited for attaching external peripheral devices instead of external memory.

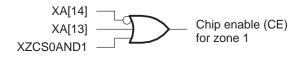

Zone 7

Zone 7 is a unique zone. This XINTF zone is only memory mapped at 0x3FC000 when the XMP/MC input signal is pulled high at reset. Software can enable or disable the mapping of this zone after reset by modifying the MP/MC mode bit in the XINTCNF2 register. When Zone 7 is not mapped, the internal boot ROM is mapped in its place. Zone 7 is the only XINTF zone that is dependent on MP/MC. Zones 0, 1, 2, and 6 are always memory mapped.

Zone 7 is typically used to boot from external memory where a customer has created their own custom boot routines and stored them in the memory attached to Zone 7. After booting, the software may enable the internal boot ROM in order to access the math tables included in the ROM. With the boot ROM mapped in place of Zone 7, the contents of the memory attached to Zone 7 can still be accessed from within Zone 6. This is because the Zone 6 and Zone 7 share the same chip-select signal XCZS6AND7 and accesses to Zone 7 use external address values 0x7C000 - 0x7FFFF that are also used by Zone 6. This has the effect of mirroring Zone 7 within the lower 16K portion of Zone 6 as shown in Figure 3.

## 1.2 Write-Followed-by-Read Pipeline Protection

In the 28x CPU pipeline, the read phase of an operation occurs before the write phase. Due to this ordering, a write followed by a read access can actually occur in the opposite order: read followed by write.

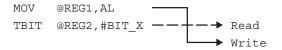

For example, the following lines of code perform a write to one location followed by a read from another. Due to the 28x CPU pipeline, the read operation will be issued before the write as shown:

On 28x devices, regions of memory where peripheral registers are common are protected from this order reversal by hardware. These regions of memory are said to be read-followed-by-write pipeline protected. On the 2812 devices, XINTF Zone 1 is by default read-followed-by-write pipeline protected. Write and read accesses to Zone 1 get executed in the same order they are written. For example, a write followed by a read is executed in the same order it was written as shown below:

The 28x CPU automatically protects writes followed by reads to the same memory location. The protection mechanism described above is for cases where the address is not the same, but within a given region of protected memory. In this case, the order of execution is preserved by the CPU

automatically inserting enough NOP cycles for the write to complete before the read occurs.

This execution ordering becomes a concern only when peripherals are mapped to the XINTF. A write to one register may update status bits in another register. In this case, the write to the first register needs to be complete before the read to the second register takes place. If the write and read operations are performed in the natural pipeline order, the wrong status may be read since the write would happen after the read. This reversal is not a concern when memory is mapped to the XINTF. XINTF Zone 1 includes the write-followed-by-read protection by default and the CPU automatically adds required cycles between writes followed by reads. Thus, Zone 1 would typically not be used to access memory but instead would be used only to access external peripherals.

If other zones other then Zone 1 are used to access peripherals that require the order write-followed-by-read instructions to be preserved, the following solutions can be used:

- Add up to 3 NOP assembly instructions between a write and read instructions. Fewer then 3 can be used if the code is analyzed and it is found that the pipeline stalls for other reasons.

- Move other instructions before the read to make sure that the write and read are at least three CPU cycles apart.

- Use the -mv compiler option to automatically insert NOP assembly instructions between write and read accesses. This option should be used with caution because this out-of-order execution is a concern only when accessing peripherals mapped to XINTF and not normal memory accesses.

# 2 XINTF Configuration Overview

The following gives an overview of the various XINTF parameters that can be configured to fit particular system requirements. The exact configuration used depends on the operating frequency of the 28x device, switching characteristics of the XINTF, and the timing requirements of the external devices to which it is being interfaced. Detailed information on each of these parameters is given in the following sections.

Because a change to many of the XINTF configuration parameters will cause a change to the access timing, code that configures these parameters should not execute from the XINTF itself.

# 2.1 Procedure to Change the XINTF Configuration and Timing Registers

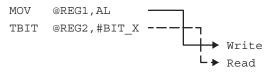

During an XINTF configuration or timing change, no accesses to the XINTF can be in progress. This includes instructions still in the CPU pipeline, write accesses in the XINTF write buffer, data reads or writes, and instruction pre-fetch operations. To be sure that no access takes place during the configuration change, you should follow the procedure shown in Figure 4 for any code that modifies the XTIMING0/1/2/6/7, XBANK, or XINTCNF2 registers.

Figure 4. Access Flow Diagram

# 2.2 XINTF Clocking

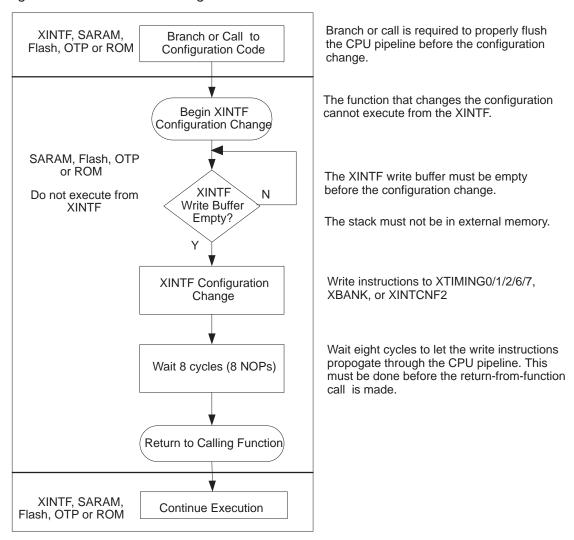

There are two clocks used by the XINTF module. Figure 5 shows the relationship between these two clocks and the CPU clock, SYSCLKOUT.

### Figure 5. Relationship Between XTIMCLK and SYSCLKOUT

Default Value after reset

All accesses to all of the XINTF zones are based on the frequency of the internal XINTF clock, XTIMCLK. When configuring the XINTF, you need to determine the ratio required for the internal XINTF clock, XTIMCLK, with respect to SYSCLKOUT. XTIMCLK can be configured to be either equal or one half of SYCLKOUT by writing to the XTIMCLK bit in the XINTFCNF2 register.

By default XTIMCLK is one-half of SYSCLKOUT.

All XINTF accesses begin on the rising edge of the external clock out, XCLKOUT. In addition, external logic may be clocked off of XCLKOUT. The frequency of XCLKOUT can be configured as a ratio of the internal XINTF clock, XTIMCLK. XCLKOUT can be configured to be either equal or one-half of XTIMCLK by writing to the CLKMODE bit in the XINTFCNF2 register.

By default, XCLKOUT is one-half of XTIMCLK, or one-fourth of the CPU clock, SYSCLKOUT.

### 2.3 Write Buffer

By default, write access buffering is disabled. In most cases, to improve performance of the XINTF, you should enable write buffering. Up to three writes to the XINTF can be buffered without stalling the CPU. The write buffer depth is configured in the XINTCNF2 register.

SPRU067C

## 2.4 XINTF Access Lead/Active/Trail Wait-State Timing Per Zone

An XINTF zone is a region of memory-mapped addresses that directly access the external interface. The timing of any read or write access to an XINTF zone can be divided into the following three portions: Lead, Active, and Trail. The number of XTIMCLK cycle wait states for each portion of an access can be configured for each XINTF zone in the corresponding zone XTIMING register. Timing for read accesses can be configured separately from timing for write accesses. In addition, to facilitate connections to slow external devices the X2TIMING bit can be used to double the specified lead/active and trail wait states for a particular zone.

During the lead portion, the chip-select signal for the zone being accessed is taken low and the address is placed on the address bus (XA). The total lead period, in XTIMCLK cycles can be configured in the zone's XTIMING register. By default, the lead period is set to the maximum six XTIMCLK cycles for both read and write accesses.

During the active period, the access to the external device is made. For a read access, the read strobe (XRD) is brought low and data is latched into the DSP. For a write access, the write enable (XWE) strobe is brought low and data is placed on the data bus (XD). If the zone is configured to sample the XREADY signal, the external device can control the XREADY signal to further extend the active period beyond the programmed wait states.

The total active period for any access that does not sample XREADY is 1 XTIMCLK cycle plus the number wait states specified in the corresponding XTIMING register. By default, the active wait states are set to the 14 XTIMCLK cycles for both read and write accesses.

The trail period serves as a hold time in which the chip-select signal remains low but the read and write strobes are brought back high. The total trail period, in XTIMCLK cycles can be configured in the zone's XTIMING register. By default the trail period is set to the maximum six XTIMCLK cycles for both read and write accesses.

Based on system requirements, the lead, active and trail wait state values can be configured to best fit the devices connected to a particular XINTF zone. The following should be considered when selecting the timing parameters:

- Minimum wait state requirements as described in section 3

- The timing characteristics of the XINTF, as described in the device data sheet

- The timing requirements of the external device

- Any additional delays between the 28x device and the external device

# 2.5 XREADY Sampling For Each Zone

By sampling XREADY, the external device can extend the active portion of the access. All of the XINTF zones on a device share the same XREADY input signal but each XINTF zone can individually be configured to either sample or ignore the XREADY signal. In addition, the sampling can be specified as synchronous or asynchronous for each zone.

□ Synchronous sampling

If XREADY is sampled synchronously, then the XREADY signal must meet set-up and hold timing relative to one XTIMCLK edge before the end of the active period. That is, XREADY will be sampled one XTIMCLK cycle before the total lead + active cycles specified for the access

Asynchronous sampling

If XREADY is sampled asynchronously, then the XREADY signal must meet set-up and hold timing relative to three XTIMCLK cycles before the end of the active period. That is, XREADY will be sampled three XTIMCLK cycles before the total lead + active cycles specified for the access.

In both the synchronous and asynchronous case if the XREADY sample is found to be low, the active portion of the cycle is extended by one XTIMCLK cycle and XREADY is sampled again during the next XTIMCLK cycle. This pattern continues until XREADY is sampled high at which time the access will complete normally.

If a zone is configured to sample XREADY, then it is done so for both read and write accesses to that zone. By default each XINTF zone is configured to sample XREADY in the asynchronous mode. When using the XREADY signal, you should consider:

- Minimum XINTF wait state requirements as described in section 3. The minimum requirements are different when sampling XREADY in the synchronous mode vs the asynchronous mode, depending on the following:

- The timing characteristics of the XINTF, as described in the device data sheet

- The timing requirements of the external device

- Any additional delays between the 28x device and the external device

### 2.6 Bank Switching

When jumping from one XINTF zone to another XINTF zone, a slow device may require extra cycles in order to release the bus in time for another device

SPRU067C

to gain access. Bank switching allows you to specify a particular zone for which extra cycles will be added for any access that crosses into or out of the specified zone. The zone and number of cycles is configured in the XBANK register.

# 2.7 Effects of the XMP/MC Signal on the XINTF

At reset the value of the XMP/MC pin is sampled and latched into the XINTF configuration register XINTFCNF2. The state of this pin at reset determines whether the boot ROM or XINTF zone 7 is enabled.

If, at reset,  $XMP/\overline{MC} = 1$  (microprocessor mode) then zone 7 is enabled and the reset vector is fetched from external memory. In this case you must be certain that the reset vector points to a valid memory location for code execution.

If, at reset,  $XMP/\overline{MC} = 0$  (microcomputer mode) then the boot ROM is enabled and XINTF zone 7 is disabled. In this case, the reset vector is fetched from the internal boot ROM and XINTF Zone 7 cannot be accessed.

After reset, the MP/MC mode can be changed by writing to the status bit in the XINTFCNF2 register. In this manner, a system can boot through the boot ROM and later software can set MP/MC to 1 to access zone 7.

# 3 Configuring Lead, Active, and Trail Wait States

XINTF signal timing can be tuned to match specific external device requirements such as setup and hold times for both read and write accesses. The timing parameters can be configured individually for each XINTF zone in the XTIMING registers. Each zone can also be configured to either ignore the XREADY signal or sample it. This allows you to maximize the efficiency of the XINTF based on the memory or peripheral being accessed.

Table 1 shows the relationship between the parameters that can be configured in the XTIMING registers and the duration of the pulse in terms of XTIMCLK cycles, tc(XTIM).

|  | Table 1. | Pulse Duration in | Terms of XTIMCLK Cycles |

|--|----------|-------------------|-------------------------|

|--|----------|-------------------|-------------------------|

|    | Description                 | Duration (ns)               |                               |  |

|----|-----------------------------|-----------------------------|-------------------------------|--|

|    |                             | X2TIMING = 0                | X2TIMING = 1                  |  |

| LR | Lead period, read access    | XRDLEAD x tc(xtim)          | (XRDLEADx2) x tc(xtim)        |  |

| AR | Active period, read access  | (XRDACTIVE+WS+1) x tc(xtim) | (XRDACTIVEx2+WS+1) x tc(xtim) |  |

| TR | Trail period, read access   | XRDTRAIL x tc(xtim)         | (XRDTRAILx2) x tc(xtim)       |  |

| LW | Lead period, write access   | XWRLEAD x tc(xtim)          | (XWRLEADx2) x tc(xtim)        |  |

| AW | Active period, write access | (XWRACTIVE+WS+1) x tc(xtim) | (XWRACTIVEx2+WS+1) x tc(xtim) |  |

| TW | Trail period, write access  | XWRTRAIL x tc(xtim)         | (XWRTRAILx2) x tc(xtim)       |  |

**Notes:** 1) tc(xtim) - Cycle time, XTIMCLK

2) WS refers to the number of wait states inserted by hardware when using XREADY. If the zone is configured to ignore XREADY (USEREADY= 0) then WS = 0.

Minimum wait-state configurations must be used for each zone's XTIMING register. These wait-state requirements are in addition to any timing requirements as specified by the device to which it is interfaced. For information on requirements for a particular device, see the data sheet for that device.

No internal device hardware is included to detect illegal settings.

If the XREADY signal is ignored (USEREADY = 0), then the following requirements must be met:

1. Lead: LR >= tc(xtim)

LW >= tc(xtim)

These requirements result in the following XTIMING register configuration restrictions:

|       | XRDLEAD | XRDACTIVE | XRDTRAIL | XWRLEAD | XWRACTIVE | XWRTRAIL | X2TIMING |

|-------|---------|-----------|----------|---------|-----------|----------|----------|

| Valid | ≥ 1     | ≥ 0       | ≥ 0      | ≥ 1     | ≥ 0       | ≥0       | 0, 1     |

Examples of valid and invalid timings when not sampling XREADY:

|         | XRDLEAD | XRDACTIVE | XRDTRAIL | XWRLEAD | XWRACTIVE | XWRTRAIL | X2TIMING |

|---------|---------|-----------|----------|---------|-----------|----------|----------|

| Invalid | 0       | 0         | 0        | 0       | 0         | 0        | 0, 1     |

| Valid   | 1       | 0         | 0        | 1       | 0         | 0        | 0, 1     |

| Valid   | ≥ 1     | $\geq 0$  | ≥0       | ≥ 1     | ≥ 0       | ≥0       | 0, 1     |

If the XREADY signal is sampled in the synchronous mode (USEREADY = 1, READYMODE = 0), then the following requirements must be met:

| 1. | Lead:   | LR | $\geq =$ | t | c (2 | ctim)    |

|----|---------|----|----------|---|------|----------|

|    |         | LW | >=       | t | C (3 | ktim)    |

| 2. | Active: |    |          |   |      | tc(xtim) |

|    |         | AW | >=       | 2 | х    | tc(xtim) |

These requirements result in the following XTIMING register configuration restrictions:

|       | XRDLEAD | XRDACTIVE | XRDTRAIL | XWRLEAD | XWRACTIVE | XWRTRAIL | X2TIMING |

|-------|---------|-----------|----------|---------|-----------|----------|----------|

| Valid | ≥ 1     | ≥ 1       | ≥0       | ≥ 1     | ≥1        | ≥0       | 0, 1     |

Examples of valid and invalid timings when using synchronous XREADY:

|         | XRDLEAD | XRDACTIVE | XRDTRAIL | XWRLEAD | XWRACTIVE | XWRTRAIL | X2TIMING |

|---------|---------|-----------|----------|---------|-----------|----------|----------|

| Invalid | 0       | 0         | 0        | 0       | 0         | 0        | 0, 1     |

| Invalid | 1       | 0         | 0        | 1       | 0         | 0        | 0, 1     |

| Valid   | 1       | 1         | 0        | 1       | 1         | 0        | 0, 1     |

If the XREADY signal is sampled in asynchronous mode (USEREADY = 1, READYMODE = 1), then the following requirements must be met:

| 3. | Lead:        | LR >= | tc(xtim)                           |

|----|--------------|-------|------------------------------------|

|    |              | LW >= | tc(xtim)                           |

| 4. | Active:      |       | 2 x tc(xtim)<br>2 x tc(xtim)       |

| 5. | Lead+Active: |       | >= 4 x tc(xtim)<br>>= 4 x tc(xtim) |

External Interface (XINTF)

22

These requirements result in the following three possible XTIMING register configurations:

|       | XRDLEAD | XRDACTIVE | XRDTRAIL | XWRLEAD | XWRACTIVE | XWRTRAIL | X2TIMING |

|-------|---------|-----------|----------|---------|-----------|----------|----------|

| Valid | ≥ 1     | ≥2        | 0        | ≥ 1     | ≥2        | 0        | 0, 1     |

| Valid | ≥2      | ≥ 1       | 0        | ≥2      | ≥ 1       | 0        | 0, 1     |

| Valid | ≥ 1     | ≥ 1       | 0        | ≥ 1     | ≥ 1       | 0        | 1        |

Examples of valid and invalid timings when using asynchronous XREADY:

|         | XRDLEAD | XRDACTIVE | XRDTRAIL | XWRLEAD | XWRACTIVE | XWRTRAIL | X2TIMING |

|---------|---------|-----------|----------|---------|-----------|----------|----------|

| Invalid | 0       | 0         | 0        | 0       | 0         | 0        | 0, 1     |

| Invalid | 1       | 0         | 0        | 1       | 0         | 0        | 0, 1     |

| Invalid | 1       | 1         | 0        | 1       | 1         | 0        | 0        |

| Valid   | 1       | 1         | 0        | 1       | 1         | 0        | 1        |

| Valid   | 1       | 2         | 0        | 1       | 2         | 0        | 0, 1     |

| Valid   | 2       | 1         | 0        | 2       | 1         | 0        | 0, 1     |

Table 2 and Table 3 show the relationship between Lead/Active/Trail values and the XTIMCLK/X2TIMING modes.

| Lead/Trail<br>Value | XTIMCLK<br>Mode | X2TIMING<br>Mode | SYSCLKOUT Cycles               | SYSCLKOUT Cycles |

|---------------------|-----------------|------------------|--------------------------------|------------------|

| Formula             | 0               | 0                | Lead Value * 1                 | Trail Value * 1  |

|                     | 0               | 1                | Lead Value * 2                 | Trail Value * 2  |

|                     | 1               | 0                | Lead Value * 2                 | Trail Value * 2  |

|                     | 1               | 1                | Lead Value * 4                 | Trail Value * 4  |

| 0                   | Х               | Х                | Not a valid value (do not use) | 0                |

| 1                   | 0               | 0                | 1                              | 1                |

|                     | 0               | 1                | 2                              | 2                |

|                     | 1               | 0                | 2                              | 2                |

|                     | 1               | 1                | 4                              | 4                |

| 2                   | 0               | 0                | 2                              | 2                |

|                     | 0               | 1                | 4                              | 4                |

| Table 2. | Relationship Between Lead/Trail Values and the XTIMCLK/X2TIMING Modes |

|----------|-----------------------------------------------------------------------|

|----------|-----------------------------------------------------------------------|

SPRU067C

External Interface (XINTF) 23

| Table 2. | Relationship Between Lead/Trail Values and the XTIMCLK/X2TIMING Modes |

|----------|-----------------------------------------------------------------------|

|          | (Continued)                                                           |

| Lead/Trail<br>Value | XTIMCLK<br>Mode | X2TIMING<br>Mode | SYSCLKOUT Cycles | SYSCLKOUT Cycles |

|---------------------|-----------------|------------------|------------------|------------------|

|                     | 1               | 0                | 4                | 4                |

|                     | 1               | 1                | 8                | 8                |

| 3                   | 0               | 0                | 3                | 3                |

|                     | 0               | 1                | 6                | 6                |

|                     | 1               | 0                | 6                | 6                |

|                     | 1               | 1                | 12               | 12               |

# Table 3. Relationship Between Active Values and the XTIMCLK/X2TIMING Modes

| Active Value | XTIMCLK Mode | X2TIMING Mode | Total Active SYSCLKOUT Cycles<br>(includes 1 implied active cycle) |

|--------------|--------------|---------------|--------------------------------------------------------------------|

| Formula      | 0            | 0             | Active Value * 1 + 1                                               |

|              | 0            | 1             | Active Value * 2 + 1                                               |

|              | 1            | 0             | Active Value * 2 + 2                                               |

|              | 1            | 1             | Active Value * 4 + 2                                               |

| 0            | 0            | Х             | 1 or Invalid if XREADY used (USEREADY = 1)                         |

|              | 1            | х             | 2 or Invalid if XREADY used (USEREADY = 1)                         |

| 1            | 0            | 0             | 2                                                                  |

|              | 0            | 1             | 3                                                                  |

|              | 1            | 0             | 4                                                                  |

|              | 1            | 1             | 6                                                                  |

| 2            | 0            | 0             | 3                                                                  |

|              | 0            | 1             | 5                                                                  |

|              | 1            | 0             | 6                                                                  |

|              | 1            | 1             | 10                                                                 |

| 3            | 0            | 0             | 4                                                                  |

|              | 0            | 1             | 7                                                                  |

24 External Interface (XINTF)

SPRU067C

| Active Value | XTIMCLK Mode | X2TIMING Mode | Total Active SYSCLKOUT Cycles<br>(includes 1 implied active cycle) |

|--------------|--------------|---------------|--------------------------------------------------------------------|

|              | 1            | 0             | 8                                                                  |

|              | 1            | 1             | 14                                                                 |

| 4            | 0            | 0             | 5                                                                  |

|              | 0            | 1             | 9                                                                  |

|              | 1            | 0             | 10                                                                 |

|              | 1            | 1             | 18                                                                 |

| 5            | 0            | 0             | 6                                                                  |

|              | 0            | 1             | 11                                                                 |

|              | 1            | 0             | 12                                                                 |

|              | 1            | 1             | 22                                                                 |

| 6            | 0            | 0             | 7                                                                  |

|              | 0            | 1             | 13                                                                 |

|              | 1            | 0             | 14                                                                 |

|              | 1            | 1             | 26                                                                 |

| 7            | 0            | 0             | 8                                                                  |

|              | 0            | 1             | 15                                                                 |

|              | 1            | 0             | 16                                                                 |

|              | 1            | 1             | 30                                                                 |

Table 3. Relationship Between Active Values and the XTIMCLK/X2TIMING Modes(Continued)

### 4 XINTF Registers

Table 4 shows the XINTF configuration registers. Modification of these registers will affect the timing of XINTF accesses and should be performed only by code running outside of the XINTF.

Name Address Size (x16) Description 2 **XTIMING0** 0x0000-0B20 XINTF Timing Register, Zone 0 XTIMING1 0x0000-0B22 2 XINTF Timing Register, Zone 1 2 XTIMING2<sup>†</sup> XINTF Timing Register, Zone 2 0x0000-0B24 2 XTIMING6 0x0000-0B2C XINTF Timing Register, Zone 6 2 XTIMING7 0x0000-0B2E XINTF Timing Register, Zone 7 2 XINTCNF2<sup>‡</sup> 0x0000-0B34 **XINTF Configuration Register** XBANK 0x0000-0B38 1 XINTF Bank Control Register **XREVISION** 1 0x0000-0B3A **XINTF Revision Register**

Table 4. XINTF Configuration and Control Register Mapping

<sup>†</sup> XTIMING3, XTIMING4, XTIMING5 are reserved for future expansion and are not currently used.

<sup>‡</sup>XINTCNF1 is reserved and not currently used.

The individual timing parameters can be programmed into the XTIMING registers described in Figure 6.

### 4.1 XINTF Timing Registers

Each XINTF zone has one timing register. Changes to this register will affect the timing of that particular zone. Changes to a zone's timing register should be made only by code executing outside of that zone.

#### Note: Timing Constraints

- Minimum wait-state requirements for different modes are shown in Section 2.

- ☐ The external device to which the 28x is interfaced may have additional timing constraints. See the vendor documentation for details.

- No logic is included to detect illegal settings.

| 31        |          |      |          |          |           |     | 24       |

|-----------|----------|------|----------|----------|-----------|-----|----------|

|           |          |      | Rese     | erved    |           |     |          |

|           |          |      | R        | -0       |           |     |          |

| 23        | 22       | 21   |          |          | 18        | 17  | 16       |

| Reserved  | X2TIMING |      | Rese     | XS       | SIZE      |     |          |

| R-0       | R/W-1    |      | R        | R/W-1    |           |     |          |

| 15        | 14       | 13   | 13 12 11 |          |           |     | 8        |

| READYMODE | USEREADY | XRDI | EAD      |          | XRDACTIVE |     | XRDTRAIL |

| R/W-1     | R/W-1    | R/V  | V-1      |          | R/W-1     |     | R/W-1    |

| 7         | 6        | 5    | 4        |          | 2         | 1   | 0        |

| XRDTRAIL  | XWR      | LEAD |          | XWRACTIV | E         | XWF | TRAIL    |

| R/W-1     | R/V      | W-1  |          | R/W-1    |           | R/  | W-1      |

# Figure 6. XTIMING0/1/2/6/7 Register Layout

**Note:** R = Read; W = Write; -n = reset value

| Bits  | Name      | Description                                                                                                                      |                                                                                                                                  |                                                                                                |  |  |  |  |  |

|-------|-----------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 31–23 | Reserved  |                                                                                                                                  |                                                                                                                                  |                                                                                                |  |  |  |  |  |

| 22    | X2TIMING  |                                                                                                                                  | This bit specifies the scaling factor of the XRDLEAD, XRDACTIVE, XRDTRAIL, XWRLEAD, XWRACTIVE, and XWRTRAIL values for the zone. |                                                                                                |  |  |  |  |  |

|       |           | 0                                                                                                                                | The values are scaled 1:1                                                                                                        |                                                                                                |  |  |  |  |  |

|       |           | 1                                                                                                                                |                                                                                                                                  | The values are scaled 2:1 (doubled). This the default mode of operation on power up and reset. |  |  |  |  |  |

| 21–18 | Reserved  | Res                                                                                                                              | Reserved                                                                                                                         |                                                                                                |  |  |  |  |  |

| 17–16 | XSIZE     | These two bits must always be written to as 1, 1. Any other combination is reserved and will result in incorrect XINTF behavior. |                                                                                                                                  |                                                                                                |  |  |  |  |  |

|       |           | 0                                                                                                                                | 0                                                                                                                                | Reserved – results in incorrect XINTF behavior                                                 |  |  |  |  |  |

|       |           | 0                                                                                                                                | 1                                                                                                                                | Reserved – results in incorrect XINTF behavior                                                 |  |  |  |  |  |

|       |           | 1                                                                                                                                | 0                                                                                                                                | Reserved – results in incorrect XINTF behavior                                                 |  |  |  |  |  |

|       |           | 1                                                                                                                                | 1                                                                                                                                | 16-bit interface- the only valid combination                                                   |  |  |  |  |  |

| 15    | READYMODE | Sets the XREADY input sampling for the zone as synchronous or asynchronous. This bit is ignored if XREADY is not sampled (USERE) |                                                                                                                                  |                                                                                                |  |  |  |  |  |

|       |           | 0                                                                                                                                |                                                                                                                                  | XREADY input is synchronous for the zone.                                                      |  |  |  |  |  |

|       |           | 1                                                                                                                                |                                                                                                                                  | XREADY input is asynchronous for the zone.                                                     |  |  |  |  |  |

SPRU067C

External Interface (XINTF) 27

# Figure 6. XTIMING0/1/2/6/7 Register Layout (Continued)

| Bits  | Name      | Description   |                                                                                   |                                                                                                                                               |                                                                  |                                                                                                       |  |  |  |

|-------|-----------|---------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|

| 14    | USEREADY  | Dete<br>signa |                                                                                   | s if acces                                                                                                                                    | ses to the z                                                     | one will sample or ignore the XREADY input                                                            |  |  |  |

|       |           | 0             |                                                                                   | The XR<br>zone.                                                                                                                               | The XREADY signal is ignored when accesses are made to the zone. |                                                                                                       |  |  |  |

|       |           | 1             |                                                                                   | access                                                                                                                                        |                                                                  | I can further extend the active portion of an<br>bast the minimum defined by the XRDACTIVE<br>elds.   |  |  |  |

| 13–12 | XRDLEAD   |               |                                                                                   | t field that defines the read cycle lead period for the zone, in XTIMC from 1, 2, 3 (if X2TIMING bit is 0) or 2, 4, 6 (if X2TIMING bit is 1). |                                                                  |                                                                                                       |  |  |  |

|       |           | Note          | <b>Note:</b> See Section 3 for minimum constraints for different operating modes. |                                                                                                                                               |                                                                  |                                                                                                       |  |  |  |

|       |           | XRDL          | EAD                                                                               | Х2Т                                                                                                                                           | IMING                                                            | Read Lead Period                                                                                      |  |  |  |

|       |           | 0             | 0                                                                                 |                                                                                                                                               | х                                                                | Invalid                                                                                               |  |  |  |

|       |           | 0             | 1                                                                                 |                                                                                                                                               | 0<br>1                                                           | 1 XTIMCLK cycle<br>2 XTIMCLK cycles                                                                   |  |  |  |

|       |           | 1             | 0                                                                                 |                                                                                                                                               | 0<br>1                                                           | 2 XTIMCLK cycles<br>4 XTIMCLK cycles                                                                  |  |  |  |

|       |           | 1             | 1                                                                                 |                                                                                                                                               | 0<br>1                                                           | 3 XTIMCLK cycles<br>6 XTIMCLK cycles                                                                  |  |  |  |

| 11–9  | XRDACTIVE | cycle         | es, froi                                                                          |                                                                                                                                               | 3, 4, 5, 6, 7                                                    | ead cycle active wait-state period, in XTIMCLK<br>(if X2TIMING bit is 0) or 0, 2, 4, 6, 8, 10, 12, 14 |  |  |  |

|       |           | Note          | <b>s:</b> 1)                                                                      | See Sect                                                                                                                                      | tion 3 for mini                                                  | mum constraints for different operating modes.                                                        |  |  |  |

|       |           |               | 2)                                                                                |                                                                                                                                               |                                                                  | y default, 1 XTIMCLK cycle. Therefore,<br>s (1 + XRDACTIVE) XTIMCLK cycles.                           |  |  |  |

|       |           | XR            | DACT                                                                              | IVE                                                                                                                                           | X2TIMIN                                                          | <b>G</b> Read Active Period Waitstates                                                                |  |  |  |

|       |           | 0             | 0                                                                                 | 0                                                                                                                                             | 0                                                                | 0                                                                                                     |  |  |  |

|       |           | 0             | 0                                                                                 | 1                                                                                                                                             | 0<br>1                                                           | 1 XTIMCLK cycle<br>2 XTIMCLK cycles                                                                   |  |  |  |

|       |           | 0             | 1                                                                                 | 0                                                                                                                                             | 0<br>1                                                           | 2 XTIMCLK cycles<br>4 XTIMCLK cycles                                                                  |  |  |  |

|       |           | 0             | 1                                                                                 | 1                                                                                                                                             | 0<br>1                                                           | 3 XTIMCLK cycles<br>6 XTIMCLK cycles                                                                  |  |  |  |

|       |           | 1             | 0                                                                                 | 0                                                                                                                                             | 0<br>1                                                           | 4 XTIMCLK cycles<br>8 XTIMCLK cycles                                                                  |  |  |  |

|       |           | 1             | 0                                                                                 | 1                                                                                                                                             | 0<br>1                                                           | 5 XTIMCLK cycles<br>10 XTIMCLK cycles                                                                 |  |  |  |

28

# Figure 6. XTIMING0/1/2/6/7 Register Layout (Continued)

| Bits | Name      | Desc                                                                                                                                           | riptio  | on        |                         |                                                                                              |  |  |  |

|------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------|-------------------------|----------------------------------------------------------------------------------------------|--|--|--|

|      |           | XRI                                                                                                                                            | DACT    | IVE       | X2TIMING                | Read Active Period Waitstates                                                                |  |  |  |

|      |           | 1                                                                                                                                              | 1       | 0         | 0<br>1                  | 6 XTIMCLK cycles<br>12 XTIMCLK cycles                                                        |  |  |  |

|      |           | 1                                                                                                                                              | 1       | 1         | 0<br>1                  | 7 XTIMCLK cycles<br>14 XTIMCLK cycles                                                        |  |  |  |

| 8–7  | XRDTRAIL  | cle trail period, in XTIMCLK cycles, from 0,<br>4, 6 (if X2TIMING bit is 1).                                                                   |         |           |                         |                                                                                              |  |  |  |

|      |           | XR                                                                                                                                             | DTR/    | AIL       | X2TIMING                | Read Trail Period                                                                            |  |  |  |

|      |           | 0                                                                                                                                              | 0       |           | 0                       | 0                                                                                            |  |  |  |

|      |           | 0                                                                                                                                              | 1       |           | 0<br>1                  | 1 XTIMCLK cycle<br>2 XTIMCLK cycles                                                          |  |  |  |

|      |           | 1                                                                                                                                              | 0       |           | 0<br>1                  | 2 XTIMCLK cycles<br>4 XTIMCLK cycles                                                         |  |  |  |

|      |           | 1                                                                                                                                              | 1       |           | 0<br>1                  | 3 XTIMCLK cycles<br>6 XTIMCLK cycles                                                         |  |  |  |

| 6–5  | XWRLEAD   |                                                                                                                                                |         |           |                         | cle lead period, in XTIMCLK cycles, from<br>6 (if X2TIMING bit is 1).                        |  |  |  |

|      |           | Note:                                                                                                                                          | See     | e Sectior | n 3 for minimum requi   | irements for different operating modes.                                                      |  |  |  |

|      |           | XM                                                                                                                                             | RLE     | AD        | X2TIMING                | Write Lead Period                                                                            |  |  |  |

|      |           | 0                                                                                                                                              | 0       |           | х                       | Invalid                                                                                      |  |  |  |

|      |           | 0                                                                                                                                              | 1       |           | 0<br>1                  | 1 XTIMCLK cycle<br>2 XTIMCLK cycles                                                          |  |  |  |

|      |           | 1                                                                                                                                              | 0       |           | 0<br>1                  | 2 XTIMCLK cycles<br>4 XTIMCLK cycles                                                         |  |  |  |

|      |           | 1                                                                                                                                              | 1       |           | 0<br>1                  | 3 XTIMCLK cycles<br>6 XTIMCLK cycles                                                         |  |  |  |

| 4–2  | XWRACTIVE | cycle                                                                                                                                          | s, fror |           | 2, 3, 4, 5, 6, 7 (if X2 | cycle active wait-state period, in XTIMCLK<br>2TIMING bit is 0) or 0, 2, 4, 6, 8, 10, 12, 14 |  |  |  |

|      |           | Notes                                                                                                                                          |         |           | ection 3 for minimum    |                                                                                              |  |  |  |

|      |           | <ol> <li>The active period is by default 1 XTIMCLK cycle. Therefore,<br/>the total active period is (1 + XWRACTIVE) XTIMCLK cycles.</li> </ol> |         |           |                         |                                                                                              |  |  |  |

|      |           | XW                                                                                                                                             | RACT    | IVE       | X2TIMING                | Write Active Period Wait States                                                              |  |  |  |

|      |           | 0                                                                                                                                              | 0       | 0         | x                       | 0                                                                                            |  |  |  |

|      |           | 0                                                                                                                                              | 0       | 1         | 0<br>1                  | 1 XTIMCLK cycle<br>2 XTIMCLK cycles                                                          |  |  |  |

SPRU067C

External Interface (XINTF)

29

# XINTF Registers

| Bits | Name     | Desc | riptio | n |          |                                                                              |

|------|----------|------|--------|---|----------|------------------------------------------------------------------------------|

|      |          | 0    | 1      | 0 | 0<br>1   | 2 XTIMCLK cycles<br>4 XTIMCLK cycles                                         |

|      |          | 0    | 1      | 1 | 0<br>1   | 3 XTIMCLK cycles<br>6 XTIMCLK cycles                                         |

|      |          | 1    | 0      | 0 | 0<br>1   | 4 XTIMCLK cycles<br>8 XTIMCLK cycles                                         |

|      |          | 1    | 0      | 1 | 0<br>1   | 5 XTIMCLK cycles<br>10 XTIMCLK cycles                                        |

|      |          | 1    | 1      | 0 | 0<br>1   | 6 XTIMCLK cycles<br>12 XTIMCLK cycles                                        |

|      |          | 1    | 1      | 1 | 0<br>1   | 7 XTIMCLK cycles<br>14 XTIMCLK cycles                                        |

| 1–0  | XWRTRAIL |      |        |   |          | cle trail period, in XTIMCLK cycles, from 0,<br>4, 6 (if X2TIMING bit is 1). |

|      |          |      |        |   | X2TIMING | Write Trail Period                                                           |

|      |          | 0    | 0      |   | х        | 0                                                                            |

|      |          | 0    | 1      |   | 0<br>1   | 1 XTIMCLK cycle<br>2 XTIMCLK cycles                                          |

|      |          | 1    | 0      |   | 0<br>1   | 2 XTIMCLK cycles<br>4 XTIMCLK cycles                                         |

|      |          | 1    | 1      |   | 0<br>1   | 3 XTIMCLK cycles<br>6 XTIMCLK cycles                                         |

# Figure 6. XTIMING0/1/2/6/7 Register Layout (Continued)

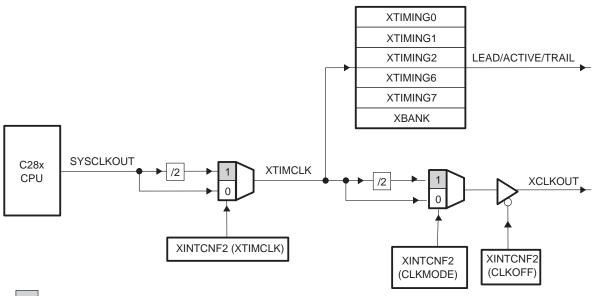

# 4.2 XINTF Configuration Register

# Figure 7. XINTCNF2 Register

| 31 |            |       |          |        |         | 19 | 18       | 16            |

|----|------------|-------|----------|--------|---------|----|----------|---------------|

|    |            |       |          |        |         |    | Х        | TIMCLK        |

|    |            |       |          |        |         |    |          | R/W-1         |

|    |            |       |          |        |         |    |          |               |

| 15 |            |       | 12       | 11     | 10      | ę  | 9        | 8             |

|    | Rese       | erved |          | HOLDAS | HOLDS   | HC | DLD      | MP/MC<br>Mode |

|    | R·         |       | R-x      | R-y    | R       | -0 | R/W-z    |               |

|    |            |       |          |        |         |    |          |               |

| 7  | 6          | 5     | 4        | 3      | 2       |    | 1        | 0             |

| V  | WLEVEL Res |       | Reserved | CLKOFF | CLKMODE | W  | rite But | ffer Depth    |

|    | R-0 R      |       | R-1      | R/W-0  | R/W-1   |    | R/\      | N-0           |

**Legend:** R = Read; W = Write; -n = reset value; x = XHOLDA output; y = XHOLD input; z = XMP/MC input

| Bits  | Name     | Des                   | criptic            | on                            |                                                                                                                                                                                                                      |

|-------|----------|-----------------------|--------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–19 | Reserved |                       |                    |                               |                                                                                                                                                                                                                      |

| 18–16 | XTIMCLK  | swito<br>This<br>Char | ching o<br>setting | operati<br>g affec<br>ο the λ | the fundamental clock for the timing of lead, active and trail<br>ons as defined by the XTIMING and XBANK registers:<br>ts all of the XINTF zones.<br>(TIMCLK ratio should be made only by code executing outside of |

|       |          | 0                     | 0                  | 0                             | XTIMCLK = SYSCLKOUT/1                                                                                                                                                                                                |

|       |          | 0                     | 0                  | 1                             | XTIMCLK = SYSCLKOUT/2                                                                                                                                                                                                |

|       |          | 0                     | 1                  | 0                             | Reserved                                                                                                                                                                                                             |

|       |          | 0                     | 1                  | 1                             | Reserved                                                                                                                                                                                                             |

|       |          | 1                     | 0                  | 0                             | Reserved                                                                                                                                                                                                             |

|       |          | 1                     | 0                  | 1                             | Reserved                                                                                                                                                                                                             |

|       |          | 1                     | 1                  | 0                             | Reserved                                                                                                                                                                                                             |

|       |          | 1                     | 1                  | 1                             | Reserved                                                                                                                                                                                                             |

| 15–12 | Reserved | Rese                  | erved              |                               |                                                                                                                                                                                                                      |

# XINTF Registers

# Figure 7. XINTCNF2 Register (Continued)

| Bits | Name          | Description                                                                                                                                                                                                                                                                                                                                                                    |

|------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11   | HOLDAS        | This bit reflects the current state of the $\overline{XHOLDA}$ output signal. It can be read by the user to determine if the external interface is currently granting access to an external device.                                                                                                                                                                            |

|      |               | 0 XHOLDA output signal is low.                                                                                                                                                                                                                                                                                                                                                 |

|      |               | 1 XHOLDA output signal is high.                                                                                                                                                                                                                                                                                                                                                |

| 10   | HOLDS         | This bit reflects the current state of the $\overline{XHOLD}$ input signal. It can be read by the user to determine if an external device is requesting access to the external bus.                                                                                                                                                                                            |

|      |               | 0 XHOLD input signal is low.                                                                                                                                                                                                                                                                                                                                                   |

|      |               | 1 XHOLD input signal is high.                                                                                                                                                                                                                                                                                                                                                  |

| 9    | HOLD          | This bit <u>grants a r</u> equest to an external device that drives the XHOLD input signal and the XHOLDA output signal.                                                                                                                                                                                                                                                       |

|      |               | 0 <u>Automatically grants a request to an external device that is driving both the XHOLD input signal and the XHOLDA output signal low.</u>                                                                                                                                                                                                                                    |

|      |               | 1 Does not grant a request to an external device that drives the XHOLD input signal low while the XHOLDA output signal stays high.                                                                                                                                                                                                                                             |

|      |               | If this bit is set while $\overline{XHOLD}$ and $\overline{XHOLDA}$ are both low (external bus accesses granted) then the $\overline{XHOLDA}$ signal is forced high (at the end of the current cycle) and the external interface is taken out of high-impedance mode.                                                                                                          |