SLUSCE2D April 2016 – January 2019

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- DBV|6

Thermal pad, mechanical data (Package|Pins)

Orderable Information

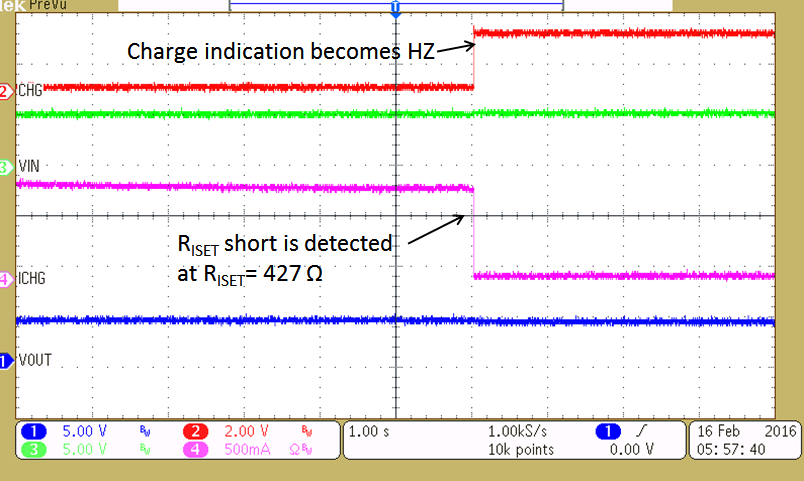

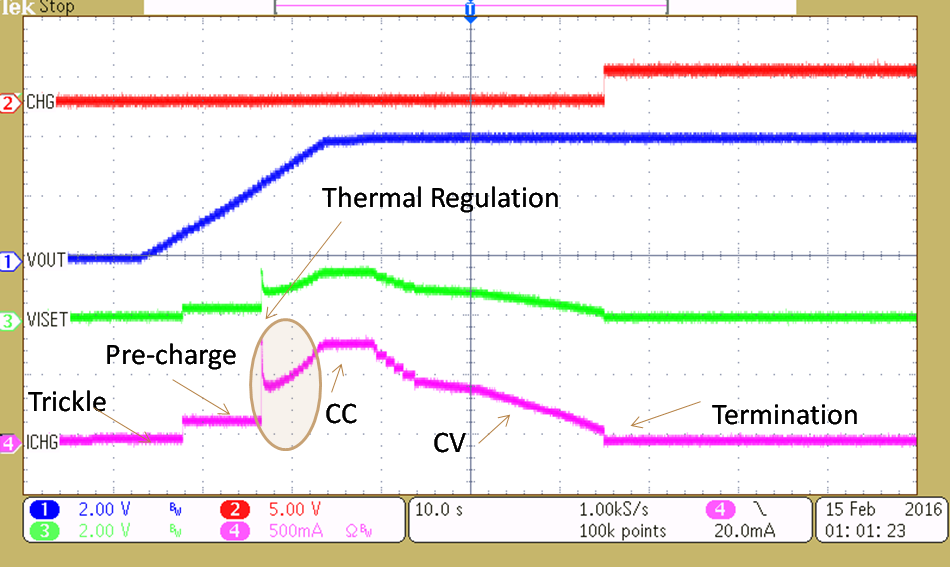

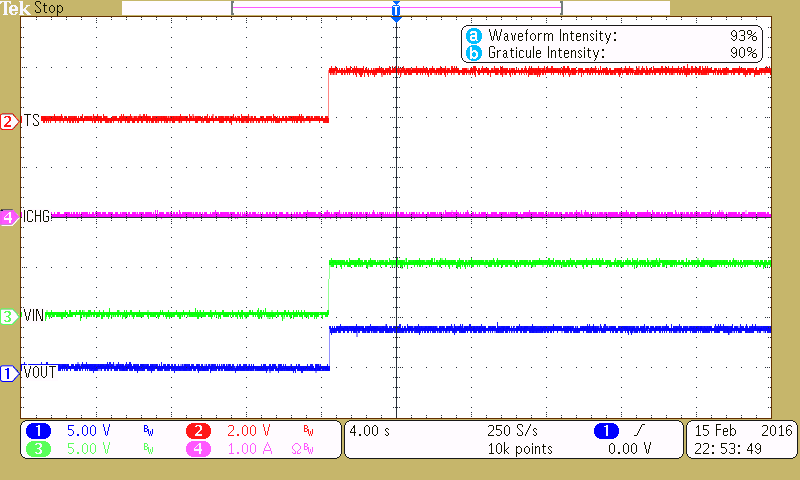

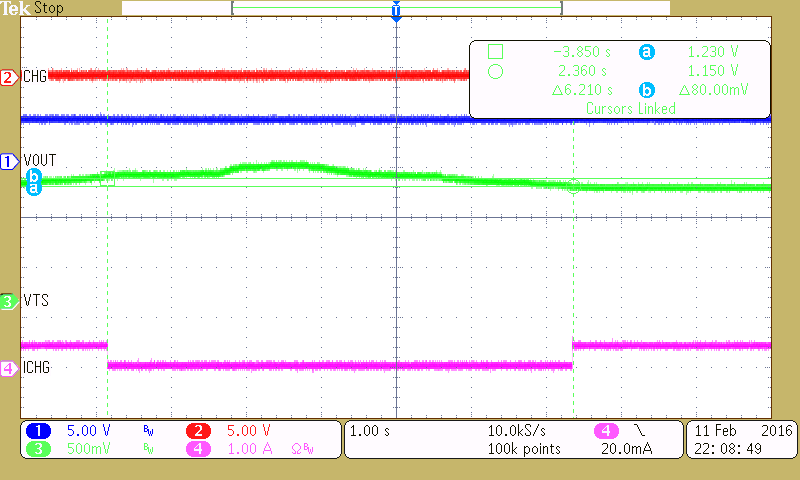

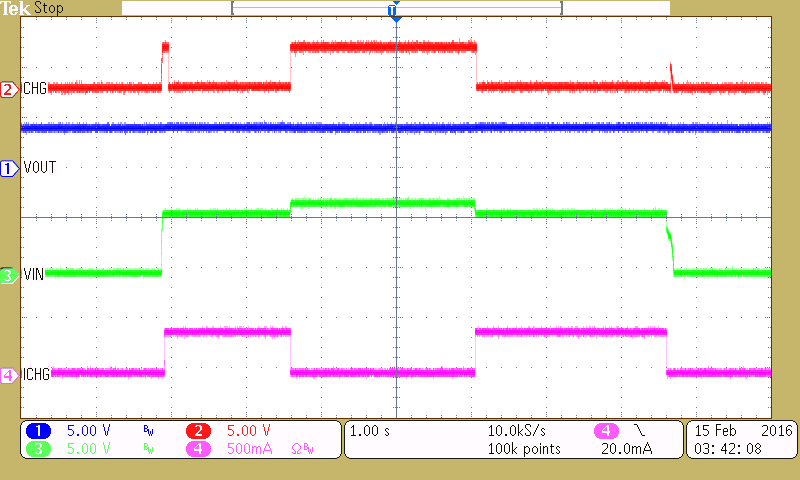

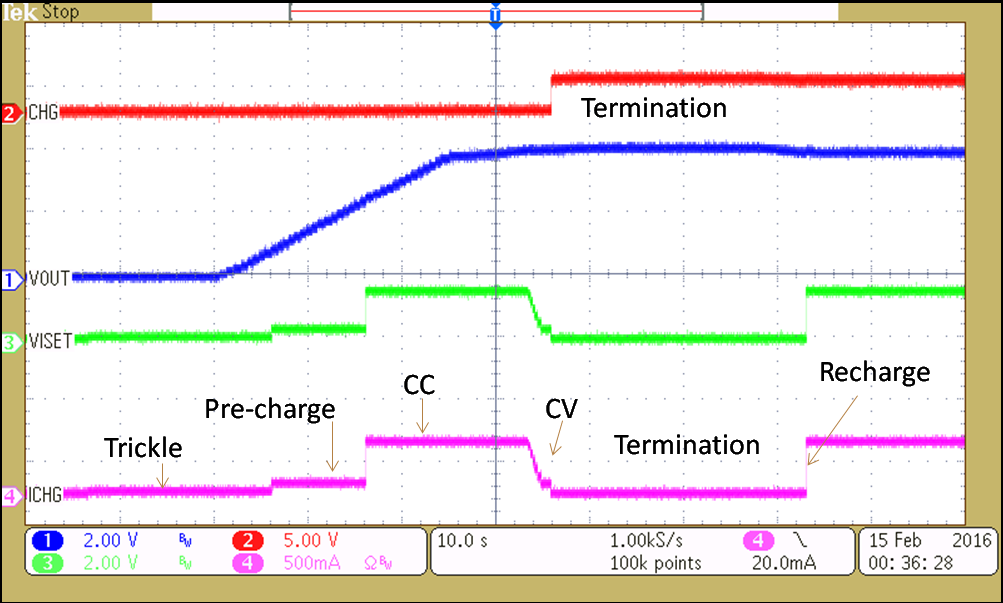

9.2.3 Application Curves

SETUP: bq21040 typical applications schematic; VIN = 5V, VBAT = 3.6V (unless otherwise indicated)

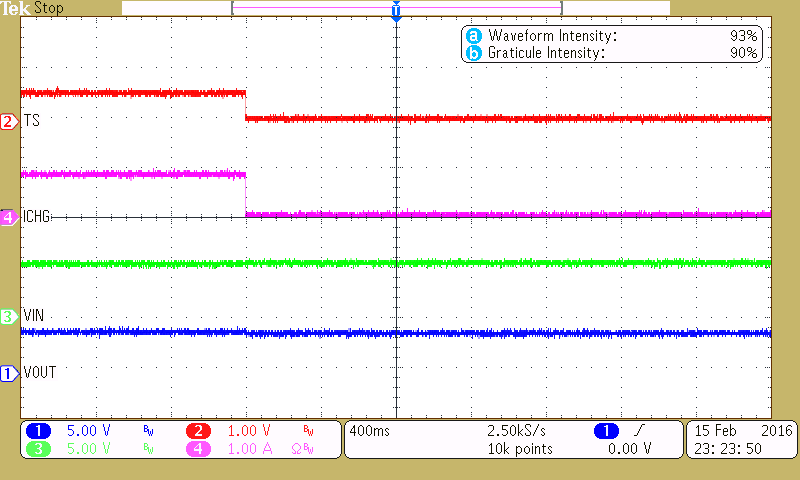

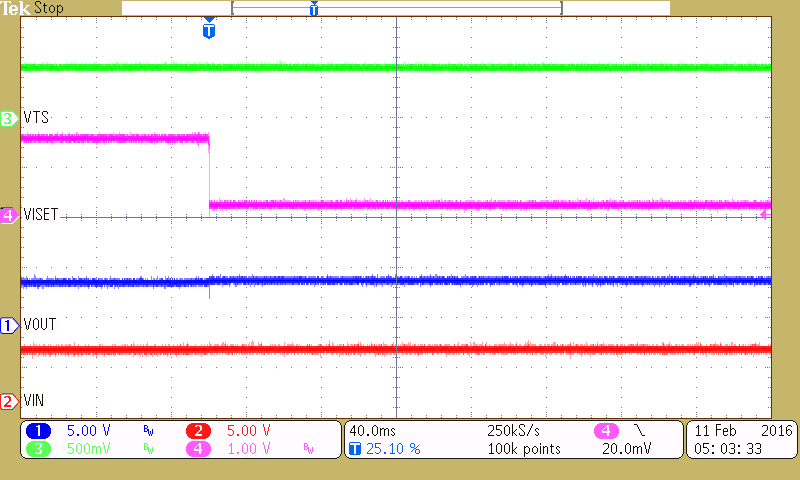

| 10-kΩ resistor from TS to GND. 10 kΩ is shorted to disable the IC | ||

.

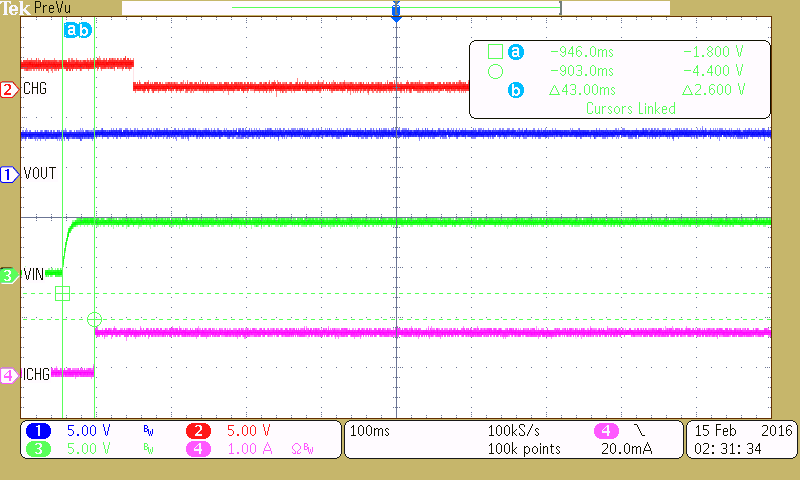

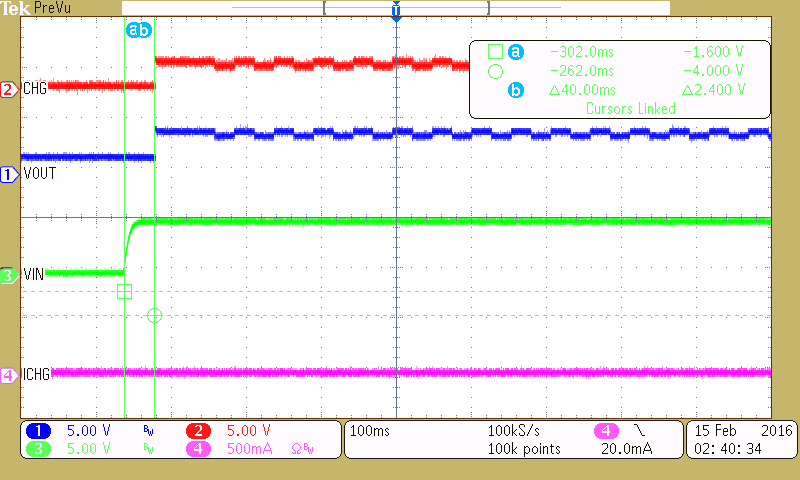

Figure 17. TS Enable and Disable

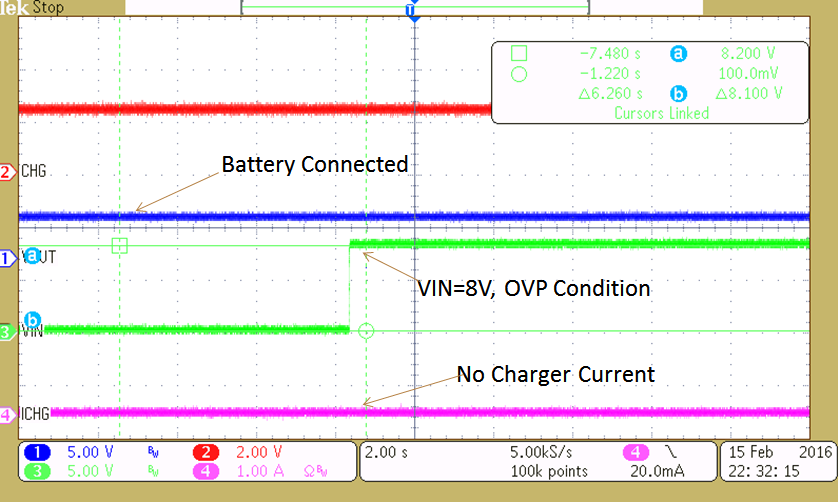

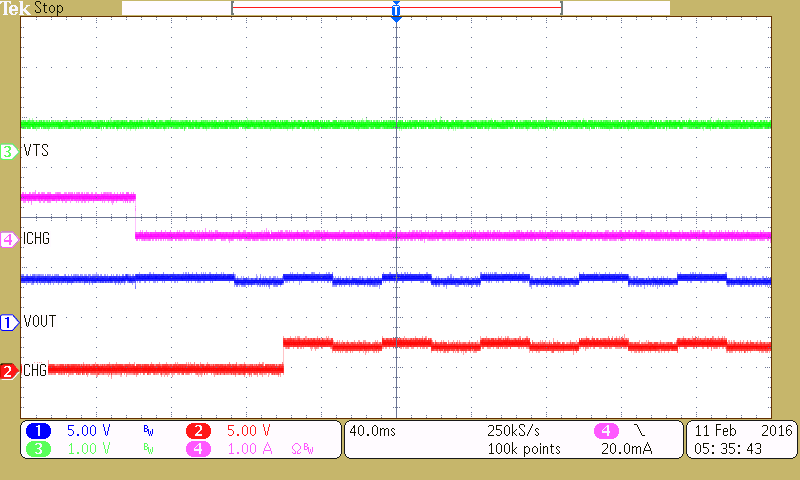

| Continuous battery detection when not in TTDM | ||

| CH4: IOUT (1A/Div) |

| CH4: IOUT (0.2A/Div) | ||

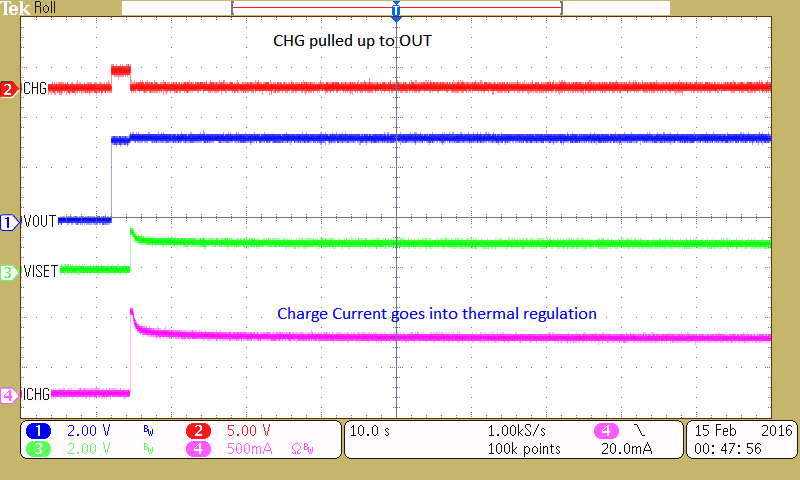

| The IC temperature rises to 125°C and enters thermal regulation. Charge current is reduced to regulate the IC at 125°C. VIN is reduced, the IC temperature drops, the charge current returns to the programmed value |

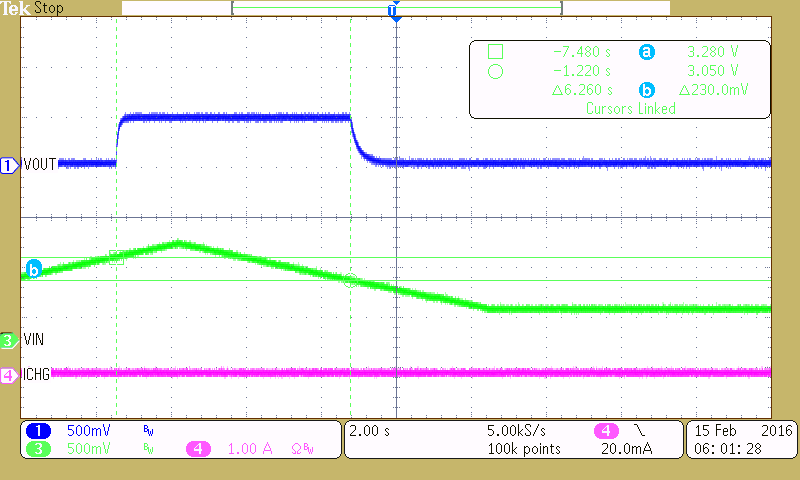

Operation – VIN 0 V → 6 V → 7 V → 6 V→ 0 V

Fixed 10kΩ resistor, between TS and GND.

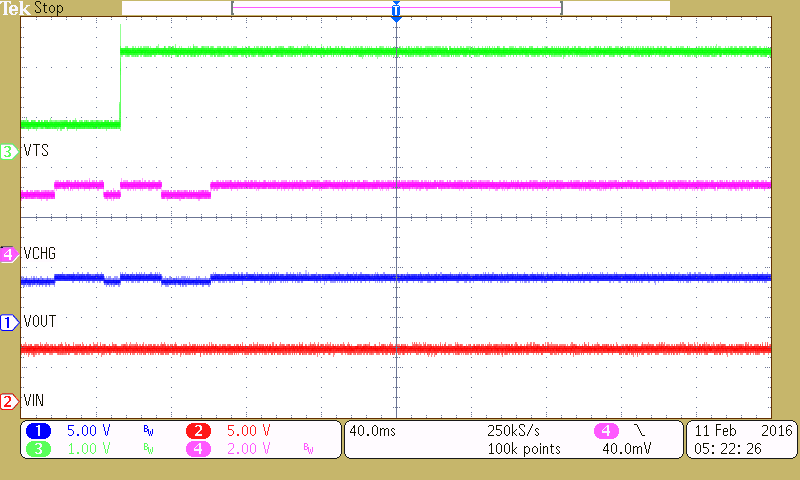

Figure 18. Power-Up Timing with No Battery and No Load – Battery Detection

TS Disconnect 1st, With 100-Ω Load

| CH4: IOUT (1A/Div) | ||

| Battery voltage swept from 0V to 4.25V to 3.9V. | ||

| CH4: IOUT (0.2A/Div) |

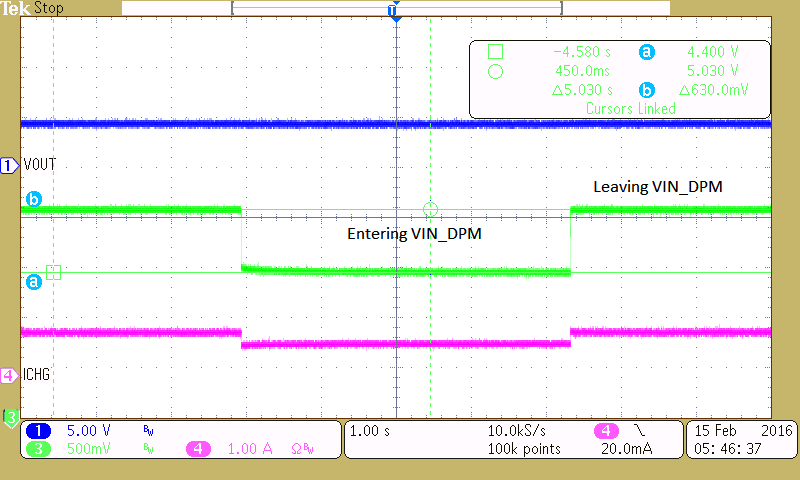

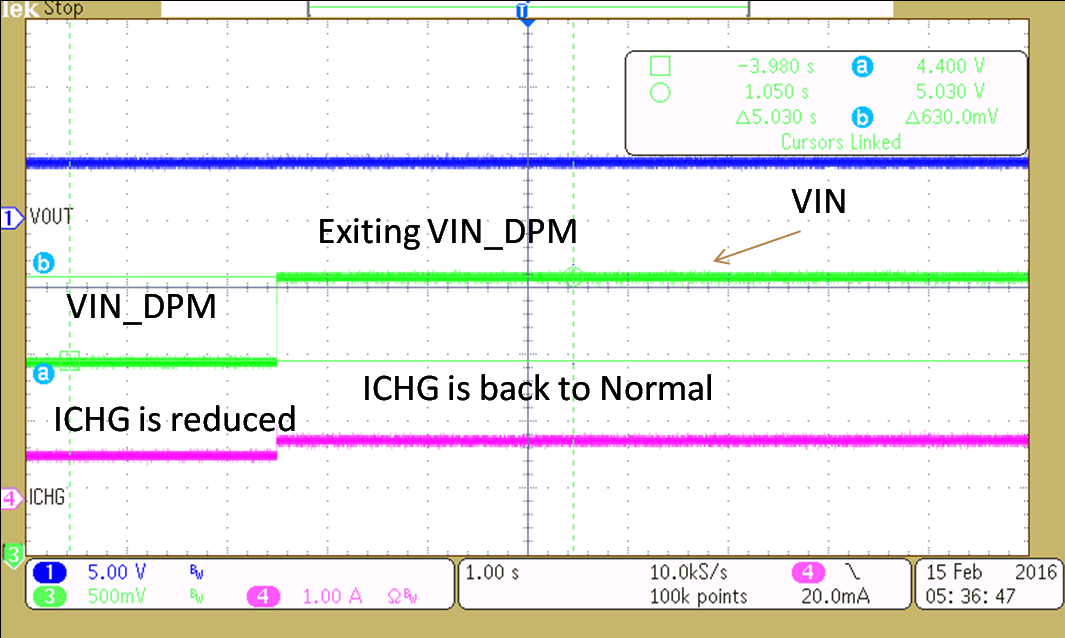

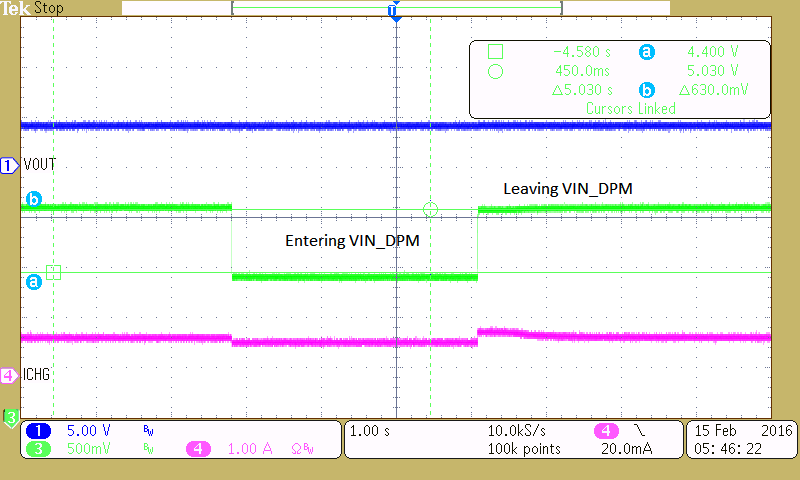

| VIN swept from 5 V to 3.9 V to 5 V | VBAT = 4 V | |