SNVSA75D November 2015 – May 2017 LP8862-Q1

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Information

- 7.5 Electrical Characteristics

- 7.6 Internal LDO Electrical Characteristics

- 7.7 Protection Electrical Characteristics

- 7.8 Power Line FET Control Electrical Characteristics

- 7.9 Current Sinks Electrical Characteristics

- 7.10 PWM Brightness Control Electrical Characteristics

- 7.11 Boost or SEPIC Converter Characteristics

- 7.12 Logic Interface Characteristics

- 7.13 Typical Characteristics

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- PWP|20

Thermal pad, mechanical data (Package|Pins)

- PWP|20

Orderable Information

8 Detailed Description

8.1 Overview

The LP8862-Q1 is a highly integrated LED driver for automotive infotainment, lighting systems, and medium-sized LCD backlight applications. It includes a DC-DC with an integrated FET, supporting both boost and SEPIC modes, an internal LDO enabling direct connection to battery without need for a pre-regulated supply, and two LED current sinks. A VDDIO/EN pin provides the supply voltage for digital IOs (PWM and SYNC inputs) and at the same time enables the device.

The switching frequency on the DC-DC regulator is set by a resistor connected to the FSET pin. The maximum output voltage of the DC-DC is set by a resistive divider connected to the FB pin. For best efficiency the output voltage is adapted automatically to the minimum necessary level needed to drive the LED strings. This is done by monitoring LED output voltage drop in real time. For EMI reduction and control two optional features are available:

- Spread spectrum, which reduces EMI noise around the switching frequency and its harmonic frequencies

- DC-DC can be synchronized to an external frequency connected to SYNC pin

The two constant current sinks OUT1 and OUT2 provide LED current up to 160 mA. Value for the current per OUT pin is set with a resistor connected to ISET pin. Unused current sink must be connected to ground. Grounded sink is disabled and excluded from adaptive output voltage control and LED string fault detection.

Brightness is controlled with the PWM input. Frequency range for the input PWM is from 100 Hz to 20 kHz. LED output PWM follows the input PWM so the output frequency is equal to the input frequency.

The LP8862-Q1 has extensive fault detection features:

- Open-string and shorted LED detections

- LED fault detection prevents system overheating in case of open or short in some of the LED strings

- VIN input overvoltage protection

- Threshold sensing from VIN pin

- VIN input undervoltage protection

- Threshold sensing from VIN pin

- VIN input overcurrent protection

- Threshold sensing across RISENSE resistor

- Thermal shutdown in case of die overtemperature

Fault condition is indicated with the FAULT output pin. Additionally, the LP8862-Q1 supports control for an optional power-line FET allowing further protection by disconnecting the device from power-line in fault condition. With the power-line FET control it possible to protect device itself, DC-DC external components and LEDs in case of shorted VOUT and too-high VIN voltage. Power-line FET control also features soft-start which reduces the peak current from the power-line during start-up.

8.2 Functional Block Diagram

8.3 Feature Description

8.3.1 Integrated DC-DC Converter

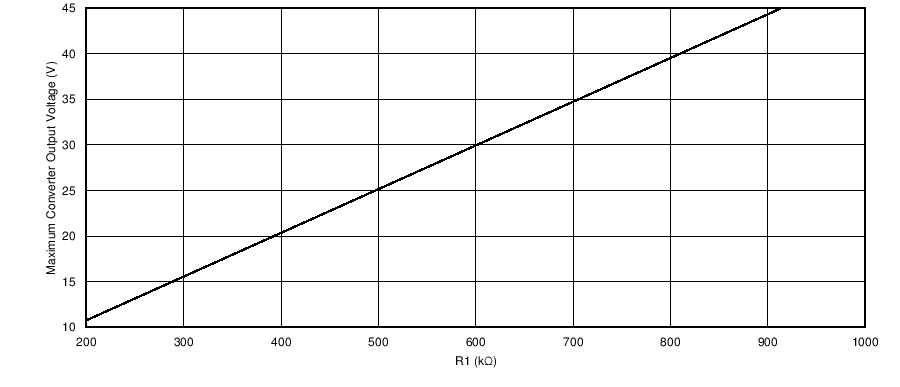

The LP8862-Q1 DC-DC converter generates supply voltage for the LEDs and can operate in boost mode or in SEPIC mode. The maximum output voltage VOUT_MAX is defined by an external resistive divider (R1, R2).

VOUT_MAX must be chosen based on the maximum voltage required for LED strings. Recommended maximum voltage is about 30% higher than maximum LED string voltage. DC-DC output voltage is adjusted automatically based on LED current sink headroom voltage. Maximum, minimum, and initial boost voltages can be calculated with Equation 1:

Figure 7. Maximum Converter Output Voltage vs R1 Resistance

Figure 7. Maximum Converter Output Voltage vs R1 Resistance

Alternatively, a T-divider can be used if resistance less than 100 kΩ is required for the external resistive divider. Refer to Using the LP8862-Q1 Evaluation Module for details.

The converter is a current mode DC-DC converter, where the inductor current is measured and controlled with the feedback. Switching frequency is adjustable between 300 kHz and 2.2 MHz with RFSET resistor as shown in Equation 2:

where

- ƒSW is switching frequency, kHz

- RFSET is frequency setting resistor, kΩ

In most cases lower frequency has higher system efficiency. DC-DC parameters are chosen automatically according to the selected switching frequency (see Table 2). In boost mode a 15-pF capacitor CFB must be placed across resistor R1 when operating in 300-kHz to 500-kHz range (see Figure 19). When operating in 1.8-MHz to 2.2-MHz range CFB = 4.7 pF.

Figure 8. Boost Block Diagram

Figure 8. Boost Block Diagram

DC-DC can be driven by an external SYNC signal between 300 kHz…2.2 MHz (Table 1). If the external synchronization input disappears, DC-DC continues operation at the frequency defined by RFSET resistor. When external frequency disappears and SYNC pin level is low, DC-DC continues operation without spread spectrum immediately. If SYNC remains high, DC-DC continues switching with spread spectrum enabled after 256 µs.

External SYNC frequency must be 1.2…1.5 times higher than the frequency defined by RFSET resistor. Minimum frequency setting with RFSET is 250 kHz to support a 300-kHz external clock.

The optional spread spectrum feature (±3% from central frequency, 1-kHz modulation frequency) reduces EMI noise at the switching frequency and its harmonic frequencies. When external synchronization is used, internal spread spectrum feature is not available.

Table 1. DC-DC Synchronization Mode

| SYNC PIN INPUT | MODE |

|---|---|

| Low | Spread spectrum disabled |

| High | Spread spectrum enabled |

| 300...2200 kHz frequency | Spread spectrum disabled, external synchronization mode |

Table 2. DC-DC Parameters(1)

| RANGE | FREQUENCY (kHz) | TYPICAL INDUCTANCE (µH) |

TYPICAL INPUT AND OUTPUT CAPACITORS (µF) |

MINIMUM SWITCH OFF TIME (ns)(2) |

BLANK TIME (ns) |

CURRENT RAMP (A/s) |

CURRENT RAMP DELAY (ns) |

|---|---|---|---|---|---|---|---|

| 1 | 300...480 | 33 | 2 × 10 (ceramic) + 33 (electrolytic) |

150 | 95 | 24 | 550 |

| 2 | 480...1150 | 15 | 10 (ceramic) + 33 (electrolytic) |

60 | 95 | 43 | 300 |

| 3 | 1150...1650 | 10 | 3 × 10 (ceramic) | 40 | 95 | 79 | 0 |

| 4 | 1650...2200 | 4.7 | 3 × 10 (ceramic) | 40 | 70 | 145 | 0 |

The converter SW pin DC current is limited to 2 A (typical). To support warm start transient condition the current limit is automatically increased to 2.5 A for a short period of 1.5 seconds when a 2-A limit is reached.

NOTE

Application condition where the 2-A limit is exceeded continuously is not allowed. In this case the current limit would be 2 A for 1.5 seconds followed by 2.5-A limit for 1.5 seconds, and this 3-second period repeats.

To keep switching voltage within safe levels there is a 48-V limit comparator in the event that FB loop is broken.

8.3.2 Internal LDO

The internal LDO regulator converts the input voltage at VIN to a 4.3-V output voltage for internal use. Connect LDO output with a minimum of 1-μF ceramic capacitor to ground as close to the LDO pin as possible. If an external voltage higher than 4.5 V is connected to LDO pin, the internal LDO is disabled, and the internal circuitry is powered from the external power supply. VIN and VSENSE_N pins must be connected to the same external voltage as LDO pin. For an application example schematic refer to the LP8861-Q1 data sheet (SNVSA50).

8.3.3 LED Current Sinks

8.3.3.1 Current Sink Configuration

The LP8862-Q1 detects LED current sink configuration during start-up. A current sink connected to ground is disabled and excluded from the adaptive DC-DC control and fault detection.

8.3.3.2 Current Setting

Maximum current for the LED current sinks is controlled with external RISET resistor. Resistor value for targeted LED string current can be calculated using Equation 3:

where

- RISET is current setting resistor, kΩ

- ILED is output current per output, mA

8.3.4 Power Line FET Control

The LP8862-Q1 has a control pin (SD) for driving the gate of an external power-line FET. Power-line FET is an optional feature. Power-line FET limits inrush current by turning on gradually when the device is enabled (VDDIO/EN = high, VIN > VGS). Inrush current is controlled by increasing sink current for the FET gradually to 230 μA. In shutdown the LP8862-Q1 turns off the power-line FET and prevents possible DC-DC and LEDs leakage. The power switch also turns off in case of any fault which causes the device to enter FAULT RECOVERY state.

8.3.5 Fault Detections

The LP8862-Q1 has fault detection for LED open and short, VIN input overvoltage (VIN_OVP), VIN undervoltage lockout (VIN_UVLO), power-line overcurrent (VIN_OCP), and thermal shutdown (TSD).

8.3.5.1 Adaptive DC-DC Voltage Control and Functionality of LED Fault Comparators

Adaptive voltage control function adjusts the DC-DC output voltage to the minimum sufficient voltage for proper LED current sink operation. The current sink with highest VF LED string is detected and DC-DC output voltage adjusted accordingly. DC-DC adaptive control voltage step size is defined by maximum voltage setting, VSTEP = (VOUT_MAX – VOUT_MIN) /256. Periodic down pressure is applied to the target voltage to achieve better system efficiency.

Every LED current sink has 3 comparators for the adaptive DC-DC control and LED-fault detections. Comparator outputs are filtered; filtering time is 1 µs.

Figure 9. Comparators for Adaptive Voltage Control and LED Fault Detection

Figure 9. Comparators for Adaptive Voltage Control and LED Fault Detection

Figure 10 illustrates different cases which cause DC-DC voltage increase, decrease, or generate faults. In normal operation, voltage at the OUT1 and OUT2 pins is between LOW_COMP and MID_COMP levels, and VOUT voltage stays constant. LOW_COMP level is the minimum for proper LED current sink operation, 1.1 × VSAT + 0.2 V (typical). MID_COMP level is 1.1 × VSAT + 1.2 V (typical) so typical headroom window is 1 V.

When voltage at OUT1 and OUT2 pin increases above MID_COMP level, DC-DC voltage adapts downwards.

When voltage at OUT1 or OUT2 pin falls below LOW_COMP threshold, DC-DC voltage adapts upwards. In the condition where VOUT reaches the maximum and there are one or more outputs still below LOW_COMP level, an open LED fault is detected.

HIGH_COMP level, 6 V typical, is the threshold for shorted LED detection. When the voltage of OUT1 or OUT2 pin increases above HIGH_COMP level and the other output is within the normal headroom window, shorted LED fault is detected.

Figure 10. DC-DC Adaptation and LED Fault Detection Algorithms

Figure 10. DC-DC Adaptation and LED Fault Detection Algorithms

8.3.5.2 Overview of the Fault/Protection Schemes

Summary of LP8862-Q1 fault detection behavior is shown in Table 3. Detected faults (excluding LED open or short) cause device to enter FAULT_RECOVERY state. In FAULT_RECOVERY the DC-DC and LED current sinks of the device are disabled, power-line FET is turned off, and the FAULT pin is pulled low. The device recovers automatically and enters normal operating mode (ACTIVE) after a recovery time of 100 ms if the fault condition has disappeared. When recovery is succesful, FAULT pin is released.

In case a LED fault is detected, device continues normal operation and only the faulty string is disabled. Fault is indicated via FAULT pin which can be released by toggling VDDIO/EN pin low for a short period of 2…20 µs. LEDs are turned off for this period but device stays in ACTIVE mode. If VDDIO/EN is low longer, device goes to STANDBY and restarts when EN goes high again.

Table 3. Fault Detections

| FAULT/ PROTECTION |

FAULT NAME | THRESHOLD | FAULT PIN | FAULT_ RECOVERY STATE |

ACTION |

|---|---|---|---|---|---|

| VIN overvoltage protection | VIN_OVP | 1. VIN > 42 V 2. VOUT > VSET_DCDC + 6..10 V. VSET_DCDC is voltage value defined by logic during adaptation |

Yes | Yes | 1. Overvoltage is monitored from the beginning of soft start. Fault is detected if the duration of over-voltage condition is 100 µs minimum. 2. Overvoltage is monitored from the beginning of normal operation (ACTIVE mode). Fault is detected if over-voltage condition duration is 560 ms minimum (tfilter). After the first fault detection filter time is reduced to 50 ms for following recovery cycles. When device recovers and has been in ACTIVE mode for 160 ms, filter time is increased back to 560 ms . |

| VIN undervoltage lockout | VIN_UVLO | Falling 3.9 V Rising 4 V |

Yes | Yes | Detects undervoltage condition at VIN pin. Sensed in all operating modes. Fault is detected if undervoltage condition duration is 100 µs minimum. |

| VIN overcurrent protection | VIN_OCP | 3 A (50-mΩ current sensor resistor) | Yes | Yes | Detects over current by measuring voltage of the RISENSE resistor connected between VIN and VSENSE_N pins. Sensed from the beginning of soft start. Fault is detected if undervoltage condition duration is 10 µs minimum. |

| Open LED fault | OPEN_LED | LOW_COMP threshold | Yes | No | Detected if the voltage of OUT1 pin or OUT2 pin is below threshold level, and DC-DC adaptive control has reached maximum voltage. Open string(s) is removed from the adaptive voltage control loop and current sink is disabled. Fault pin is released by toggling VDDIO/EN pin. If VDDIO/EN is low for a period of 2…20 µs, LEDs are turned off for this period but device stays ACTIVE. If VDDIO/EN is low longer, device goes to STANDBY and restarts when EN goes high again. |

| Shorted LED fault | SHORT_LED | Shorted string detection level 6 V | Yes | No | Detected if the voltage of OUT1 pin or OUT2 pin is above shorted string detection level, and the voltage of the other OUT pin is within headroom window. Shorted string is removed from the adaptive voltage control loop and current sink is disabled. Fault pin is released by toggling the VDDIO/EN pin. If VDDIO/EN is low for a period of 2…20 µs, LEDs are turned off for this period but device stays ACTIVE. If VDDIO/EN is low longer, device goes to STANDBY and restarts when EN goes high again. |

| Thermal protection | TSD | 165ºC Thermal Shutdown Hysteresis 20ºC |

Yes | Yes | Thermal shutdown is monitored from the beginning of soft start. Die temperature must decrease by 20°C for device to recover. |

Figure 11. VIN Overvoltage Protection (DC-DC OVP)

Figure 11. VIN Overvoltage Protection (DC-DC OVP)

Figure 12. VIN Overvoltage Protection (VIN OVP)

Figure 12. VIN Overvoltage Protection (VIN OVP)

Figure 13. VIN Undervoltage Lockout

Figure 13. VIN Undervoltage Lockout

Figure 14. Input Voltage Overcurrent Protection

Figure 14. Input Voltage Overcurrent Protection

Figure 15. LED Open Fault

Figure 15. LED Open Fault

Figure 16. LED Short Fault

Figure 16. LED Short Fault

8.4 Device Functional Modes

8.4.1 Device States

The LP8862-Q1 enters STANDBY mode when the internal LDO output rises above the power-on reset level, VLDO > VPOR. In STANDBY mode the device is able to detect the VDDIO/EN signal. When VDDIO/EN is pulled high, the device powers up. During soft start the external power-line FET is opened gradually to limit inrush current. Soft start is followed by boost (SEPIC) start, during which time VOUT is ramped to the initial value. After boost (SEPIC) start LED outputs are sensed to detect grounded outputs. Grounded outputs are disabled and excluded from the adaptive boost (SEPIC) voltage control loop.

If a fault condition is detected, the LP8862-Q1 enters FAULT_RECOVERY state. In this state power line FET is switched off and both the boost (SEPIC) and LED current sinks are disabled. Faults that cause the device to enter FAULT_RECOVERY are shown in Figure 17. When LED open or short is detected, faulty string is disabled but the device stays in ACTIVE mode.

Figure 17. State Diagram

Figure 17. State Diagram

Figure 18. Timing Diagram for Typical Start-Up and Shutdown

Figure 18. Timing Diagram for Typical Start-Up and Shutdown