SLLS992B August 2009 – March 2015 SN65LVDS93A

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Description (continued)

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

- 9 Detailed Description

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- DGG|56

Thermal pad, mechanical data (Package|Pins)

Orderable Information

1 Features

- Industrial Temperature Range –40°C to 85°C

- LVDS Display Serdes Interfaces Directly to LCD Display Panels With Integrated LVDS

- Package Options: 4.5-mm × 7-mm BGA, and 8.1-mm × 14-mm TSSOP

- 1.8 V up to 3.3-V Tolerant Data Inputs to Connect Directly to Low-Power, Low-Voltage Application and Graphic Processors

- Transfer Rate up to 135 Mpps (Mega Pixels Per Second); Pixel Clock Frequency Range 10 MHz to 135 MHz

- Suited for Display Resolutions Ranging From HVGA up to HD With Low EMI

- Operates From a Single 3.3-V Supply and 170 mW (Typical) at 75 MHz

- 28 Data Channels Plus Clock In Low-Voltage TTL to 4 Data Channels Plus Clock Out Low-Voltage Differential

- Consumes Less Than 1 mW When Disabled

- Selectable Rising or Falling Clock Edge Triggered Inputs

- ESD: 5-kV HBM

- Supports Spread Spectrum Clocking (SSC)

- Compatible With all OMAP™2x, OMAP3x, and DaVinci™ Application Processors

2 Applications

- LCD Display Panel Drivers

- UMPC and Netbook PCs

- Digital Picture Frames

3 Description

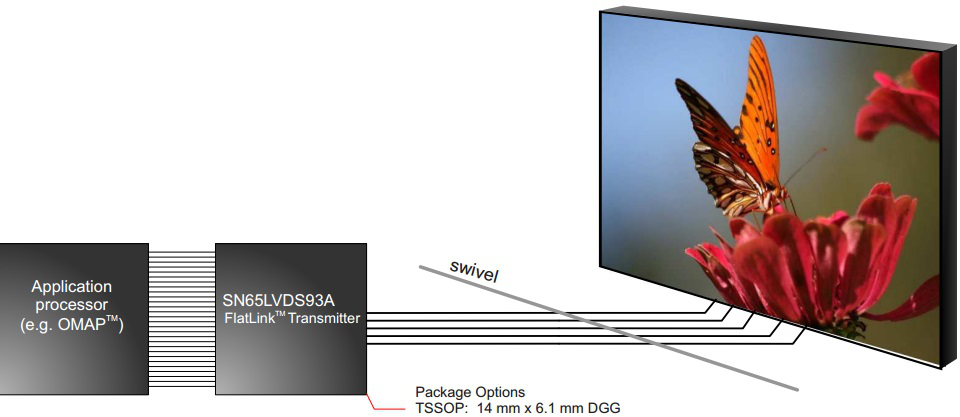

The SN65LVDS93A LVDS SerDes (serializer/deserializer) transmitter contains four 7-bit parallel load serial-out shift registers, a 7 × clock synthesizer, and five low-voltage differential signaling (LVDS) drivers in a single integrated circuit. These functions allow synchronous transmission of 28 bits of single-ended LVTTL data over five balanced-pair conductors for receipt by a compatible receiver, such as the SN65LVDS94 (SLLS928).

When transmitting, data bits D0 through D27 are each loaded into registers upon the edge of the input clock signal (CLKIN). The rising or falling edge of the clock can be selected through the clock select (CLKSEL) pin. The frequency of CLKIN is multiplied seven times and then used to serially unload the data registers in 7-bit slices. The four serial streams and a phase-locked clock (CLKOUT) are then output to LVDS output drivers. The frequency of CLKOUT is the same as the input clock, CLKIN.

Device Information(1)

| PART NUMBER | PACKAGE | BODY SIZE (NOM) |

|---|---|---|

| SN65LVDS93A | TSSOP (56) | 14.00 mm × 6.10 mm |

| BGA MICROSTAR JUNIOR (56) | 7.00 mm × 4.50 mm |

- For all available packages, see the orderable addendum at the end of the data sheet.

RGB Video System Using Discrete LVDS TX