SLUS769D July 2013 – December 2016 UCC28910 , UCC28911

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Simplified Schematic

- 5 Revision History

- 6 Device Comparison Table

- 7 Pin Configuration and Functions

- 8 Detailed Pin Description

- 9 Specifications

-

10Detailed Description

- 10.1 Overview

- 10.2 Functional Block Diagram

- 10.3 Feature Description

- 10.4 Device Functional Modes

-

11Applications and Implementation

- 11.1 Application Information

- 11.2

Typical Application

- 11.2.1

Battery Charger, 5 V, 6 W

- 11.2.1.1 Design Requirements

- 11.2.1.2

Detailed Design Procedure

- 11.2.1.2.1 Power Handling Curves

- 11.2.1.2.2 Input Stage Design and Bulk Capacitance

- 11.2.1.2.3 Transformer Turns Ratio

- 11.2.1.2.4 Output Capacitance

- 11.2.1.2.5 VDD Capacitance, CVDD

- 11.2.1.2.6 VS Resistor Divider

- 11.2.1.2.7 RVDD Resistor and Turn Ratio

- 11.2.1.2.8 Transformer Input Power

- 11.2.1.2.9 RIPK Value

- 11.2.1.2.10 Transformer Primary Inductance Value

- 11.2.1.2.11 Pre-Load

- 11.2.1.2.12 DRAIN Voltage Clamp Circuit

- 11.2.2 Application Curves

- 11.2.3 Multi-Output Converter with UCC2891x Devices

- 11.2.4 Do’s and Don'ts

- 11.2.1

Battery Charger, 5 V, 6 W

- 12Power Supply Recommendations

- 13Layout

- 14Device and Documentation Support

- 15Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- D|7

Thermal pad, mechanical data (Package|Pins)

Orderable Information

9 Specifications

9.1 Absolute Maximum Ratings

(unless otherwise noted) (1)(2)| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| VDRAIN | DRAIN voltage | Internally limited(3) | 700 | V |

| IDRAIN | Negative drain current | –100 | mA | |

| VDD | Supply voltage | Internally limited(3) | V | |

| IVDD(clp) | Maximum VDD clamp current | 10 | mA | |

| VVS | Voltage range | Internally limited(3) | 7 | V |

| VIPK | Voltage range | −0.5 | 5.0 | V |

| IVS | Peak VS pin current (current out of the pin) | −1.2 | mA | |

| IDRAIN | Pulsed drain current(4), UCC28910 | 950 | mA | |

| Pulsed drain current(4), UCC28911 | 1200 | mA | ||

| TLEAD | Lead temperature 1.6 mm (1/16 inch) from case for 10 seconds | 260 | °C | |

| TJ | Operating junction temperature range | −55 | 150 | °C |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to GND. Currents are positive into, negative out of the specified pin. These ratings apply over the operating ambient temperature ranges unless otherwise noted.

(3) Do not drive with low impedance voltage source.

(4) Maximum pulse width = 100 μs.

9.2 Storage Conditions

| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| Tstg | Storage temperature | −65 | 150 | °C |

9.3 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±2000 | V |

| Charged-device model (CDM), per JEDEC specification JESD22-C101(2) | ±500 | |||

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

9.4 Recommended Operating Conditions(1)(2)

| MIN | NOM | MAX | UNIT | |||

|---|---|---|---|---|---|---|

| VVDD | Voltage on VDD terminal during operation | VDDOFF | VVDD(clp) | V | ||

| IVS | Current out of the terminal | 1 | mA | |||

| ID(peak_max) | Maximum drain peak current | UCC28910 | 600 | mA | ||

| UCC28911 | 700 | mA | ||||

| TJ | Operating junction temperature | -40 | 125 | °C | ||

(1) Unless otherwise noted, all voltages are with respect to GND.

(2) In case of thermal shut down, if TA > 100°C, the device does not restart because of the TJ(hys) Electrical Characteristics.

9.5 Thermal Information

| THERMAL METRIC(1) | UCC28910 | UCC28911 | UNITS | |

|---|---|---|---|---|

| D | D | |||

| 7 Pin SOIC | 7 Pin SOIC | |||

| θJA | Junction-to-ambient thermal resistance | 102.2 | 102.2 | °C/W |

| θJCtop | Junction-to-case (top) thermal resistance | 39.1 | 39.1 | |

| θJB | Junction-to-board thermal resistance | 54.7 | 54.7 | |

| ψJT | Junction-to-top characterization parameter | 5.4 | 5.4 | |

| ψJB | Junction-to-board characterization parameter | 54.7 | 54.7 | |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

9.6 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted), VVDD = 15 V, TA = -40°C to 125°C, TA = TJ9.7 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|

| TIMING | |||||||

| fSW(max) | Maximum switching frequency | VVS < 3.9 V | UCC28910 | 105 | 115 | 125 | kHz |

| VVS = 3.75 V | UCC28911 | 105 | 115 | 125 | kHz | ||

| fSW(min) | Minimum switching frequency | VVS > 4.1 V | UCC28910 | 360 | 420 | 490 | Hz |

| VVS = 4.35 V | UCC28911 | 360 | 420 | 500 | Hz | ||

| tZTO | Zero crossing timeout delay | VVS < 3.9 V | UCC28910 | 1.80 | 2.10 | 2.65 | µs |

| VVS = 4.35 V | UCC28911 | 1.80 | 2.10 | 2.75 | µs | ||

| tON(min) | Minimum on time | IPK = 0.85 V | UCC28910 | 390 | ns | ||

| UCC28911 | 420 | ns | |||||

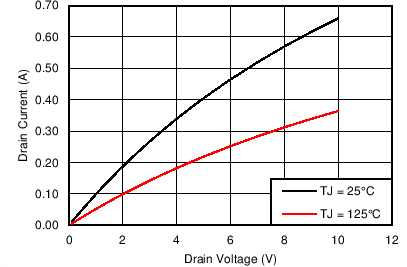

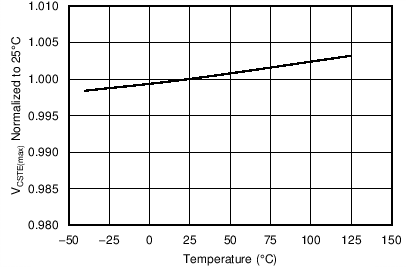

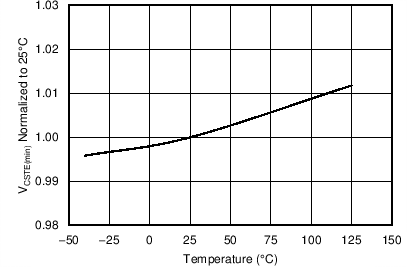

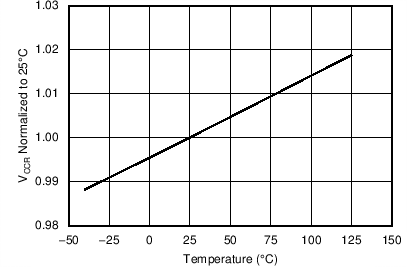

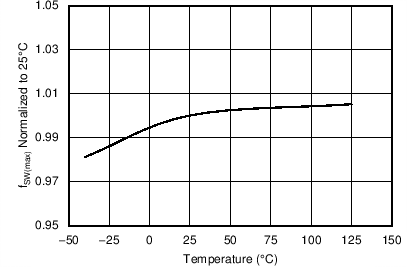

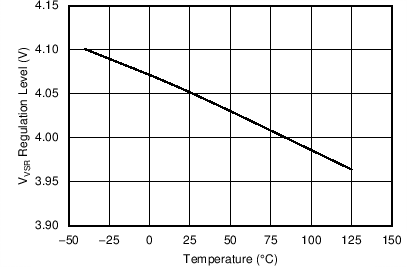

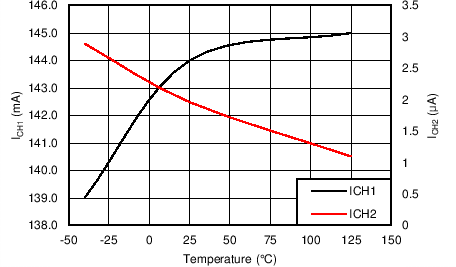

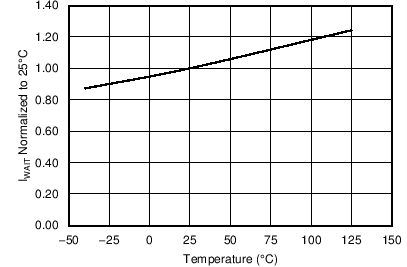

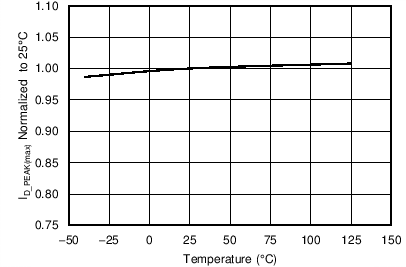

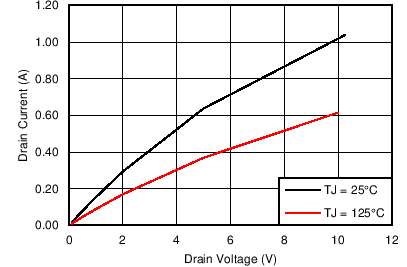

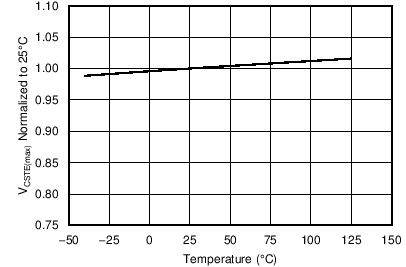

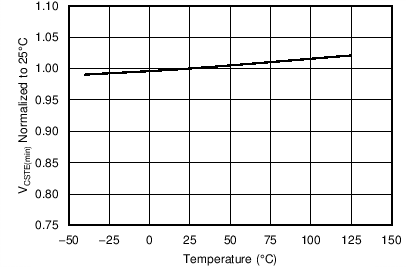

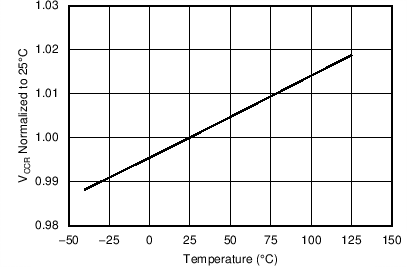

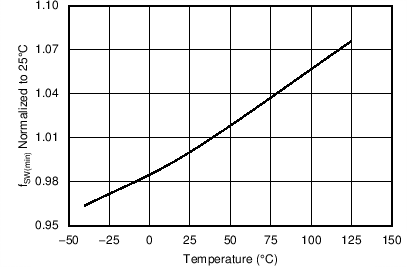

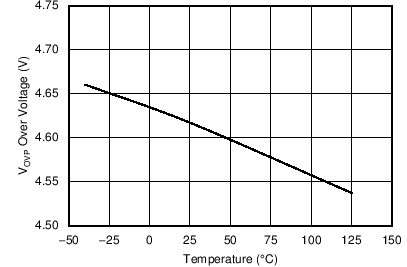

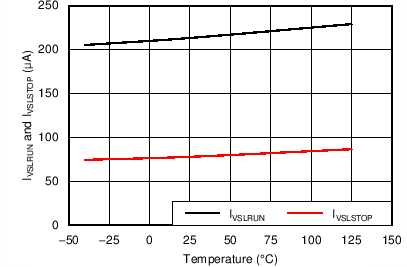

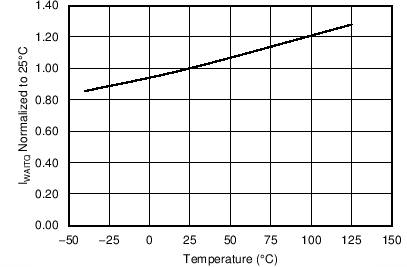

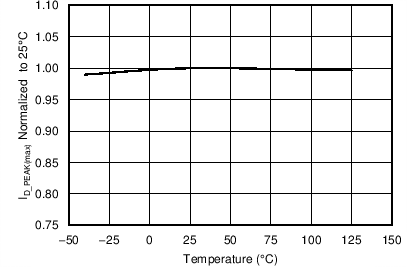

9.8 Typical Characteristics

Unless otherwise specified, VVDD = 15 V, TA = –40°C to 125°C, TA = TJ