## HYBRID ISOLATION AMPS ZAP PRICE AND VOLTAGE BARRIERS

Two Hybrid Amplifiers Cut a Novel Path to High-Voltage Isolation.

They Spare Designers From Having to Engineer Difficult Solutions Themselves.

If any device tests an analog designer's ingenuity, it is an isolation amplifier. Its job is to pass precise analog signals—safely and without degradation—between two points that may differ by hundreds, even thousands, of volts. Even though the high voltage may be damaging and noisy, it is often there by design, and sometimes because of a fault in the system.

Ideally, an amplifier should be small, hermetically sealed, reliable—and inexpensive. Standard devices have included modular and hybrid isolation amplifiers, now available for more than 10 years. Yet because of the stringent requirements of most applications, some 80% of all amplifiers in use are in-house designs.

A family of isolation amplifiers aims at relieving engineers of the chore of designing their own. The family's first two members, the ISO102 and ISO106, are rated respectively at 1500V and 3500V. Both are unity-gain buffers. Each device is easy to make, electrically and mechanically rugged, inexpensive, and isolates better than any now available by an order of magnitude.

As three-chip hybrids, the amplifiers have from the start been designed to solve economically the problems that up to now have limited the use of off-the-shelf units. Key to keeping costs down is a capacitive-coupling approach to isolation. Any amplifiers so far available with the same capabilities are costly, enlisting magnetic or optical techniques to bridge the high-voltage barrier. Whether hybrids or modules, they are all multidevice circuits requiring complex assembly procedures.

The least expensive competitive device, for example, is rated at half the ISO102's rms voltage, yet costs twice as much.

The two new units, on the other hand, combine innovative packaging to their novel approach to high-voltage isolation. Each of the amplifiers is housed in a low-profile, side-brazed 0.6" wide ceramic DIP. (see "Building a Hermetically Sealed Isolation Amp").

## DIFFERENT VOLTAGE. DIFFERENT LENGTH

The only physical difference between the two amplifiers lies in the different lengths needed for withstanding their respective isolation voltages—the voltage across the barrier. The ISO102 is in a 24-pin package, the ISO106 in one for 40 pins. However, to maximize isolation, all but 16 pins—8 at each end of the packages—have been eliminated. External spacing between conductive materials on opposite sides of the barrier is 390 mils for the 1500V ISO102, 1180 mils for the 3500V ISO106.

Because of that construction, their isolation-mode rejection ratio (IMRR), a key specification similar to common-mode rejection ratio (CMRR), is guaranteed to be at least –125dB at 60Hz. (The IMRR is found by taking the change in the amplifier's output-signal voltage caused by a change in the voltage across the barrier, and dividing it by the barrier-voltage change.) While not a function of ambient temperature, IMRR, like CMRR, rolls off with frequency at 20dB per decade. However, unlike that of most other amplifiers, the IMRRs of the ISO102 and ISO106 hold their value at the rated isolation voltage.

Another unusual feature, even among hybrids built on ceramic substrates, is that they are hermetically sealed. Furthermore, many other devices incorporate organic packaging materials and therefore are subject to something called partial discharge, which can degrade a barrier continuously exposed to high AC voltages.

It is important to understand partial discharge when using isolation amplifiers. The phenomenon takes place as a localized breakdown of material, but the breakdown does not bridge the space across the barrier. The discharge-inception voltage depends on the insulation material and can be significantly less than the rated breakdown voltage.

Experiments show that a typical barrier's breakdown voltage will actually decrease with time if continuously exposed to partial discharge. Thus, for maximum reliability the isolation barrier must not be operated at an AC voltage beyond the point at which partial discharge starts.

Voids in the insulating material set the stage for the problem. Alternating electric fields can generate a localized plasma within the voids. A short burst of current flows for about 50ns as the pockets of plasma form, and measurement of this current indicates that partial discharge is taking place. The plasma is usually destructive because ionic bombardment of the walls of the void creates excessive temperature on the wall surface.

Because the barriers of the ISO102 and ISO106 are made of ceramic they are not only virtually free of voids, but also able to stand high temperatures over long periods without damage. Moreover, partial discharge is much more prevalent in barriers insulated with organic materials, which are impossible to fabricate without voids and therefore more damageable by plasma.

In another innovative technique, the ISO102 and ISO106 feature coupling capacitors that jump the isolation barrier by using frequency modulation, a technique previously untried in isolation amps. The capacitors are simply 3pF thick-film devices deposited on the ceramic substrate at the time its tungsten metallization is laid down. The capacitors take the place of transformers or of a combination of LEDs and photodiodes.

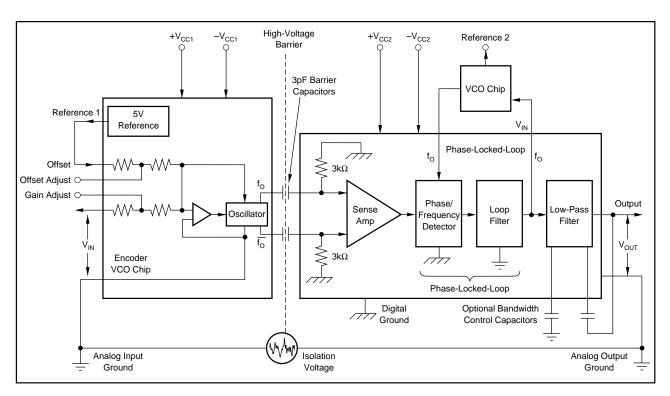

The signal through the capacitors is a 1MHz frequency-modulated square wave; in effect, it is a pseudo-digital waveform. It takes three proprietary chips to modulate and demodulate the  $\pm 10$  input signal—one of them a phase-locked loop, the other two are voltage-to-frequency converters. One of the three, the encoder (which is the FM modulator) to which the floating signal is applied, is a voltage-controlled oscillator (VCO) with a center frequency of 1MHz (Figure 1). The  $\pm 10V$  input modulates the 1MHz signal  $\pm 500 \text{kHz}$ . The VCO's output is through a pair of complimentary pulse trains,  $f_{\rm O}$  and  $\overline{f_{\rm O}}$ , that drive the two

tungsten capacitors. The decoder on the other side of the barrier is formed by the phase-locked loop (PLL) and the second VCO.

The PLL chip contains a sense amplifier, the loop circuitry, and an output filter. The sense amplifier reshapes the pulse trains after they have been high-pass filtered by an RC network formed by the barrier capacitors and the chip's  $3k\Omega$  input resistors. The sense amplifier drives a digital phase and frequency detector that guarantees rapid phase-locking. The detector's output, in turn, feeds a 70kHz loop filter that drives the feedback VCO.

The pair of VCOs gives virtually identical transfer functions to modulation and demodulation. The accuracy of the isolation buffer thus depends only on the matching of the VCOs, not on their actual transfer function. The PLL forces the feedback VCO to run at the same frequency as the encoder VCO, something that occurs when the two have the same input voltage. The input voltage to the feedback VCO becomes the output  $(V_{\text{OUT}})$  of the isolation amplifier after a second-order Butterworth low-pass filter removes residual carrier noise.

Each VCO chip also contains a 5V, 10ppm/°C reference that controls the buffer's input and output offset voltages. The references are in effect independent 5V sources, each of which can supply up to 5mA to external circuits.

FIGURE 1. The ISO102 and ISO106, Respectively Rated 1500V and 3500V, Transport Their Analog Input Signals Across the High-Voltage Barrier on a Pair of 3pF Tungsten Capacitors. To feed the input signal through the capacitors, the signal frequency modulates a 1MHz carrier in an encoder VCO; The signal is demodulated on the other side of the barrier by a matching feedback VCO and a phase-locked loop.

The easy-to-use buffers have gain and offset trimmed respectively to within 0.1% and 20mV while the chips are still on-wafer. Gain and offset errors may be trimmed through zero with a pair of input potentiometers.

Nominally, the chips on both sides of the barrier operate from split  $\pm 15$ V supplies; in practice they will operate anywhere between  $\pm 10$  and  $\pm 20$ V. The device can put out 5mA and swing to within 3V of the rails. Indeed, because only the output supplies limit the swing, input voltage can actually exceed input supply voltage.

By adding a pair of small capacitors on the output side of the buffer, in parallel with the low-pass-filter capacitors, the designer can trade off between system bandwidth and system dynamic range—maximum signal swing divided by the noise floor. Doubling the dynamic range quarters the bandwidth (Figure 1 again); adding 0.01 and 0.02μF capacitors boosts the dynamic range to 16 bits while cutting the bandwidth to 280Hz. Without the two capacitors, dynamic range is typically 12 bits, small-signal bandwidth 70kHz, and the 1MHz carrier appears as a 1mVp-p ripple on the output.

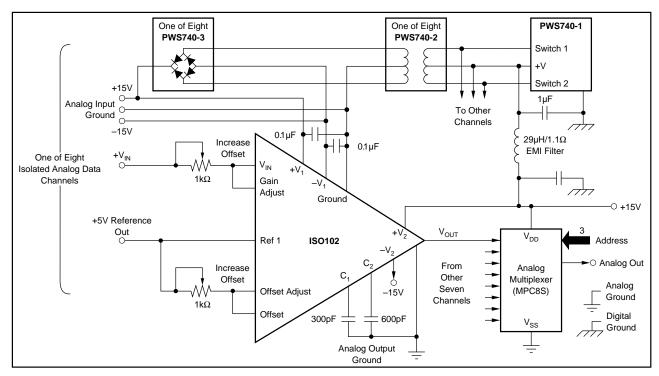

One common configuration for an isolation amplifier is a system with multiple channels isolated from each other as well as from their output side. At the output, the signals feed an A/D converter and a computer.

One of the eight amplifiers drives an eight-channel analog multiplexer. A  $5k\Omega$  potentiometer trims the channel's gain to unity, while one of two  $1k\Omega$  potentiometers trims offset voltage to as close to zero as possible. The potentiometers

can also trim other gain and offset errors in the channel. In addition, with 300pF and 600pF capacitors connected respectively to the  $C_1$  and  $C_2$  pins, small-signal bandwidth is reduced to 10kHz.

Isolated power for the eight separate amplifiers comes from the PWS740 series of DC/DC converter building blocks. One 400kHz PWS740-1 switch-mode control circuit drives eight PWS740-2 transformers in parallel, one for each channel

Each transformer's output is rectified by a PWS740-3 diode bridge, while  $0.1\mu F$  bypass capacitors on the isolation amplifier's power pins provide all the filtering needed. An LC  $\pi$  filter in the +15V line to the controller eliminates conducted EMI from the rest of the circuit.

To maintain a system's accuracy, a designer must take several limiting aspects of the amplifiers into consideration. For example, the modulation and demodulation technique imposes a limit on the isolation voltage's permissible slew rate.

Transients across the barrier that exceed  $100V/\mu s$  can generate enough common-mode current in the capacitors to overdrive the decoding circuit. The effect is to interrupt accurate signal transmission for a moment, but no damage occurs because the devices are protected for transients to  $100,000V/\mu s$ .

On the other hand, the rated IMRR prevails in the presence of a 7.5kHz, 1500Vrms sine wave because slew rate across the barrier does not exceed 100V/µs. For a rated IMRR, the

FIGURE 2. The Isolation Amplifiers Lend Themselves to Multichannel Isolated Analog Data Systems. Gain and zero (offset) adjustment potentiometers can handle that job for both amplifier and other channel errors.

rms value of the isolation voltage must be less than 11.3MV divided by the frequency in Hertz, as well as less than the rated isolation voltage.

The slew-rate limit is of concern only when the signal floats continuously on rapidly changing potentials. It need not be considered where isolation is only a factor under fault conditions, as in medical devices.

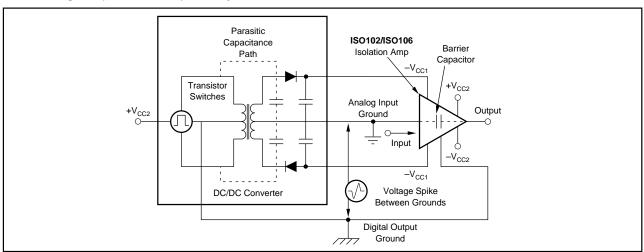

Typical among isolated systems is the kind with completely floating inputs powered by a high-frequency DC/DC converter, driven in turn by a logic supply on the barrier's output side. The likelihood then is that the supply's ground is the same as the buffer's digital ground.

In such a case, because the primary of the transformer is driven with a fast rising and falling rectangular waveform, the converter capacitively couples a charge to the ground system of its output side (Figure 3). Moreover, the transformer's core and wiring capacitance form a path between the primary and secondary windings.

That path continues through the amplifier and its barrier capacitors to the digital ground. The transformer capacitance in turn forms a voltage divider with the barrier capacitors so that a portion of the switching waveform appears across them.

Any noise spikes between input and output grounds faster than  $100V/\mu s$  and higher than 1Vp-p, will interfere with the buffer. Spikes can be reduced, however, by using bifilar wire for the transformer's primary and secondary windings; that is, winding each side of the center tap with a pair of twisted wires, rather than one wire. The result is a greater symmetry in the primary to secondary capacitance, reducing the coupled charge. Another method is to use an electrostatic shield between the primary and secondary windings.

## BUILDING A HERMETICALLY SEALED ISOLATION AMP

The hardest part of making an isolation amplifier is building the high-voltage barrier. The barrier in the 1500V ISO102 and the 3500V ISO106 is an elegant and simple solution: a pair of 3pF capacitors form an integral part of the DIP that houses the amplifier.

Construction of the package starts with a 0.6" wide ceramic substrate. A layer of tungsten forms the amplifier's pin-to-die and die-to-die connections, as well as the spiral patterns of the barrier capacitors. Capacitance results from the fringing electric fields of adjacent lines of tungsten, which are 0.63mm apart.

Next, a layer of ceramic is fired on top of the substrate, embedding the capacitor in solid ceramic. The material's 15,000V/mm dielectric strength imparts a breakdown voltage in excess of 9000Vrms. The barrier's resistance is typically  $10^{14}\Omega$ . Windows in this second layer of ceramic form cavities for the amplifier's three integrated circuits—two voltage controlled oscillators and a phase-locked loop.

Metal patterns, including lid-seal rings and lead pads, are screened onto the layer and nickel-plated. The pins are brazed to the sides of the package and all exposed metal is plated with one micron of gold. The chips are then mounted in the finished package. After testing, the lids are soft-soldered over the two cavities, hermetically sealing the amplifier.

FIGURE 3. In Some Cases, as When a DC/DC Converter Drives the Isolation Amplifier, Voltage Rate of Change is as Important as Voltage Level. The reason is that the transformer's core and the barrier capacitors form a voltage divider, with a portion of the switching waveform appearing across it.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

## **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated