# Interfacing the TLV1544 Analog-to-Digital Converter to the TMS320C50 DSP

December 1998

**Mixed-Signal Products**

SLAA025A

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated

| 1  | Introd                                     | uction                                                                                                                                                                                                                                                                                                                                 | 1                                                            |

|----|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| 2  | <b>The S</b><br>2.1<br>2.2<br>2.3          |                                                                                                                                                                                                                                                                                                                                        | 2<br>3                                                       |

| 3  | ADC 0<br>3.1<br>3.2                        | Overview         Signal Sequence           The ADC/DSP Interface                                                                                                                                                                                                                                                                       | 8                                                            |

| 4  | <b>The TI</b><br>4.1<br>4.2<br>4.3         | MS320C50 DSP         Key Features         The DSP Serial Port         4.2.1 Signals and Registers         4.2.2 Serial Port Operation         4.2.3 Serial Port Configuration         4.2.4 Transmit and Receive Operations in Burst Mode         The Hardware Timer         4.3.1 Timer Operation         4.3.2 Programming the Timer | . 15<br>. 16<br>. 16<br>. 17<br>. 18<br>. 20<br>. 21<br>. 21 |

| 5  | 5.1<br>5.2                                 | are Description                                                                                                                                                                                                                                                                                                                        | 26<br>27<br>28<br>32<br>33<br>33<br>36                       |

| 6  | Summ                                       | nary                                                                                                                                                                                                                                                                                                                                   | . 40                                                         |

| 7  | Refere                                     | ences                                                                                                                                                                                                                                                                                                                                  | . 43                                                         |

| Ap | A.1<br>A.2<br>A.3<br>A.4                   | A TLV1544 Program Files: Timer as Interrupt Source)<br>Boot Routine: BOOTIN.ASM<br>C-Program: C1544T.C<br>C-Callable Interface Program: C1544TIN.ASM<br>Vector Table: VECTIN.ASM                                                                                                                                                       | A-1<br>A-2<br>A-3                                            |

| Ap |                                            | B TLV1544 Program Files: Timer as Clock Source<br>Boot Routine: BOOTCLK.ASM<br>C-Program: C1544C.C<br>C-Callable Interface Program: C1544CLK.ASM<br>Vector Table: VECCLK.ASM                                                                                                                                                           | B-1<br>B-2<br>B-3                                            |

| Ap | <b>Dpendix</b><br>C.1<br>C.2<br>C.3<br>C.4 | C TLV1544 Program Files: NOPs for Wait-Loop<br>Boot Routine: BOOTNOP.ASM<br>C-Program: C1544N.C<br>C-Callable Interface Program: C1544NOP.ASM<br>Vector Table: VECNOP.ASM                                                                                                                                                              | C-1<br>C-2<br>C-3                                            |

## Contents

## List of Figures

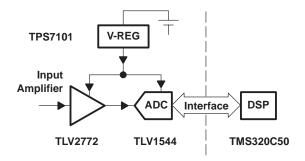

| 1  | Data Acquisition System Using the TLV1544 ADC                                  | . 2 |

|----|--------------------------------------------------------------------------------|-----|

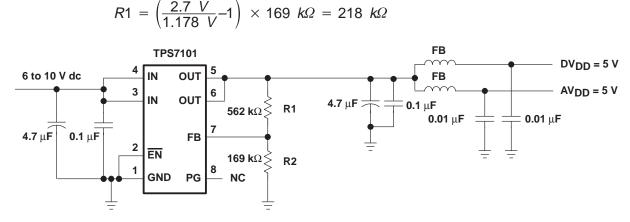

| 2  | Standard ADC/DSP Interface for a Fixed Data Clock at CLKX                      | 3   |

| 3  | Typical Voltage Regulator Schematic                                            | . 4 |

| 4  | Schematic of a Noninverting Analog Input Buffer                                | 5   |

| 5  | Schematic of an Inverting Input Buffer for Larger Input Signals                | 6   |

| 6  | Functional Block Diagram of the TLV1544 and TLV1548                            | . 7 |

| 7  | DSP Interface Timing (16-Clock Transfer, Normal Sample Mode, INV CLK = High)   | 9   |

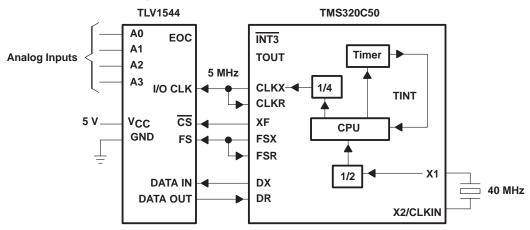

| 8  | Glueless ADC/DSP Interface                                                     | 11  |

| 9  | Maximum Data Throughput via Immediate EOC Detection                            | 12  |

| 10 | Serial Interface for Low-Volt Operation and High Data Throughput               | 12  |

| 11 | Glueless Interface for Low-Volt Operation                                      | 13  |

| 12 | Serial Port Block Diagram                                                      | 17  |

| 13 | Serial Port Control Register                                                   | 18  |

| 14 | Configuring and Activating the Serial Port for 5-V Operation of the ADC        | 19  |

| 15 | Configuring and Activating the Serial Port for 2.7-V Operation of the ADC      | 20  |

| 16 | Transmit and Receive Operation in Burst Mode                                   | 20  |

| 17 | Timer Block Diagram                                                            | 22  |

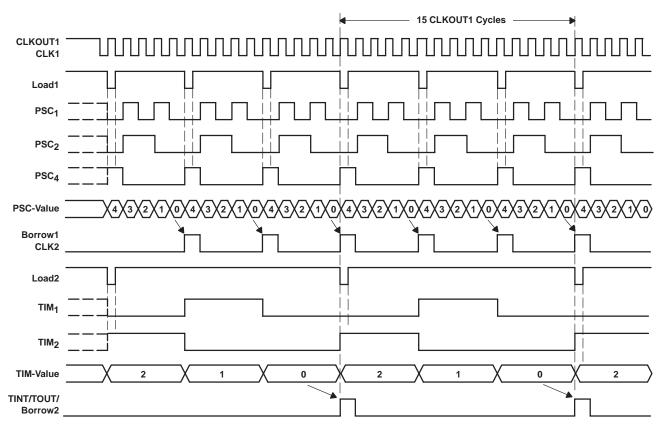

| 18 | Timing Diagram for TDDR = 4 and PRD = 2                                        | 23  |

| 19 | Timer Control Register                                                         | 23  |

| 20 | Timer Interrupt, TINT, Indicates EOC in a Glue-Less Interface                  | 27  |

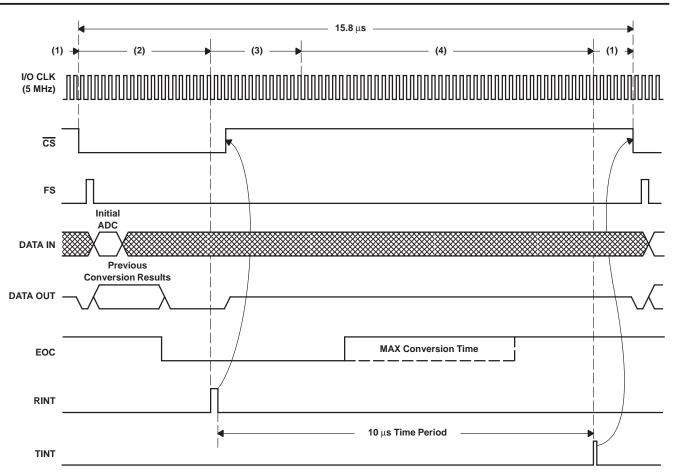

| 21 | Data Transfer Sequence When Using TINT and ADC in Fast Conversion Mode         | 28  |

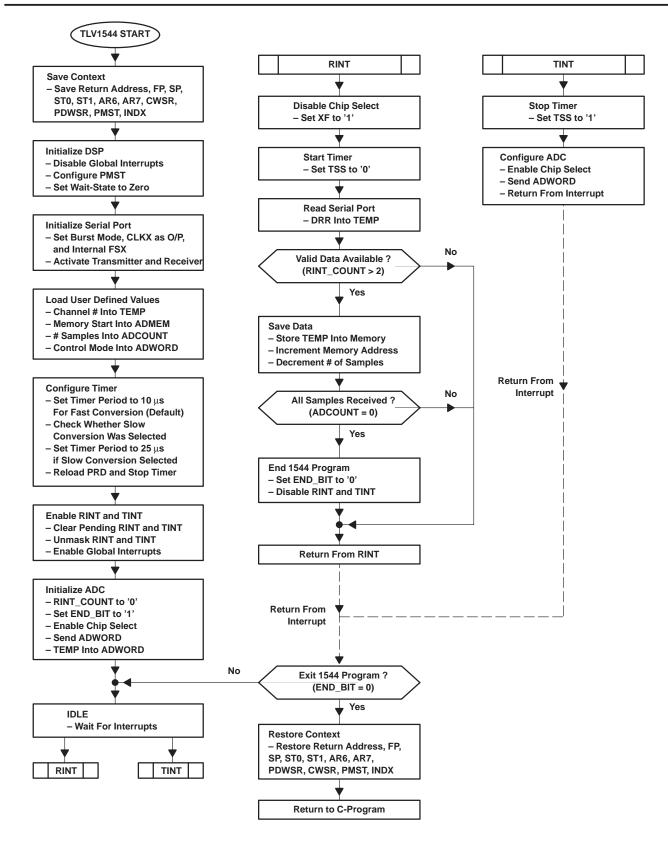

| 22 | Flowchart of C1544IN.asm (Timer as Interrupt Source)                           | 30  |

| 23 | External Interrupt, INT3, Detects EOC Via External Inverter                    | 32  |

| 24 | Data Transfer Sequence When Using INT3 and ADC in Slow Conversion              | 33  |

| 25 | Flowchart of C1544CLK.asm (Timer as Clock Source)                              | 35  |

| 26 | A Wait-loop Indicates EOC in a Glueless Interface for Low-Volt Application     | 36  |

| 27 | Data Transfer Sequence When Using a Wait-Loop for a Low-Volt Application       | 37  |

| 28 | Flowchart of C1544NOP.asm (Timer as Clock Source + NOP delay)                  | 38  |

| 29 | Interfacing the TLV1544 ADC with the TMS320C50 DSP                             | 40  |

| 30 | Time Periods Between Two Consecutive Data Transfers for Different Applications | 41  |

## List of Tables

| 1  | TLV1544/TLV1548 ADC Control Words                          | 10 |

|----|------------------------------------------------------------|----|

| 2  | Conversion Times for Fast and Slow Conversion              | 11 |

| 3  | Clock Frequencies at I/O CLK for 5.5-V and 2.7-V Operation | 12 |

| 4  | Benefits of the Individual Interface Circuits              | 14 |

| 5  | Serial Port Registers                                      | 17 |

| 6  | Serial Port Control Register Bits Summary                  | 18 |

| 7  | SPC Configuration for Interfacing to the TLV1544/48 ADC    | 19 |

| 8  | Timer Control Register Bits Summary                        | 24 |

| 9  | Local and Global Variables and Corresponding Programs      | 26 |

| 10 | ) Timer Application and Corresponding Filenames            | 27 |

## Interfacing the TLV1544 Analog-to-Digital Converter to the TMS320C50 DSP

Thomas Kugelstadt and David Quach

#### ABSTRACT

This application report presents two hardware solutions for interfacing the TLV1544 10-bit low-power analog-to-digital converter (ADC) to the TMS320C50 16-bit fixed-point digital signal processor (DSP). The report describes the interface hardware and shows three C-callable software routines which support the data transfer. In addition, it provides useful hints on the design of a typical system power supply and shows two input buffers for the analog inputs of the ADC.

#### 1 Introduction

The TLV1544/48 is a 10-bit, low-power, successive approximation analog to digital converter (ADC) with a conversion time of  $t_{CONV} \le 10 \,\mu s$ . The TLV1544 has four analog inputs; the TLV1548 has eight.

The device operates from a maximum supply voltage of  $V_{DD}$  = 5.5 V down to a minimum supply voltage of  $V_{DD}$  = 2.7 V, thus making it suitable for portable, low-power applications.

With a 5.5-V supply, a maximum ADC interface clock (I/OCLK) of 10 MHz is possible. With a 2.7-V supply, the maximum clock is 2.89 MHz.

The DSP serial interface port standard configuration provides only a 5-MHz clock and it is applied when the ADC operates at 5 V.

A second serial port configuration uses the DSP on-chip timer to generate a programmable clock rate between 0 Hz and 5 MHz. This configuration is used to clock the interface at 2 MHz when the ADC operates at 2.7 V.

In addition, this solution allows increasing the data throughput by a factor of two. The interface configuration possibilities are discussed in detail in Section 3.2.

#### 2 The System

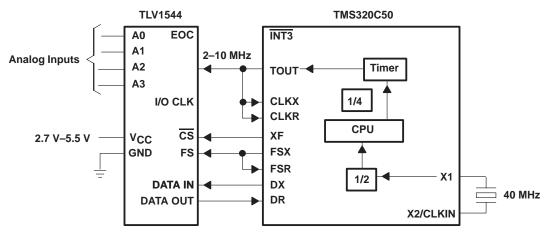

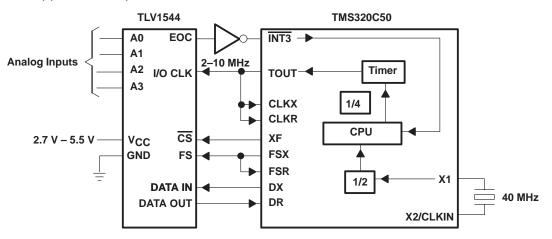

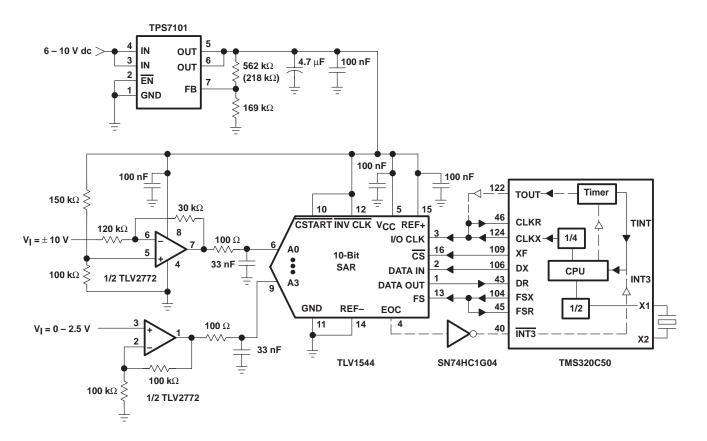

While this report focuses on the interface between the ADC and DSP (see Figure 1), it includes informative hints on the power supply section and on the buffering of the ADC inputs.

#### 2.1 Standard ADC-DSP Interface

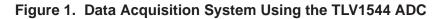

Figure 2 shows the standard ADC/DSP interface for a fixed data clock rate at CLKX. The regulated supply voltage of  $V_{DD} = 5$  V is applied to the ADC  $V_{CC}$  pin. A 4.7-µF bulk capacitor keeps the entire circuit supply stable against any significant current changes during ADC operation. The 0.1- $\mu$ F bypass capacitors keep the ADC supply, as well as the positive reference voltage and the unused digital inputs, ripple-free. The bypass capacitors should be as close as possible to the individual pins.

The positive reference voltage (REF+), is tied to  $V_{CC}$ ; the negative reference voltage, REF-, is connected to GND. This defines the analog conversion range of the ADC and specifies the maximum input signal level at the analog inputs, A0 to A3.

The unused, low active, digital control pins are tied to  $V_{CC}$ .

In the application with fixed data clock, the interface between the TLV1544 ADC and the TMS320C50 DSP requires no additional control logic.

- The DSP sends an initial chip-enable signal via the XF pin to the  $\overline{CS}$  pin of • the ADC.

- The transmit clock output of the DSP, CLKX, provides a fixed data clock into ۰ the I/O CLK input of the ADC and into the receive clock input, CLKR.

- The transmit frame-sync output (FSX), initializes every data transfer by • sending a frame-sync pulse to the ADC FS input as well as to the receive frame-sync input, FSR.

- The DSP initializes the ADC by transferring 4-bit control words from the DX • output into the DATA IN input of the ADC.

- The ADC clocks digital conversion results out at DATA OUT into the DR-pin of the DSP.

Section 3.1 gives detailed information on signal sequence, word-length and clock rates.

SLAA025A 2

NOTE: Fixed data clock is only possible with  $V_{DD} = 5 V$ .

#### Figure 2. Standard ADC/DSP Interface for a Fixed Data Clock at CLKX

#### 2.2 Power Supply Circuit

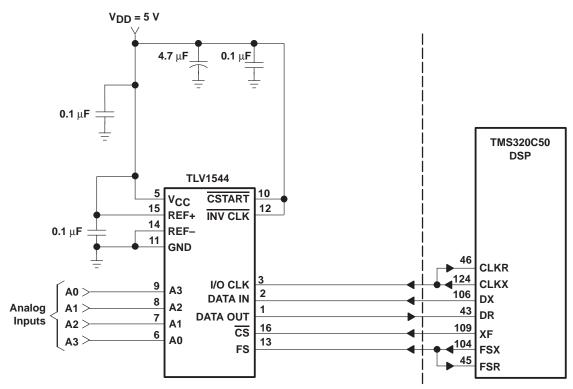

Figure 3 shows a typical voltage regulator schematic using the adjustable low-dropout regulator (LDO) TPS7101. The LDO has a very low dropout voltage of 32 mV at an output current of  $I_{OUT}$  = 100 mA.

Its very low typical quiescent current of 285  $\mu A$  remains independent of output loading over the full range of output current, 0 mA to 500 mA.

The TPS7101 regulates an input voltage in the range of 6 to 10 V dc down to the adjusted output level. In this application the output is adjusted to 5.1 V through the voltage divider R1 and R2.

The equation governing the output voltage is:

$$V_O = V_{REF} \times \left(1 + \frac{R1}{R2}\right)$$

with Vref = reference voltage of 1.178 V typ. (1)

Resistors R1 and R2 should be chosen for approximately 7  $\mu$ A divider current. The recommended value for R2 is 169 k $\Omega$  with R1 adjusted for the desired output voltage. Smaller resistors can be used, but offer no inherent advantage and consume more power. Larger values of R1 and R2 should be avoided, as leakage currents at the FB pin will introduce an error. Solving Equation 1 for R1 yields a more useful equation for choosing the appropriate resistance:

$$R1 = \left(\frac{V_O}{V_{ref}} - 1\right) \times R2 \tag{2}$$

Calculating R1 for  $V_{OUT}$  = 5.1 V and R2 = 169 k $\Omega$  results in:

$$R1 = \left(\frac{5.1 \ V}{1.178 \ V} - 1\right) \times 169 \ k\Omega = 562 \ k\Omega$$

In the low-power application the TLV1544 ADC operates at the minimum supply voltage of  $V_{CC}$  = 2.7 V. Therefore, the value of R1 changes to:

NOTES: A. R1 = 562 k $\Omega$  for V\_DD = 5.1 V and 218 k $\Omega$  for V\_DD = 2.7 V

- B. Bypass capacitors should be placed as close to the device pins as possible. The total ESR of the regulator output capacitors must maintain between 0.7 Ω min and 2.5 Ω max.

- C. FB is the Fair-Rite <sup>™</sup> #27-44-044447 or equivalent. Fair-Rite is a trademark of Fair–Rite Products Corporation.

- D. NC = no internal connection.

#### Figure 3. Typical Voltage Regulator Schematic

The input capacitors shown are usually not required; however, the  $0.1-\mu F$  ceramic bypass capacitor improves load transient response and noise rejection if the TPS7101 is located more than a few inches from the power supply. A higher capacitance electrolytic capacitor may be necessary if large load transients with fast rise times are anticipated.

The chosen output capacitors are required for stability. A low-ESR 4.7- $\mu$ F solid tantalum capacitor and a 0.1- $\mu$ F high-frequency ceramic capacitor, connected from the regulator output to ground, are sufficient to ensure stability, provided that the total ESR is maintained between 0.7  $\Omega$  and 2.5  $\Omega$ .

Two additional low-pass filters, each consisting of a ferrite bead, FB, and a  $0.01-\mu F$  capacitor, block the digital noise and transients on the digital supply line,  $DV_{DD}$ , from the analog supply,  $AV_{DD}$ .

For more information on the type of ferrite beads and the selection and type of low-ESR capacitors, refer to the TPS7101 Data Sheet, literature number SLVS092F and the TLV1544 EVM User's Guide, literature number SLAU014.

#### 2.3 Analog Input Buffer Circuit

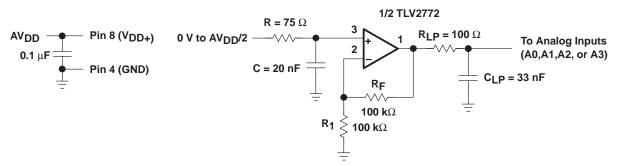

Figure 4 and Figure 5 show the schematics of typical analog input buffers using the TLV2772 dual operational amplifier.

The TLV2772 combines high slew rate and bandwidth, rail-to-rail output swing, high output drive and excellent dc precision. The device provides 10.5 V/ $\mu$ s of slew rate and 5.1 MHz of bandwidth while only consuming 1 mA of supply current per channel.

This ac performance is much higher than current competitive CMOS amplifiers. The rail-to-rail output swing and high output drive make it a good choice for driving the analog input or reference of analog-to-digital converters. The device also has low distortion while driving a  $600-\Omega$  load for use in telecom systems.

This amplifier has a 360  $\mu$ V input offset voltage, a 17 nV/Hz input noise voltage, and a 2 pA input bias current for measurement, medical, and industrial applications.

The device operates from a 2.5 V to 5.5 V single supply voltage. Its low power consumption makes it a good solution for portable applications.

#### Figure 4. Schematic of a Noninverting Analog Input Buffer

In this configuration the TLV2772 works as a noninverting amplifier with a closed loop gain of two (as shown in Equation 3).

$$Gain = \frac{V_{OUT}}{V_{IN}} = 1 + \frac{R_F}{R_1} = 1 + \frac{100 \ k\Omega}{100 \ k\Omega} = 2$$

(3)

The input voltage range is therefore limited to between 0 V and  $AV_{DD}/2$ . The input low-pass filter consists of an RC circuit with a corner frequency of 106 kHz. While the filter is optional, it can be useful when operating in a noisy environment.

The low-pass filter at the op-amp output (RLP and CLP), has a corner frequency of

$$fc = \frac{1}{2\pi \times R_{LP} \times C_{LP}} = \frac{1}{2\pi \times 100 \ \Omega \times 33 \ nF} = 48 \ kHz \tag{4}$$

This filter limits the input signal bandwidth, and with it the operational amplifier inherent noise level which is fed into the ADC, thus improving the signal-to-noise ratio of the system significantly.

An additional 0.1- $\mu$ F bypass capacitor, connected between V<sub>DD+</sub> (pin 8) and GND (pin 4) of the device, ensures a noise-free supply for the operational amplifier.

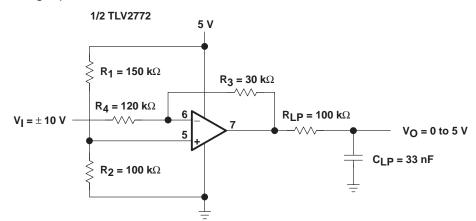

Figure 5 shows another input buffer circuit that allows  $\pm 10$ -V input signals into the 5-V analog inputs of the ADC.

#### Figure 5. Schematic of an Inverting Input Buffer for Larger Input Signals

In this configuration the TLV2772 operates as an inverting amplifier with a closed loop gain of 0.25 (as shown in Equation 4).

$$Gain = \frac{V_{OUT}}{V_{IN}} = -\frac{R_3}{R_4} = -\frac{30 \ k\Omega}{120 \ k\Omega} = -0.25$$

(5)

Resistors R<sub>1</sub> and R<sub>2</sub> bias the output of the operational amplifier to a 2.5-V operating point. A maximum input voltage of  $\pm 10$ -V is amplified by -0.25 and results in an output voltage of  $\pm 2.5$  V. The negative sign in the gain factor represents a phase shift of 180° between input- and output-signal.

## 3 ADC Overview

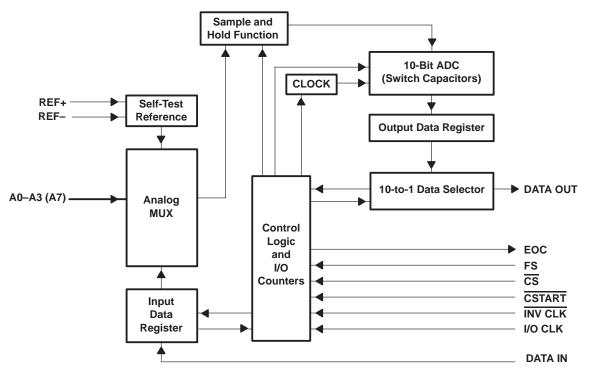

The TLV1544 and TLV1548 are CMOS 10-bit switched capacitor successive approximation (SAR) ADCs. The TLV1544 has four analog inputs; the TLV1548 has eight. Figure 6 shows a functional block diagram of the devices.

The TLV1544 operates from a minimum supply of 2.7-V to a maximum supply of 5.5-V and allows high-speed data transfer from the host of up to 10-MHz maximum. In addition to the on-chip multiplexer that can select any one of the analog inputs or any one of the three internal self-test voltages, the ADC provides a versatile control capability. Through the DATA IN pin, 4-bit control words initialize the device for:

- Any one of the analog input channels

- Power-down mode

- Slow or fast conversion rate

- Any one of the self-test voltages.

Figure 6. Functional Block Diagram of the TLV1544 and TLV1548

A 4-wire serial interface (SPI <sup>TM</sup>, QSPI <sup>TM</sup>) allows data transfer to a microprocessor or DSP. When interfacing to a TMS320 DSP, an additional frame sync (FS) signal indicates the start of a serial data frame. A high at the chip-select pin  $\overline{CS}$  activates the device. The data clock at I/O CLK determines the data rate between ADC and host. Through DATA IN, 4-bit control words initialize the ADC for the desired operation mode and select the analog input. The EOC pin indicates the end of a conversion and DATA OUT provides the conversion results in a 10-bit serial format.

SPI and QSPI are trademarks of Motorola, Inc.

A high at the INV CLK pin allows for I/O clock phase adjustment of 180°. When operating in the extended sampling mode, the CSTART pin controls the sampling period of the sample-and-hold circuit and starts the conversion. In this application, INV CLK and CSTART are not used and are therefore tied high.

#### 3.1 Signal Sequence

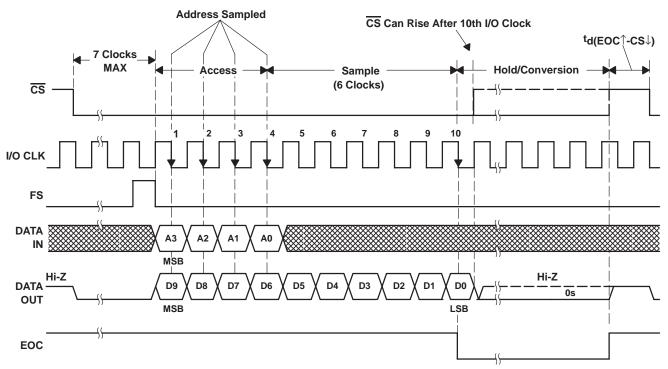

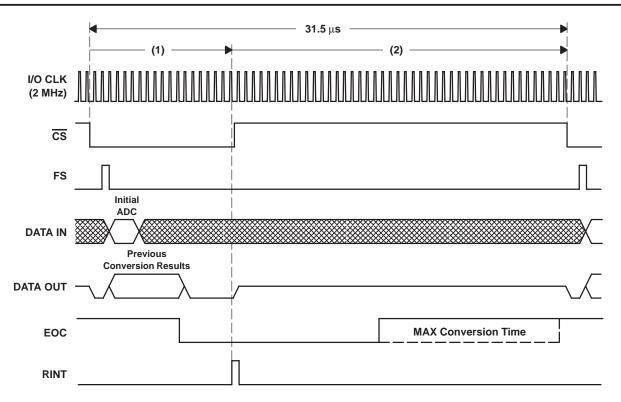

Figure 7 shows the timing diagram of a data transfer between the TLV1544 ADC and the TMS320C50 DSP through the DSP serial port. The ADC serves as a slave device and the DSP operates as the master, supplying the frame-sync signal, FS, and the data transfer clock, I/O CLK. Initially, with CS high and the ADC being inactive, the inputs, DATA IN and I/O CLK, are disabled. DATA OUT is in the high-impedance state and EOC is high.

When the DSP activates the ADC by taking  $\overline{CS}$  low and providing the data clock to I/O CLK, the data transfer sequence begins. I/O CLK and DATA IN are enabled and DATA OUT is removed from the high-impedance state to logic low. The DSP then sends out a FS pulse on the FS line, indicating the start of a data frame.

With the falling edge of FS, the DSP provides the 4-bit control word to DATA IN (see Table 1 for ADC control words) starting with the most significant bit (MSB). At the same time, the ADC provides a 10-bit conversion result (from the previous conversion) at DATA OUT, beginning with MSB.

The input data selects a different mode or selects different analog input channels. In the case of the control word being a channel address, the selected analog input channel is accessed during the first four I/O clock cycles after the falling edge of FS. Starting with the falling edge of the fourth I/O cycle, the sample-and-hold (S&H) circuit samples the selected analog input.

NOTES: E. The falling edge of FS has to appear within 7 I/O clock cycles from the falling edge of  $\overline{CS}$ .

F. The TLV1544/48 data sheet specifies a minimum time of t<sub>d</sub> = 100-ns after the rising edge of EOC before the next falling edge of CS.

#### Figure 7. DSP Interface Timing (16-Clock Transfer, Normal Sample Mode, INV CLK = High)

At the tenth falling edge of I/O CLK, the sample is held and the analog-to-digital conversion starts. At the same time the EOC output changes from high to low, indicating the conversion start. The DSP initiates the end of a data transfer sequence by taking  $\overline{CS}$  high, which disables DATA IN, I/O CLK and DATA OUT. This can happen between the end of the tenth I/O clock and the rising edge at EOC, indicating end-of-conversion.

If  $\overline{CS}$  is taken high immediately after the tenth clock, DATA OUT goes into high-impedance state and, following the 10-bit conversion result, random signal levels are clocked into the DSP for the next six clock cycles. If  $\overline{CS}$  changes to high somewhere between the end of the tenth clock and EOC going high, the 10-bit result is padded with a maximum of six zeros to complement the 16-clock cycle of the DSP.

In any case, the six bits following the conversion result are useless information and should be ignored by the DSP interface software. The entire data transfer sequence is complete when EOC returns to high.

A delay time of  $t_{d(EOC\uparrow - CS\downarrow)} = 100$  ns after the rising edge of EOC is required before  $\overline{CS}$  can change to low again to start a new data transfer.

|                                                        | INPUT DAT | A BYTE |                                                   |

|--------------------------------------------------------|-----------|--------|---------------------------------------------------|

| FUNCTION SELECT                                        | A3 –      | A0     | COMMENT                                           |

|                                                        | BINARY    | HEX    |                                                   |

| Analog channel A0 for TLV1548 Selected                 | 0000b     | 0h     | Analog channel 0 for TLV1544                      |

| Analog channel A1 for TLV1548 Selected                 | 0001b     | 1h     |                                                   |

| Analog channel A2 for TLV1548 Selected                 | 0010b     | 2h     | Analog channel 1 for TLV1544                      |

| Analog channel A3 for TLV1548 Selected                 | 0011b     | 3h     |                                                   |

| Analog channel A4 for TLV1548 Selected                 | 0100b     | 4h     | Analog channel 2 for TLV1544                      |

| Analog channel A5 for TLV1548 Selected                 | 0101b     | 5h     |                                                   |

| Analog channel A6 for TLV1548 Selected                 | 0110b     | 6h     | Analog channel 3 for TLV1544                      |

| Analog channel A7 for TLV1548 Selected                 | 0111b     | 7h     | 1001b                                             |

| Software power down set                                | 1000b     | 8h     | No conversion result (cleared by any access)      |

| Fast conversion rate (10 $\mu$ s) set                  | 1001b     | 9h     | No conversion result (cleared by setting to fast) |

| Slow conversion rate (40 µs) set                       | 1010b     | Ah     | No conversion result (cleared by setting to slow) |

| Self-test voltage ( $V_{ref+} - V_{ref-}$ )/2 selected | 1011b     | Bh     | Output result = 200h                              |

| Self-test voltage V <sub>ref-</sub> selected           | 1100b     | Ch     | Output result = 000h                              |

| Self-test voltage Vref+ selected                       | 1101b     | Dh     | Output result = 3FFh                              |

| Reserved                                               | 1110b     | Eh     | No conversion result                              |

| Reserved                                               | 1111b     | Fh     | No conversion result                              |

#### Table 1. TLV1544/TLV1548 ADC Control Words

#### 3.2 The ADC/DSP Interface

Following the signal sequence description in Section 3.1 and recalling that the DSP is the master and the ADC the slave device, the following interconnections always stay the same:

- **XF** The XF output drives the chip-enable signal into the  $\overline{CS}$ -pin of the ADC.

- **FSX/FSR** The frame-sync pulse is generated by the DSP. This signal is sent from the FSX output into the FS input of the ADC and into the FSR input of the DSP to synchronize the transmitter and receiver stages within the serial port.

- DX Control data, which initialize the TLV1544, are driven from the DSP data transmit output, DX into DATAIN of the ADC.

- **DR** Conversion results from the ADC are fed into the data receive input, DR.

This section focuses mainly on the different options for generating the I/O clock and detecting the end-of-conversion that are possible with the TLV1544/48.

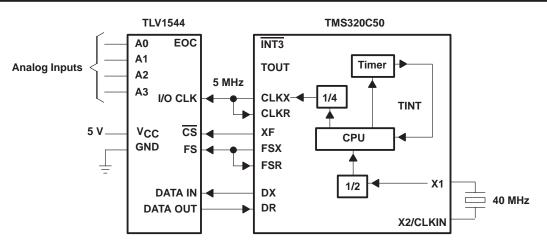

Figure 8 shows the standard interface between a TLV1544/48 ADC and a TMS320C50 DSP with a glueless interface.

The DSP provides an on-chip oscillator, which is enabled by connecting a crystal, with a fundamental frequency of 40 MHz, across X1 and X2/CLKIN. An internal divide-by-two clock option provides the CPU clock of 20 MHz, which translates to an instruction cycle time of 50 ns.

The generation of the I/O clock happens with the initialization of the serial port, which provides an additional divide-by-four function and sets the data transfer clock at CLKX to 5 MHz.

The information on the end-of-conversion status is important, since a previous conversion must be completed before a new conversion can start. The application in Figure 8 does not detect the end-of-conversion signal, but waits for the ADC maximum conversion time to pass. The TLV1544 data sheet specifies the typical and the maximum conversion times for fast and slow conversion, as shown in Table 2.

|                                    | LAB                                                   | DATA SHEET | UNIT |    |

|------------------------------------|-------------------------------------------------------|------------|------|----|

|                                    | Fast conversion from V <sub>CC</sub> = 5.5 V to 3.3 V | 5          | 10   |    |

| Conversion time, t <sub>CONV</sub> | Slow conversion from V <sub>CC</sub> = 5.5 V to 2.7 V | 13         | 25   | μs |

Table 2. Conversion Times for Fast and Slow Conversion

In the interface software, the DSP on-chip timer-counter is programmed with the maximum conversion time for the selected conversion mode and causes a timer interrupt (TINT) once the counter value reaches zero. The following interrupt routine can then initiate a new data transfer sequence.

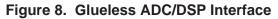

Table 2 compares the conversion times, measured on a series of TLV1544 evaluation modules (EVMs) with the maximum values specified in the data sheet. The lab data differ by a factor of two from the maximum possible conversion times. It is obvious that, even with a glueless interface, waiting for the maximum conversion time to pass is highly time-inefficient. To maximize the data throughput over the interface, the end of a conversion must be detected as soon as it occurs. Only then is it possible to start a new data transfer with minimum latency. The circuit in Figure 9 accomplishes this by connecting the EOC output of the ADC through an inverter to the external interrupt input, INT3 of the DSP.

The end-of-conversion signal (rising edge at EOC) is inverted into a high-to-low transition at INT3 and causes an external interrupt. The initiated interrupt service routine can now start a new data transfer sequence.

The two previous scenarios describe the interface for 5-V operation. For low-power applications with supply voltages of 3 V and less, the TLV1544 data sheet defines lower data clock frequencies at I/O CLK, when compared to 5-V operation.

| Table 3. | <b>Clock Frequencies</b> | at I/O CLK for 5.5-V | and 2.7-V Operation |

|----------|--------------------------|----------------------|---------------------|

|----------|--------------------------|----------------------|---------------------|

| PARAMET                                      | MIN                     | TYP | MAX | UNIT |        |

|----------------------------------------------|-------------------------|-----|-----|------|--------|

| Clock frequency at I/O CI K, factor          | V <sub>CC</sub> = 5.5 V | 0.1 | 6   | 10   | MHz    |

| Clock frequency at I/O CLK, f <sub>CLK</sub> | $V_{CC} = 2.7 V$        | 0.1 | 2   | 2.81 | IVITIZ |

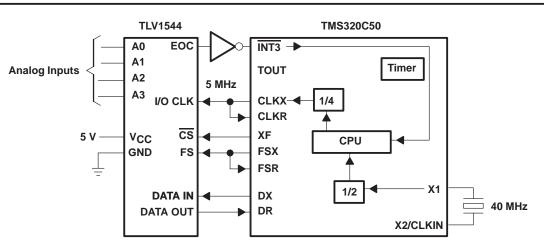

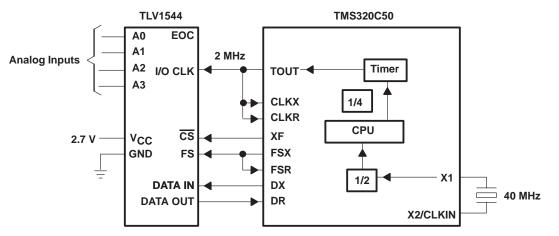

The circuit in Figure 10 shows the ADC operating from a 2.7-V supply. The required data clock at I/O CLK is 2 MHz nominal. Since the only frequency the DSP can provide at CLKX is one fourth of the internal CPU clock (CLKX = 5 MHz), the on-chip timer is initialized as a programmable clock source.

The two period registers of the timer, PRD and TDDR, are programmed to divide the CPU clock of 20 MHz by 10. The timer now generates periodic interrupts at a rate of 2 MHz. While the interrupt requests are masked to the CPU, the 2-MHz signal is still available as data clock at the timer output, TOUT. For more information on the timer functions see Section 4.3. A further advantage of this adjustable clock generator is that it can be programmed for clock rates of up to one half of the CPU clock, to TOUT = 10 MHz.

Since the timer serves here as a clock generator, it is no longer available as an interrupt source to indicate the end-of-conversion (EOC) state of the TLV1544/48. As in the previous application, this circuit detects the EOC by inverting the EOC signal from the ADC into a high-to-low transition at INT3. The external interrupt request to the CPU starts the interrupt service routine which initiates a new data transfer sequence. Figure 11 shows that when the external inverter is removed, the interface becomes glueless again.

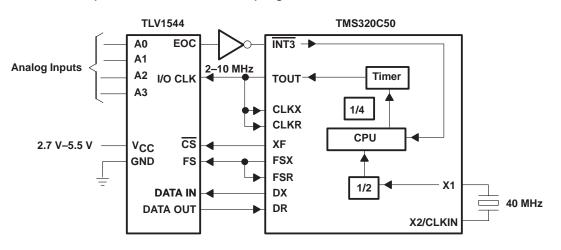

Figure 11. Glueless Interface for Low-Volt Operation

Since neither the inverter nor the timer is available for EOC detection, additional software is required to accomplish this task. A few lines of software code, forming a delay loop that waits for the ADC maximum conversion time to pass, need to be added to the interface program. The additional wait loop consumes DSP programming power and reduces the data throughput significantly. Applying this technique to a low-power application, which already operates in slow conversion mode and at a low data transfer rate, reduces the data throughput significantly. Depending on the requirements of the final application, the simplicity of a glueless interface might outweigh the benefits of a higher data throughput.

Table 4 summarizes the pros and cons of the interface circuits, shown in Figure 8 through Figure 11.

| FIGURE | PROS                                                                                                                                                                                     | CONS                                                                   |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| 8      | Glueless interface for 5-V operation at fixed data clock                                                                                                                                 | Low data throughput due to waiting for maximum conversion time to pass |

| 9      | Factor 2 higher data through put for standard 5-V operation                                                                                                                              | No glueless interface due to external inverter                         |

| 10     | <ul> <li>Flexible interface for a supply range from 2.7 V to 5.5 V</li> <li>Flexible data clocks from 2 MHz to 10 MHz</li> <li>Higher data throughput over whole supply range</li> </ul> | No glueless interface due to external inverter                         |

| 11     | <ul> <li>Glueless interface</li> <li>Flexible interface for a supply range from 2.7 V to 5.5 V</li> <li>Flexible data clocks from 2 MHz to 10 MHz</li> </ul>                             | Low data throughput due to waiting for maximum conversion time to pass |

Table 4. Benefits of the Individual Interface Circuits

The software description in Section 5 provides three examples of interface programs for the circuits in Figure 8 through Figure 11.

## 4 The TMS320C50 DSP

The TMS320C50 DSP is a 16-bit fixed-point, static CMOS digital signal processor. The combination of an advanced Harvard architecture (separate buses for program memory and data memory), on-chip peripherals, on-chip memory, and a highly specialized instruction set is the basis of the operational flexibility of this device.

#### 4.1 Key Features

The 'C50 offers the following key features:

#### • 2K x 16-bit On-Chip ROM

This on-chip, maskable, programmable memory is used for booting from slower, external ROM or EPROM of program to fast on-chip or external SRAM.

#### • 1056 x 16-bit On-Chip Data RAM

The data RAM can be accessed twice per machine cycle (dual-access RAM). This block of memory is primarily intended to store data values but, when needed, can be used to store programs as well as data.

#### • 9K x 16-bit On-Chip Program/Data RAM

This memory is software configurable as program and/or data memory space. Code can be booted from an off-chip, nonvolatile memory and then executed at full speed, once it is loaded into this RAM.

#### • On-Chip Memory Security

The 'C50 has a maskable option to protect the contents of on-chip memories. When the related bit is set, no externally originating instruction can access the on-chip memory spaces.

#### • 16 Address-Mapped Software Wait-State Generator

The device incorporates a software wait-state logic for interfacing with slower off-chip memory and I/O devices. This circuit consists of 16 wait-state generating circuits and is user programmable to operate 0, 1, 2, 3, or 7 wait states. For off-chip memory access, these wait state generators can be mapped on 16K-word boundaries in program memory, data memory, and to the I/O ports.

#### User-Maskable Interrupts

The 'C50 has four external-interrupt lines. These lines are internally latched so that asynchronous interrupt operations can be performed by the DSP. Also the device possesses five internal interrupts: the timer interrupt, TINT, and four serial port interrupts.

#### • 64K Parallel I/O Ports

The 'C50 has a total of 64K I/O ports, sixteen of which are memory-mapped in data memory space. These ports can be addressed by the IN instruction or the OUT instruction. The memory-mapped I/O ports can be accessed with any instruction that reads or writes data memory.

#### • 2 Serial I/O Ports

The two high-speed serial ports are capable of operating at up to one-fourth the machine cycle rate (CLKOUT1). One of the two circuits is a synchronous, full-duplex serial port. Its transmitter and receiver are double buffered and

individually controlled by maskable, external interrupt signals. Data is framed either as bytes or as words. The second circuit is a full-duplex serial port that can be configured either for synchronous or for time-division multiple (TDM) access operations.

#### Hardware Timer

The on-chip timer consists of a 16-bit counter and a 4-bit prescaler. This timer clocks between one-half and one-thirty-second the machine rate, depending upon the programmable divide-down ratio. The timer can be stopped, restarted, reset, or disabled by specific status bits.

From the list of key features, the serial port and the hardware timer are the two on-chip peripherals that are mainly used in this application. Their block diagrams and operation are, therefore, explained in more detail in the following sections.

#### The DSP Serial Port 4.2

The serial port provides communication with serial devices such as codecs and serial ADCs. Receive and transmit operations are double-buffered, thus allowing a continuous communication stream in either 8- or 16-bit data packets.

In the internal clock mode, the maximum transmission rate for transmit and receive operations is the CPU clock divided by four or CLKOUT1 rate/4. Therefore, the maximum rate is 5 megabits/s for a 20-MHz (50 ns) device.

Two modes of operation are provided to support a wide range of applications.

- Continuous mode provides operation that requires only one FS pulse to transmit several packets at maximum frequency.

- Burst mode allows transmission of a single 16-bit word following an FS pulse.

#### 4.2.1 Signals and Registers

The serial port consists of the following six basic signals:

Transmit clock input or output. This signal clocks data from the CLKX transmit shift register (XSR) to the DX pin. The serial port can be configured for either generating an internal clock, or accepting an external clock.

> If the port is configured for generating an internal clock, CLKX becomes an output, transmitting a maximum frequency equal to one fourth of the CPU clock. If the port is configured to accept an external clock, CLKX changes to an input, receiving the external clock signal.

Transmit frame synchronization. FSX indicates the start of a FSX transmission.

> If the port is configured for generating an internal frame sync pulse, the FSX pin transmits the pulse.

> If the port is configured for accepting an external frame sync pulse, this pin receives the pulse.

- DX Serial data transmit. DX transmits serial data from the transmit shift register (XSR).

- Receive clock input. CLKR receives an external clock for clocking the CLKR data from the DR pin into the receive shift register (RSR).

- **FSR** Receive frame synchronization. FSR initiates the reception of data at the beginning of the packet.

- **DR** Serial data receive. DR receives serial data, transferring it into the receive shift register (RSR).

The serial port operates through the three memory–mapped registers SPC, DXR, and DRR and two other registers, XSR and RSR, that are not accessible but permit double-buffering capability. These five registers are listed in Table 5.

| REGISTERS | DESCRIPTION                  |

|-----------|------------------------------|

| SPC       | Serial port control register |

| DXR       | Data transmit register       |

| DRR       | Data receive register        |

| XSR       | Transmit shift register      |

| RSR       | Receive shift register       |

Table 5. Serial Port Registers

#### 4.2.2 Serial Port Operation

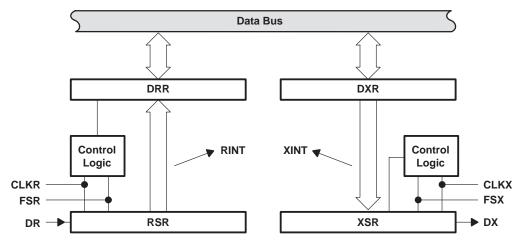

Figure 12 shows how the pins and registers are configured on the serial port and how the double buffering is implemented.

Figure 12. Serial Port Block Diagram

Transmit data is written to the DXR, while received data is read from the DRR.

A transmit is executed by writing data to the DXR, which copies the data to the XSR. The XSR manages the shifting of the data to the DX pin, thus allowing another write to DXR as soon as the DXR-to-XSR copy is completed.

Upon completion of the DXR-to-XSR copy, a 0-to-1 transition occurs on the transmit-ready bit, XRDY, in the SPC, and generates a transmit interrupt, XINT, that signals to the CPU that DXR is ready for a new word. The process is similar on the receive side.

Data from the DR pin is shifted into the RSR, which copies it to the DRR from which it may be read. Upon completion of the RSR-to-DRR copy, a 0-to-1 transition occurs on the receive ready bit, RRDY, in the SPC, and generates a receive interrupt, RINT.

Thus, the serial port is double-buffered because data can be transferred to or from DXR or DRR while another transmit or receive is being performed.

In burst mode, the frame sync pulse synchronizes the transfer timing as described in section 4.2.4 transmit and receive operations in burst mode.

#### 4.2.3 Serial Port Configuration

While the data registers are mainly responsible for shifting and buffering data, the SPC configures the entire serial port and is therefore the most important register used in the interface programs. Figure 13 shows the 16-bit memory-mapped SPC. Some of the bits are read-only while others are read/write.

| 15   | 14   | 13      | 12       | 11   | 10   | 9   | 8   | 7    | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|------|------|---------|----------|------|------|-----|-----|------|------|-----|-----|-----|-----|-----|-----|

| FREE | SOFT | RSRFULL | XSREMPTY | XRDY | RRDY | IN1 | IN0 | RRST | XRST | тхм | мсм | FSM | FO  | DLB | RES |

| R/W  | R/W  | R       | R        | R    | R    | R   | R   | R/W  | R/W  | R/W | R/W | R/W | R/W | R/W | R   |

#### Figure 13. Serial Port Control Register

Table 6 gives an overview of the bit definition of the SPC. Only the bits which are important to this application are explained. For detailed information on the bit functions refer to the TMS320C5x User's Guide.

| BIT      | NAME         | FUNCTION                                                                                                                                                                                                                   |

|----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | Reserved     | Always read as zero.                                                                                                                                                                                                       |

| 1        | DLB          | The digital loop-back mode bit allows to connect the transmitter output (DX and FSX) to the receiver input (DR and FSR). (This bit is not used in the application and set to zero.)                                        |

| 2        | FO           | The format bit specifies the word length of the transmitter and receiver.<br>FO = 0, word length is 16 bit<br>FO = 1, word length is 8 bit                                                                                 |

| 3        | FSM          | The frame synch mode bit specifies when a frame sync pulse is needed.<br>FSM = 1, burst mode is selected (an FS-pulse is used for each word)<br>FSM = 0, continuous Mode is selected (only one start pulse is required)    |

| 4        | MCM          | The clock mode bit specifies the clock source for CLKX.<br>MCM = 1, on-chip clock source is used with CLKX = 1/4 CLKOUT1<br>MCM = 0, external clock source is chosen                                                       |

| 5        | ТХМ          | The transmit mode bit specifies the source for FSX-pulse generation<br>TXM = 1, FSX is generated on–chip and synchronized to CLKX<br>TXM = 0, FSX needs to be applied from extern                                          |

| 6<br>7   | XRST<br>RRST | The transmit and receive reset signals activate and deactivate the transmitter and receiver of the serial port.<br>XRST/ RRST = 1, transmitter and receiver are active<br>XRST/ RRST = 0, activity halts                   |

| 8<br>9   | IN0<br>IN1   | The input 0 bit and input 1 bit reflect the levels of the CLKX and CLKX pins. IN0 and IN1 are read only bits.                                                                                                              |

| 10<br>11 | RRDY<br>XRDY | The receive and transmit ready bits. Upon the completion of a RSR–to–DRR copy or a DXR-to-XSR copy, these bits perform a 0–1 transition, indicating a receive interrupt (RINT or a transmit interrupt (XINT) respectively. |

| 12       | XSREMPTY     | The transmit shift register empty flag indicates whether the transmitter has experienced underflow. XSREMPTY is a read only bit.                                                                                           |

#### Table 6. Serial Port Control Register Bits Summary (Continued)

| BIT | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                  |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13  | RSRFULL | The receive shift register full flag indicates whether the receiver has experienced overrun. RSRFULL is a read only bit.                                                                                                                                                                                                  |

| 14  | SOFT    | The SOFT bit is an emulation bit that aborts transmission when a breakpoint is encountered in the high-level language debugger. It is enabled when the FREE bit is 0.<br>SOFT = 1, stop after word completion<br>SOFT = 0, immediate stop<br>(This bit is effective only in emulation mode, otherwise it is set to zero). |

| 15  | FREE    | The FREE bit selects the free run of CLKX.<br>FREE = 1, CLKX runs free<br>FREE = 0, STOP bit is enabled<br>(This bit is effective only in emulation mode, otherwise it is set to zero).                                                                                                                                   |

When interfacing to the TLV1544/48 ADC, the serial port of the TMS320C50 DSP must be configured as shown in Table 7.

#### Table 7. SPC Configuration for Interfacing to the TLV1544/48 ADC

| REQUIRED CONFIGURATION                                                                                                                                 | AFFECTED BITS   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| The DSP needs to be set-up as the master device, generating the necessary frame sync pulse to start a data transfer.                                   | TXM = 1         |

| Because of serial port inactivity during the conversion process of the ADC, the serial port must operate in burst mode.                                | FSM = 1         |

| The communication between ADC and DSP must use the 16-bit word format to support the 10-bit format of the ADC conversion result.                       | FO = 0          |

| When the ADC operates at 5 V, the DSP on-chip clock source can be selected to provide CLKX as the data transfer clock to the I/O CLK input of the ADC. | MCM = 1         |

| When the ADC operates at 2.7 V, the CLKX pin of the DSP needs to change to an input, to receive the clock signal from the timer output, TOUT.          | MCM = 0         |

| When the SPC is to be modified to reconfigure the serial port, transmitter and receiver need to be reset.                                              | XRST / RRST = 0 |

| After the modification is complete, transmitter and receiver need to be activated.                                                                     | XRST / RRST = 1 |

With the exception of the MCM bit, which needs to comply with the specific ADC clock requirements at 5-V and 2.7-V supply, the remaining bits of the SPC stay the same.

When reconfiguring the SPC, two instructions are required. The first instruction resets the transmitter and receiver and configures the SPC. The second instruction reactivates the transmitter and receiver.

Figures 14 and 15 show the binary format and the hex code of the assembler instructions used to configure and to activate the serial port.

|                   |                     | FREE | SOFT | RSRFULL | XSREMPTY | XRDY | RRDY | IN1 | IN0 | RRST | XRST | TXM | MCM | FSM | FO | DLB | RES |

|-------------------|---------------------|------|------|---------|----------|------|------|-----|-----|------|------|-----|-----|-----|----|-----|-----|

|                   |                     | 0    | 0    | 0       | 0        | 0    | 0    | 0   | 0   | 0    | 0    | 1   | 1   | 1   | 0  | 0   | 0   |

| Configure<br>Port | SPLK<br>#0038h, SPC | 0    |      |         | 0        |      |      | 3   |     |      |      | 8   |     |     |    |     |     |

|                   |                     | 0    | 0    | 0       | 0        | 0    | 0    | 0   | 0   | 1    | 1    | 1   | 1   | 1   | 0  | 0   | 0   |

| Activate Port     | SPLK<br>#00F8h, SPC | 0    |      |         | 0        |      |      | F   |     |      |      | 8   |     |     |    |     |     |

Figure 14. Configuring and Activating the Serial Port for 5-V Operation of the ADC

|                   |                     | FREE | SOFT | RSRFULL | XSREMPTY | XRDY | RRDY | IN1 | IN0 | RRST | XRST | TXM | MCM | FSM | FO | DLB | RES |

|-------------------|---------------------|------|------|---------|----------|------|------|-----|-----|------|------|-----|-----|-----|----|-----|-----|

|                   |                     | 0    | 0    | 0       | 0        | 0    | 0    | 0   | 0   | 0    | 0    | 1   | 0   | 1   | 0  | 0   | 0   |

| Configure<br>Port | SPLK<br>#0028h, SPC | 0    |      | 0       |          |      | 2    |     |     | 8    |      |     |     |     |    |     |     |

|                   |                     | 0    | 0    | 0       | 0        | 0    | 0    | 0   | 0   | 1    | 1    | 1   | 0   | 1   | 0  | 0   | 0   |

| Activate<br>Port  | SPLK<br>#00E8h, SPC | 0    |      | 0       |          |      | E    |     |     |      | 8    |     |     |     |    |     |     |

Figure 15. Configuring and Activating the Serial Port for 2.7-V Operation of the ADC

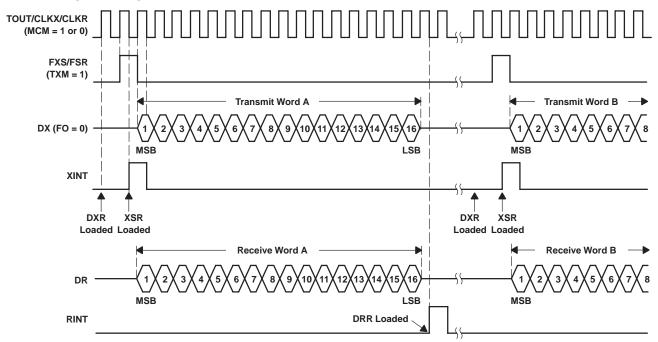

#### 4.2.4 Transmit and Receive Operations in Burst Mode

In burst mode operation, there is a period of serial port inactivity between packet transmits. Therefore each data packet needs to be marked by a frame sync pulse.

In transmit direction, after a write to DXR, a FSX pulse is generated on the next rising edge of CLKX. On the next falling edge of CLKX, XSR is loaded with the value from DXR. XRDY goes high, generating a transmit interrupt, XINT. On the next rising edge of the CLKX cycle, the first data bit (MSB first) is driven on the DX pin. With the fall of the frame sync pulse, the remaining bits are shifted out. When all bits are transferred, the DX pin enters the high-impedance state.

In receive direction, the shifting into RSR begins on the falling edge of the CLKX cycle after the FX has gone low. After all bits have been received, the content of the RSR is transferred to the DRR on the falling edge of CLKX. RRDY goes high, generating a receive interrupt, RINT.

Figure 16. Transmit and Receive Operation in Burst Mode

#### 4.3 The Hardware Timer

The second on-chip peripheral used in this application is the hardware timer. When the ADC operates at 3V or less, the timer serves as the data clock source, providing the necessary low clock rate of 2 MHz.

In applications where a slow data clock is not required, the timer can be programmed as an EOC indicator.

#### 4.3.1 Timer Operation

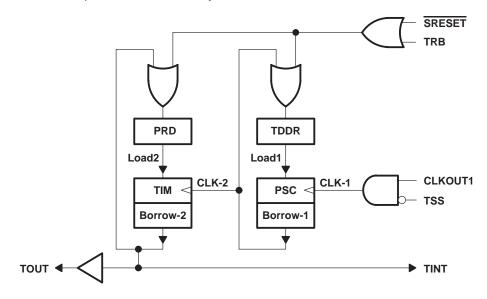

The hardware timer is a fully programmable down counter. It can be stopped, restarted, reset, or disabled by specific status bits. The timer consists of a 16-bit main counter, TIM, and a 4-bit prescaler counter, PSC.

Figure 17 shows the block diagram of the timer. Each counter is loaded by a preceding register. The PCS is loaded by the timer divide-down register, TDDR, and the TIM is loaded by the period register, PRD.

When the PSC decrements to zero, a borrow-1 signal is generated on the next CLK-1 cycle (with the CLK-1 being identical to the CLKOUT1 cycle). At that time the value of the TDDR is loaded into the PSC, and the TIM decrements by one.

Similarly, when the TIM decrements to zero, a borrow-2 signal is generated on the next CLK-2 cycle (with CLK-2 being identical to the borrow-1 signal). This time, both counters are reloaded. The value of the PRD is loaded into the TIM, and the content of the TDDR is loaded into the PSC. In addition, the borrow-2 pulse is sent as a TOUT-pulse to the external timer output pin, TOUT, and as a timer interrupt, TINT, to the CPU.

The TINT request sets the TINT flag in the interrupt flag register, IFR, and can be masked or unmasked in the interrupt mask register, IMR.

The duration of a borrow-2 pulse at TOUT is equal to that of a CLKOUT1 cycle.

The timing diagram in Figure 18 gives a typical sequence of events for the two timer values, PSC = 4 and TIM = 2.

- An initial load-pulse, at Load1 and Load2, copies the TDDR value of 4 into the PSC, and the PRD value of 2 into the TIM.

- The PSC decrements on each succeeding CLK-1 cycle (CLKOUT1) until it reaches zero.

- On the next CLK-1 cycle, a borrow-1 is generated. The TDDR loads the new divide-down count into the PSC, and the TIM decrements by one.

- The PSC and the TIM continue to decrement in the same way until the TIM decrements to zero.

- On the next CLK-2 cycle, a borrow-2 pulse is generated. A timer interrupt, TINT, is sent to the CPU, and the borrow-2 pulse is sent to the TOUT-pin. Both counters, TIM and PSC, are reloaded by their corresponding registers, PRD and TDDR, and the entire sequence can be repeated.

The TIM decrements by one, every (TDDR + 1) CLKOUT1 cycles. When either one of the two period registers, or both registers, PRD and TDDR, are nonzero, the interrupt rate is defined by equation 5 and the interrupt interval is given by equation 6.

$$TINT[MHz] = \frac{CLKOUT1[MHz]}{(TDDR + 1) \times (PRD + 1)}$$

(6)

$$t_{TINT} = t_C \times (PRD + 1) \times (TDDR + 1)$$

<sup>(7)</sup>

For the example in Figure 18, the TINT rate results in:

$$TINT[MHz] = \frac{CLKOUT1[MHz]}{(4+1) \times (2+1)} = \frac{CLKOUT1[MHz]}{15}$$

That means the CPU clock, CLKOUT1, is divided by 15, or every 15 CPU clock cycles, a TINT pulse is generated.

**NOTE:** When both registers, PRD and TDR, are zero, the timer interrupt rate automatically sets to CLKOUT1/2.

Figure 17. Timer Block Diagram

Figure 18. Timing Diagram for TDDR = 4 and PRD = 2

#### 4.3.2 Programming the Timer

The on-chip timer is configured by the period register, PRD, and the timer control register, TCR. The PRD is a 16-bit, memory-mapped register that specifies the initial period of the timer. The TCR is a 16-bit, memory-mapped register that contains the status and control bits to operate the timer. Figure 19 shows the status and control bits within the TCR, and Table 8 gives an overview of the bit definition of the TCR.

| 15 | 14 | 13     | 12 | 11   | 10   | 9 | 8 | 7  | 6 | 5   | 4   | 3 | 2 | 1   | 0 |

|----|----|--------|----|------|------|---|---|----|---|-----|-----|---|---|-----|---|

|    | Re | served |    | Soft | Free |   | Р | SC |   | TRB | RSS |   | т | DDR |   |

| Figure 19. | Timer | Control | Register |

|------------|-------|---------|----------|

|------------|-------|---------|----------|

| BIT     | NAME     | FUNCTION                                                                                                                                                                                                                                                                                                                                             |

|---------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-3     | TDDR     | The timer divide-down register bits define the divide-down ratio for the timer.                                                                                                                                                                                                                                                                      |

| 4       | TSS      | The timer stop status bit starts or stops the timer.<br>TSS = 0, Timer starts<br>TSS = 1, Timer stops                                                                                                                                                                                                                                                |

| 5       | TRB      | The timer reload bit resets the timer. When the TRB is set, the TIM is reloaded with the value in the PRD, and the PSC is loaded with the value in the TDDR. (This bit is always read as zero).                                                                                                                                                      |

| 6 – 9   | PSC      | The prescaler counter bits hold the current prescale count for the timer. The PSC is reloaded with the contents of the TDDR one cycle after it has reached zero, or whenever the TRB is et by software.                                                                                                                                              |

| 10      | FREE     | The FREE bit selects the free run of the timer.<br>FREE = 1, Timer runs free<br>FREE = 0, STOP bit is enabled<br>(This bit is effective only in emulation mode, otherwise it is set to zero).                                                                                                                                                        |

| 11      | SOFT     | The SOFT bit is an emulation bit that aborts transmission when a breakpoint is encountered in the high–level language debugger. It is enabled when the FREE bit is 0.<br>SOFT = 1, Timer stops after completion of transmission<br>SOFT = 0, Timer stops immediately<br>(This bit is effective only in emulation mode, otherwise it is set to zero). |

| 12 – 15 | Reserved | Always read as zero.                                                                                                                                                                                                                                                                                                                                 |

Table 8. Timer Control Register Bits Summary

When programming the timer interrupt rate using equation 6, it is common to specify the initial timer period within the PRD and to keep the TDDR value within the TCR at zero. By programming the PRD from 0 to 65536, it is possible to generate timer interrupts, TINT, every 2 to 65536 CPU cycles. If a lower interrupt rate is required, an additional divide-down value can be programmed into the TDDR that extends the interrupt interval by the desired factor.

In the software description in Section 5, Program 1 uses the on-chip timer as an end-of-conversion indicator for the ADC. Thus the timer has to generate only one interrupt, TINT, for the length of 10  $\mu$ s (which is the maximum conversion time of the ADC). With a CPU clock of 20 MHz, or a clock cycle of t<sub>C</sub> = 50 ns, the interrupt period needs to be 200 CPU cycles.

Solving equation 7 for PRD and keeping TDDR = 0, results in:

$$PRD = \frac{t_{TINT}}{t_C \times (TDDR + 1)} - 1 = \frac{10 \ \mu s}{50 \ ns \times (0 + 1)} - 1 = 199$$

The following instructions configure the timer in program 1:

SPLK #199, PRD ; load timer period of 10  $\mu$ s into PRD SPLK #0030h, TCR ; set TRB = 1 to reload PRD/TDDR and set TSS = 1 to stop timer SPLK #0008h, IFR ; clear any pending timer interrupt (TINT)

Program 2 uses the on-chip timer as a programmable clock generator to generate a 2-MHz interface clock. With a CPU clock of 20 MHz and an interrupt rate of 2 MHz, the PRD value needs to be:

$$PRD = \frac{CLOCKOUT1}{TINT-rate \times (TDDR + 1)} - 1 = \frac{20 MHz}{2 MHz \times (0 + 1)} - 1 = 9$$

The following instructions configure the timer in program 2:

SPLK #9, PRD ; load timer period of 10  $\mu s$  into PRD SPLK #0020h, TCR ; set TRB = 1 to reload PRD/TDDR and set TSS = 0 to run timer

**NOTE:** Since the timer operates as a clock generator, the timer interrupt, TINT, is masked for the entire program. Therefore, an additional instruction to clear any pending interrupts is not required.

### 5 Software Description

The interface software consists of three C-callable assembler programs and three corresponding C-programs. The user can specify certain data transfer parameters—such as the analog input channel, the conversion mode, the memory start address, and the number of samples—through the global variables of the .C file without modifying the corresponding assembler program.

When a specific .C interface routine is called, the global variables in the specific C file are loaded into the local variables of the assembler program.

Table 9 shows the global and local variables and their corresponding files.

| PROGRAM             | TYPE   | VARIABLE     | DESCRIPTION                                          |

|---------------------|--------|--------------|------------------------------------------------------|

|                     | Global | _Samples     | User defined number of samples to be acquired        |

| All C–files         | Global | _MemStart    | User defined memory pointer start                    |

|                     | Global | _Channel     | User defined channel number to be sampled            |

| C1544T.C only       | Global | _ControlMode | User defined conversion mode                         |

| C1544C.C only       | Global | _Vcc         | User defined ADC voltage supply                      |

|                     | Local  | ADWORD       | ADC Control word                                     |

|                     | Local  | ADCOUNT      | Sample counter                                       |

| All Assembler files | Local  | ADMEM        | Memory pointer                                       |

| All Assembler mes   | Local  | RINT_COUNT   | Number of Receive Interrupts                         |

|                     | Local  | END_BIT      | End-of-program bit                                   |

|                     | Local  | TEMP         | Temporary register for control mode and receive data |

Table 9. Local and Global Variables and Corresponding Programs

Each of the three assembler programs executes the following steps:

- 1. Initialize the DSP and the serial port

- 2. Load the user defined values

- 3. Activate and initialize the ADC

- 4. Acquire the specified number of data

- 5. Disable the ADC

- 6. Return to the C program

The above sequence shows that the assembler routines are used solely to acquire data. It also shows that every time the interface routine is called, the ADC is enabled for the data acquisition process and disabled before the routine returns to the C program. Therefore neither of the self-test modes nor the power-down instruction, which are available in the list of TLV1544 control words, are used in these routines.

All programs are differentiated by the use of the on-chip timer as shown in Table 10.

- Program 1 uses the timer as an interrupt source and is called C1544**TIN**.ASM.

- Program 2 uses the timer as a clock generator and is called C1544**CLK**.ASM. The end-of-conversion is detected by using the EOC output of the ADC.

- Program 3 is similar to Program 2, but uses a delay loop, which waits for the ADC maximum conversion time to pass. This wait-loop executes a specified

26

number of no-operation-instructions, NOPs, to generate the necessary delay, hence the program name is C1544**NOP**.ASM.

| TIMER USED AS         |                       |                               |  |  |  |  |  |  |  |

|-----------------------|-----------------------|-------------------------------|--|--|--|--|--|--|--|

| Interrupt source      | Clock source,         | Clock source,                 |  |  |  |  |  |  |  |

| to detect EOC         | EOC used from ADC     | EOC indicated after wait-loop |  |  |  |  |  |  |  |

| C1544 <b>TIN</b> .asm | C1544 <b>CLK</b> .asm | C1544 <b>NOP</b> .asm         |  |  |  |  |  |  |  |

| (Program–1)           | (Program–2)           | (Program–3)                   |  |  |  |  |  |  |  |

| C1544 <b>T</b> .c     | C1544 <b>C</b> .c     | C1544 <b>N</b> .c             |  |  |  |  |  |  |  |

Table 10. Timer Application and Corresponding Filenames

The following sections explain the main assembler program in detail. For a review of the individual file listings, refer to Appendix A for Program-1, Appendix B for Program-2 and Appendix C for Program-3.

#### **5.1 Program-1** (*Filename: C1544TIN.asm* ⇒ *Timer as Interrupt-Source*)

Program 1 supports the glueless DSP-to-ADC interface in Figure 20. The serial port is programmed for burst-mode operation. The interface clock, CLKX (5 MHz), and the frame-sync signal, FS, are generated on chip. The on-chip timer is programmed to generate an interrupt, TINT, after the maximum conversion time of the ADC (10  $\mu$ s) has elapsed.

#### Figure 20. Timer Interrupt, TINT, Indicates EOC in a Glueless Interface

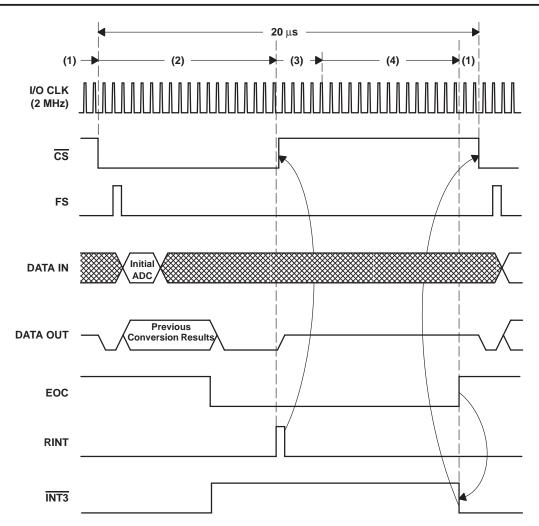

The timing diagram in Figure 21 divides a data transfer sequence into four steps:

- 1. The DSP activates the ADC by taking the  $\overline{\text{CS}}$  low. Then the control word to initialize the ADC is loaded into the DSP serial port.

- 2. The actual data transfer happens. While the DSP sends control data to configure the ADC operation mode, the ADC transmits conversion results to the serial port receiver.

- On the 16<sup>th</sup> clock cycle of I/O CLK (CLKX) after FS has gone low, a receive interrupt, RINT, is generated automatically. The following interrupt service routine, RINT-ISR, disables the ADC and starts the on-chip timer. Then it stores the received data into memory and returns from interrupt to idle mode.

- 4. The CPU continues idling during the entire conversion time of the ADC.

After the timer period has elapsed, a timer interrupt, TINT, is generated. The following interrupt service routine, TINT-ISR, stops the timer and loads the latest ADC control word into the serial port to prepare for a new data transfer.

#### Figure 21. Data Transfer Sequence When Using TINT and ADC in Fast Conversion Mode

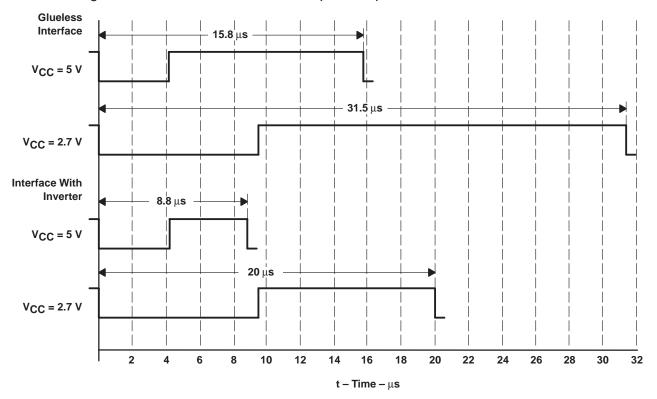

One data transfer takes 15.8 µs when the ADC operates in fast conversion mode, and 30.8 µs when in slow conversion mode.

### 5.1.1 Assembler Program-1 Description

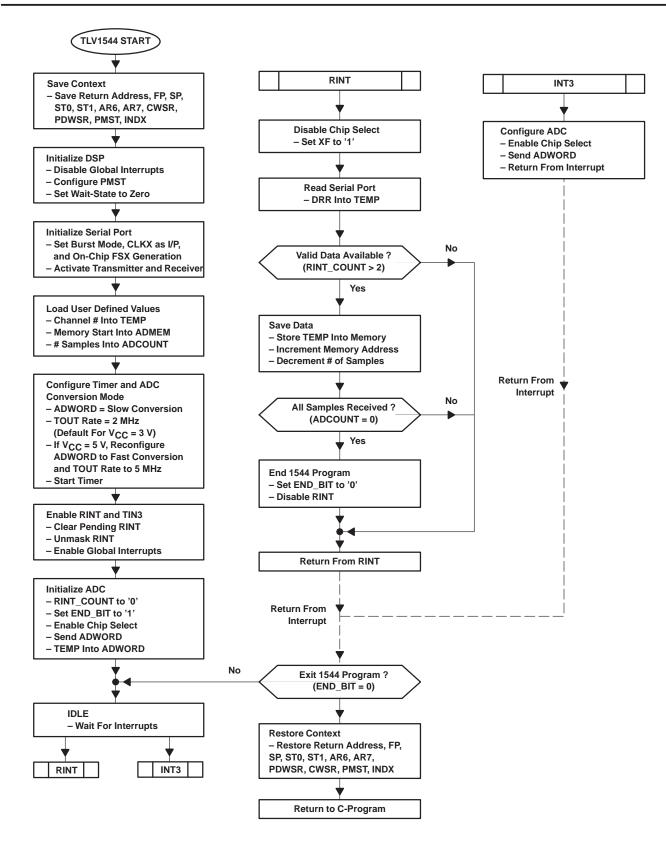

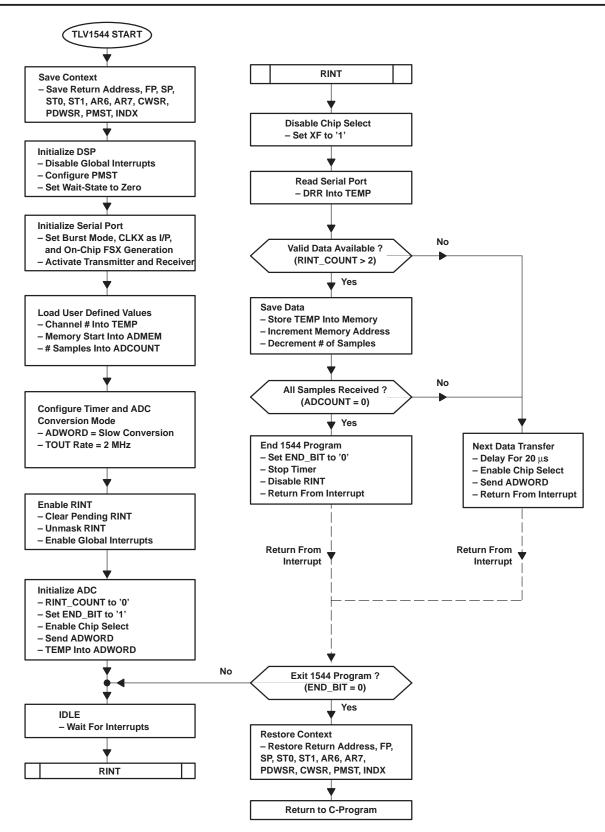

Following the flowchart in Figure 22, this section explains the assembler program in detail.

NOTE: Each task box in the flowchart appears as a header in the assembler program listing in Appendix A.

### TLV1544START

The program starts with the call of the main routine C1544TIN from the C program. At first, all previously used pointers and registers are saved. These include the following registers:

- The frame and the stack pointer, FP and SP •

- The status registers, ST0 and ST1 •

- The auxiliary registers, AR6 and AR7

- The wait-state registers, PDWSR and CWSR •

- The processor mode status register PMST

- The index register INDX

- 28 SLAA025A

During the DSP initialization all interrupts are disabled, the PMST is updated, and the wait states are set to zero. Then the serial port is configured for burst-mode operation. The FS signal and the CLKX are programmed to be generated on-chip. Finally the transmitter and receiver stages are activated.

Now, the user defined values (global variables in the C program) are loaded into the local variables of the assembler routine. The channel number is stored into TEMP. The memory start address is loaded into ADMEM, and the number of samples to be acquired is saved into ADCOUNT. The control mode, which can be fast or slow conversion is stored into ADWORD.

The following timer configuration writes a default period of 10  $\mu$ s into the period register (PRD). Depending upon whether the user selected slow or fast conversion, the content of PRD is either overwritten to 25  $\mu$ s, or keeps its default value. After that, the timer start/stop bit (TSS), in the timer control register (TCR), is set to 1 to halt the timer. Both DSP internal interrupts, RINT and TINT, are now enabled.

Before the initialization of the ADC begins, the variable RINT\_COUNT is set to 0. RINT\_COUNT specifies the number of receive interrupts that must occur before the ADC can provide valid conversion results.

The local variable, END\_BIT, which defines the end of the entire program, is set to 1. The general output port (XF), of the DSP is driven low to enable the ADC through the chip-select pin,  $\overline{CS}$ .

The variable ADWORD, which contains the conversion mode, is then copied into the serial port data transmit register (DXR), and sent to the ADC. Subsequently the content of TEMP, which specifies the channel number, is loaded into ADWORD.

The CPU then resides in idle mode and waits for a receive interrupt (RINT), to occur.

Figure 22. Flowchart of C1544IN.asm (Timer as Interrupt Source)

SLAA025A

#### RINT (Receive Interrupt Routine)

With the initialization of the ADC into fast-conversion mode, the DSP starts the first data transfer of control data in a 16-bit data frame. Therefore, upon the 16<sup>th</sup> clock cycle of CLKX, RINT is generated that forces the CPU to execute the RINT service routine (RINT-ISR). At the beginning of the RINT routine, the XF output of the DSP is taken high, disabling the ADC. Then the TSS bit in the TCR is set to zero to start the timer. After that the content of the data receive register (DRR), is stored into the temporary (TEMP) register.

The following decision box investigates the receive data for validity by checking the content of RINT\_COUNT for a value higher than two. Since it takes two data transfers to configure the ADC completely—one to specify the conversion mode and a second one to select the analog input channel—the conversion results from the ADC are invalid for both transfers. With each data transfer generating a receive interrupt, the number of occurring RINTs (which is stored in RINT\_COUNT) must be three to indicate that valid data are available.

If no valid data are available, the CPU leaves the RINT-ISR to configure the ADC channel number via the timer interrupt service routine (TINT-ISR).

If valid data are available, the latest receive data, stored in TEMP, are saved into memory. Subsequently the memory address is increased by incrementing the content of ADMEM, and the number of samples is decreased by decrementing the content of ADCOUNT.

A second decision box checks whether all samples have been received. If all samples were received, the END\_BIT is set to zero and both interrupts, RINT and TINT, are disabled. The program leaves the RINT-ISR and returns to the C program through the EXIT routine.

If all samples were not received, the CPU returns from the RINT-ISR into the idle mode and waits for a timer interrupt to occur.

#### TINT (Timer Interrupt Routine)

The TINT routine loads the serial port with transmit data and initiates a new data transfer. Once the timer period has elapsed, a timer interrupt is generated that causes the CPU to enter the TINT service routine. At the beginning the TSS is set to one, which stops the timer immediately. Then the DSP initiates a new data transfer by taking the XF output low to enable the ADC. The channel number stored in ADWORD is loaded into the serial port and sent to the ADC as the new control word. Afterwards the program returns from interrupt and the CPU resides in idle mode until the next RINT occurs.

#### Exit 1544 program ?

This decision box determines whether the entire data transfer program is terminated. As long as END-BIT is one, the CPU diverts to the idle mode to continue acquiring data. Once END\_BIT has been set to zero, all previously saved registers in the save-context box are restored. The CPU now exits the interface routine and returns to the C program.

#### **5.2 Program-2** (*Filename: C1544CLK.asm* ⇒ *Timer as Clock-Source*)

Program 2 supports the non-glueless interface in Figure 23. In this application the ADC operates from a 2.7 V supply and is configured for slow conversion mode. The required transfer clock at I/O CLK is 2 MHz. Since the only frequency the DSP can provide at CLKX is 5 MHz (1/2 of the CPU clock), the on-chip timer is configured as a programmable clock source providing a 2-MHz clock signal at the TOUT. Although this timer configuration is required for low-volt operation of the ADC, it allows the clock rate at TOUT to be increased to 10 MHz if the ADC operates at 5.5 V. For supply voltages above 3.3 V the ADC can operate in fast conversion mode, for voltages below 3.3 V, the ADC must be operated in slow conversion mode.