# XIO1100 NAND-Tree Test

Mike Campbell

DIBU

## ABSTRACT

Checking the interconnections between integrated circuits (IC) once they have been assembled on a PCB is important in some applications. The normal method for performing this check is through using boundary scan as defined by the IEEE Std 1149.1a specification (also known as JTAG). Since boundary scan is not implemented in the XIO1100 PHY, an alternative method must be employed. The XIO1100 PHY has a NAND-tree test feature that can be used. This document discusses the NAND-tree test feature, explains what it does, and describes how to use it.

## Contents

| 1 | Introduction                                | 2 |

|---|---------------------------------------------|---|

| 2 | JTAG Pins                                   | 2 |

|   | NAND Tree Pin Order                         |   |

| - | Performing the NAND-Tree Test               | - |

|   | 4.1 Putting XIO1100 PHY into NAND-Tree Mode |   |

|   | 4.2 Stepping Through the NAND Tree          |   |

|   |                                             |   |

#### Figures

| Figure 1. | XIO1100 NAND | Tree | 2 |

|-----------|--------------|------|---|

|-----------|--------------|------|---|

#### Tables

| Table 1. | JTAG Pins           | 3 |

|----------|---------------------|---|

| Table 2. | NAND Tree Pin Order | 3 |

# 1 Introduction

The common method for checking the interconnections between the ICs is to use JTAG boundary scan. Since the XIO1100 PHY does not support JTAG boundary scan, a NAND-tree feature has to be employed.

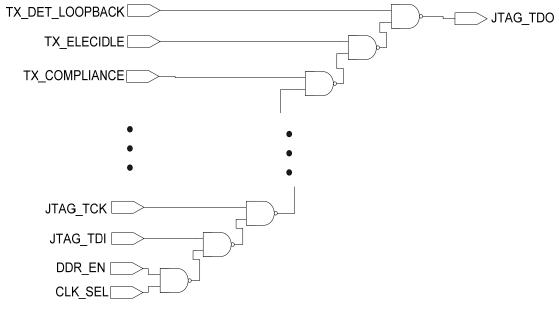

A NAND tree is exactly how it sounds: A number of nested NAND gates in which each I/O pin is an input to one NAND gate. Figure 1 illustrates a NAND tree. The output of the nested NAND gates is provided on the JTAG\_TDO pin. A NAND-tree feature does not provide 100% coverage but does allow for checking the connectivity of most I/Os on the XIO1100 PHY.

Figure 1. XIO1100 NAND Tree

# 2 JTAG Pins

In the XIO1100 datasheet, the five reserved pins are B9, A10, B10, A9, and C9. These pins should be left unconnected during normal operations except for C9 which should be tied to GND.

To use the NAND-tree mode in the XIO1100 PHY, these pins need to be connected to a JTAG controller. The function of each reserved pin is described in Table 1. The system designer should note that some of the reserved pins have internal pullup resistors. Also note that the JTAG pins in Table 1 are NOT 3.3-V tolerant. These pins are powered from the VDD\_IO supply (1.5 V or 1.8 V). See the XIO1100 datasheet for the electrical characteristics of VDD\_IO pins.

| Pin # | Description                                             |  |  |  |

|-------|---------------------------------------------------------|--|--|--|

| B9    | JTAG_TCK. This pin has a weak internal pullup resistor. |  |  |  |

| A10   | JTAG_TDI. This pin has a weak internal pullup resistor. |  |  |  |

| B10   | JTAG_TDO                                                |  |  |  |

| A9    | JTAG_TMS. This pin has a weak internal pullup resistor. |  |  |  |

| C9    | JTAG_TRST                                               |  |  |  |

## Table 1. JTAG Pins

# 3 NAND Tree Pin Order

Table 2 shows the pin order of the NAND tree. The pins must be toggled in the order listed. The result of the NAND logic can be observed on the JTAG\_TDO pin.

| Order | Pin Name        |

|-------|-----------------|

| 1     | TX_DET_LOOPBACK |

| 2     | TX_ELECIDLE     |

| 3     | TX_COMPLIANCE   |

| 4     | TX_CLK          |

| 5     | TX_DATA0        |

| 6     | TX_DATA1        |

| 7     | TX_DATA2        |

| 8     | TX_DATA3        |

| 9     | TX_DATA4        |

| 10    | TX_DATA5        |

| 11    | TX_DATA6        |

| 12    | TX_DATA7        |

| 13    | TX_DATA8        |

| 14    | TX_DATA9        |

| 15    | TX_DATA10       |

| 16    | TX_DATA11       |

| 17    | TX_DATA12       |

| 18    | TX_DATA13       |

| 19    | TX_DATA14       |

| 20    | TX_DATA15       |

| 21    | TX_DATAK0       |

| 22    | TX_DATAK1       |

| 23    | RX_DATA0        |

| 24    | RX_DATA1        |

| 25    | RX_DATA2        |

| 26    | RX_DATA3        |

| 27    | RX_DATA4        |

| 28    | RX_DATA5        |

| 29    | RX_DATA6        |

Table 2. NAND Tree Pin Order

| RX_DATA7    |

|-------------|

| RX_DATA8    |

| RX_DATA9    |

| RX_DATA10   |

| RX_DATA11   |

| RX_DATA12   |

| RX_DATA13   |

| RX_DATA14   |

| RX_DATA15   |

| RX_DATAK0   |

| RX_DATAK1   |

| RX_STATUS0  |

| RX_STATUS1  |

| RX_STATUS2  |

| RX_ELECIDLE |

| RX_POLARITY |

| RX_VALID    |

| P1_SLEEP    |

| POWERDOWN0  |

| POWERDOWN1  |

| PHYSTATUS   |

| JTAG_TCK    |

| JTAG_TDI    |

| DDR_EN      |

| CLK_SEL     |

|             |

# 4 Performing the NAND-Tree Test

## 4.1 Putting XIO1100 PHY into NAND-Tree Mode

To put the XIO1100 PHY into NAND-tree mode, software must set bit 2 in the TESTMODE register. The TESTMODE register is 32-bits in length and is located at JTAG OPCODE 0x2. The default value of this register should be 0x00000000. It is important that the software set only bit 2. Once bit 2 is set to a '1', the XIO1100 PHY is in NAND-tree mode.

## 4.2 Stepping Through the NAND Tree

Once the XIO1100 has been put into NAND-tree mode, the I/O pins listed in Table 2 should all be driven low. Once all I/O pins are low, the JTAG\_TDO pin should be high.

At this point, the logic controlling the pins listed in Table 2 can toggle the first pin from low to high and the observed JTAG\_TDO from high to low. This indicates the first pin is connected properly.

The logic controlling the pins should then leave the first pin high and then toggle the second pin from low to high. The JTAG\_TDO pin should go from low to high. This indicates that the second pin is connected properly.

Pins 1 and 2 should be left high and then the logic should toggle pin 3 from low to high. The JTAG\_TDO pin should go from a high to low. This indicates that the third pin is connected properly.

The logic should continue this sequence for every pin listed in Table 2. Every pin in Table 2 that causes JTAG\_TDO to toggle high-to-low or low-to-high indicates a good connection. If JTAG\_TDO fails to toggle when a pin in Table 2 toggles from low to high, the pin has a bad connection.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products           |                        | Applications       |                           |

|--------------------|------------------------|--------------------|---------------------------|

| Amplifiers         | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters    | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface          | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic              | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt         | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers   | microcontroller.ti.com | Security           | www.ti.com/security       |

| RFID               | www.ti-rfid.com        | Telephony          | www.ti.com/telephony      |

| Low Power Wireless | www.ti.com/lpw         | Video & Imaging    | www.ti.com/video          |

|                    |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2007, Texas Instruments Incorporated