# **Designing Fast Response Synchronous Buck Regulators Using the TPS5210**

March 1999

**Mixed-Signal Products**

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated

# Contents

| 1 | 1.1                                                                                                                        | uction                                                                                                                                                                                                                                                                                                                                                                                                                      | . 2                                                                                                                                                                                                                                |

|---|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 1.2                                                                                                                        | Hysteretic Control Operation                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                    |

| 2 |                                                                                                                            | 210 Operation Overview                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                    |

| 3 |                                                                                                                            | ple Design Circuit                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                    |

|   | 3.1                                                                                                                        | Measured Performance                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                    |

|   |                                                                                                                            | 3.1.1 Line and Load Regulation                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                    |

|   |                                                                                                                            | 3.1.2 Efficiency      3.1.3 Transient Load Response                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                    |

|   |                                                                                                                            | 3.1.4 Overcurrent Protection                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                    |

|   |                                                                                                                            | 3.1.5 Power-Up Performance                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                    |

| 4 | Exam                                                                                                                       | ple Circuit Design Procedure                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                    |

| - | 4.1                                                                                                                        | Duty Cycle Estimate                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                    |

|   | 4.2                                                                                                                        | Input Capacitance                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                    |

|   | 4.3                                                                                                                        | Output Filter Design                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                    |

|   |                                                                                                                            | 4.3.1 Output Capacitance                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                    |

|   |                                                                                                                            | 4.3.2 Output Inductance                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                    |

|   | 4.4                                                                                                                        | Switching Frequency Analysis                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                    |

|   |                                                                                                                            | <ul><li>4.4.1 Output Ripple</li></ul>                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                    |

|   | 4.5                                                                                                                        | Power MOSFET Selection                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                    |

|   | 4.5                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                             | 24                                                                                                                                                                                                                                 |

| 5 |                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                    |

| 5 | TPS52                                                                                                                      | 210 Functions                                                                                                                                                                                                                                                                                                                                                                                                               | 26                                                                                                                                                                                                                                 |

| 5 |                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>26</b><br>27                                                                                                                                                                                                                    |

| 5 | <b>TPS52</b><br>5.1                                                                                                        | 210 Functions                                                                                                                                                                                                                                                                                                                                                                                                               | <b>26</b><br>27<br>28<br>28                                                                                                                                                                                                        |

| 5 | <b>TPS52</b><br>5.1<br>5.2<br>5.3<br>5.4                                                                                   | 210 Functions<br>V <sub>CC</sub> Undervoltage Lockout<br>Inhibit<br>Slowstart Design<br>Hysteresis Setting                                                                                                                                                                                                                                                                                                                  | <b>26</b><br>27<br>28<br>28<br>29                                                                                                                                                                                                  |

| 5 | <b>TPS52</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5                                                                            | 210 Functions<br>V <sub>CC</sub> Undervoltage Lockout<br>Inhibit<br>Slowstart Design<br>Hysteresis Setting<br>Noise Suppression                                                                                                                                                                                                                                                                                             | <b>26</b><br>27<br>28<br>28<br>29<br>31                                                                                                                                                                                            |

| 5 | <b>TPS52</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                                                                     | 210 Functions<br>V <sub>CC</sub> Undervoltage Lockout<br>Inhibit<br>Slowstart Design<br>Hysteresis Setting<br>Noise Suppression<br>Overcurrent Protection                                                                                                                                                                                                                                                                   | <b>26</b><br>27<br>28<br>28<br>29<br>31<br>32                                                                                                                                                                                      |

| 5 | <b>TPS52</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7                                                              | 210 Functions<br>V <sub>CC</sub> Undervoltage Lockout<br>Inhibit<br>Slowstart Design<br>Hysteresis Setting<br>Noise Suppression<br>Overcurrent Protection<br>Overvoltage Protection                                                                                                                                                                                                                                         | <b>26</b><br>27<br>28<br>28<br>29<br>31<br>32<br>35                                                                                                                                                                                |

| 5 | <b>TPS52</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                                                                     | 210 Functions         V <sub>CC</sub> Undervoltage Lockout         Inhibit         Slowstart Design         Hysteresis Setting         Noise Suppression         Overcurrent Protection         Overvoltage Protection         Droop Compensation                                                                                                                                                                           | 26<br>27<br>28<br>29<br>31<br>32<br>35<br>36                                                                                                                                                                                       |

| 5 | <b>TPS52</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8                                                       | Punctions         V <sub>CC</sub> Undervoltage Lockout         Inhibit         Slowstart Design         Hysteresis Setting         Noise Suppression         Overcurrent Protection         Overvoltage Protection         Droop Compensation         Power Good                                                                                                                                                            | 26<br>27<br>28<br>29<br>31<br>32<br>35<br>36<br>36                                                                                                                                                                                 |

| 5 | <b>TPS52</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9                                                | 210 Functions         V <sub>CC</sub> Undervoltage Lockout         Inhibit         Slowstart Design         Hysteresis Setting         Noise Suppression         Overcurrent Protection         Overvoltage Protection         Droop Compensation         Power Good         Bias         Gate Drivers                                                                                                                      | 26<br>27<br>28<br>29<br>31<br>32<br>35<br>36<br>36<br>36<br>36<br>37                                                                                                                                                               |

| 5 | <b>TPS52</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10                                        | 210 Functions         V <sub>CC</sub> Undervoltage Lockout         Inhibit         Slowstart Design         Hysteresis Setting         Noise Suppression         Overcurrent Protection         Overvoltage Protection         Droop Compensation         Power Good         Bias         Gate Drivers         5.11.1                                                                                                       | 26<br>27<br>28<br>29<br>31<br>32<br>35<br>36<br>36<br>36<br>36<br>37<br>40                                                                                                                                                         |

| 5 | <b>TPS52</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10                                        | 210 Functions         V <sub>CC</sub> Undervoltage Lockout         Inhibit         Slowstart Design         Hysteresis Setting         Noise Suppression         Overcurrent Protection         Overvoltage Protection         Droop Compensation         Power Good         Bias         Gate Drivers         5.11.1         Low-Side Driver Controls         5.11.2                                                       | 26<br>27<br>28<br>29<br>31<br>32<br>35<br>36<br>36<br>36<br>36<br>37<br>40<br>41                                                                                                                                                   |

|   | <b>TPS52</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11                                | Punctions         V <sub>CC</sub> Undervoltage Lockout         Inhibit         Slowstart Design         Hysteresis Setting         Noise Suppression         Overcurrent Protection         Overvoltage Protection         Droop Compensation         Power Good         Bias         Gate Drivers         5.11.1         Low-Side Driver Controls         5.11.3         Grounding                                         | 26<br>27<br>28<br>29<br>31<br>32<br>35<br>36<br>36<br>36<br>36<br>37<br>40<br>41<br>41                                                                                                                                             |

| 5 | <b>TPS52</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11                                | 210 Functions         V <sub>CC</sub> Undervoltage Lockout         Inhibit         Slowstart Design         Hysteresis Setting         Noise Suppression         Overcurrent Protection         Overvoltage Protection         Droop Compensation         Power Good         Bias         Gate Drivers         5.11.1         Low-Side Driver Controls         5.11.2                                                       | 26<br>27<br>28<br>29<br>31<br>32<br>35<br>36<br>36<br>36<br>36<br>37<br>40<br>41<br>41                                                                                                                                             |

|   | <b>TPS52</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11                                | Punctions         V <sub>CC</sub> Undervoltage Lockout         Inhibit         Slowstart Design         Hysteresis Setting         Noise Suppression         Overcurrent Protection         Overvoltage Protection         Droop Compensation         Power Good         Bias         Gate Drivers         5.11.1         Low-Side Driver Controls         5.11.3         Grounding                                         | <ul> <li>26</li> <li>27</li> <li>28</li> <li>29</li> <li>31</li> <li>32</li> <li>35</li> <li>36</li> <li>36</li> <li>36</li> <li>36</li> <li>36</li> <li>36</li> <li>37</li> <li>40</li> <li>41</li> <li>41</li> <li>42</li> </ul> |

| 6 | <b>TPS52</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br><b>Layou</b><br><b>Summ</b> | Punctions         V <sub>CC</sub> Undervoltage Lockout         Inhibit         Slowstart Design         Hysteresis Setting         Noise Suppression         Overcurrent Protection         Overvoltage Protection         Droop Compensation         Power Good         Bias         Gate Drivers         5.11.1         Low-Side Driver Controls         5.11.2         High-Side Driver         5.11.3         Grounding | <ul> <li>26</li> <li>27</li> <li>28</li> <li>29</li> <li>31</li> <li>32</li> <li>35</li> <li>36</li> <li>36</li> <li>37</li> <li>40</li> <li>41</li> <li>41</li> <li>42</li> <li>44</li> </ul>                                     |

# List of Figures

| 3<br>5<br>9<br>10 |

|-------------------|

| 9                 |

|                   |

| 10                |

|                   |

| 10                |

| 11                |

| 12                |

| 12                |

| 13                |

| 13                |

| 13                |

| 19                |

| 20                |

| 20                |

| 22                |

| 23                |

| 23                |

| 24                |

| 27                |

| 29                |

| 32                |

| 33                |

| 34                |

| 37                |

| 38                |

| 39                |

| 39                |

| 40                |

| 43                |

|                   |

# List of Tables

| 1 | Critical Power Stage Components | 1 | 0 |

|---|---------------------------------|---|---|

| 2 | Power Stage Design Parameters   | 1 | 4 |

# Designing Fast Response Synchronous Buck Regulators Using the TPS5210

#### ABSTRACT

This application report describes the operation and performance of a 12-V to 2-V 20-A synchronous buck regulator evaluation design using the TPS5210 Programmable Synchronous Buck Regulator Controller. Experimental data shows tight static and dynamic regulation ( $\pm$ 55 mV), fast transient response (within 1 µs), high efficiency (up to 90%), and stable operation with good noise immunity. The TPS5210 architecture is also presented describing the major functional blocks: 1% reference, fast hysteretic comparator with noise suppression, droop compensation, 30-V rating from BOOT pin to ground, 8-V/2-A gate drive with adaptive deadtime control, Vds current sensing, slowstart, OVP, powergood, UVLO, and INHIBIT. Finally, a simple mathematical description of switching frequency and output voltage for a ripple regulator is derived and presented, showing good correlation with experimental data.

## 1 Introduction

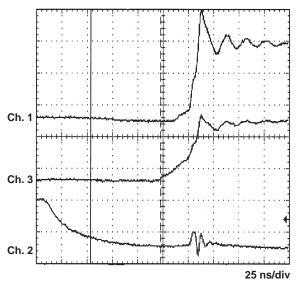

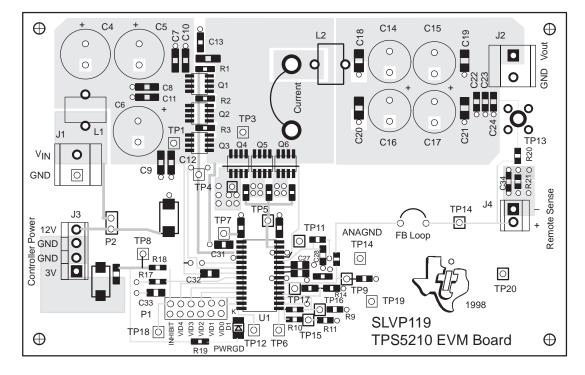

This application report describes how to design and construct a 12-V to 2-V 20-A synchronous buck regulator (example design) using a TI TPS5210 Programmable Synchronous Buck Regulator Controller (TPS5210) and appropriate external components. The example design illustrates measured performance, component selection, design considerations, and board layout guidelines.

Forthcoming workstations, driven by next-generation high-performance microprocessors, may require from 40 to 80 watts of power for the CPU alone. Although the nominal supply output voltage may be 2 V, the supply should still be capable of providing an output voltage range from 1.3 V to 3.5 V, determined by a 5-bit DAC code. Parasitic interconnect impedances between the power supply and the processor must be kept to a minimum<sup>[1]</sup> since maximum current could be anywhere from 20 A to 40 A. Load current must be supplied with up to 30 A/µs slew rate, while keeping the output voltage within tight regulation and response time tolerances.<sup>[2]</sup> Fast response synchronous buck converters controlled by the Texas Instruments TPS5210 are ideally suited for microprocessor power applications requiring fast response and precise regulation to rapidly changing loads.

Conventional regulator control techniques include fixed frequency voltage-mode, fixed frequency current-mode, variable frequency current-mode, variable on-time, or variable off-time. CPU power supplies that are designed using these types of control methods require additional bulk storage capacitors on the output to maintain  $V_O$  within the regulation limits during the high di/dt load transients because of the limited bandwidth of the controller. Some controllers add a fast loop around the slower main control loop to improve the response time, but  $V_O$  must deviate outside a fixed tolerance band before the fast loop becomes active. The hysteretic control method employed by the TPS5210 offers superior performance with no requirements for additional output capacitance or difficult loop compensation design.

The TPS5210 was optimized for tight  $V_O$  regulation under static and dynamic load conditions, for improved system efficiency, and for operation in systems that derive main power from 12 V, 5 V, and at 3.3 V.

#### 1.1 Synchronous Buck Regulator Operation

The synchronous buck converter is a variation of the traditional buck converter. The main switching device is usually a power MOSFET and is driven in the same manner as in a traditional buck converter. The freewheeling rectifier, usually a Schottky device, is replaced by a power MOSFET and is driven in a complementary or synchronous fashion relative to the main switching device; when one MOSFET is on, the other is off. The freewheeling MOSFET is selected so that its ON voltage drop is less than the forward drop of the original freewheeling rectifier, thus increasing conversion efficiency. A very important design issue when using a synchronous buck converter is preventing cross-conduction of the two power MOSFETs, i.e., preventing both MOSFETs from being on simultaneously. A small amount of deadtime is necessary.

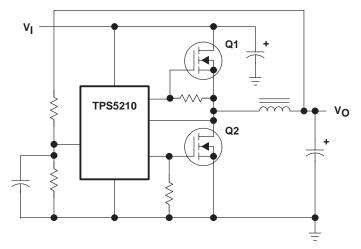

Figure 1 shows a simplified schematic of a synchronous buck converter. The TPS5210 senses the output voltage and then drives Q1 and Q2 depending on the sensed voltage. The TPS5210 senses the voltage at the junction of Q1, Q2, and L1 and uses it to actively prevent simultaneous conduction of Q1 and Q2.

Figure 1. Simplified Synchronous Buck Converter Schematic

## **1.2 Hysteretic Control Operation**

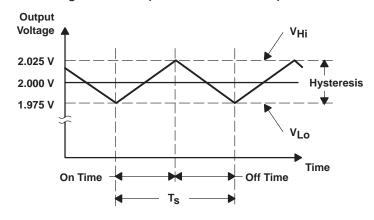

Hysteretic control, also called bang-bang control or ripple regulator control, maintains the output voltage within the hysteresis band centered about the internal reference voltage. Figure 2 shows a simplified example of a hysteretic controlled output voltage with a reference voltage of 2.000 V and a hysteresis band of 50 mV. If the output voltage is at or below the level of the reference minus one-half of the hysteresis band ( $V_{1,0} = 1.975$  V), the TPS5210 turns off the low-side MOSFETs (Q2 in Figure 1) and turns on the high-side MOSFETs (Q1 in Figure 1) of the synchronous buck converter power stage. This is the power stage on-state, and it causes the output voltage to increase. When the output voltage reaches or exceeds the reference plus one-half of the hysteresis band (V<sub>Hi</sub> = 2.025 V), the TPS5210 turns off the high-side MOSFETs and turns on the low-side MOSFETs. This is the power stage off-state, and it causes the output voltage to decrease. This hysteretic method of control keeps the output voltage within the hysteresis band around the reference voltage. If output-load current steps or input-voltage transients force the output voltage out of the hysteresis band, the TPS5210 sets the power-stage MOSFETs in the continuous on or off state as required to return the output voltage to the hysteresis band. Thus, the output voltage is corrected as quickly as the output filter allows. There are no error amplifier sensing and adjusting delays, as is the case with either voltage- or current-mode controllers. Other advantages of hysteretic control include no loop compensation design and no input filter interaction problems.

Figure 2. Simplified Hysteretic Controlled Output Voltage Waveform

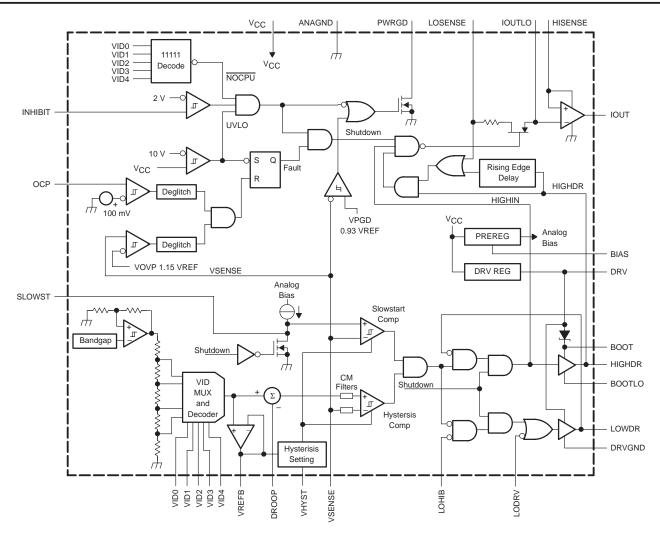

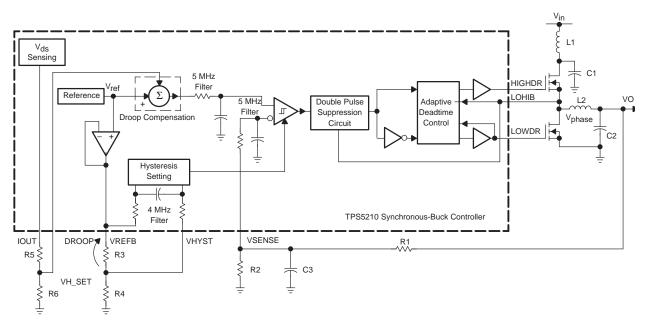

# 2 TPS5210 Operation Overview

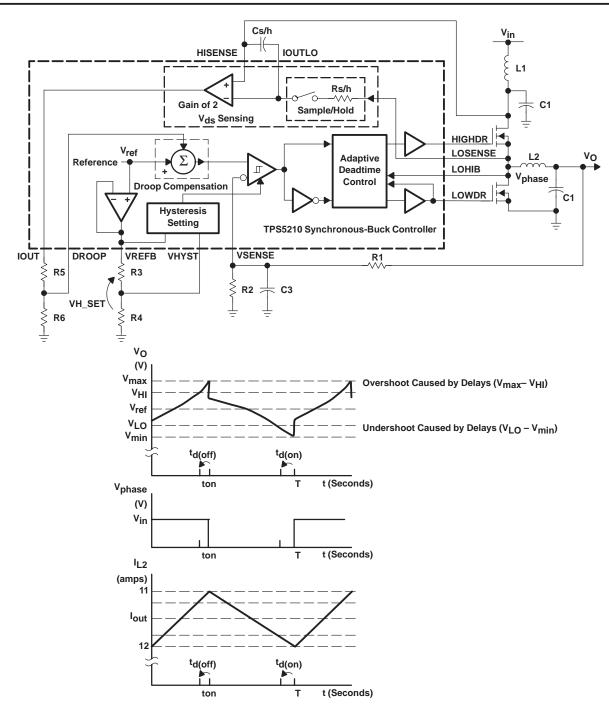

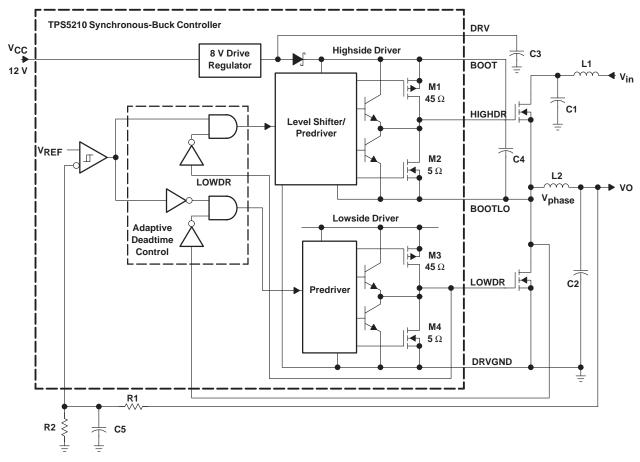

The TPS5210 is a controller for a high-performance synchronous buck hysteretic regulator. Figure 3 shows the schematic and waveforms of a hysteretic regulator, including a simplified block diagram of the TPS5210. The TPS5210 block diagram shows only the hysteretic regulator functions. The main function blocks are shown: synchronous-buck gate drivers with adaptive deadtime control, 1% reference, hysteresis level control, droop compensation control, and current sense control. Not shown in the block diagram are the protective functions such as slowstart and overcurrent protection, control functions such as Inhibit and VID inputs, or the separate power and analog grounds or floating high-side drive.

The main hysteretic control block is a fast comparator with a hysteresis level that is symmetrical about the reference voltage. Excluding delays, the high-side gate drive signal toggles on when the instantaneous output voltage decreases below the lower hysteresis limit,  $V_{LO}$ ; the gate drive signal toggles off when the instantaneous output voltage increases above the upper hysteresis limit,  $V_{Hi}$ . The low-side gate drive signal toggles synchronously so that when the high side is on, the low side is off. The hysteresis is symmetrical with respect to the reference voltage. The TPS5210 regulates  $V_O$  to the reference value while also regulating the ripple voltage on  $V_O$ . The hysteretic regulator provides a fast response to load transients and is well suited for CPU power supplies. The operating frequency of the hysteretic regulator depends upon  $V_I$ ,  $V_O$ , the output inductor and the output capacitors and is very predictable because  $V_I$  typically has a 5% regulation limit in CPU systems. Section 4.4.2 in this application report describes how to predict the operating frequency with design equations.

Figure 3. Hysteretic Regulator and Waveforms

Referring again to Figure 3, delays in the feedback path cause the ripple voltage to exceed the hysteresis levels set by the TPS5210. The source of the delays includes the propagation delay from the comparator inputs to the synchronous buck gate driver outputs (250ns maximum), the turn-on/turn-off delays of the power MOSFETs, the non-overlap delay time of the deadtime control circuit (100ns maximum), and the delay from the external RC filter between V<sub>O</sub> and the VSENSE pin (R1 and C3 in Figure 3). The ripple voltage is regulated to Vmax–Vmin. This higher ripple voltage should be taken into account when determining the programmed ripple voltage versus the actual ripple voltage.

The hysteresis band ( $V_{HI} - V_{Lo}$ ) is set with a voltage divider from the buffered reference (VREFB); the hysteresis band is equal to twice the difference voltage between VREFB and VHYST ( $V_{H\_SET}$  in Figure 3). The hysteresis band is set to a percentage of Vref within the hysteretic comparator.

The synchronous buck gate drivers have adaptive deadtime control to minimize the conduction time through the body-drain diode of the low-side MOSFET and prevent simultaneous conduction of the power MOSFETs, which would cause shoot-through currents.

The output current is indirectly sensed by sampling and holding the voltage across the high-side MOSFET. The RC time constant of the sample/hold switch resistance and hold capacitor is set to be greater than the conduction time of the high-side MOSFET so that the average voltage across the high-side MOSFET is sampled, and is proportional to the DC output current. The differential voltage across the sample/hold capacitor is amplified by 2 and converted to a single-ended signal on the IOUT pin; the voltage on IOUT is proportional to the output current.

The DROOP compensation circuit provides additional margin to maintain  $V_O$  within the load transient tolerance limits required by the processor.  $V_O$  is offset above the reference by the resistor divider from  $V_O$  to VSENSE (R1 and R2 in Figure 3). The voltage on the DROOP pin is made proportional to the load current by the resistor divider from IOUT to DROOP (R5 and R6 in Figure 3) such that  $V_O$  will be offset below the reference under full-load conditions. Section 3.2.3 contains test results that illustrate the advantage of DROOP compensation during a transient load.

Operation of the TPS5210 relies on the output ripple voltage waveform characteristics. The output voltage consists of an ac waveform riding on the average dc waveform. The ac component is influenced predominantly by the output capacitor ESL, ESR, and capacitance values in conjunction with the inductor ripple current. The output voltage is composed of:

$$vout(t) = Vdc + vac(t) = Vdc + ESL \times \frac{d(i_{ripple}(t))}{dt} + ESR \times i_{ripple}(t) + \frac{1}{Cout} \times \int i_{ripple}(t) dt$$

The ripple component from ESL causes the voltage steps; ESR causes the ramps; and capacitance causes the curvature in the ripple voltage during the switching transitions, as shown in Figure 3. Section 4 gives a more detailed analysis of the switching frequency and output voltage waveforms.

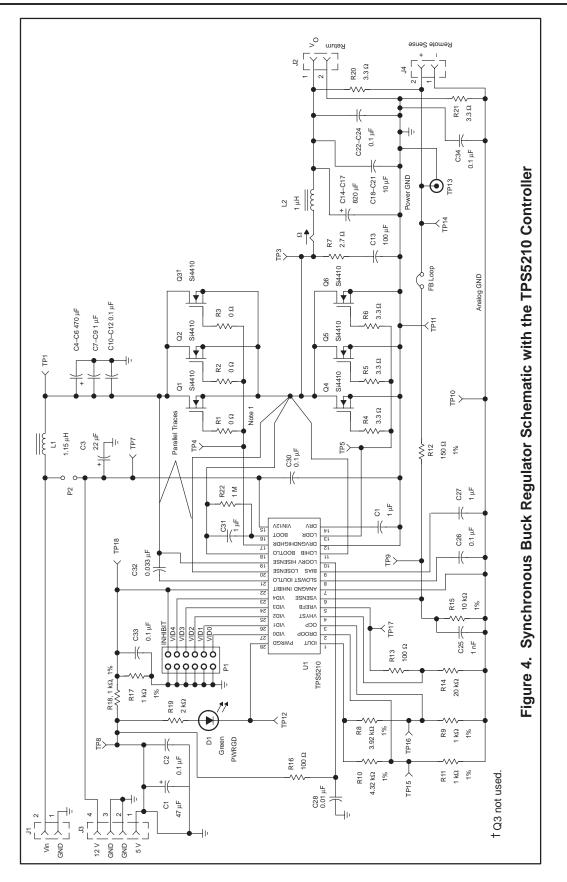

# 3 Example Design Circuit

The circuit shown in Figure 4 was designed and tested to demonstrate the performance attainable from a synchronous buck regulator using the TPS5210. The example was designed for typical server application operating conditions; Vin = 12 V,  $V_0$  = 2.0 V, lout = 20 A peak. Table 1 lists the critical power stage components for the example design of Figure 4.

Designing Fast Response Synchronous Buck Regulators Using the TSP5210

| Component Designator | Description                                    |

|----------------------|------------------------------------------------|

| Q1 – Q6†             | Si4410                                         |

| C4 – C6              | 470 μF, 16 V, Sanyo OS-CON #16SA470M           |

| L1                   | 8 turns, 18 AWG on Micrometals T44-8/90 toroid |

| L2                   | 7 turns, 16 AWG on Micrometals T68-8/90 toroid |

| C14 – C17            | 820 μF, 4 V, Sanyo OS-CON #4SP820M             |

| C18 – C21            | 10 µF, 16 V ceramic; Murata #GRM235Y5V106Z16   |

| C7 – C9              | 1 μF, 16 V; Panasonic #ECSH1CY105R             |

Table 1. Critical Power Stage Components

†Q3 not used.

#### 3.1 Measured Performance

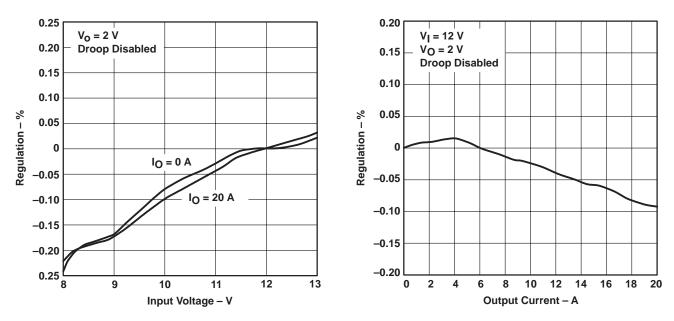

The tight line and load regulation of the example design with droop disabled, are shown in Figures 5 and 6 respectively with  $V_0 = 2 V$ . Regulation is maintained well below 1%.

#### 3.1.1 Line and Load Regulation

Figure 6. Normalized Load Regulation

## 3.1.2 Efficiency

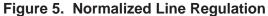

Since no current sense resistor is used, and adaptive delay circuitry is included for optimum drive, the efficiency is above 90% at 10 A and 88% at 20 A, as shown in Figure 7.

Figure 7. Efficiency vs Load Current

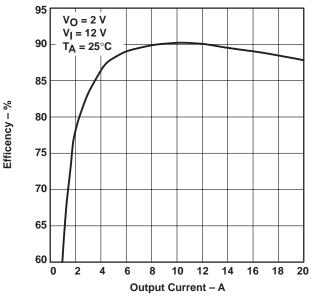

#### 3.1.3 Transient Load Response

Transient load operation of the TPS5210 is similar to the dc ripple regulation operation. The high-side gate drive signal maintains its state until the one hysteresis limit is reached, then the complement state remains fixed until the other hysteresis limit is reached. Propagation delays still apply. This characteristic allows extremely fast response times to load transitions.

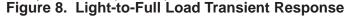

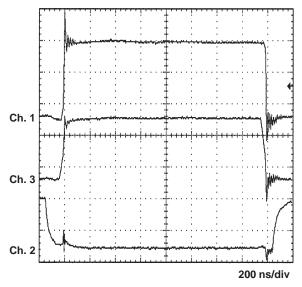

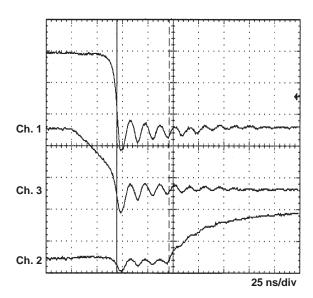

A load transient response test was conducted with a 0.1-A to 20.4-A load step at a 30-A/ $\mu$ s slew rate, and 1-kHz repetition rate (V<sub>I</sub> = 12 V, V<sub>O</sub> = 2 V). Figures 8 and 9 show the transient response for a light-to-full load transition and a full-to-light load transition, respectively, with droop active. After quickly regaining regulation, the voltage droop compensation circuit reduces the regulation set point by 50 mV in Figure 8, and increases it by 50 mV in Figure 9. With droop active, the transient regulation on V<sub>O</sub> is ±55 mV. The controller response time is less than 1  $\mu$ s.

Ch. 1: Voltage at the junction of high-side MOSFETs and low-side MOSFETs (20 V/div)

Ch. 4: Output ripple voltage (50 mV/div)

Ch. 2: Voltage on DROOP pin (50 mV/div)

Ch. 3: Output load current (14.5 A/div)

Ch. 1: Voltage at the junction of high-side MOSFETs and low-side MOSFETs (20 V/div) Ch. 4: Output ripple voltage (50 mV/div) Ch. 2: Voltage on DROOP pin (50 mV/div) Ch. 3: Output load current (14.5 A/div)

#### Figure 9. Full-to-Light Load Transient Response

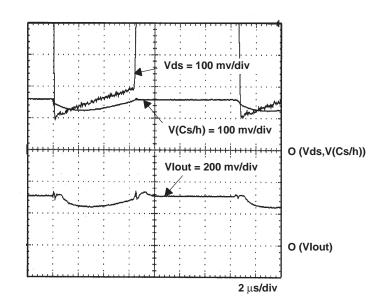

#### 3.1.4 Overcurrent Protection

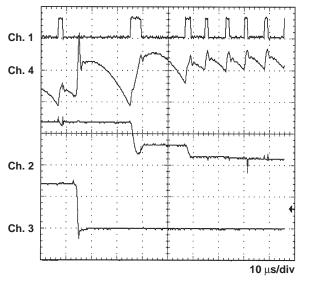

Overcurrent protection, OCP, is demonstrated in Figure 10 with load shorted, and in Figure 11 with the terminal common to MOSFETs shorted.

Figure 10. OCP Shorted Load Waveforms

#### 3.1.5 Power-Up Performance

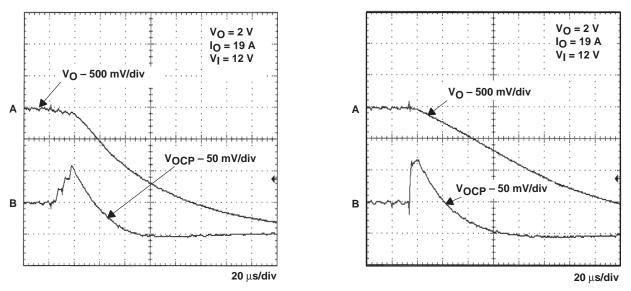

Figure 12 shows the power-up performance for a 20-A load. Its performance, similar to no load, is well behaved with almost no output voltage overshoot. The 12-V supply must be greater than the 10-V UVLO start threshold, and the 5 V supply must be greater than 4.2 V (set by a resistor divider from 5 V input to the INHIBIT pin in Figure 4) before the TPS5210 is enabled.

Figure 12. Power-Up Performance (I<sub>O</sub> = 20 A)

Designing Fast Response Synchronous Buck Regulators Using the TPS5210

# 4 Example Circuit Design Procedure

This section shows the procedure used in designing and selecting the power stage components to meet the performance parameters shown in Table 2 for the example circuit shown in Figure 4.

Before proceeding with any power supply design, certain decisions must be made that impact the course of the design. For this example design, the following performance parameters are adopted:

| PARAMETER                                       | VALUE       |

|-------------------------------------------------|-------------|

| Nominal output voltage                          | 2 V         |

| Output voltage static tolerance (see Note 1)    | ±60 mV      |

| DC output voltage tolerance                     | ±22 mV      |

| Output ripple and noise                         | 35 mV pk–pk |

| Output load regulation                          | ±0.1% VO    |

| Output line regulation                          | ±0.25% VO   |

| Output voltage transient tolerance (see Note 2) | ±100 mV     |

| Load transient response                         | 60 mV pk    |

| Load transient response time                    | 2 μs        |

| Maximum output current                          | 20 Amps     |

| Nominal switching frequency                     | 125 kHz     |

| Ambient temperature range                       | 0°C – 60°C  |

Table 2. Power Stage Design Parameters

NOTES: 1. Output voltage static tolerance includes:

- DC output initial voltage tolerance and set point adjust tolerance

- Output ripple and noise

- -Output load regulation

- Temperature

2. Output voltage transient tolerance includes:

- Load transient output voltage deviation

-Response time for output voltage return to within static tolerance limits.

## 4.1 Duty Cycle Estimate

An estimate of the duty cycle is used frequently in the following sections. The duty cycle, D, is the ratio of the high-side power-switch conduction time to the period of one switching cycle. The duty cycle for a continuous mode step-down converter is given by:

$$D = \frac{V_O + V_{DS(ON)}}{V_I}$$

Where:

$V_{DS(ON)}$  = An estimate of the on-voltage of the power MOSFETs.

For an initial estimate for  $V_{DS(ON)}$ , use 0.2 V. So, for an output voltage of 2 V and an input voltage of 12 V, the duty cycle calculates to:

$$D = \frac{2 V + 0.2 V}{12 V} = 0.18$$

#### 4.2 Input Capacitance

The input capacitance provides a low-impedance voltage source for the power stage. The ESR, ESL, RMS current rating and capacitance value of the input capacitance are important parameters in the selection process. The most stringent requirement is often the RMS current that the capacitance must handle. An equation for the RMS current seen by the input capacitance for a buck converter is given by:

$$I_{Cin(RMS)} = \sqrt{D \times (1-D) \times I_O^2}$$

The above equation assumes that the output ripple current is small, that there is an input inductor, and that its ripple current is small. For  $V_I = 12$  V and  $I_O = 20$  A, we get:

$$I_{Cin(RMS)} = \sqrt{0.18 \times (1-0.18) \times 20^2} = 7.7 \ A \ RMS$$

The input capacitance for this design uses three  $470-\mu$ F, 16-V Sanyo OS-Con type electrolytic capacitors in parallel. They are C4, C5, and C6 in Figure 4. The ripple current rating for one of these capacitors is 6.08 A RMS at 45°C and is reduced to 4.26 A RMS at 85°C. Using linear interpolation to get an estimate for the rating at 60°C gives a rating of 5.5 A RMS for each capacitor. The total ripple current rating for the input capacitance is  $3 \times 5.5 = 16.5$  A RMS.

## 4.3 Output Filter Design

Unlike fixed-frequency PWM-controlled power supplies, the output filter design is driven primarily by the need to provide satisfactory output voltage performance in response to fast load transients encountered when supplying power to currentand next-generation microprocessors. A secondary consideration is the switching frequency resulting from the output filter component values. This section discusses important considerations when selecting/designing the output filter elements. A detailed analysis of the output voltage ripple characteristics is also presented, resulting in an expression for predicting the power supply switching frequency.

## 4.3.1 Output Capacitance

Normally, the output capacitor is selected to limit ripple voltage to the level required by the specification, but in a hysteretic regulator, such as this one, the TPS5210 essentially determines the output voltage ripple. The output ripple is previously chosen to be 35 mV and is relatively independent of the output capacitor characteristics. Since output voltage ripple is set by the comparator hysteresis band, the output capacitor is chosen to provide satisfactory response to fast load transients.

To show the importance of the output capacitor characteristics, consider the following: This example circuit is designed for a worst case load step of no load (0 Amps) to full load (20 Amps) with a slew rate of 30 A/µs. This implies that the load transient occurs 667 ns  $\left(\frac{20 A}{30 A/µs} = 667 ns\right)$ . For a transient of this duration, the output filter alone controls the initial output voltage deviation. Further examination shows that the output filter inductor current changes little during the load transient. Therefore, for fast load transients, the output capacitor characteristics dominate the output filter performance. In this design, the output capacitor's ESR (equivalent series resistance) and ESL (equivalent series inductance) are the parameters that are most critical.

To calculate the ESR requirement, assume that all the load transient current is supplied by the output capacitor. Also assume that the output voltage change due to the capacitor's capacitance is much smaller than the voltage change due to the ESR, and that the capacitor's ESL is negligible. In most practical applications, these assumptions are reasonable and they greatly simplify calculations. The ESR required to limit output voltage change to 60 mV due to a 20 amp load step is:

$$ESR \leq \frac{\Delta V_O}{\Delta I_O} = \frac{60 \ mV}{20 \ A} = 3 \ m\Omega$$

The required level of ESR requires a large amount of capacitance. For this design, four Sanyo OS-Con type electrolytic capacitors connected in parallel are selected. These capacitors are a good compromise between performance, cost, and board area requirements. Less costly capacitors are available but more capacitors are required to achieve equivalent ESR levels. Even though the Sanyo parts may be more expensive, the cost is offset by providing savings in board area and number of parts required. The particular part used is an 820- $\mu$ F, 4-V capacitor with a specified maximum ESR of 12 m $\Omega$ , giving a total maximum ESR of 3 m $\Omega$ . These capacitors are C14, C15, C16, and C17 in Figure 4. For good design practice, C18–C21, four 10- $\mu$ F ceramic capacitors, are placed in parallel with C14–C17. Ceramic capacitors are very effective for suppressing high frequency switching spikes and reducing the effects of the ESL of C14–C17.

To summarize, the output capacitance must be selected to provide a sufficiently low ESR. The capacitor(s) must have an adequate voltage rating for the particular application. In addition, the capacitor(s) must have an ample ripple current rating to handle the applied ripple current. This ripple current is dependent on the ripple current in the output inductance that is calculated in the next section. The RMS current in the output capacitance is calculated as follows:

$$I_{CRMS} = \Delta I_L \times \frac{\sqrt{3}}{6} = \Delta I_L \times 0.289 = 10.6 \ A \times 0.289 = 2.9 \ A_{RMS}$$

Where  $\Delta I_L$  is the peak-to-peak ripple current in the output inductor.

The ripple current rating for one of these capacitors is 5.04 A RMS at 45°C and is reduced to 3.53 A RMS at 85°C. Using linear interpolation to get an estimate for the rating at 60°C, gives a rating of 4.47 A RMS for each capacitor. The total ripple current rating for the output capacitance is  $4 \times 4.47 = 17.9$  A RMS.

#### 4.3.2 Output Inductance

The output filter inductance is the next quantity to be determined. Like the output capacitance selection, the primary consideration is providing satisfactory response to a fast load transient.

The inductance affects the output voltage response to transient loads by governing the rate at which its current can increase (or decrease). For example, during a load transient where the output current increases from no load to full load, the output capacitor supplies all of the output current until the inductor current has time to increase to full load. So, a relatively small inductance is desired.

On the other hand, the inductance also plays a part in the power supply switching frequency, because the inductance limits how fast the output voltage traverses through the hysteresis band. As the inductance decreases, the output voltage changes faster, giving rise to higher switching frequencies.

Therefore, the inductor value is fairly critical and should be stable over the expected load and temperature range. Care should be exercised in the inductance selection because design requirements for hysteretic regulators are different from PWM controlled converters. Recall that for a fixed frequency PWM controlled buck converter, for a given operating point, the output inductance governs the peak-to-peak amplitude and the slope (di/dt) of the inductor current. In a hysteretic regulator, the ripple current is set by the output voltage ripple setting and the output capacitance impedance.

Other important factors to be considered when designing or selecting the inductor are current capability, allowable operating frequency, and DC resistance.

After choosing an initial inductance value, the power supply switching frequency must be estimated to insure that it is within the desired range. The switching frequency for the example design given in Figure 4 is nominally 125 kHz. A detailed analysis of the switching frequency and an equation to predict it is given later.

To calculate the maximum inductance allowed for a given response time, load step, and operating point, the following simple relationship is used:

$$V_{L} = L \times \frac{I_{TRAN}}{\Delta t} \Rightarrow L \le \frac{V_{L}}{I_{TRAN}} \times \Delta t$$

Where:

$V_L$ = the voltage applied across the output inductor,  $I_{TRAN}$  = the magnitude of the load step, and  $\Delta t$  = the desired response time.

For a load step from light load to heavy load, the voltage applied across the inductor can be assumed to be  $V_I - V_O$ . This also assumes that the duty cycle is 100% as the output voltage is corrected. Alternatively, for a load step from heavy load to light load, the voltage across the inductor can be assumed to be  $V_O$ . This assumes that the duty cycle is 0% as the output voltage is corrected.

For the example circuit described here, the condition which gives the smallest inductor value is a load step from heavy load to light load. This is because the voltage applied to the output inductor is the lowest, i.e., the output voltage. For this case, allowing 15  $\mu$ s for the inductor current to change, an inductance value is calculated as follows:

$$L \le \frac{V_L}{I_{TRAN}} \times \varDelta t = \frac{2}{20} \times 15 \times 10^{-6} = 1.5 \ \mu H$$

For convenience, a  $1.2-\mu$ H inductor was designed for this circuit. Figures 8 and 9 illustrate satisfactory transient load performance for the output filter values selected in this and the previous sections.

#### 4.4 Switching Frequency Analysis

After the elements of the output filter are determined, the power supply switching frequency must be estimated. If the estimated switching frequency is too high, the switching losses in the power MOSFETs will be high, resulting in less than optimum efficiency. If the estimated switching frequency is too low, the inductor value may be too high, resulting in unsatisfactory transient response. A switching frequency outside the desired range should be corrected by changing either the output ripple setting, the output capacitance, or the output inductance.

To accurately predict the switching frequency of a hysteretic regulator, the output voltage ripple must be investigated. This should be expected, since the power supply switching instants are based upon the state of the output voltage. A simple and accurate method of determining the switching frequency is described below.

#### 4.4.1 Output Ripple

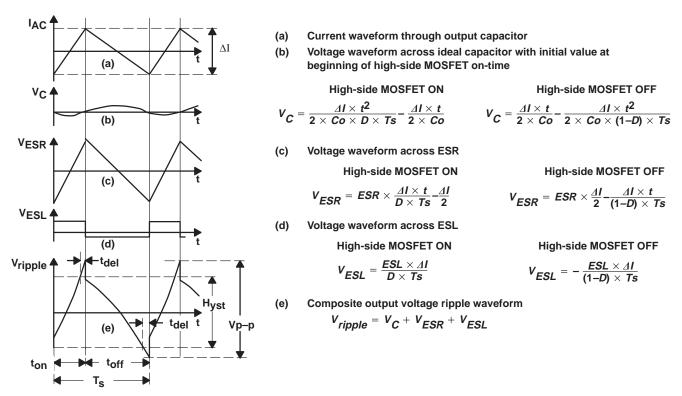

The three elements of the capacitor that contribute to ripple are ESR, ESL, and capacitance. Assume that all three elements are in series and there are no other parasitic components to consider. Figure 13 shows the voltage waveforms across each component of the output capacitor and the corresponding equations.

#### Figure 13. Output Ripple Voltage Detail

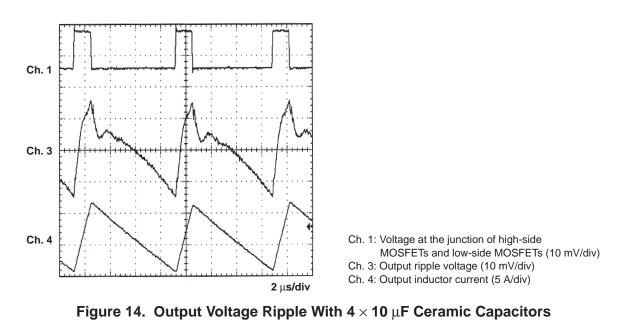

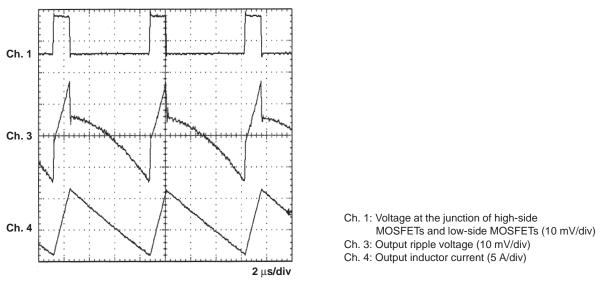

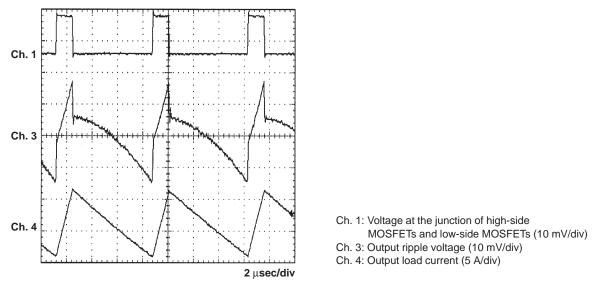

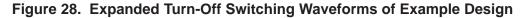

Figure 14 shows the phase voltage (voltage at junction of high-side MOSFET with low-side MOSFET), output voltage, and inductor current waveforms for the example circuit of Figure 4. The output voltage waveform is slightly different from the theoretical waveform of Figure 3 due to the smoothing effect of the four  $10-\mu$ F ceramic capacitors in parallel with the OS-CON electrolytic capacitors. Some resonance due to the ceramic and electrolytic capacitors is also noticeable as the voltage begins to drop. Figure 15 demonstrates how the waveforms, with the ceramic capacitors removed, closely resemble the theoretical waveforms of Figure 3. The waveforms are very similar to ideal waveforms, and the ESL, ESR, and capacitive effects are noticeable.

#### 4.4.2 Switching Frequency Equation

Assume that the input and output voltage ripple magnitudes are relatively negligible compared to the dc component. Also assume that the time constant  $L/(R_{DS(on)} + R_L)$ , where L is the output inductance, R<sub>L</sub> is the inductor resistance and R<sub>DS(on)</sub> is the on-state resistance of the high-side MOSFET(s), is high in comparison with the switching period. Assume the body diode conduction time and switching transition time are much smaller than the switching period. These assumptions are reasonable for low voltage ripple and high efficiency regulators. In such a case the output inductor current can be modeled as the sum of the dc component, which is equal to the output current *Io*, and the ac linear ramp component, which flows through the output capacitor (Figure 13).

The numbered equations in this section are used to derive the switching frequency equation.

Peak to peak value of the inductor current  $\Delta I$  is given by the following equation:

$$\Delta I = \frac{V_I - Io \times (R_{DS(on)} + R_L) - V_O}{L} \times D \times Ts$$

(1)

Where:

$V_{I} = \text{the input voltage}$   $V_{O} = \text{the output voltage}$  Ts = the switching period  $D = \frac{V_{O} + Io \times \left(R_{DS(on)} + R_{L}\right)}{V_{I}}$ is the duty cycle which is defined as :  $D = \frac{t_{ON}}{Ts} \text{ and } t_{ON} \text{ is the on time of the high-side MOSFET.}$

Referring to Figure 13 (e), the output voltage ripple,  $V_{p-p}$ , is higher than the hysteresis band, *Hyst*, because of the delays,  $t_{del}$ , that were described in Section 2. Assume that delays for both switching instants are equal for simplicity. The ideal capacitor voltage component has the same initial value during switching instants  $t_{ON}$  and  $(T_{s}-t_{ON})$  (see Figure 13 (b)). In this case the voltage  $V_{p-p}$  is:

$$V_{p-p} = \frac{ESL}{L} \times V_{I} + \Delta I \times ESR$$

<sup>(2)</sup>

On the other hand, the hysteresis band is equal to the difference between the peak-peak values of the V<sub>O</sub> ripple,  $v_{ripple}$ , at the moments  $t_{ON} - t_{del}$  and  $t_{OFF} - t_{del}$

$$Hyst = V_{ripple} \left( t_{ON} - t_{del} \right) - V_{ripple} \left( t_{OFF} - t_{del} \right)$$

(3)

After substituting equation (1) into equations for  $v_C$ ,  $v_{ESR}$  and  $v_{ESL}$  (Figure 13) and using equations (2) and (3), the following equation for the switching frequency,  $f_S$ , can be derived:

$$f_{S} = \frac{V_{O} \times (V_{I} - V_{O}) \times (ESR - t_{del} / Co)}{V_{I} \times (V_{I} \times ESR \times t_{del} + Hyst \times L - ESL \times V_{I})}$$

(4)

Equation (4) shows that the switching frequency strongly depends on *ESR* and *ESL*. It is important that *ESL* meet the following condition:

$$ESL < (ESR \times t_{del} + Hyst \times L \times D / Vout)$$

If it does not, the voltage step across the ESL during switching exceeds the hysteresis window, and the switching frequency becomes too high and uncontrollable.

The switching frequency does not depend on the load current in equation (4), because a synchronous regulator has the same two stages of operation during the switching period over the load current range, including no load condition. There is no discontinuous mode operation at very light loads. In reality there is a weak dependence of the switching frequency on the load current because of power losses and additional voltage drops through non-ideal components. Equation (4) should be sufficiently accurate for the first frequency estimate at the beginning of a design.

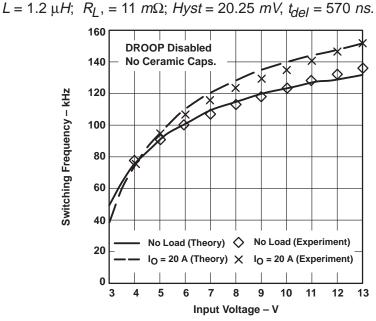

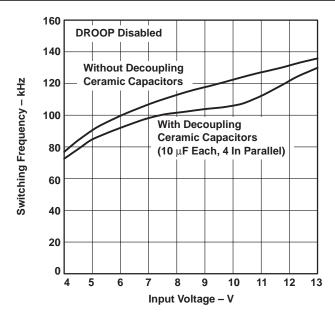

Figure 16 gives theoretical estimate and measurement results of the frequency for the example circuit of Figure 4 without the four 10- $\mu$ F ceramic decoupling capacitors (C18–C21), under no-load and 20-A load conditions. There is good agreement with theoretical and measured results; the maximum difference is less than 7%. Four Os-Con 820- $\mu$ F, 4-V capacitors were used in this example circuit. The measured values for ESR and ESL for each capacitor were 8 m $\Omega$ , and 4.8 nH, respectively, using an impedance analyzer with lead length error compensation. Since there are four capacitors in parallel, these values were divided by four and substituted in equation (4). The other values that were substituted in equation (4) are the following:

Figure 16. Switching Frequency vs Input Voltage

The switching frequency was also measured with the 4  $\times$  10  $\mu F$  ceramic capacitors (C18–C21) in the example circuit of Figure 4. Comparison results with and without ceramics are given in Figure 17. For low input voltages, the switching frequencies are about the same. For V<sub>I</sub> ranging between 7 V and 11 V, the frequency is lower with ceramics because the resonant period between ceramics and the OS-CON capacitors is close to the on-time of the converter, resulting in a longer on-time; the off-time increases to regulate V<sub>O</sub> to the correct value, causing a decrease in switching frequency. Adding decoupling ceramic capacitors decreases ESL from 1.2 nH to 0.8 nH; consequently, decreasing the switching frequency.

Figure 17. Switching Frequency With and Without Ceramic Capacitors

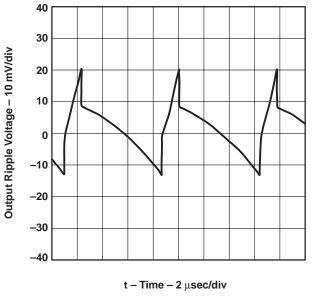

Theoretical output voltage waveforms based on the frequency calculation were obtained using Mathcad<sup>™</sup> software (Figure 18). These calculations are very close to the experimental waveforms measured without decoupling capacitors (Figure 19).

Figure 18. Theoretical Output Ripple Waveform

Figure 19. Measured Output Ripple Waveform

#### 4.5 Power MOSFET Selection

The TPS5210 is designed to drive N-channel power MOSFETs in a synchronous rectifier configuration. The MOSFET chosen for this design is the Siliconix Si4410DY. This device is chosen for its low  $r_{DS(on)}$  of 13.5 m $\Omega$  and drain-to-source breakdown voltage rating of 30 V. In addition, to reduce power dissipation, two power MOSFETs (Q1 and Q2) are paralleled for the high-side switch and three power MOSFETs (Q4, Q5, and Q6) are paralleled for the low-side switch.

Power dissipation for the switching MOSFETs, which includes both conduction and switching losses, is given by:

$$P_{D(Q1-Q2)} = \left(I_D^2 \times r_{DS(on)} \times D\right) + \left(0.5 \times V_i \times I_D \times t_{r+f} \times f_{sw}\right)$$

$$P_{D(Q4-Q6)} = \left(I_D^2 \times r_{DS(on)} \times (1-D)\right) + \left(0.5 \times V_i \times I_D \times t_{r+f} \times f_{sw}\right)$$

An example MOSFET power dissipation calculation for Q1 and Q3 is shown below with the following assumptions:

The total switching time,  $t_{r+f} = 100$  ns,

An  $r_{DS(on)}$  high temperature adjustment factor = 1.4,

A 60°C maximum ambient temperature,

$V_I$  = 12.0 V,  $V_O$  = 2 V, and  $I_O$  = 20 A then :

$$P_{D(Q1)} = \left(\frac{20.0}{2}\right)^2 \times (0.0135 \times 1.4) \times 0.18 + 0.5 \times 12 \times \left(\frac{20}{2}\right) \times 100 \times 10^{-9} \times 125 \ \text{kHz} = 0.34 + 0.75 = 1.09 \ \text{W}$$

$$P_{D(Q4)} = \left(\frac{20}{3}\right)^2 \times (0.0135 \times 1.4) \times 0.82 + 0.5 \times 12 \times \left(\frac{20}{3}\right) \times 100 \times 10^{-9} \times 125 \ \text{kHz} = 0.69 + 0.50 = 1.19 \ \text{W}$$

The thermal impedance of these devices,  $R_{\theta JA}$  = 90°C/W for FR-4 with 2-oz. copper and a one-inch-square pattern, thus:

$$T_{J(Q1)} = T_A + (R_{\theta J-A} \times P_D) = 60 + (50 \times 0.90) = 115^{\circ}C$$

$$T_{J(Q3)} = T_A + (R_{\theta J-A} \times P_D) = 60 + (50 \times 1.19) = 120^{\circ}C$$

It is good design practice to check power dissipation at the extreme limits of input voltage to find the worst case.

The total losses in both the high-side switches (2 in parallel) and low-side switches (3 in parallel) can simply be summed up as follows:

$$P_{D(Total)} = (2) \times (1.09 \text{ W}) + (3) \times (1.19 \text{ W}) = 5.75 \text{ W}$$

# 5 TPS5210 Functions

The functional block diagram of the TPS5210 is given in Figure 20. The controller has the following main features:

- VID/DAC that conforms to Intel's VRM8.3 specification; reference levels between 1.8 V and 1.3 V decremented by 50 mV, and 3.5 V to 2.1 V decremented by 0.1 V.

- 1% reference over 0°C to125°C junction temperature range for reference voltages between1.3 V and 2.5 V.

- Synchronous-buck gate drivers with adaptive deadtime control

- High-side MOSFET driver voltage rating of 30 V

- MOSFET driver peak current rating of 2 A

- Hysteretic comparator: 250 ns propagation delay to gate driver outputs, 2.5 mV offset voltage, symmetrical hysteresis, hysteresis setting is a percentage of Vref.

- Lossless output current sensing circuit

- Accurate, fast droop compensation circuit

- Slowstart circuit; slowstart time independent of VID setting

- Internal 8 V drive regulator for reduced gate charge power losses

- POWERGOOD comparator, 93% of Vref trip

- UVLO, Vcc undervoltage lockout, 10 V start, 2 V hysteresis

- INHIBIT comparator that can also monitor UVLO of the system logic supply, 2.1 V start, 100 mV hysteresis.

- Latched overcurrent shutdown circuit

- Latched overvoltage shutdown circuit

- LODRV pin that activates the low-side MOSFETs as a crowbar to protect against a short across the high-side MOSFETs.

Figure 20. TPS5210 Functional Block Diagram

This section describes the functions governed by the TPS5210. A procedure is given to determine the values of components used in the example design given in Figure 4. Example calculations accompany the design equations. There are many possible ways to proceed when designing power supplies and some iteration may be necessary when actual performance differs from design predictions. Reference designators refer to the circuit in Figure 4.

## 5.1 V<sub>CC</sub> Undervoltage Lockout

The V<sub>CC</sub> undervoltage lockout circuit disables the controller while V<sub>CC</sub> is below the 10-V start threshold during power-up. While the controller is disabled, the output drivers will be low and the slowstart capacitor will be shorted. When V<sub>CC</sub> exceeds the start threshold, the short across the slowstart capacitor is released and normal converter operation begins. There is a 2-V hysteresis in the undervoltage lockout circuit for noise immunity.

#### 5.2 Inhibit

The inhibit circuit is a comparator with a 2.1-V start voltage and a 100-mV hysteresis. When inhibit is low, the output drivers are low and the slowstart capacitor is discharged. When inhibit is above the start threshold, the short across the slowstart capacitor is released and normal operation begins.

When the system logic supply is connected to the inhibit pin, the inhibit pin also controls power sequencing by locking out controller operation until the system logic supply exceeds the input threshold voltage of the inhibit circuit; thus, the 12-V supply and the system logic supply (either 5 V or 3.3 V) must be above UVLO thresholds before the controller is allowed to start up.

In applications that derive main power from 5 V or 3.3 V for the power stage, the inhibit circuit can be the UVLO circuit for the main power supply.

#### 5.3 Slowstart Design

Slowstart or soft-start is added to reduce power-up transients. Without slowstart, when input power is first applied, the TPS5210 attempts to raise the output voltage (initially zero) to its normal operating level by turning on the top MOSFET until the voltage is approximately Vref. This can cause high transient currents to flow in the output inductor and output capacitor. Although this form of startup usually does not cause component failures, it does apply stresses much greater than those typically encountered in normal operation. It is good design practice to include slowstart circuitry to avoid these unnecessary stresses.

The slowstart circuit in the TPS5210 controls the rate at which the output voltage powers up. A capacitor, C26, connected between SLOWST (pin 8) and ANAGND (pin 7), is charged by an internal current source. This current source is proportional to the reference voltage and is adjustable by an external resistance selected by the user. The output voltage follows the voltage on the slowstart capacitor during startup. Since the charging current is proportional to the reference voltage for a given resistor value.

Choices of the slowstart time and the slowstart capacitor value are largely arbitrary as long as system startup time requirements are met. For this example design, a slowstart time of 10 ms is chosen, and the slowstart capacitor is chosen to be 0.1  $\mu$ F. Therefore, to charge 0.1  $\mu$ F from zero volts to 2 V in 10 ms, the following equation holds:

$$I_{SLOWSTART} = C_{SLOWSTART} \times \frac{\Delta V_c}{\Delta t_{ss}} = 0.1 \ \mu F \times \frac{2 \ V}{10 \ ms} = 20 \ \mu A$$

The slowstart charging current is determined by the following equation:

$$I_{SLOWSTART} = \frac{I(VREFB)}{5}$$

where I(VREFB) = the current out of VREFB (pin 5).

For an I<sub>SLOWSTART</sub> current equal to 20  $\mu$ A, I(VREFB) should be set to:

$$(VREFB) = 5 \times I_{SLOWSTART} = 5 \times 20 \ \mu A = 100 \ \mu A$$

The voltage on VREFB (pin 5) is a buffered reference voltage from the output of the VID network. For this design, the VID inputs are driven to produce a reference (and output) voltage of 2 V.<sup>[4]</sup> The resistance from the VREFB pin to ANAGND can be calculated as:

$$R_{VREFB} = \frac{2 V}{100 \ \mu A} = 20 \ k\Omega$$

This value is used to determine the values of R13 and R14 that set the hysteresis level.

The equations above can be used to derive a simplified relationship for the slowstart time as shown:

$$t_{SLOWSTART} = 5 \times C_{SLOWSTART} \times R_{VREFB}$$

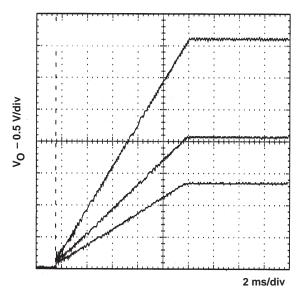

$V_O$  start-up waveforms for different VID (and reference voltage) settings are given in Figure 21, showing that slowstart time is independent of the VID setting.

Figure 21. Output Voltage Slowstart at 1.3 V, 2 V, 3.5 V Settings

#### 5.4 Hysteresis Setting

The next step in this design is choosing the desired output voltage ripple. As a first approximation, the output voltage ripple is simply the difference between the two levels ( $V_{LO}$  and  $V_{Hi}$ ) shown in Figure 2. The hysteresis setting of the hysteresis comparator of the TPS5210 sets these two levels. The hysteresis is set by two external resistors and is centered around VREF (pin 5). The hysteretic comparator is designed with low input offset voltage ( $\pm 2.5$  mV max) low propagation delays (250ns max to gate driver outputs with 10mV overdrive) and accurate hysteresis setting ( $\pm 3.5$  mV max). The hysteresis is proportional to the reference voltage; programming Vref to a new value automatically adjusts the hysteresis to be the same percentage of Vref.

To accurately choose the output voltage ripple, all of the propagation delays must be considered. The first step is to calculate the amount of ripple expected due to the delays, in addition to the ripple set by the hysteresis comparator. Using the terminology of Section 4.4.1, this additional ripple is equal to  $V_{p-p}$  – Hyst and will be referred to  $V_{del}$  for ease of reference. Or:

$$V_{p-p} = Hyst + V_{del}$$

Where:

$V_{p-p}$  =the total output ripple,

Hyst = the hysteresis setting of the hysteretic comparator, and  $V_{del}$  = the output ripple exceeding Hyst and due to all propagation delays.

Assuming the output ripple during the delay time is primarily caused by the inductor ripple current flowing through the output capacitors' ESR, the additional ripple, V<sub>del</sub>, can be estimated as:

$$V_{del} = \left[\frac{V_l - V_O}{L} \times t_{del}\right] \times ESR + \left[\frac{V_O}{L} \times t_{del}\right] \times ESR$$

To calculate  $V_{del}$  for this example design, use the measured components given in Section 4.4.2. They are repeated here for convenience:

$$\begin{split} L &= 1.2 \; \mu H \\ \text{ESR} &= 2 \; \text{m} \Omega \\ \text{T}_{\text{del}} &= 570 \; \text{ns} \end{split}$$

Now calculate V<sub>del</sub>:

$$V_{del} = \left[\frac{12-2}{1.2 \times 10^{-6}} \times 570 \times 10^{-9}\right] \times 0.002 + \left[\frac{2}{1.2 \times 10^{-6}} \times 570 \times 10^{-9}\right] \times 0.002 = 11.4 \text{ mV}$$

Since the total output voltage ripple was set to 35 mV in Table 2 of Section 4, the hysteresis needs to be set for 35 mV - 11.4 mV = 23.6 mV. For convenience, and allowing a little margin, the hysteresis will be designed for 20 mV.

To set the hysteresis, connect two external resistors to form a resistor divider from VREFB (pin 5) to ANAGND (pin 7) with the center of the divider connected to VHYST (pin 4). The hysteresis of the comparator is equal to twice the voltage that is between the VREFB (pin 5) and VHYST (pin 4) pins. Or,

$$V_{Hysteresis} = 2 \times (VREFB-VHYST)$$

For this design, 20 mV of hysteresis was chosen for a 2.0 V output voltage.

$$V_{Hysteresis} = 20 \ mV = 2 \times (2 \ V - V HYST)$$

Solving for VHYST:

$$VHYST = VREFB - \frac{V_{Hysteresis}}{2} = 2 - \frac{20 \ mV}{2} = 1.99 \ V$$

Referring to the schematic, Figure 4, the two external resistors are R13 and R14. From the previous section, the total resistance required is 20 k $\Omega$ . Since R13 is very small compared to R14, for simplicity set R14 = 20 k $\Omega$ . To calculate the value of R13:

$$VHYST = VREFB \times \frac{R14}{R14 + R13}$$

Solving for R10:

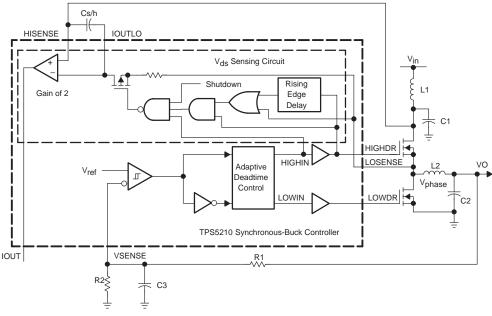

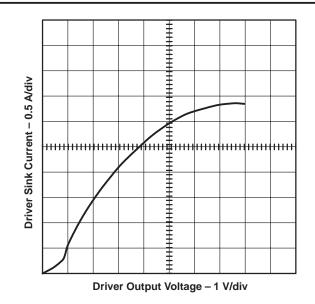

$$R13 = \frac{VREFB \times R14}{VHYST} - R14 = \frac{(2 \ V) \ (20 \ k\Omega)}{1.99 \ V} - 20 \ k\Omega = 100 \ \Omega$$