## AN-1977 LMH0346 Customization with SMBus

#### **ABSTRACT**

This application report explains how to customize the LMH0346 reclocker using the SMBus.

|   | Contents                                                                       |   |

|---|--------------------------------------------------------------------------------|---|

| 1 | Introduction                                                                   |   |

| 2 | SMBus Overview                                                                 |   |

| 3 | Enabling SMBus Access for the LMH0346                                          |   |

| 4 | Description of a Subset of LMH0346 Registers                                   | 6 |

|   | List of Figures                                                                |   |

| 1 | SMBus Transaction Format                                                       | 3 |

| 2 | SMBus Register Write                                                           | 3 |

| 3 | SMBus Register Read                                                            | 2 |

| 4 | LMH0346 SMBus Implementation                                                   | 5 |

| 5 | SMBus Timing Parameters                                                        | Ę |

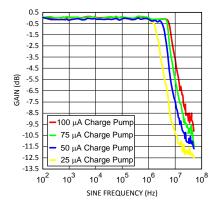

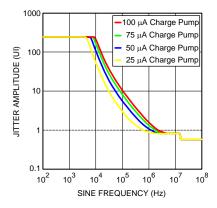

| 6 | LMH0346 2.97 Gbps Jitter Transfer with Different Charge Pump Current Settings  | 7 |

| 7 | LMH0346 2.97 Gbps Jitter Tolerance with Different Charge Pump Current Settings | 7 |

|   | List of Tables                                                                 |   |

| 1 | Recommended SMBus Timing                                                       | Ę |

| 2 | Register 00h – Basic Control                                                   | 6 |

| 3 | Register 0Eh – Modifying the CDR Loop Bandwidth                                | 7 |

| 4 | Register 10h – Powering Down the SDO and SCO/SDO2 CML Drivers                  | 8 |

| 5 | Register 32h – Reading Back the Detected Rate                                  | 8 |

All trademarks are the property of their respective owners.

Introduction www.ti.com

#### 1 Introduction

The LMH0346 3G HD/SD SDI Reclocker provides excellent jitter performance for 2.97 Gbps digital video streams that comply with the SMPTE 424M standard. The reclocker's small size, excellent jitter performance, and low power make it ideal for applications such as routers, video switchers, and distribution amplifiers.

The LMH0346 provides pin-accessible features such as: two differential serial data outputs (one programmable as a data-rate clock output), auto or manual rate select, auto or manual data bypass, SD/HD rate indicator, output mute, and lock detect indicator.

Additional features of the LMH0346 can be accessed through special SMBus register access. Care must be taken when controlling the device using the registers as normal pin-control functionality of the device is disabled in this mode.

This application report includes an overview of SMBus, followed by details on how to enable SMBus access on the LMH0346. Information on using the LMH0346 SMBus to accomplish the following three useful tasks is included at the end of the document:

- Read back the detected data rate (2.97 Gbps, 1.485 Gbps, or 270 Mbps)

- · Modify the CDR loop bandwidth

- Disable the second CML output driver to minimize power

#### 2 SMBus Overview

The System Management Bus (SMBus) is a two-wire serial interface through which various system component chips can communicate with each other and with the rest of the system.

The SMBus is controlled through two lines: a clock line (SCL) and a data line (SDA). SCL is the clock output from the master (i.e., FPGA host) to the slave devices on the bus. SDA is the bidirectional data signal between the host and the slave devices on the bus. SCL and SDA are both open drain and require external pullup resistors. (On the LMH0346, the BYPASS/AUTO BYPASS pin is used for SDA, and the OUTPUT MUTE pin is used for SCL.)

Most microcontrollers support SMBus. Please refer to the SMBus Specification version 2.0 for implementation details.

#### 2.1 Transfer of Data via the SMBus

During normal operation the data on SDA must be stable during the time when SCL is high. Data can only change state when SCL is low. Two unique states define the message START and STOP conditions:

START: A high-to-low transition on SDA while SCL is high indicates a message START condition.

**STOP:** A low-to-high transition on SDA while SCL is high indicates a message STOP condition.

The host generates START and STOP patterns at the beginning and end of each transaction.

#### 2.2 SMBus Transactions

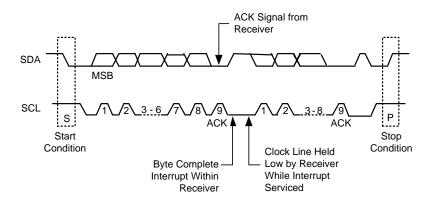

Each byte (8 bits) is transferred MSB first, followed by an acknowledge bit. The acknowledge bit is "0" for acknowledge (ACK), or "1" for not acknowledge (NACK). The host generates nine clock pulses for each byte transfer, and the ninth clock pulse constitutes the acknowledge cycle. The transmitter releases the SDA line during the acknowledge clock cycle to allow the receiver to send the ACK (or NACK). See Figure 1.

www.ti.com SMBus Overview

Figure 1. SMBus Transaction Format

## 2.3 Writing a Register

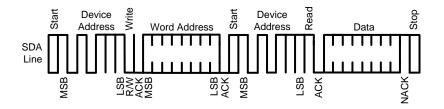

To write a register, the following protocol is used (refer to Figure 2 and also see the SMBus 2.0 specification).

- 1. The host drives a START condition, the 7-bit SMBus address, and a "0" indicating a WRITE.

- 2. The device (slave) drives the ACK bit ("0").

- 3. The host drives the 8-bit Register Address.

- 4. The device drives an ACK bit ("0").

- 5. The host drives the 8-bit data byte.

- 6. The device drives an ACK bit ("0").

- 7. The host drives a STOP condition.

Figure 2. SMBus Register Write

## 2.4 Reading a Register

To read a register, the following protocol is used (refer to Figure 3 and also see the SMBus 2.0 specification).

- 1. The host drives a START condition, the 7-bit SMBus address, and a "0" indicating a WRITE.

- 2. The device (slave) drives the ACK bit ("0").

- 3. The host drives the 8-bit Register Address.

- 4. The device drives an ACK bit ("0").

- 5. The host drives a START condition.

- 6. The host drives the 7-bit SMBus Address, and a "1" indicating a READ.

- 7. The device drives an ACK bit ("0").

- 8. The device drives the 8-bit data value (register contents).

- 9. The host drives a NACK bit ("1") indicating end of the READ transfer.

10. The host drives a STOP condition.

Figure 3. SMBus Register Read

## 3 Enabling SMBus Access for the LMH0346

The LMH0346 SMBus registers were intended for production test control and device monitoring. These registers are not documented in the LMH0346 datasheet and their performance has not been characterized. However, some of these registers are useful in certain applications.

Please note the following important points about using the LMH0346 SMBus mode:

- A dedicated SMBus is required per reclocker.

- The LMH0346 SMBus pins must be driven from a 3.3V source (they are not 5V compliant).

- When the SMBus mode is enabled, the hardware power-on-reset function in the LMH0346 is disabled. When using the LMH0346 SMBus features, the registers and state machine must be initialized by first powering up in Auto Rate mode and then switching to SMBus mode.

- The 7-bit address for the LMH0346 is **57h**. The LSB is set to 0b for a WRITE and 1b for a READ, so the 8-bit default address for a WRITE is AEh and the 8-bit default address for a READ is AFh.

The following steps explain how to enable SMBus access for the LMH0346:

- Connect RATE0 pin to VCC (nominally 3.3V), while maintaining the ability to drive this pin high or low to properly reset the device.

- Connect RATE1 pin to VCC (nominally 3.3V), while maintaining the ability to drive this pin high or low to properly reset the device.

- Connect SCO\_EN pin to ground. (Note that enabling the serial clock output while using SMBus access requires a register bit to be set.)

- Access SDA (SMBus serial data input/output) through the BYPASS/AUTO BYPASS pin of the LMH0346. This pin requires an external 10 kΩ pullup resistor to VCC. Voltage levels are LVCMOS.

- Access SCL (SMBus serial clock input) through the OUTPUT MUTE pin of the LMH0346. This pin requires an external 10 kΩ pullup resistor to VCC. Voltage levels are LVCMOS

- Power up the LMH0346 in Auto Rate mode (RATE0=0, RATE1=0) and then change it into SMBus mode (RATE0=1, RATE1=1) after power up. The LMH0346 should be held in Auto Rate mode for approximately 300 ms prior to entering SMBus mode. This procedure ensures a proper reset of the SMBus registers and reclocker state machine.

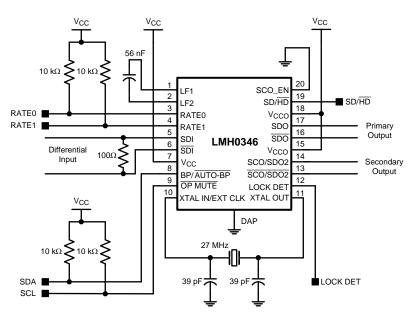

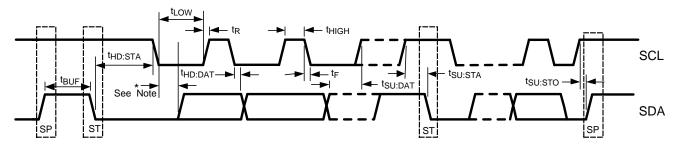

Figure 4 shows the SMBus implementation for the 20-pin e-TSSOP version of the LMH0346. Table 1 and Figure 5 show the recommended SMBus Timing.

Figure 4. LMH0346 SMBus Implementation

**Table 1. Recommended SMBus Timing**

| Symbol              | Parameter                                                                                    | Min | Тур | Max  | Units |

|---------------------|----------------------------------------------------------------------------------------------|-----|-----|------|-------|

| f <sub>SMB</sub>    | Bus Operating Frequency                                                                      | 10  |     | 100  | kHz   |

| t <sub>BUF</sub>    | Bus free time between Stop and Start Condition                                               | 4.7 |     |      | μs    |

| t <sub>HD:STA</sub> | Hold time after (repeated) Start Condition. After this period, the first clock is generated. | 4.0 |     |      | μs    |

| t <sub>SU:STA</sub> | Repeated Start Condition setup time                                                          | 4.7 |     |      | μs    |

| t <sub>SU:STO</sub> | Stop Condition setup time                                                                    | 4.0 |     |      | μs    |

| t <sub>HD:DAT</sub> | Data hold time                                                                               | 300 |     |      | ns    |

| t <sub>SU:DAT</sub> | Data setup time                                                                              | 250 |     |      | ns    |

| t <sub>LOW</sub>    | Clock low period                                                                             | 4.7 |     |      | μs    |

| t <sub>HIGH</sub>   | Clock high period                                                                            | 4.0 |     | 50   | μs    |

| t <sub>F</sub>      | Clock/Data Fall Time                                                                         |     |     | 300  | ns    |

| t <sub>R</sub>      | Clock/Data Rise Time                                                                         |     |     | 1000 | ns    |

| t <sub>POR</sub>    | Time in which device must be operational after power on                                      |     |     | 500  | ms    |

<sup>\*</sup> Note: SDA and SCL should be held low for 2 µs after a Start condition to properly de-assert the Start indicator.

Figure 5. SMBus Timing Parameters

## 4 Description of a Subset of LMH0346 Registers

NOTE:

When writing to the LMH0346 registers, RSVD bits must be written with the indicated default values. Only the non-reserved register bits should be modified.

## 4.1 Register 00h – Basic Control

Register 00h is used to invoke the pin control modes that aren't accessible when the SMBus is enabled, as shown in Table 2.

Table 2. Register 00h - Basic Control

| Address | R/W | Bits | Name   | Default | Description                                                                                                                                                       |

|---------|-----|------|--------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00h     | R/W | 7:6  | RATE   | 00      | Rate select (bit 6 = RATE0, bit 7 = RATE1).<br>00: Auto rate select (default)<br>01: 270 Mbps.<br>10: 1.483, 1.485, 2.967, 2.97 Gbps.<br>11: 2.967, 2.97 Gbps.    |

|         |     | 5:3  | RSVD   | 000     | Reserved. These bits must always be 000.                                                                                                                          |

|         |     | 2    | BYPASS | 0       | Bypass/Auto Bypass.  0: Normal operation. Reclocking automatically bypassed when reclocker is unlocked or data rate is not supported.  1: Reclocking is bypassed. |

|         |     | 1    | OPMUTE | 0       | Output Mute. 0: Normal operation (outputs not muted). 1: Outputs are muted.                                                                                       |

|         |     | 0    | SCO_EN | 0       | SCO Enable. 0: SCO/SDO2 output is data. 1: SCO/SDO2 output is clock.                                                                                              |

Bits [7:6] can be controlled to force the rate detection mode.

When SMBus mode is used, the SCO\_EN and OUTPUT MUTE pins are not available. In order to observe the serial clock, bit 0 must be set high. Similarly, in order to mute the outputs, bit 1 must be set high.

## 4.2 Register 0Eh – Modifying the CDR Loop Bandwidth via the Charge Pump Current

The default settings of the LMH0346 registers have been set to minimize output jitter while meeting SMPTE 424M specifications for jitter tolerance. It may be useful in some applications to increase the loop bandwidth of the CDR to extend input jitter tolerance to higher frequencies. Register 0Eh can be used to increase the LMH0346's CDR charge pump current, as shown in Table 3. Increasing the charge pump current will, in turn, increase the loop bandwidth.

Figure 6 and Figure 7 show 2.97 Gbps Jitter Transfer and Jitter Tolerance, respectively, for the LMH0346 with different charge pump current settings.

| Address | R/W | Bits | Name           | Default | Description                                                                                                                                                                                                                       |

|---------|-----|------|----------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0Eh     | R/W | 7:4  | RSVD           | 0001    | Reserved. These bits must always be 0001.                                                                                                                                                                                         |

|         |     | 3:2  | CHARGE<br>PUMP | 00      | Charge Pump current. 00: Current = 25 μA, CDR BW @ 2.97 Gbps = 2.7 MHz. 01: Current = 50 μA, CDR BW @ 2.97 Gbps = 5.3 MHz. 10: Current = 75 μA, CDR BW @ 2.97 Gbps = 7.8 MHz. 11: Current = 100 μA, CDR BW @ 2.97 Gbps = 9.5 MHz. |

|         |     | 1:0  | RSVD           | 11      | Reserved. These bits must always be 11.                                                                                                                                                                                           |

Table 3. Register 0Eh - Modifying the CDR Loop Bandwidth

Figure 6. LMH0346 2.97 Gbps Jitter Transfer with Different Charge Pump Current Settings

Figure 7. LMH0346 2.97 Gbps Jitter Tolerance with Different Charge Pump Current Settings

### 4.3 Register 10h – Powering Down the SDO and SCO/SDO2 CML Drivers to Save Power

The LMH0346 has two separate CML output drivers. These drivers can be independently powered down if not required in the system (that is, if the system needs only one CML driver), as shown in Table 4. Approximate power savings is 24 mA/buffer.

Table 4. Register 10h – Powering Down the SDO and SCO/SDO2 CML Drivers

| Address | R/W | Bits | Name           | Default | Description                                                                                        |

|---------|-----|------|----------------|---------|----------------------------------------------------------------------------------------------------|

| 10h     | R/W | 7:3  | RSVD           | 10000   | Reserved. These bits must always be 10000.                                                         |

|         |     | 2    | PD SDO         | 0       | Power down SDO output driver. 0: Normal operation. 1: SDO output driver is powered down.           |

|         |     | 1    | PD<br>SCO/SDO2 | 0       | Power down SCO/SDO2 output driver. 0: Normal operation. 1: SCO/SDO2 output driver is powered down. |

|         |     | 0    | RSVD           | 0       | Reserved. This bit must always be 0.                                                               |

# 4.4 Register 32h – Detecting the Locked Rate and Distinguishing Between 3G, HD, and SD

Register 32h can be read to determine the status of the lock detection state machine – and which data rate has been detected. While acquiring lock at a given frequency, the LMH0346 will automatically cycle through the following states:

- 1. Coarse acquisition (adjusts VCO center frequency with the control voltage held to mid-supply).

- 2. Frequency acquisition (tunes the VCO to a multiple of the 27 MHz crystal frequency).

- 3. Phase acquisition (tunes the VCO phase to optimally clock the data input to the LMH0346).

- 4. Locked.

The register values are shown in Table 5.

Table 5. Register 32h - Reading Back the Detected Rate

| Address | R/W | Bits | Name  | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|-----|------|-------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32h     | R   | 7:4  | STATE | 000     | Status of Lock Detection State Machine. 0000, 0001, 0010, 0011: Reserved. 0100: Rate = 270 Mbps, Coarse acquisition. 0101: Rate = 270 Mbps, Frequency acquisition. 0110: Rate = 270 Mbps, Phase acquisition. 0111: Rate = 270 Mbps, LOCKED. 1000: Rate = 1.483/1.485 Gbps, Coarse acquisition. 1001: Rate = 1.483/1.485 Gbps, Frequency acquisition. 1010: Rate = 1.483/1.485 Gbps, Phase acquisition. 1011: Rate = 1.483/1.485 Gbps, LOCKED. 1100: Rate = 2.967/2.97 Gbps, Coarse acquisition. 1101: Rate = 2.967/2.97 Gbps, Frequency acquisition. 1110: Rate = 2.967/2.97 Gbps, Phase acquisition. 1111: Rate = 2.967/2.97 Gbps, LOCKED. |

|         |     | 3:0  | RSVD  | 0000    | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

#### Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers <u>microcontroller.ti.com</u> Video and Imaging <u>www.ti.com/video</u>

RFID www.ti-rfid.com

OMAP Applications Processors <u>www.ti.com/omap</u> TI E2E Community <u>e2e.ti.com</u>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>