# AN-1538 Interfacing Texas Instruments DS90CR218A and LM98714

#### **ABSTRACT**

This application report examines the issues that system designers may face when interfacing the Texas Instruments DS90CR218A and LM98714. It also offers guidance and solutions on solving these issues that will deliver for a reliable and cost effective LVDS data link.

|   | Contents                                  |   |

|---|-------------------------------------------|---|

| 1 | Introduction                              | 2 |

| 2 | Advantages of LVDS                        | 3 |

| 3 | System Adjustment                         | 3 |

|   | 3.1 Setup and Hold Time Adjustment        | 3 |

|   | 3.2 Receiver Skew Margin Calculation      | 4 |

|   | 3.3 Timing Margin                         |   |

| 4 | PCB Layout Guideline                      |   |

|   | 4.1 General Guideline                     |   |

|   | 4.2 Device-Specific Recommendation        |   |

| 5 | References                                | 6 |

|   | List of Figures                           |   |

| 1 | System Block Diagram                      | 2 |

| 2 | DS90CR218A (Receiver) Setup and Hold Time |   |

| 3 | DS90CR218A (Receiver) Skew Margin         |   |

All trademarks are the property of their respective owners.

Introduction www.ti.com

#### 1 Introduction

Digital image processing systems like color copier, scanner, and so on. involve moving large amount of data between the sensor controller unit to the image processor across a 60 to 150 cm cable in an EMI efficient fashion.

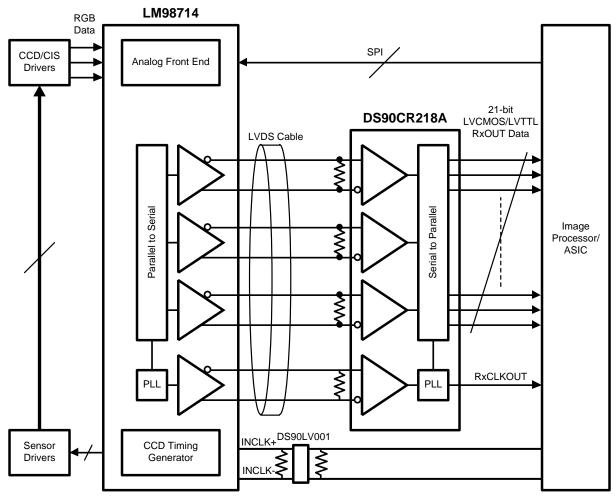

Texas Instruments DS90CR218A, a LVDS channel-link receiver together with LM98714, a 16-Bit, 45 MSPS signal processing AFE (Analog Front End) provide a high performance solution to digitize the CCD/CIS sensor outputs, process it and make it available to the image processor. See Figure 1. The LVDS signaling and serialization of the LM98714 output solve the EMI and cable size problems associated with wide, high-speed LVCMOS/LVTTL interfaces operating from 12MHz to 45MHz.

While operating in LVDS mode, the LM98714 serializes the ADC output to 3 data channels with an additional line for the output clock. The DS90CR218A de-serializes the three input LVDS data streams into 21 bits of CMOS/TTL output data. The receiver supports an input clock frequency of 12 to 85 MHz.

Figure 1. System Block Diagram

www.ti.com Advantages of LVDS

## 2 Advantages of LVDS

LVDS (Low Voltage Differential Signaling) is a low swing, differential signaling technology which allows high speed data transmission while consuming significantly less power than conventional single ended technologies. In addition, LVDS is less susceptible to common-mode noise, and it also tends to radiate less noise than single-ended signals due to the canceling of magnetic fields. The current-mode driver used in LVDS is also less prone to ringing and switching spikes (switching noise), further reducing noise.

The current-mode, low swing, low noise nature of LVDS technology means data can be switched very quickly without creating noise and power consumption issues, which are common trade-offs for high-speed data transmission applications.

Both the LM98714 and DS90CR218A support LVDS signaling and together enable a low EMI system that is less prone to signal quality issues.

# 3 System Adjustment

# 3.1 Setup and Hold Time Adjustment

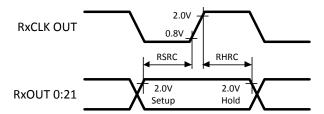

When designing for the parallel clock LVDS receiver, such as the DS90CR218A, the system designer must pay close attention to the relationship between the device's clock and its data. The DS90CR218A is a rising edge data strobe LVDS receiver. The rising edge refers to the internal shift clock that is used to strobe the incoming serial data and the outgoing parallel data. It is important to note that the setup time (RSRC) and hold time (RHRC) found on the device datasheet are referred to the rising edge of the clock, as shown in Figure 2. Hence, when interfacing the DS90CR218A output to an image processor/ASIC or any device, system designer must adjust the downlink device to allow for rising edge data strobe.

For the LVDS receiver input, no adjustment is needed because all of the Texas Instruments LVDS parallel clock transmitter and receiver, including the DS90CR218A and LM98714, use the rising edge of the clock as the reference edge for the LVDS link.

Figure 2. DS90CR218A (Receiver) Setup and Hold Time

System Adjustment www.ti.com

## 3.2 Receiver Skew Margin Calculation

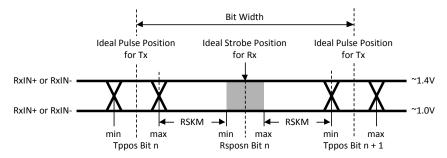

Receiver Skew Margin (RSKM) is defined as the valid data sampling region at the receiver inputs. It is one of the more important parameters that a system designer has to be aware of when designing with Channel-Link receivers. If the margin is less than the total sum of cable skew and jitter, it will limit the performance of the LVDS link and can lead to data sampling errors.

The RSKM specification consists of the receiver's internal PLL strobe positions (RSPOS), and the variation of Transmitter's output data pulse position relative to the output clock (TPPOS). The total margin after accounting for the minimum RSPOS and maximum TPPOS is the receiver input skew margin (RSKM), as shown in Figure 3.

Figure 3. DS90CR218A (Receiver) Skew Margin

RSKM can be calculated from the following equations:

$$RSKM = Rspos (min) - Tppos (max)$$

(1)

RSKM indicates how much skew and jitter the receiver can tolerate. RSKM must be greater than the sum of clock-to-data skew and all data and clock jitter to achieve error free operation.

**Clock-to-data Skew.** Clock-to-data skew should include skew found within the cable pairs and skew from PCB trace.

**Cycle-to-Cycle Jitter**. It is important to account for the input clock cycle-to-cycle jitter because the receiver uses the previous clock cycle to define the sampling window of the current data cycle. Therefore, the receiver sampling window may vary depending on the amount of cycle-to-cycle jitter present on the clock. The LM98714 and all of Texas Instruments Channel-Link Transmitters have been designed to help reduce cycle-to-cycle jitter; hence the cycle-to-cycle jitter at the Transmitter's input clock will not pass directly to the receiver. However, to optimize performance when designing with Channel-Link devices, cycle-to-cycle jitter on the clock should be minimized.

**Data Jitter, ISI, Cross-talk.** When RSKM is specified for a chipset, then the data jitter from the transmitter outputs is already accounted for; therefore, only jitter contributed by the interconnect, such as ISI, and crosstalk induced by the cable and connector should be considered. When the RSKM specification references "Ideal" transmitter pulse positions, then the calculation for the remaining margin should include variances in the transmitter pulse position (typically the worst case number is used), data jitter, ISI, and crosstalk from the cable/connector fixture.

For more information on Channel-Link's RSKM calculation, please refer to the *AN-1059 1059 High Speed Transmission with LVDS Link Devices Application Report* (SNLA050) and the *Channel Link I Design Guide* (SNLA167).

www.ti.com PCB Layout Guideline

## 3.3 Timing Margin

Note that the DS90CR218A datasheet (reference [4]) RSKM specification references Ideal Pulse Positions (Tppos Ideal), so when calculating for RSKM, the Transmitter's pulse position and data jitter must be included.

The following table shows the typical RSKM of the DS90CR218A when using the LM98714 as a Transmitter at 12MHz.

**Table 1. Receiver Skew Margin**

| Symbol | Parameter                                        | Тур      |

|--------|--------------------------------------------------|----------|

| RSKM   | Receiver Skew Margin with LM98714 as Transmitter | 0.968 ns |

## 4 PCB Layout Guideline

To optimize the performance of the DS90CR218A and LM98714, good high-speed PCB layout techniques should be used. This section provides the system designer some general design recommendations and guidelines for PCB layout.

### 4.1 General Guideline

- Place the components so that PCB traces do not take a lot of turns, corners, and pass through PCB vias when going from one component to another.

- For LVDS or any other high-speed differential signaling device, keep transmitters and receivers as close to the connector as possible.

- Separate high frequency or high level inputs and outputs to minimize unwanted stray noise pickup, feedback, and interference. It is best to put any fast edge rate CMOS/TTL and LVDS signals on a different layer(s).

- Use at least 4 PCB board layers: LVDS signals, ground, power, TTL/CMOS signals. Dedicating planes for power and ground are typically required for high-speed system design.

- Power system performance may be greatly improved by using thin dielectrics (4 to 10 mils) for power/ground sandwich; this will create an excellent high frequency bypass capacitance, making the value and placement of external bypass capacitors less critical.

- External bypass capacitors should be placed as close as possible to the power pins to minimize parasitic effect. One or two multi-layer ceramic (MLC) surface mount capacitors (0.1μF or 0.01μF) in parallel should be used between each power pin and ground pin for best results.

- Good power supply design practice also includes a bulk capacitor at the point of power entry. This is typically in the range of 50 μF to 100 μF and will smooth low frequency noise.

## 4.2 Device-Specific Recommendation

General device-specific bypassing recommendations are provided.

#### 4.2.1 DS90CR218A

**Pair-to-Pair Skew.** Always minimize pair-to-pair skew on LVDS inputs; particularly, the skew between LVDS data and clock lines. Large skew between LVDS clock and data pairs can cause mis-sampling of data. Make sure pair-to-pair skew meets RSKM requirements.

**LVDS Traces.** LVDS pairs should be closely coupled and designed for  $100\Omega$  differential impedance. Route the differential pair traces as close together as possible and as soon as they leave the IC. This helps to eliminate reflections and ensures that the majority of common-mode noise is rejected.

**LVDS Termination.** LVDS termination is required for DS90CR218A. Choose the termination resistor value to match the loaded differential impedance of the transmission line. The value of the termination is typically  $100\Omega$ . Place termination resistors as close as possible to the receiver inputs or end of the transmission lines.

References www.ti.com

**PLL Supply.** The DS90CR218A requires a clean power supply – less than 100mV noise peak-to-peak. PLL VCC noise in the frequency range of 200 kHz to 3 MHz can increase jitter and reduce noise margin; therefore, a CRC or CLC notch filter may be required to filter out noise in this spectrum.

**LVDS Supply.** Typically, a 0.1  $\mu$ F capacitor is sufficient for the LVDS power supply pins. If space is available, a 0.01  $\mu$ F capacitor (Place smaller value capacitors closer to the device) may be used in parallel for additional high-frequency filtering. Connect the LVDS ground to the cable ground to provide a return path for any common (even) mode currents.

**Digital Supply.** Good digital supply filtering is critical for the DS90CR218A when multiple outputs switch at the same time (simultaneous switching noise). An estimate of local capacitance required indicates a minimum of 34 nF is required. Rounding up to a standard value, 0.1  $\mu$ F is selected for each Digital power pin.

#### 4.2.2 LM98714

**PLL Setting.** The default settings for the LM98714's PLL is optimized around the middle of its operating frequency range. This can be tuned to better match the operating frequency of the application in order to improve the system skew margin. So, while operating at the 12 MHz frequency the PLL setting register (Page 0, Main Configuration Register 3, Bit[2:0]) can be set to low frequency mode (3'b000). The default for this register is 3'b111. Please refer to the LM98714 datasheet (reference [3]) for additional details on this setting.

#### 5 References

- 1. Channel Link I Design Guide (SNLA167)

- 2. AN-1059 1059 High Speed Transmission with LVDS Link Devices Application Report (SNLA050)

- 3. LM98714 Three Channel, 16-Bit, 45 MSPS Digital Copier Analog Front End with Integrated CCD/CIS Sensor Timing Generator and LVDS Output (SNAS254)

- 4. DS90CR218A +3.3V Rising Edge Data Strobe LVDS 21-Bit Channel Link 12 MHz to 85 MHz (SNLS054)

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers <u>microcontroller.ti.com</u> Video and Imaging <u>www.ti.com/video</u>

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>