# Interfacing TMS320C5x and Parallel Stereo CODEC with other TMS320 DSP Considerations

APPLICATION REPORT: SPRA097

Mathew George, Jr

Digital Signal Processing Solutions December 1997

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain application using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1997, Texas Instruments Incorporated

#### TRADEMARKS

TI is a trademark of Texas Instruments Incorporated.

Other brands and names are the property of their respective owners.

#### CONTACT INFORMATION

| US TMS320 HOTLINE | (281) 274-2320 |

|-------------------|----------------|

| US TMS320 FAX     | (281) 274-2324 |

| US TMS320 BBS     | (281) 274-2323 |

| US TMS320 email   | dsph@ti.com    |

| Abstract                                                                | 7  |

|-------------------------------------------------------------------------|----|

| Product Support                                                         | 8  |

| World Wide Web                                                          |    |

| Email                                                                   | 8  |

| INTRODUCTION                                                            | 9  |

| SYSTEM CONFIGURATION                                                    | 10 |

| System Modes                                                            | 10 |

| System Block Diagram                                                    | 11 |

| System Registers and Bits                                               | 13 |

| SYSTEM OPERATION                                                        | 17 |

| Mode 1 Programmed I/O                                                   | 17 |

| Mode 2 Interrupt Driven                                                 |    |

| Mode 3 Stereo Codec DMA                                                 |    |

| SYSTEM CONSIDERATIONS                                                   | 24 |

| FIFO25                                                                  |    |

| External DMA                                                            |    |

| Serial Codec with DSP "DMA"                                             |    |

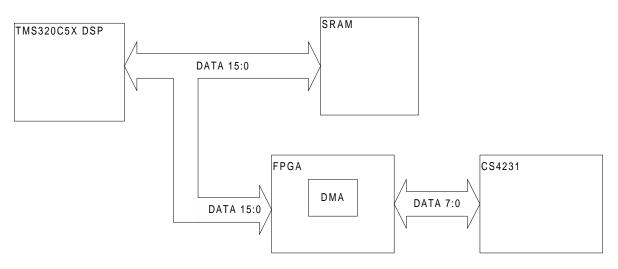

| Parallel Codec with Separate Bus and External DMA Optional              |    |

| CONCLUSION                                                              | 29 |

| REFERENCES                                                              | 30 |

| Appendix A - Code                                                       | 31 |

| Mode 1 - PIO Digital Loopback                                           | 31 |

| Mode 2 - Interrupt Driven Digital Loopback                              |    |

| Mode 3 - Stereo Codec DMA Digital Loopback                              | 39 |

| Mode 3 - Stereo Codec DMA Digital Loopback with Intermediate Buffer and |    |

| Interrupts                                                              |    |

| Appendix B - Stereo Codec DMA Structure                                 |    |

| Stereo Codec DMA Schematic                                              |    |

| Stereo Codec DMA FSM's                                                  | 49 |

## Contents

## Figures

| Figure 2.       Mode 1 - PIO Connection of TMS320C5x Parallel Stereo Codec                                                                                                                                                                                                                                                                                                                                                                                      | Figure 1. | Connection of TMS320C5x DSP to Parallel Stereo Codec                  | .12 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------------------------------------------------------|-----|

| Figure 4.Mode 3 - DMA Controller Connection of TMS320C5x Parallel Stereo Codec21Figure 5.Mode 3 - Test Code in Appendix A (Digital Loopback with DMA)                                                                                                                                                                                                                                                                                                           | Figure 2. | Mode 1 - PIO Connection of TMS320C5x Parallel Stereo Codec            | .18 |

| Figure 5.       Mode 3 - Test Code in Appendix A (Digital Loopback with DMA)       23         Figure 6.       Basic DSP/SRAM/Codec System       24         Figure 7.       FIFO DSP/SRAM/Codec System       25         Figure 8.       External DMA DSP/SRAM/Codec System       26         Figure 9.       DSP with "DMA"/SRAM/Serial Codec System       27         Figure 10.       DSP/SRAM/Parallel Codec with Separate Bus and External DMA System       28 | Figure 3. | Mode 2 - Interrupt Connection of TMS320C5x Parallel Stereo Codec      | .19 |

| Figure 6. Basic DSP/SRAM/Codec System       24         Figure 7. FIFO DSP/SRAM/Codec System       25         Figure 8. External DMA DSP/SRAM/Codec System       26         Figure 9. DSP with "DMA"/SRAM/Serial Codec System       27         Figure 10. DSP/SRAM/Parallel Codec with Separate Bus and External DMA System       28                                                                                                                             | Figure 4. | Mode 3 - DMA Controller Connection of TMS320C5x Parallel Stereo Codec | .21 |

| Figure 7. FIFO DSP/SRAM/Codec System       25         Figure 8. External DMA DSP/SRAM/Codec System       26         Figure 9. DSP with "DMA"/SRAM/Serial Codec System       27         Figure 10. DSP/SRAM/Parallel Codec with Separate Bus and External DMA System       28                                                                                                                                                                                    | Figure 5. | Mode 3 - Test Code in Appendix A (Digital Loopback with DMA)          | .23 |

| Figure 8. External DMA DSP/SRAM/Codec System                                                                                                                                                                                                                                                                                                                                                                                                                    | Figure 6. | Basic DSP/SRAM/Codec System                                           | .24 |

| Figure 9. DSP with "DMA"/SRAM/Serial Codec System27<br>Figure 10. DSP/SRAM/Parallel Codec with Separate Bus and External DMA System28                                                                                                                                                                                                                                                                                                                           | Figure 7. | FIFO DSP/SRAM/Codec System                                            | .25 |

| Figure 10. DSP/SRAM/Parallel Codec with Separate Bus and External DMA System28                                                                                                                                                                                                                                                                                                                                                                                  | Figure 8. | External DMA DSP/SRAM/Codec System                                    | .26 |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Figure 9. | DSP with "DMA"/SRAM/Serial Codec System                               | .27 |

| Figure 11. DMA Controller for Parallel Codec                                                                                                                                                                                                                                                                                                                                                                                                                    | Figure 10 | . DSP/SRAM/Parallel Codec with Separate Bus and External DMA System   | .28 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Figure 11 | . DMA Controller for Parallel Codec                                   | .48 |

## Tables

| Table 1. | Smart Registers                                    | 13 |

|----------|----------------------------------------------------|----|

| Table 2. | PC Status Register Definition                      | 13 |

| Table 3. | PCSR Explanation                                   | 14 |

| Table 4. | Bit I/O Register Definition                        | 14 |

| Table 5. | Bit I/O Explanation                                | 15 |

| Table 6. | DSP Control Register Bit Definitions               | 15 |

| Table 7. | SYSCFG Explanation                                 | 15 |

| Table 8. | Address Receive Register (ARR) Bit Definitions     | 16 |

| Table 9. | Receive Buffer (BXR) Size Register Bit Definitions | 16 |

| Table 10 | . Address Transmit Register (AXR) Bit Definitions: | 16 |

| Table 11 | . Transmit Buffer (BXK) Size Register:             | 16 |

|          |                                                    |    |

# Interfacing TMS320C5x and Parallel Stereo CODEC with other TMS320 DSP Considerations

#### Abstract

The CS4231 is a 16 bit stereo codec chip with various features, such as multiple analog inputs and outputs, mixing, and gain capabilities, that make them ideal for computer sound applications [1][2]. The digital interface consists of a parallel 8-bit bus and is meant to directly connect to a PC (ISA/EISA) interface. Since it is a glueless interface to a PC bus, it looks a bit different from a TMS320C5x or other TMS320 DSPs with asynchronous memory interface. This Application Note describes an optimum interface to a TMS320C5x DSP. Note that other TMS320 DSP asynchronous buses are very similar and most of the interface described here will also apply to any TMS320 DSP system. In this implementation the TMS320C5x and codec share the same bus with SRAM. This tradeoff keeps pin count and thus cost down, at the cost of performance. A separate codec bus mapped into the DSP's memory or I/O space would make the system more efficient and is briefly described at the end of this Application Note along with other system considerations.

## **Product Support**

#### World Wide Web

Our World Wide Web site at www.ti.com contains the most up to date product information, revisions, and additions. Users registering with TI&ME can build custom information pages and receive new product updates automatically via email.

#### Email

Ť

For technical issues or clarification on switching products, please send a detailed email to dsph@ti.com. Questions receive prompt attention and are usually answered within one business day.

### INTRODUCTION

The CS4231 is a 16 bit stereo codec chip with various features, such as multiple analog inputs and outputs, mixing, and gain capabilities, that make them ideal for computer sound applications [1][2]. The digital interface consists of a parallel 8-bit bus and is meant to directly connect to a PC (ISA/EISA) interface. Since it is a glueless interface to a PC bus, it looks a bit different from a TMS320C5x or other TMS320 DSPs with asynchronous memory interface. This Application Note describes an optimum interface to a TMS320C5x DSP. Note that other TMS320 DSP asynchronous buses are very similar and most of the interface described here will also apply to any TMS320 DSP system. In this implementation the TMS320C5x and codec share the same bus with SRAM. This tradeoff keeps pin count and thus cost down, at the cost of performance. A separate codec bus mapped into the DSP's memory or I/O space would make the system more efficient and is briefly described at the end of this Application Note along with other system considerations.

## SYSTEM CONFIGURATION

This TMS320C5x implementation was done with a TPC1280 FPGA acting as the glue logic. It was meant to be a prototype for an ASIC/cDSP type system with minimum hardware and concurrent playback and capture. Thus the system was designed within these parameters, assuming a roadmap to ASIC/cDSP. There are a variety of other ways that this interface could be accomplished if discrete logic or an FPGA with FIFOs will be in the final system. Thus some aspects could be more efficient using a faster ASIC or even discrete logic or PLDs. The needs of the system seem to differ based on the DSP software/OS to be used. As much flexibility was put into this system as possible (such as polled and interrupt modes) to allow determination by the programmer based on the specific system.

#### System Modes

Thus the following three progressive levels of interface were implemented:

- Programmed I/O Necessary for initialization of the codec, but slow in actual operation due to the use of bit polling for capture and playback. Uses the least amount of pins and the DSP does all the work. This is not an efficient configuration.

- 2) Interrupt driven Various possible configurations, but the general idea is that the DSP is somehow interrupted by the codec for capture and playback. It is faster than mode 1, but uses more pins and logic. Again the DSP does all the work. In this implementation, the number of interrupt pins used was minimized as a tradeoff for more software protocol. This mode is *probably* more efficient if classic assembly-level, lowoverhead DSP code is used.

3) Stereo Codec DMA - Again various configurations, but the general idea is that the DSP is put in -HOLD (i.e. taken off the bus) based on an interrupt. Then external logic (i.e. a DMA controller implemented in the FPGA and modeled after the Buffered Serial Port seen in the TMS320C56/57 and TMS320C54x DSPs [7]) will copy the data for capture and playback between the DSP and memory. Mode 3 needs more pins and is faster than mode 1. (Again, as in mode 2, the number of interrupt pins was minimized). The DSP is oblivious to this task until an interrupt tells it that input or output buffers in memory are full and need to be processed. But there can be some overhead if the DSP needs to access external memory [3]. Mode 3 uses the same number of pins as mode 2 and (regarding speed) is probably more efficient, if a less-classic, C-based multi-tasking operating system, higher-overhead DSP code is used.

#### NOTE:

Note that in mode 1, the codec is placed in the PIO mode and uses the command interface. The command interface is there by default in a polled fashion and no additional pins are required. But while in modes 2 and 3, the DSP is in DMA mode and uses DMA pins (PDRQ/CDRQ and -PDAK/-CDAK). Note that these modes may be mixed, using one for playback and the other for capture if so desired.

#### System Block Diagram

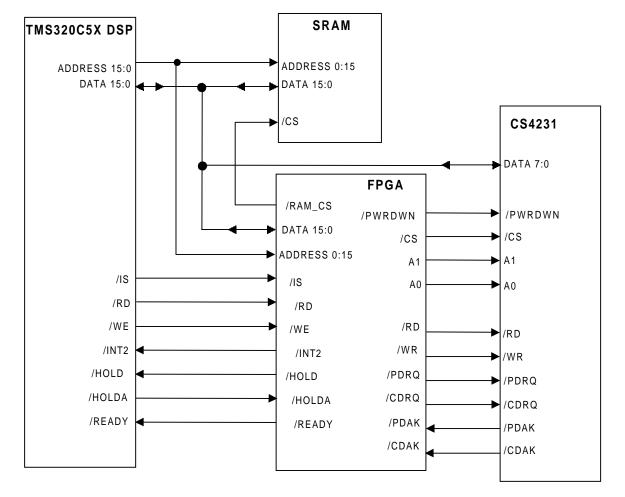

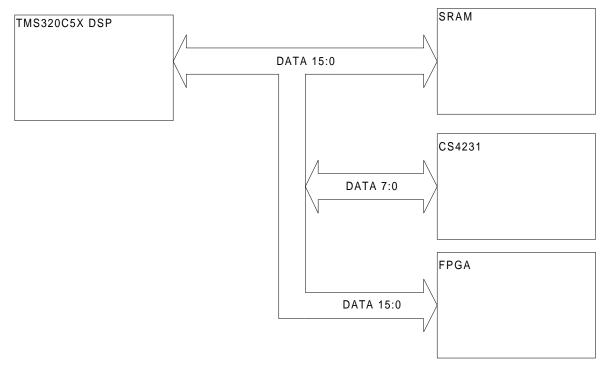

The following block diagram shows how the digital aspects of how the DSP/codec system appears (Figure 1). All three modes are supported here. Some pins may be eliminated if just a particular mode is needed. These are described in more detail in the System Operation section.

Figure 1. Connection of TMS320C5x DSP to Parallel Stereo Codec

Three devices are connected to the TMS320C5x external bus: the SRAM, the codec and an FPGA. The SRAM is usually the most used, since the program is running from there. It is mapped into the program and/or data space (dual mapped in this case with a zero decode logic [4]). The four codec parallel Interface Registers R0-R3 are mapped into the DSP I/O space from 58h-5Bh. Various FPGA registers that control the codec (and other things) are mapped into DSP I/O space 50h-54h and 5Ch-5Fh.

Table 1 describes the registers used in this implementation. Much of this comes from the original implementation and can be ignored. Registers with any codec relevant bits are in bold (for a full description of these registers please see reference [5]):

| Register | Memory Addre         | Default        | A     | ccess |          |

|----------|----------------------|----------------|-------|-------|----------|

|          | PCMCIA Common Memory | 'C5x I/O Space | Value | PC    | DSP      |

| SIGR     | 000400h              |                | XXXX  | R/W   |          |

| Reserved | 000000h              |                |       |       |          |

| DSPCR    | 000002h              |                | 0108h | R/W   |          |

| DSPSR    | 000004h              |                | 0xxxh | R     |          |

| DSPTXD   | 000006h              | 0050h          | 0000h | R     | W        |

| DSPRXD   | 000008h              | 0051h          | 0000h | W     | R        |

| Reserved | 00000Ah-00000Fh      |                |       |       |          |

| PCSR     |                      | 0052h          | 000xh |       | R        |

| BIOR     |                      | 0053h          | 000xh |       | R/W    R |

| SYSCFG   |                      | 0054h          | 0080h |       | R/W      |

| Reserved |                      | 0055h-0057h    |       |       |          |

| CODEC R0 |                      | 0058h          | xx80h |       | R/W      |

| CODEC R1 |                      | 0059h          | xx80h |       | R/W      |

| CODEC R2 |                      | 005Ah          | xx80h |       | R/W      |

| CODEC R3 |                      | 005Bh          | xx80h |       | R/W      |

| ARR      |                      | 005Ch          | 0000h |       | R/W      |

| BKR      |                      | 005Dh          | 0000h |       | R/W      |

| AXR      |                      | 005Eh          | 0000h |       | R/W      |

| BKX      |                      | 005Fh          | xx80h |       | R/W      |

Table 1. Smart Registers

The codec relevant bits are described in the following few Tables 2, 3, 4, 5, 6, 7, 8, 9, 10, and 11. Notice that they are in bold; please ignore the other bits. (Again for a full description of these all these registers and bits please see [5]). Note that some of the bits used for Mode 3 were placed in PC accessible registers DSPCR/DSPSR so that capture/play data was in shared memory that the PC could directly access. But this has not been stressed in this application note. See [5] for more detail.

Table 2. PC Status Register Definition

| 15-8     | 7  | 6  | 5    | 4    | 3    | 2    | 1      | 0       |

|----------|----|----|------|------|------|------|--------|---------|

| Reserved | ХН | RH | XINT | RINT | PDQR | CDQR | RXFULL | TXEMPTY |

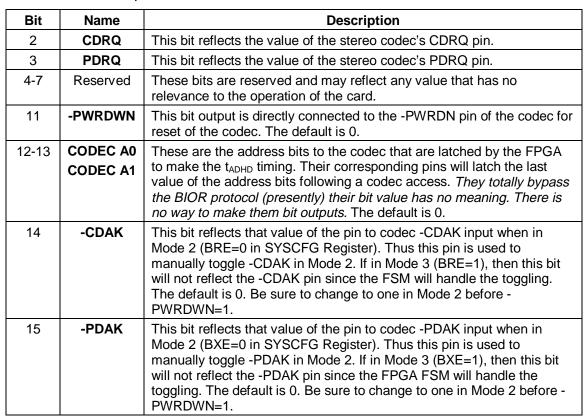

| D:4 | Nomo     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2   | CDRQ     | This bit reflects the value of the stereo codec's CDRQ pin                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3   | PDRQ     | This bit reflects the value of the stereo codec's PDRQ pin.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4   | RINT     | Receive (Capture) Interrupt: This bit becomes active when the DSP needs to service a capture interrupt. In Mode 2 (BRE=0) this means that the DSP must move data from the codec to memory, and the bit is cleared by doing enough of these moves to make CDRQ inactive. In Mode 3 (BRE=1) it means that the capture buffer from the codec is full and needs servicing by the DSP, and the bit is cleared when PCSR is read (So just do it once). The default value of this bit is 0.     |

| 5   | XINT     | Transmit (Playback) Interrupt: This bit becomes active when the DSP needs to service a playback interrupt. In Mode 2 (BXE=0) this means that the DSP must move data from memory to the codec, and the bit is cleared by doing enough of these moves to make PDRQ inactive. In Mode 3 (BXE=1) it means that the playback buffer from the codec is full and needs servicing by the DSP, and the bit is cleared when PCSR is read (So just do it once). The default value of this bit is 0. |

| 6   | RH       | (Receive Half) This bit indicates which half of the buffer has been processed. It should be considered a full flag so if RH=0 then the first half of the buffer (defined by ARR and BKR) is full and needs to be processed. The default value is 0.                                                                                                                                                                                                                                      |

| 7   | ХН       | (Transmit Half) This bit indicates which half of the buffer has been processed. It should be considered an empty flag so if RH=0 then the first half of the buffer (defined by AXR and BKX) is empty and needs to be filled. The default value is 0.                                                                                                                                                                                                                                     |

| 8   | Reserved | These bits are reserved and may reflect any value that has no relevance to the operation of the card.                                                                                                                                                                                                                                                                                                                                                                                    |

## Table 3. PCSR Explanation

| 15    | 14    | 13      | 12      | 11      | 10-8  | 7-4      | 3    | 2    | 1-0   |

|-------|-------|---------|---------|---------|-------|----------|------|------|-------|

| -PDAK | -CDAK | CODECA1 | CODECA0 | -PWRDWN | 02-00 | Reserved | PDRQ | CDRQ | I1-I0 |

| Table 5. | Bit I/O Explanation |

|----------|---------------------|

|----------|---------------------|

| Table 6. DS | P Control Register Bit Definitions |

|-------------|------------------------------------|

|-------------|------------------------------------|

| 15-12              | 11-8               | 7            | 6   | 5-4           | 3   | 2 | 1-0                   |

|--------------------|--------------------|--------------|-----|---------------|-----|---|-----------------------|

| EXCP7-4    EXDP3-0 | EXCP3-0    EXPP3-0 | CPD/<br>-SPD | BXE | GLODAP<br>1-0 | PHD |   | CLK<br>DIVISOR<br>1-0 |

Table 7. SYSCFG Explanation

| Bit | Name | Description                                                                                                                                                                                                                                        |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | BRE  | Receive Autobuffering Enable Bit. This bit enables the DMA for receive (capture) operation if BRE=1, i.e. Mode 3. This bit must be 0 for capture in mode 1 or 2 to occur. <i>Note that BRE is mutually exclusive to BXE.</i> The default is 0.     |

| 6   | BXE  | Transmit Autobuffering Enable Bit. This bit enables the DMA for transmit (playback) operation if BXE=1, i.e. Mode 3. This bit must be 0 for playback in mode 1 or 2 to occur. <i>Note that BXE is mutually exclusive to BRE.</i> The default is 0. |

Stereo Codec Registers R0-R3:

- □ See [1] or [2] for definition of:

- Index Address Register

- Indexed Data Register

- Status Register

- PIO Data Register

| 15-0                                              |  |

|---------------------------------------------------|--|

| Receive (Capture) Buffer 16-Bit Beginning Address |  |

The ARR 16 bit register (Table 8) gives the beginning address of the receive buffer for Stereo Codec external DMA.

Table 9. Receive Buffer (BXR) Size Register Bit Definitions

| 15-0                                           |  |

|------------------------------------------------|--|

| Receive (Capture) Buffer 16-Bit Ending Address |  |

This 16 bit register (Table 9) gives the ending address of the receive buffer for Stereo Codec external DMA. (Note that this is slightly different than the BSP spec because of limited combinatorial gates in the FPGA).

Table 10. Address Transmit Register (AXR) Bit Definitions:

| 15-0                                                |

|-----------------------------------------------------|

| Transmit (Playback) Buffer 16-Bit Beginning Address |

This 16 bit register (Table 10) gives the beginning address of the transmit buffer for Stereo Codec external DMA.

Table 11. Transmit Buffer (BXK) Size Register:

| 15-0                                             |  |

|--------------------------------------------------|--|

| Transmit (Playback) Buffer 16-Bit Ending Address |  |

This 16 bit register (Table 11) gives the ending address of the transmit buffer for Stereo Codec external DMA. (Note that this is slightly different than the BSP spec because of limited combinatorial gates in the FPGA).

## SYSTEM OPERATION

The architecture described in this Application Note allows for the use of all three modes. DSP specific system level considerations can be found in various literature items available from TI, especially [6].

From the codec standpoint, it needs to be programmed after coming out of reset (unfortunately misnamed as -PDWN). This operation is done by addressing the R0-R3 registers in decoded logic and can be observed in the code section for all modes. Basically this programming involves setting of codec I/O channels, data format, gains, etc. since the huge flexibility in these parts rarely allow the system to be up and running, as is seen with more classic DSP codecs such as the TLC3204x family. Use of IN/OUT instructions was essential in the design because of the relatively slow FPGA accesses when compared to that of the DSP, especially turn-off time. Memory-mapped I/O accesses using the DSP are NOT advised.

Another system aspect that should be appreciated is how slow the codec cycles are (several hundred nanoseconds) compared to a 40 or 50 MIP DSP. This aspect is due to the analog noise margins that increased digital speeds would incur. This fact drove the decision to ignore certain functions that are provided in the codec (such as capture and play ready bits in modes 2 and 3, thus ignoring the codec INT pin) and to move these functions to the FPGA. The assumption is that when the interface logic is made discrete, or more likely into an ASIC or cDSP, the system will run operate faster.

#### Mode 1 Programmed I/O

From a hardware standpoint, the decode necessary for the programming makes this almost a default mode. The playback function is readily available since the DSP is writing to the codec. But in the case of capture, the  $t_{ADHD}$  address hold timing from the DSP is too fast for the codec which, as mentioned earlier, was made for a slower PC bus. Thus latching of the address lines for the codec is essential for reliable capture.

#### NOTE:

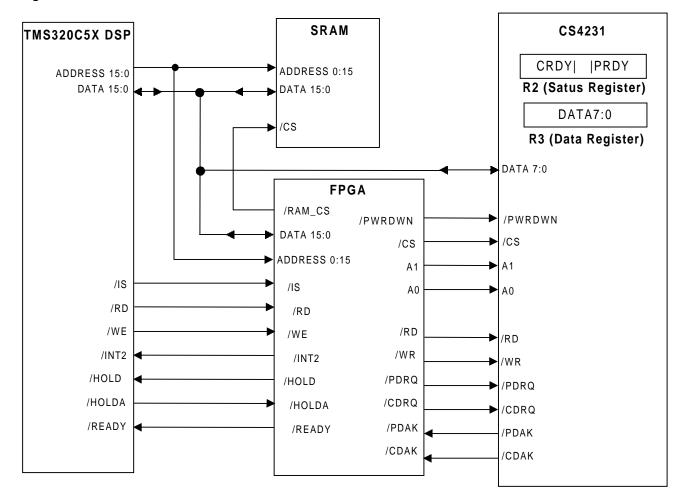

Figure 2 shows mode 1 PIO, whose only difference from the main block diagram in Figure 1 is the stress on stereo codec Direct Registers.

Figure 2. Mode 1 - PIO Connection of TMS320C5x Parallel Stereo Codec

From the software standpoint, the codec must first be programmed into the PIO mode and various bits polled. Then PIO Capture and Playback bits (CRDY/PRDY) in the codec Status Register R2 (called Direct 2 Status on AD65) is polled by the DSP in a tight loop before receiving or sending data. Obviously this mode ends up becoming slow since it is poll driven. Also note that each of these codec accesses are in the hundreds of nanoseconds, slow to a DSP. Code for PIO that does a simple digital loop back can be seen in Appendix A.

Loop: Test codec Status Register R2 for CRDY/PRDY Read/write data from/to codec Data Register R3 Goto Loop Thus the other two modes place the codec in the DMA mode using the PDRQ and CDRQ pins. As mentioned earlier, the INT pin is not used because it does not differentiate between capture and play. This function was moved to the FPGA. This is not much faster, but was done based on the assumption that an ASIC/cDSP implementation was the final goal. Note that though the next two modes use the same pins, they handle data movement quite differently.

#### **Mode 2 Interrupt Driven**

In this mode after putting the codec into DMA mode the DSP handles not only the data movement interrupt-based, but also the handshake with DMA acknowledge pins -CDAK and -PDAK. The following Figure 3 shows the relevant configuration.

Figure 3. Mode 2 - Interrupt Connection of TMS320C5x Parallel Stereo Codec

The PDRQ/CDRQ requests have been multiplexed to the same DSP interrupt pin -INT2. The CDRQ and PDRQ bits in the DSPSR register must then be read and the appropriate action taken. Whether capture or play, the DSP must write to the CDAK or PDAK bits in the SYSCFG register to manually exercise the DMA mode. Thus the following sequence must occur in the ISR, assuming simultaneous capture and play.

- 1) Read PCSR and test if CDRQ, PDRQ or both are high.

- 2) Write 0 to -CDAK/-PDAK bit in SYSCFG (based on whichever is higher priority) to acknowledge the DMA cycle.

- Read/write data value from/to codec before/after writing/reading to memory.

- Write 1 to -CDAK/-PDAK bit in SYSCFG to end DMA cycle acknowledgement.

- 5) Repeat for number of bytes.

The last step is required since FPGA will pend and interrupt the DSP if PDRQ or CDRQ is high. If the DSP chooses to mask this interrupt, then data will be lost. Code that exercises some simple digital loopback in this mode may be found in Appendix A.

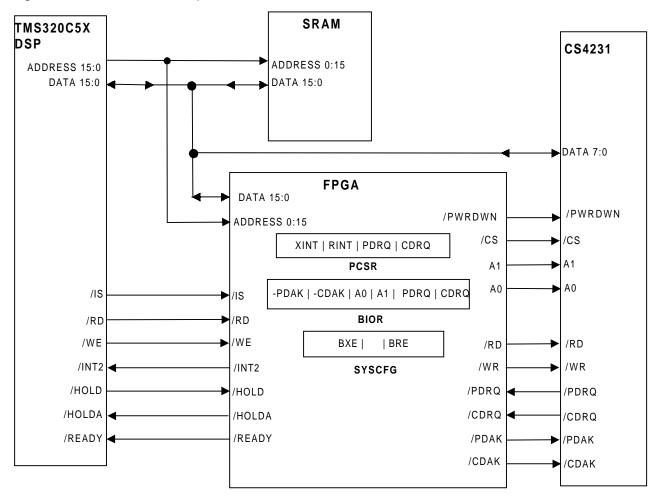

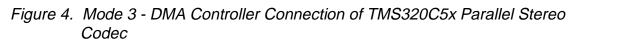

#### Mode 3 Stereo Codec DMA

In this mode the DSP is taken off the bus (using the -HOLD/-HOLDA protocol) and the data is copied back and forth between the DSP and memory. A DMA controller is designed into the FPGA that consists of three parts each for receive and transmit. These parts are: a finite state machine to act as the intelligent entity, address generation blocks, and wave form generation module. Parts of the wave form generation module can be shared between capture and playback parts since the single bus prevents them from occurring at the exact same time (even though they may run concurrently). If there is any conflict for resources, priority has been given to the capture module.

The following figure shows how these modules are constructed in the FPGA.

As mentioned earlier, this logic was designed to look similar to [7]. The capture and playback buffers may be placed anywhere in external memory. The DSP will be interrupted when the DMA controller reaches either the halfway point or end of the buffer. Then the RH/XH flag must be read to determine which half of the buffer needs servicing. The DMA controller for capture or play is enabled by the BRE and BXE flags respectively. The schematics for the FSM's and Address Generators can be seen in Appendix B. A full description of this would be found in [9].

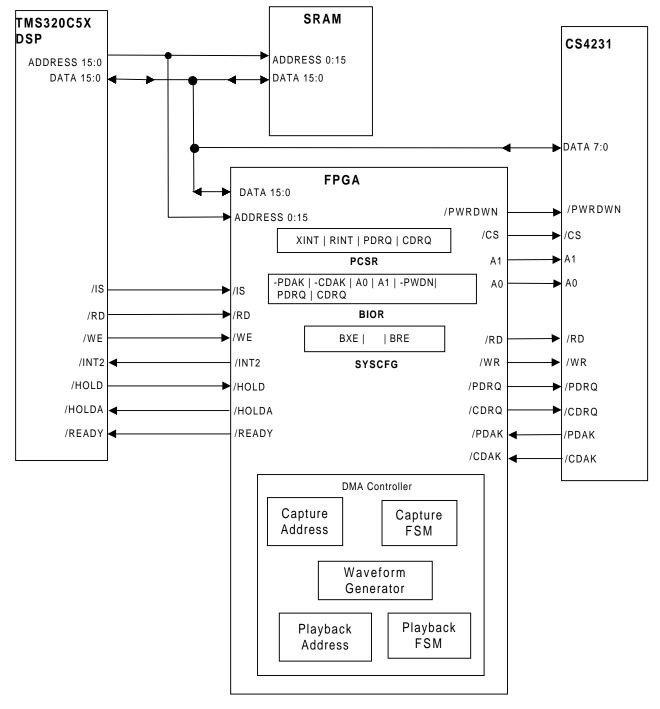

From a software standpoint, after the DMA is setup the DSP needs to deal with the data only when a buffer is full or empty. The code looks similar to the interrupt driven except that the acknowledges are handled by the FSM and large buffers of data are used. Thus the following sequence must occur in the ISR, assuming simultaneous capture and play.

- 1) Read PCSR and test if RINT, XINT or both are high.

- 2) Test RH or XH to see which buffer may now be manipulated.

- Change buffer pointers for main code to deal with these buffers.

In Appendix A, some code may be found that does some simple digital loopback. Appendix A also has a bit more interesting loopback code (Figure 5).

Figure 5. Mode 3 - Test Code in Appendix A (Digital Loopback with DMA)

That sets up an intermediate buffer so that the capture ISR copies data from the capture buffer and puts it into the intermediary buffer. Meanwhile the playback ISR copies data from the intermediary buffer to the playback buffer. While all this is happening, the FSM's are copying data to and from the codec from the capture and playback buffers. Also a second interrupt is occurring while all this is happening.

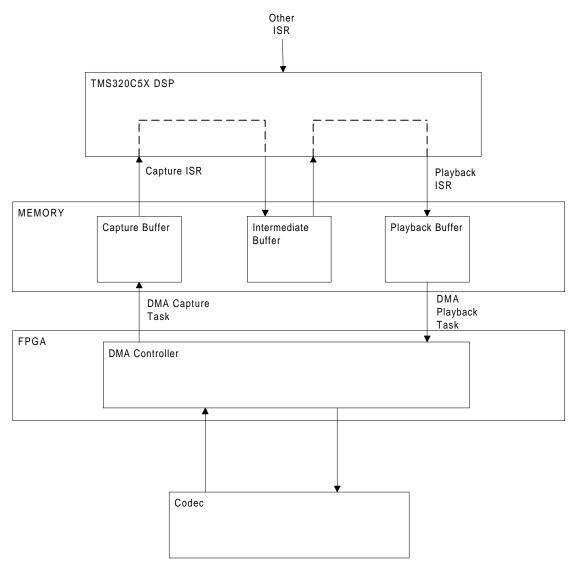

## SYSTEM CONSIDERATIONS

The basic system described previously in this Application Note looks as follows in Figure 6.

The problem with this architecture, which should minimize the time that the DSP is not accessing the SRAM, is compounded by the relatively slow access time of the stereo codec in relation to the codec. Three possible methods of speeding up this interface are described below, with different costs:

- 1) FIFO

- 2) External DMA

- 3) Serial Port (with internal DSP DMA)

#### NOTE:

Note that they all ignore the speed of the FPGA/ASIC/logic (which will be addressed later) and that only two were implemented in this paper.

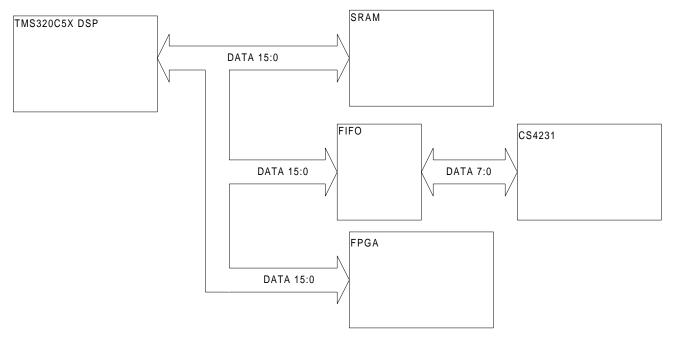

#### FIFO

In this implementation a FIFO is added as a classical mismatched speed bus interface solution. If the FIFO is fast enough, then the DSP can access data at zero wait states even though the codec interface is in the hundreds of nanoseconds. This method is probably the medium simplicity though higher cost since an additional part (and also interface glue logic) will need to be added. See Figure 7.

Figure 7. FIFO DSP/SRAM/Codec System

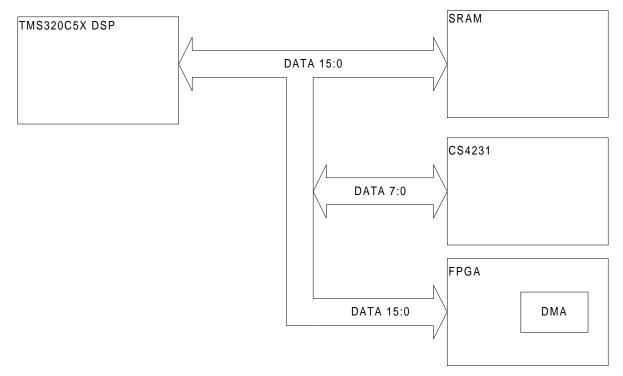

#### **External DMA**

This implementation was discussed in detail in this paper. It takes the burden off the DSP to do the data moving work, but is quite complicated. It is not that expensive, since existing logic may be used. This method is probably the most complex, and is mediumto-higher cost since much design and added logic are needed. See Figure 8. Note that TMS320 DSPs with their own DMA controllers exist, but much data is still going over the same bus, hence limiting the bandwidth.

Figure 8. External DMA DSP/SRAM/Codec System

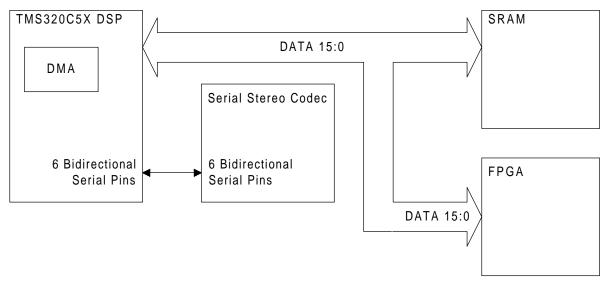

#### Serial Codec with DSP "DMA"

In this implementation an alternative serial bus is given to the codec so that it does not conflict with the SRAM. It is important here for the DSP to have some sort of bi-directional DMA capability, which may be seen in TMS320C5x/C54x parts with the bufferred serial port or TMS320C32/TMS320C6xxx with multiple DMA channels (see Figure 9). This system probably makes the most sense for the mass market customer who is not doing a cDSP/ASIC.

Figure 9. DSP with "DMA"/SRAM/Serial Codec System

## Parallel Codec with Separate Bus and External DMA Optional

This implementation should be mentioned as the ideal for performance. A separate data bus is created through logic to feed the DSP. Thus the DSP is protected from the slowness of the codec in a FIFO like style if a fast ASIC is used for the logic. The use of the DMA is optional based on the system. Of course this implementation will cost the most pins. This implementation probably makes the most sense for the cDSP customer.

Figure 10. DSP/SRAM/Parallel Codec with Separate Bus and External DMA System

## CONCLUSION

There are MANY ways to hook up these two parts. The important thing is to understand the parts and find the optimum configuration from both hardware AND software aspects. The limiting tradeoffs are those between design complexity and bus bandwidth.

## REFERENCES

ł

- 1) Crystal Data Book

- 2) TLC320AD65 Data Sheet

- 3) TMS320C5x User's Guide (p. HOLD)

- 4) Designer Notebook Page #4x.

- 5) PCMCIA DSP/Memory Card for the TMS320C5x Specification

- 6) PCMCIA DSP/Memory Card for the TMS320C5x Application Note

- 7) TMS320C57 Buffered Serial Port Spec

- 8) TLC320AD65 Data Sheet P\_PORT Addendum

- 9) FPGA Spec

## **Appendix A - Code**

The following section has all sorts of code that was written for a system based on [5]. Note in all cases that the codec is first initialized in either PIO or DMA mode and then put into its function. Note that there is a good amount of redundancy in the code, but all of it is fully functional.

#### Mode 1 - PIO Digital Loopback

This code initializes the codec in PIO mode with appropriate inputs and gains and then uses mode 1 - PIO to do the digital loopback one sample at a time.

|                      | .mmregs<br>.include         | e "cs4231.                       | .inc" |                                                  |

|----------------------|-----------------------------|----------------------------------|-------|--------------------------------------------------|

| LEFT_ADC_GAIN<br>CFS | .set 02<br>.set CS          | 2h<br>54231_48KH                 | IZ    |                                                  |

|                      | .sect "\                    | vectors"                         |       |                                                  |

|                      | b                           | init                             | ;00;  | Reset.                                           |

|                      | .space                      | 2 * 16                           | ;02;  | Vector for external interrupt ; INT1.            |

|                      | .space                      | 2 * 16                           | ;04;  | <pre>Vector for external interrupt ; INT2.</pre> |

|                      | .space                      | 2 * 16                           | ;06;  | <pre>Vector for external interrupt ; INT3.</pre> |

|                      | .space                      | 2 * 16                           | ;08;  | timer interrupt vector - TINT                    |

|                      | .space                      | 2 * 16                           | ;0A;  | Serial port receive interrupt ; RINT             |

|                      | .space                      | 2 * 16                           | ;0C;  | Serial port transmit<br>; interrupt XINT         |

|                      | .space                      | 4 * 16                           | ;0E;  | vectors for TDM port TRNT,<br>; TXNT             |

|                      | .space                      | 2 * 16                           | ;12;  | <pre>vector for external interrupt ; INT4</pre>  |

|                      | .space                      | 14 * 16                          | ;14;  | Reserved space. Should not be ; used.            |

|                      |                             | 2 * 16                           |       | Trap instruction vector                          |

|                      | .space                      | 2 * 16                           | ;24;  | Non Maskable Interrupt vector                    |

|                      | .space                      | 4 * 16                           | ;26;  | Reserved space. Should not be ; used.            |

|                      | .text                       |                                  |       |                                                  |

| init:                |                             |                                  |       |                                                  |

|                      | ldp<br>splk<br>clrc<br>splk | #0<br>#0000000<br>OVM<br>#001Fh, | ; Di  | IMR<br>sable overflow saturation mode            |

|          | splk<br>splk                                                 |                                                                                                                                                            |

|----------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | call                                                         | _InitAIC                                                                                                                                                   |

|          | lacc<br>sacl<br>lacc<br>sacl<br>lar<br>lacc<br>sacl          | <pre>#08000h ; set up circular buffer pointers CBSR1 ; buffer1 = 8000 -&gt; ffff #0FFFFh ; CBER1 ; AR7,#08000h; set receive buffer #11101111b ; CBCR</pre> |

|          | lacc<br>mar<br>rpt<br>sacl                                   | #0<br>*, AR7<br>#8000h<br>*+                                                                                                                               |

|          | SET_CS42                                                     | 231 I9, CS4231_ENABLE<br>; Capture and Playback enabled.                                                                                                   |

|          | Clrc                                                         | INTM ; Globally enable interrupts                                                                                                                          |

| Loop:    | in<br>nop<br>lacl<br>and<br>bcnd<br>lacl<br>and<br>bcnd<br>b | TEMP0, CS4231_R2<br>TEMP0<br>#00100000B<br>Capture, NEQ<br>TEMP0<br>#00000010B<br>Playback, NEQ<br>Loop                                                    |

| Capture: |                                                              |                                                                                                                                                            |

|          | in<br>lacl<br>and<br>sacb                                    | *, CS4231_R3<br>*<br>#0FFh                                                                                                                                 |

|          | in<br>lacc<br>sacl<br>lacb<br>or<br>sacl                     | *, CS4231_R3<br>*, 8<br>TEMP0<br>TEMP0<br>*                                                                                                                |

|          | b                                                            | Loop                                                                                                                                                       |

Playback:

÷

\*+ lacc sacl temp0 TEMP0, CS4231\_R3 out rpt #07h sfr sacl temp0 TEMP0, CS4231\_R3 out b Loop ; \_InitAIC() - AIC Initialization Routine \_InitAIC: zap sacl TEMP1 ; TEMP1 <- clears MCE lacc #8F00h ; Take out of reset sacl temp0 TEMP0, CS4231\_PDWN out rpt #0F000h ; Wait a while longer (Dag) nop Wait\_80: TEMP0, CS4231 R1 in nop #80h, TEMP0 cpl bcnd Wait\_80, TC ; ; ===== Clear previous states =============== IS\_CS4231\_RDY TEMP0 ; Wait for PIO ready SET\_CS4231 19, 0; Disable playback and capture TEMP0, CS4231\_R2 out ; Clear interrupts IS\_CS4231\_RDY TEMP0 SET\_CS4231 SETMCE | I12, CS4231\_SETMODE2 ; Set the MODE2 SET\_CS4231 SETMCE | I9, CS4231\_P\_PIO | CS4231\_C\_PIO SET\_CS4231 SETMCE | I28, CS4231\_MONO | CS4231\_16LINEAR ; Set The Capture mode to ; 16-bit linear

SET\_CS4231 SETMCE | I8, CFS | CS4231\_MONO | CS4231 16LINEAR ; Set 16-bit, mono. rpt #0FFFFh nop IS\_CS4231\_RDY TEMP0 ; Clocks must resynch. SET\_CS4231 SETMCE | I0, CS4231\_MIC | LEFT\_ADC\_GAIN ; Left ADC input source select : Microphone. SET\_CS4231 SETMCE | I6, CS4231\_SETGAIN ; Left DAC attenuator. ; lacc #SETMCE | 19 ; Set up R0 by setting Index ; to I9 sacl temp0 ; and setting MCE. out TEMP0, CS4231\_R0 ; Set the ACAL bits in in TEMP0, CS4231\_R1 nop lacl TEMP0 ; Set ACI bit in I9 without clearing #CS4231\_SETACAL ; any other bits. This will or ; cause device to recalibrate. sacl TEMP0 TEMP0, CS4231\_R1 out nop TEMP1, CS4231\_R0 out ; Clear MCE to initiate calibration nop Wait cal: in TEMP0, CS4231\_R1 nop #80h, TEMP0 cpl bcnd Wait\_cal, TC lacl #I11 sacl TEMP0 TEMP0, CS4231\_R0 out ; Wait until the device is ; finished calibrating. Notdone: TEMP0, CS4231\_R1 in nop bit TEMP0, BIT5 ; This bit indicates the ; status of calibration. bcnd Notdone, TC ret

This code initializes the codec in DMA simultaneous capture/playback mode with appropriate inputs and gains and then uses mode 2 - Interrupt Driven to do the digital loopback one sample at a time. Again the DSP is doing the moving based on interrupts from the codec based on PDRQ/CDRQ. Also the DSP must manually toggle -CDAK/-PDAK lines.

|                      | * This uses DMA model Interment DDDO                                                                     |

|----------------------|----------------------------------------------------------------------------------------------------------|

|                      | * This uses DMA mode - Interrupt PDRQ                                                                    |

|                      | .mmregs<br>.sect "vectors"                                                                               |

| INT1<br>INT2<br>INT3 | B start ;00; RESET<br>B pc_isr ;02; vectors for interrupts int1-int3<br>B codec_isr<br>B INT3            |

| receive B            | .space 2 * 16 ;08; timer interrupt vector - TINT<br>receive ;0A; Serial port receive interrupt<br>; RINT |

| transmit B           | transmit ;OC; Serial port transmit interrupt<br>; XINT                                                   |

|                      | .space 4 * 16 ;0E; vectors for TDM port TRNT,<br>; TXNT                                                  |

|                      | .space 2 * 16 ;12; vector for external interrupt<br>; INT4                                               |

|                      | .space 14 * 16 ;14; Reserved space. Should ; not be used.                                                |

|                      | .space 2 * 16 ;22; Trap instruction vector                                                               |

|                      | .space 2 * 16 ;24; Non Maskable Interrupt<br>; vector                                                    |

|                      | .space 4 * 16 ;26; Reserved space. Should ; not be used.                                                 |

| start:               | .text<br>LDP #0                                                                                          |

|                      | LACC #0000h ; Reset codec<br>SACL 61h                                                                    |

|                      | OUT 61h, 53h<br>RPT #0f000h ; Wait<br>NOP                                                                |

|                      | LACC #0c800h ;Take out of reset & -CDAK/-PDAK high<br>SACL 61h<br>OUT 61h, 53h                           |

|                      | RPT #0f000h ; Wait a while longer (Dag)<br>NOP                                                           |

| stuck:               | IN 61h, 58h ; Checking for 80h<br>LACL 61h<br>AND #0080h<br>BCND stuck, NEQ                              |

LACC #0009h ; Flip MCE bit=1 and Register 9 SACL 61h OUT 61h, 58h LACC #0008h ; Switch to DMA Dual Channel Mode SACL 61h OUT 61h, 59h LACC #000bh ; Flip MCE bit=0 and Register 11 SACL 61h OUT 61h, 58h stuck1: IN61h, 58h ; Checking for 80h LACL 61h AND #0080h BCND stuck1, NEQ 61h, 58h ; Checking for 20h on register 11 stuck2: INLACL 61h AND #0020h BCND stuck2, NEQ LACC #0009h ; Set to register 9 SACL 61h OUT 61h, 58h LACC #000bh ; Enable any playback/capture SACL 61h OUT 61h, 59h LACC #0000h ; Set to Left Input Register SACL 61h OUT 61h, 58h LACC #0000h ; Write to Left Input Register ;Making this 7h sounds better, but codec cuts out! SACL 61h OUT 61h, 59h LACC #0006h ; Set to Left Output Register SACL 61h OUT 61h, 58h LACC #0000h ; Write to Left Output Register SACL 61h OUT 61h, 59h lacc #08000h ; set up circular buffer pointers sacl CBSR1 ; buffer1 = 8000 -> ffff lacc #08000h sacl CBSR2 lacc #0800fh ; buffer2 = ffff -> 8000 sacl CBER1 lacc #0800fh ; buffer2 = ffff -> 8000 CBER2 sacl lar AR6,#08000h ; set receive buffer lar AR7,#08000h ; set transmit buffer

|                  | lacc #000000001              | .1111110b ; buf1=AR7, buf2=AR6, |

|------------------|------------------------------|---------------------------------|

|                  | sacl CBCR                    | ; enable both                   |

| ; Set up block r |                              | 1                               |

| -                | LACC #8000h<br>SACL 61h      | ; ARR Value                     |

|                  | OUT 61h, 5Ch                 | ; Write                         |

|                  | LACC #08010h<br>SACL 61h     | ; BKR Value                     |

|                  | OUT 61h, 5Dh                 | ; Write                         |

|                  | LACC #0a000h                 | ; AXR Value                     |

|                  | SACL 61h                     |                                 |

|                  | OUT 61h, 5Eh<br>LACC #0a010h | ; Write<br>; BKX Value          |

|                  | SACL 61h                     | , BKX Value                     |

|                  | OUT 61h, 5Fh                 | ; Write                         |

| ;Set up DMA and  | Interrupts                   |                                 |

|                  | LACC #0ffffh                 |                                 |

|                  | SACL IFR                     | · mark on DC and redor ISP      |

|                  | SACL IMR                     | ; mask on PC and codec ISR      |

|                  |                              | ; bogus read from DSPRXD        |

|                  |                              | ; disable BXE and BRE           |

|                  | SACL 61h                     |                                 |

|                  | OUT 61h, 54h<br>CLRC INTM    |                                 |

| loop:            | NOP                          |                                 |

| -                |                              | ; bogus read from DSPRXD        |

|                  |                              | ; bogus write to DSPTXD         |

|                  | NOP<br>B loop                |                                 |

|                  | в тоор                       |                                 |

| 7 1.             | MAR *, AR6                   |                                 |

| loop1:           | IN 61h, 5ah<br>LACL 61h      |                                 |

|                  | AND #20h                     |                                 |

|                  | BCND loop1, EQ               |                                 |

|                  | IN *, 5bh                    | ; Read data                     |

| loop2:           | IN 61h, 5ah                  |                                 |

|                  | LACL 61h<br>AND #02h         |                                 |

|                  | BCND loop2, EQ               |                                 |

|                  | OUT *+, 5bh                  | ; Write data                    |

| ;                | RPT #5000                    | ; Wait                          |

| ;                | NOP<br>B loop1               |                                 |

| playback:        | P TOOPT                      |                                 |

|                  | RPT #5000                    | ; Wait                          |

|                  | NOP                          |                                 |

|                  | OUT *+, 5bh                  | ; Write data                    |

В playback pc\_isr: NOP SETC XF RPT #100 NOP CLRC XF RETE ; This one is for Level2 codec\_isr: SETC XF NOP IN60h, 52h ; Read PCSR LACL 60h ; Need to change these bits, eh! #0004h AND ; Test CDRQ BCND cap\_serve, NEQ ptest: LACL 60h ; Test PDRQ AND #0008h BCND play\_serve, NEQ isr\_done NOP CLRC XF RETE cap\_serve: \*,ARб MAR LACC #08800h ; -CDAK low SACL 61h OUT 61h, 53h IN 61h, 5bh ; Read Value LACL 61h \*+ SACL LACC #0c800h ; -CDAK high SACL 61h OUT 61h, 53h В ptest play\_serve: MAR \*,AR7 LACC #04800h ; -PDAK low SACL 61h OUT 61h, 53h LACL \*+ SACL 61h OUT 61h, 5bh ; Play Value LACC #0c800h ; -PDAK high SACL 61h OUT 61h, 53h isr\_done В

This code initializes the codec in DMA simultaneous capture/playback mode with appropriate inputs and gains and then uses mode 3 - Stereo Codec to do the digital loopback one sample at a time. But here the DMA controller is doing the moving based on CDRQ/PDRQ, not the DSP. Capture and playback buffers are set as one and the same (8000h-B000h in DSP data memory). The DSP processes the data based on interrupts from the DMA controller. Also the FSM's in the DMA Controller must toggle the -CDAK/-PDAK lines.

|                         | * This uses DMA mode                                                                                                                                                                                                                                                                         |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                         | .mmregs<br>.sect "vectors"                                                                                                                                                                                                                                                                   |  |  |

| INT1<br>INT2<br>INT3    | <pre>B start ;00; RESET B pc_isr ;02; vectors for interrupts int1-int3 B codec_isr B INT3</pre>                                                                                                                                                                                              |  |  |

| receive B<br>transmit B | <pre>.space 2 * 16 ;08; timer interrupt vector - TINT<br/>receive ;0A; Serial port receive interrupt RINT<br/>transmit ;0C; Serial port transmit interrupt XINT<br/>.space 4 * 16 ;0E; vectors for TDM port TRNT, TXNT<br/>.space 2 * 16 ;12; vector for external interrupt<br/>; INT4</pre> |  |  |

|                         | <pre>.space 14 * 16 ;14; Reserved space. Should not<br/>; be used.<br/>.space 2 * 16 ;22; Trap instruction vector<br/>.space 2 * 16 ;24; Non Maskable Interrupt vector<br/>.space 4 * 16 ;26; Reserved space. Should not be<br/>; used.</pre>                                                |  |  |

| start:                  | .text<br>LDP #0<br>LACC #0c000h ; Reset codec<br>SACL 61h<br>OUT 61h, 53h<br>RPT #0f000h ; Wait<br>NOP                                                                                                                                                                                       |  |  |

|                         | LACC #0c800h ; Take out of reset<br>SACL 61h<br>OUT 61h, 53h<br>RPT #0f000h ; Wait a while longer (Dag)                                                                                                                                                                                      |  |  |

| stuck:                  | NOP<br>IN 61h, 58h ; Checking for 80h<br>LACL 61h<br>AND #0080h<br>BCND stuck, NEQ                                                                                                                                                                                                           |  |  |

LACC #0049h ; Flip MCE bit=1 and Register 9 SACL 61h OUT 61h, 58h LACC #0008h ; Switch to DMA Dual Channel Mode SACL 61h OUT 61h, 59h LACC #0048h ; Set to register 8 SACL 61h OUT 61h, 58h ; LACC #0040h ; 16 `bit mono LACC #0000h ; 8 `bit mono SACL 61h OUT 61h, 59h LACC #000bh ; Flip MCE bit=0 and Register 11 SACL 61h OUT 61h, 58h stuck1: IN 61h, 58h ; Checking for 80h LACL 61h AND #0080h BCND stuck1, NEQ stuck2: IN61h, 58h ; Checking for 20h on register 11 LACL 61h AND #0020h BCND stuck2, NEQ LACC #0009h ; Set to register 9 SACL 61h OUT 61h, 58h LACC #000bh ; Enable any playback/capture SACL 61h OUT 61h, 59h LACC #0000h ; Set to Left Input Register SACL 61h OUT 61h, 58h LACC #0000h ; Write to Left Input Register ;Making this 7h sounds better, but codec cuts out! SACL 61h OUT 61h, 59h LACC #0006h ; Set to Left Output Register SACL 61h OUT 61h, 58h LACC #0000h ; Write to Left Output Register SACL 61h OUT 61h, 59h ; set up circular buffer pointers lacc #09000h ; buffer1 = 8000 -> ffff sacl CBSR1

sacl CBSR2 ; lacc #0900fh ; buffer2 = ffff -> 8000 sacl CBER1 sacl CBER2 lar AR6,#09000h ; set receive buffer AR7,#09000h lar ; set transmit buffer lacc #000000011101111b ; buf1=AR7, buf2=AR6, ; enable both sacl CBC ; Set up block registers LACC #8000h ; ARR Value SACL 61h 61h, 5Ch ; Write OUT LACC #0b000h ; BKR Value SACL 61h OUT 61h, 5Dh ; Write LACC #8000h ; AXR Value SACL 61h OUT 61h, 5Eh ; Write LACC #0b000h ; BKX Value SACL 61h 61h, 5Fh ; Write OUT ;Set up DMA and Interrupts LACC #0ffffh SACL IFR ; mask on PC and codec ISR LACC #03h SACL IMR 61h, 51h ; bogus read from DSPRXD INLACC #0c4h ; Enable BXE and BRE SACL 61h OUT 61h, 54h CLRC INTM SETC INTM ; loop: NOP 61h, 51h ; bogus read from DSPRXD 61h, 50h ; bogus write to DSPTXD IN OUT NOP loop В \*, AR6 MAR loop1: IN 61h, 5ah LACL 61h AND #20h BCND loop1, EQ \*, 5bh IN; Read data loop2: IN61h, 5ah LACL 61h #02h AND BCND loop2, EQ OUT \*+, 5bh ; Write data

| ;<br>;<br>playback:    | RPT<br>NOP<br>B                    | #5000<br>loop1                          | ; Wait                        |

|------------------------|------------------------------------|-----------------------------------------|-------------------------------|

| prayback               |                                    | #5000<br>*+, 5bh<br>playback            | ; Wait<br>; Write data        |

| pc_isr: NOP            | SETC<br>RPT<br>NOP<br>CLRC<br>RETE | #100                                    |                               |

| codec_isr:             | LACL<br>AND<br>BCND                | 60h<br>#0010h<br>cap_serve, NE(         |                               |

| ptest:<br>isr_done NOP | AND                                | play_serve, NH                          | ; Test XHFULL<br>EQ           |

| cap_serve:             | RETE                               | ΧI.                                     |                               |

|                        | LACL<br>AND<br>BCND                | #0040h                                  | ; Test which half DMA is cap  |

| dmaclow                | NOP<br>MAR<br>RPT<br>BLDD<br>B     | *,AR6<br>#0eh<br>#8000h, *+<br>isr_done | ; Process high                |

| dmachigh               | NOP<br>MAR<br>RPT<br>BLDD<br>B     | *,AR6<br>#0eh<br>#8000h, *+<br>isr_done | ;Process low                  |

| play_serve:            | LACL<br>AND<br>BCND                | 60h<br>#0080h<br>dmaphigh, NEQ          | ; Test which half DMA is play |

| dmaplow                | NOP<br>MAR<br>RPT                  | *,AR7<br>#0eh                           | ; Process high                |

÷

BLDD \*+, #8010h B isr\_done dmaphigh NOP ;Process low MAR \*,AR7 RPT #0eh BLDD \*+, #8010h B isr\_done

## Mode 3 - Stereo Codec DMA Digital Loopback with Intermediate Buffer and Interrupts

This code is graphically represented in Figure 5. It initializes the codec in DMA simultaneous capture/playback mode with appropriate inputs and gains and then uses mode 3 - Stereo Codec to do the digital loopback one sample at a time. Again the DMA controller is doing the moving based on CDRQ/PDRQ, not the DSP. The DSP processes the data based on interrupts from the DMA controller. But as an added twist, the capture/play buffers are different now (8000h-8010h and A000h-A0010h, respectively) and there is an intermediate buffer (9000h-9010h) and the DSP ISR's move the data to and from it. Also the FSM's in the DMA Controller must toggle -CDAK/-PDAK lines.

#### DMA Cap Play

|                         | * This uses DMA mode                                                                                                                                                                                                               |  |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                         | .mmregs<br>.sect "vectors"                                                                                                                                                                                                         |  |  |

| INT1<br>INT2<br>INT3    | <pre>B start ;00; RESET B pc_isr ;02; vectors for interrupts int1-int3 B codec_isr B INT3</pre>                                                                                                                                    |  |  |

| receive B<br>transmit B | <pre>.space 2 * 16 ;08; timer interrupt vector - TINT<br/>receive ;0A; Serial port receive interrupt RINT<br/>transmit ;0C; Serial port transmit interrupt XINT<br/>.space 4 * 16 ;0E; vectors for TDM port<br/>; TRNT, TXNT</pre> |  |  |

|                         | .space 2 * 16 ;12; vector for external<br>; interrupt INT4                                                                                                                                                                         |  |  |

|                         | .space 14 * 16 ;14; Reserved space. Should<br>; not be used.                                                                                                                                                                       |  |  |

|                         | .space 2 * 16 ;22; Trap instruction vector                                                                                                                                                                                         |  |  |

|                         | .space 2 * 16 ;24; Non Maskable Interrupt<br>; vector                                                                                                                                                                              |  |  |

|                         | .space 4 * 16 ;26; Reserved space. Should ; not be used.                                                                                                                                                                           |  |  |

| start:                  | .text<br>LDP #0<br>LACC #0C000h ; Reset codec                                                                                                                                                                                      |  |  |

|         | NOP                                                                    | ; Wait                                                               |

|---------|------------------------------------------------------------------------|----------------------------------------------------------------------|

|         | LACC #0C800h<br>SACL 61h<br>OUT 61h, 53h<br>RPT #0f000h                | ; Take out of reset<br>; Wait a while longer (Dag)                   |

| stuck:  | NOP<br>IN 61h, 58h<br>LACL 61h<br>AND #0080h<br>BCND stuck, NEQ        | ; Checking for 80h                                                   |

|         | LACC #0049h<br>SACL 61h<br>OUT 61h, 58h<br>LACC #0008h                 | ; Flip MCE bit=1 and Register 9<br>; Switch to DMA Dual Channel Mode |

|         | SACL 61h<br>OUT 61h, 59h                                               | , Switch to Diff Duar chainer noue                                   |

|         | LACC #0048h<br>SACL 61h                                                | ; Set to register 8                                                  |

| ;       | OUT 61h, 58h<br>LACC #0040h<br>LACC #0000h<br>SACL 61h<br>OUT 61h, 59h | ; works better with 8<br>; 16 `bit mono<br>; 8 `bit mono             |

|         | LACC #000bh<br>SACL 61h<br>OUT 61h, 58h                                | ; Flip MCE bit=0 and Register 11                                     |

| stuck1: | IN 61h, 58h<br>LACL 61h<br>AND #0080h<br>BCND stuck1, NE               | ; Checking for 80h<br>Q                                              |

| stuck2: | IN 61h, 58h<br>LACL 61h<br>AND #0020h<br>BCND stuck2, NE               | ; Checking for 20h on register 11<br>Q                               |

|         | LACC #0009h<br>SACL 61h                                                | ; Set to register 9                                                  |

|         | OUT 61h, 58h<br>LACC #000bh<br>SACL 61h<br>OUT 61h, 59h                | ; Enable any playback/capture                                        |

|         | LACC #0000h<br>SACL 61h                                                | ; Set to Left Input Register                                         |

÷

OUT 61h, 58h LACC #0000h ; Write to Left Input Register ;Making this 7h sounds better, but codec cuts out! SACL 61h OUT 61h, 59h LACC #0006h ; Set to Left Output Register SACL 61h OUT 61h, 58h LACC #0000h ; Write to Left Output Register SACL 61h OUT 61h, 59h lacc #09000h ; set up circular buffer pointers sacl CBSR1 ; buffer1 = 8000 -> ffff lacc #0a000h sacl CBSR2 ; ; buffer2 = ffff -> 8000 lacc #0900fh sacl CBER1 ; lacc #0a00fh ; buffer2 = ffff -> 8000 sacl CBER2 lar AR6,#09000h ; set receive buffer AR7,#0a000h ; set transmit buffer lar lacc #000000011111110b ; buf1=AR7, buf2=AR6, enable both sacl CBCR ; ; Set up block registers LACC #8000h ; ARR Value SACL 61h 61h, 5Ch ; Write OUT LACC #08010h ; BKR Value SACL 61h 61h, 5Dh ; Write OUT LACC #0a000h ; AXR Value SACL 61h 61h, 5Eh ; Write OUT LACC #0a010h ; BKX Value SACL 61h OUT 61h, 5Fh ; Write ;Set up DMA and Interrupts LACC #0ffffh SACL IFR LACC #02h ; mask on PC and codec ISR SACL IMR 61h, 51h ; bogus read from DSPRXD INLACC #0c4h ; Enable BXE and BRE SACL 61h OUT 61h, 54h CLRC INTM loop: NOP IN 61h, 51h ; bogus read from DSPRXD

|              | OUT       61h, 50h         IN       61h, 5ch         IN       61h, 5dh         IN       61h, 5eh         IN       61h, 5fh         NOP       B | <pre>; bogus write to DSPTXD ; bogus read from DSPRXD ; bogus read from DSPRXD ; bogus read from DSPRXD ; bogus read from DSPRXD</pre> |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| loop1:       | MAR *, AR6<br>IN 61h, 5ah<br>LACL 61h<br>AND #20h<br>BCND loop1, EQ<br>IN *, 5bh                                                               | ; Read data                                                                                                                            |

| loop2:       | IN 61h, 5ah<br>LACL 61h<br>AND #02h<br>BCND loop2, EQ                                                                                          | ; Write data<br>; Wait                                                                                                                 |

| ;            | NOP<br>B loop1                                                                                                                                 |                                                                                                                                        |

| playback:    | _                                                                                                                                              |                                                                                                                                        |

|              | NOP                                                                                                                                            | ; Wait<br>; Write data                                                                                                                 |

| pc_isr: NOP  |                                                                                                                                                |                                                                                                                                        |

|              | SETC XF<br>RPT #100<br>NOP<br>CLRC XF<br>RETE                                                                                                  |                                                                                                                                        |

| codec_isr:   |                                                                                                                                                |                                                                                                                                        |

|              | LACL 60h                                                                                                                                       | ead PCSR - Will clear all interrupts!<br>; Test RHFULL<br>. NEO                                                                        |

| ptest:       | LACL 60h<br>AND #0020h                                                                                                                         | ; Test XHFULL                                                                                                                          |

| isr_done NOP | BCND play_serve<br>CLRC XF<br>RETE                                                                                                             | с, ису                                                                                                                                 |

| cap_serve:   | LACL 60h                                                                                                                                       | ; Test which half DMA is cap                                                                                                           |

SPRA097

| dmaclow              | AND<br>BCND<br>NOP<br>MAR<br>RPT<br>BLDD | dmachigh, NEQ<br>*,AR6<br>#07h                      | ; Process high                |

|----------------------|------------------------------------------|-----------------------------------------------------|-------------------------------|

| dmachigh             | BLDD<br>IN<br>B<br>NOP                   |                                                     | ; Bogus Read<br>;Process low  |

| unaciiigii           |                                          | #8008h, *+                                          | ; Bogus Read                  |

| play_serve:<br>;Why? | LACL<br>AND                              |                                                     | ; Test which half DMA is play |

| dmaplow              | RPT                                      | *,AR7<br>#07h                                       | ; Process high                |

| dmaphigh             | RPT<br>BLDD                              | 61h, 5eh<br>isr_done<br>*,AR7<br>#07h<br>#9008h, *+ | ; Bogus Read<br>;Process low  |

|                      | IN<br>B                                  | 61h, 5eh<br>isr_done                                | ; Bogus Read                  |

-U

# Appendix B - Stereo Codec DMA Structure

This Appendix addresses some specifics about the external DMA Controller that copies data between codec and external memory.

## **Stereo Codec DMA Schematic**

Figure 11 displays the main schematic for the DMA controller. The top half is the capture section while the bottom is playback. All the way in the top left corner are the address generator counters. Farther to the right are the RH adders and comparators along with interrupt generators. Then all the way in the right top corner (with the 3 flip-flops) is the capture FSM. Right in the middle is the beginning of the waveform generators (continued in another sheet not shown here) that is a counter that executes the codec read and write cycles. Finally, tucked into the bottom left, are multiplexors going to the 'C51 address bus. For much more detail see [9].

Figure 11. DMA Controller for Parallel Codec

## Stereo Codec DMA FSM's