# TMS320 DSP DESIGNER'S NOTEBOOK Hardware UART for the TMS320C3x

APPLICATION BRIEF: SPRA223

*Contributed by Lawrence Wong Digital Signal Processing Products Semiconductor Group*

*Texas Instruments June 1993*

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty, or endorsement thereof.

Copyright © 1999 Texas Instruments Incorporated

#### TRADEMARKS

TI is a trademark of Texas Instruments Incorporated.

Other brands and names are the property of their respective owners.

### **CONTACT INFORMATION**

| US TMS320 HOTLINE | (281) 274-2320 |

|-------------------|----------------|

| US TMS320 FAX     | (281) 274-2324 |

| US TMS320 BBS     | (281) 274-2323 |

| US TMS320 email   | dsph@ti.com    |

## Contents

| Abstract       | 7 |

|----------------|---|

| Design Problem | 8 |

| Solution       |   |

|                |   |

# Figures

| Figure 1. | Hardware UART      | 8 |

|-----------|--------------------|---|

| Figure 2. | Transmit Circuitry | 9 |

| Figure 3. | Receive Circuitry  | 0 |

# Hardware UART for the TMS320C3x

### Abstract

The TMS320C3X does not offer a UART for asynchronous communication. On the TI Digital Signal Processor BBS there is a software UART emulator available. This will allow the TMS320C3x to perform asynchronous communication. There are some instances that a hardware UART may be necessary for a particular application. This document describes one possible solution for implementing a hardware UART. This design was originally done in an FPGA and it can be easily transferred to an ASIC. Modification to this design can be done to accommodate faster data rates or different communication protocols. Several schematics are provided.

### **Design Problem**

The TMS320C3X does not offer a UART for asynchronous communication.

### Solution

Ť

On the TI DSP BBS there is a software UART emulator available. This will allow the TMS320C3x to perform asynchronous communication. There are some instances that a hardware UART may be necessary for a particular application. The following describes one possible solution for implementing a hardware UART. This design was originally done in an FPGA and it can be easily transferred to an ASIC. Modification to this design can be done to accommodate faster data rates or different communication protocols.

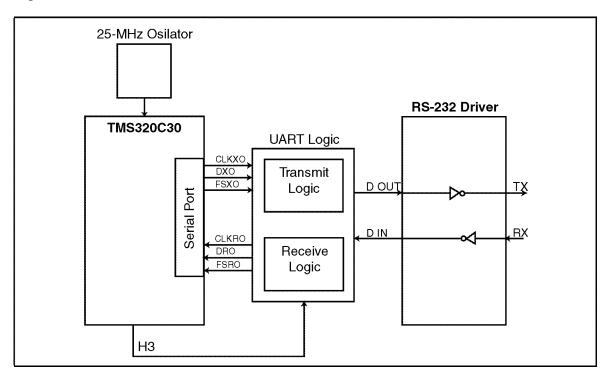

Figure 1. Hardware UART

The following schematic is for a 9600-baud UART with one stop bit and a start bit. The clock signal, H3, is supplied to the circuit from the TMS320C3x. The DSP was running with a 25-MHz clock, which was necessary for a particular application. Modification to the FPGA timing circuit will be necessary to accommodate a higher clock speed for the DSP.

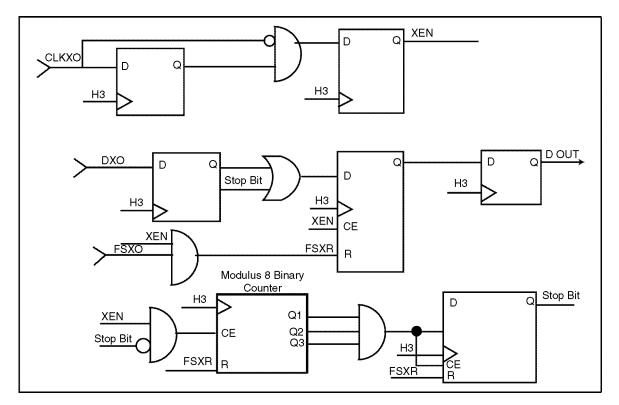

Figure 2. Transmit Circuitry

The TMS320C30 transmit section of the serial port is configured to output eight bits of data at a rate of approximately 9.6 kHz. This is achieved by using one of the TMS320C30's internal timers and programming it to the desired 9.6 kHz frequency. The transmitting port is configured in the fixed burst mode. This allows the leading FSX signals to help initiate a start bit for the UART protocols. The stop bit is generated at the end of the eighth bit by the UART circuitry.

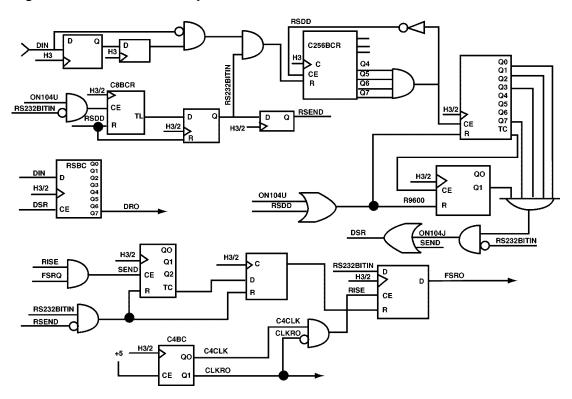

The receive section of the UART is activated when the circuitry detects the start bit. The start bit is a logical zero. The delay circuit is activated on the falling edge of the start bit. The delay is used so that sampling of the incoming data bits occur in the middle of the signal level, thus causing the UART to have a higher noise immunity.

Figure 3. Receive Circuitry

After the delay is performed, the timer is activated. The timer has a period of 104  $\mu$ s, which is approximately 9.6 kHz. At each period, a data is sampled into an eight-bit shift register. After all eight bits are received, the data is passed to the TMS320C30 at a speed of 1/8 of the H3 clock. The FPGA circuitry interfaces the TMS320C30 in the fixed burst mode of operation to the serial port. Both the clock and the frame sync signals are generated by the FPGA circuitry.

This UART circuitry can easily be designed into an ASIC that could also be incorporated into a Configurable Digital Signal Processor (cDSP). Modification to this circuit could be done for different serial communication protocols or even higher baud rates.