*TMS320 DSP DESIGNER'S NOTEBOOK*

# TMS320C5x Memory Paging (Expanding its Address Reach)

APPLICATION BRIEF: SPRA242

*Contributed by Joe George Digital Signal Processing Products Semiconductor Group*

*Texas Instruments May 1994*

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain application using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1997, Texas Instruments Incorporated

#### TRADEMARKS

TI is a trademark of Texas Instruments Incorporated.

Other brands and names are the property of their respective owners.

#### CONTACT INFORMATION

| US TMS320 HOTLINE | (281) 274-2320 |

|-------------------|----------------|

| US TMS320 FAX     | (281) 274-2324 |

| US TMS320 BBS     | (281) 274-2323 |

| US TMS320 email   | dsph@ti.com    |

## Contents

| Design Problem | Abstract       | 7 |

|----------------|----------------|---|

| Solution       | Design Problem | 8 |

|                | Solution       | 8 |

## Figures

| Figure 1. | TMS320C5x Paging Hardware                          | 8 |

|-----------|----------------------------------------------------|---|

| Figure 2. | General DSP Memory Map (Separate Program and Data) | 9 |

## Examples

| Example 1. | . Code Listing | . 9 |

|------------|----------------|-----|

|------------|----------------|-----|

## TMS320C5x Memory Paging (Expanding its Address Reach)

#### Abstract

This document discusses how the designer can extend the address space of a TMS320C5x device.

Since a TMS320C5x is a 16-bit machine with a 16-bit address, memory paging is needed if more than 64K of memory is to be addressed in a particular space. An external device needs to supply the upper addresses beyond the 16-bit memory range. This document describes how to implement this solution and gives block diagrams and a code listing to support this solution.

### **Design Problem**

How can I extend the address space of a TMS320C5x device?

### Solution

Ť

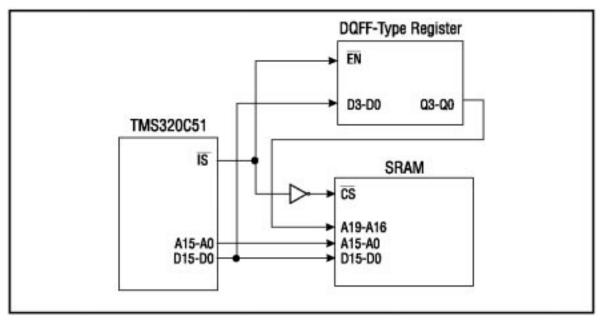

Since a TMS320C5x is a 16-bit machine with a 16-bit address, memory paging is needed if more than 64K of memory is to be addressed in a particular space. An external device needs to supply the upper addresses beyond the 16-bit memory range. This is done by having the DSP write a value to a register located in its I/O space, whose data lines are the higher address bits. An example is shown below in Figure 1.

Figure 1. TMS320C5x Paging Hardware

Since the bank switch requires some action from the DSP, frequent switching between banks is not very efficient. It would be best to partition tasks within a bank, and switch banks when starting new tasks. It may even be desirable to fix a certain part of the memory as nonpageable, where the task manager would run (or use internal memory). This task manager kernel could determine on which page a called function resides and swap banks accordingly.

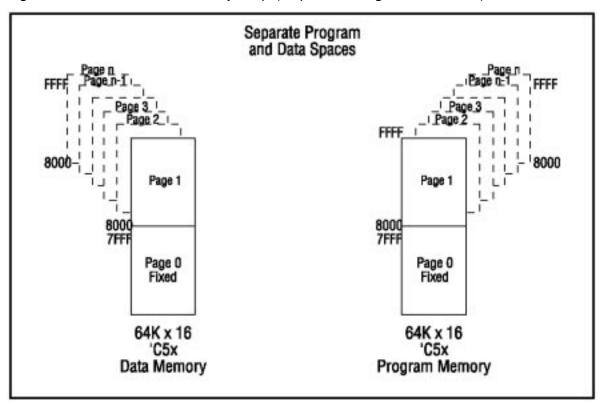

Figure 2. General DSP Memory Map (Separate Program and Data)

An example of a separate program and data scheme is shown above in Figure 2 with a fixed 32K page 0 in the lower half of memory and pageable 32K blocks in upper memory.

Thus in software, any task function would be called through the task manager from the main code.

```

Example 1. Code Listing

```

```

main()

{

taskman(task1, parms...);

}

void taskman(task, parms...)

{

case task{

task1:

asm (OUT pa0, BANK1)

task1(parms...);

task2: asm (OUT pa0, BANK2)

return(1)

```

```

}

task1 (parms. . . )

{

return(1)

}

```

At present, the TMS320 debuggers do not understand paged code for various spaces. They only understand page 0 for program, page 1 for data, and page 2 for I/O (1994 TMS320C5x Debugger Users Guide pages 13-32 and 13-33). Any of these spaces may be paged by the user. The debugger, which is unaware of paging, will display the data values after the user reads the space. Also, if the symbol information for a new page is desired, then doing an "sload" of the particular file containing a maximum of 64K (per page) must be done. The linker, on the other hand, understands up to 256 multiple pages (page 8-21 of Fixed-Point Assembly Tools). Thus one may combine the object files of each page into a single .out file using the linker. A smart loader can be written by the user to load the entire program and data into the specific system. The user must remember that the linker numbers its pages from 0 to 255 and therefore must be verified with the DSP memory map. For example data memory page 7 may actually arbitrarily correspond to linker page 12.

With these techniques, a user may extend the address reach of a TMS320C5x far above the 64K per memory space limited by the 16 address bits, allowing the use of more verbose code on a cheaper fixed-point platform. TI is presently in the process of studying the alternatives for cohesive expanded address reach support for all its tools.