# ADSL Clear EOC Channel Capability

Ryan Yi Wang

Broadband Access Group

#### ABSTRACT

This application report outlines the implementation of a CPE remote management scheme using the clear EOC Channel. The capabilities of the Clear EOC Channel are discussed for G.dmt different framing mode as well as ADSL2. This application report is meant to be used to provide a basic understanding of the Clear EOC channel and how it might be used for ADSL CPE remote management.

#### Contents

| 1   | Background Introduction                        | . 2 |

|-----|------------------------------------------------|-----|

| 2   | G.dmt Framing Mode                             | . 2 |

| 3   | Clear EOC Capability Analysis                  | . 3 |

|     | 3.1 ADSL Superframe Structure                  |     |

|     | 3.2 Clear EOC Capability in Full Overhead Mode | . 3 |

|     | 3.3 Clear EOC Capability in Frame Mode 3       |     |

|     | 3.4 Clear EOC Capability in ADSL2              | . 5 |

| 4   | References                                     | . 6 |

| Арр | endix A Keywords                               | . 7 |

#### **List of Figures**

| Figure 1 | ADSL Superframe Structure                                            | 3 |

|----------|----------------------------------------------------------------------|---|

| Figure 2 | Fast Synchronization Byte ("fast byte") Format in Full Overhead Mode | 4 |

#### **List of Tables**

| Table 1 | Definition of Framing Modes                                                       | 2 |

|---------|-----------------------------------------------------------------------------------|---|

| Table 2 | EOC Message Fields                                                                | 4 |

| Table 3 | Overhead Functions for Reduced Overhead Mode –<br>With Merged Fast and Sync Bytes | 5 |

| Table 4 | Overhead Message Priority                                                         | 6 |

Trademarks are the property of their respective owners.

## 1 Background Introduction

Embedded operations channel (EOC) is defined in G.dmt for the retrieval of ATU-R status information, ADSL performance parameters monitor, and maintenance. Clear EOC is one of EOC operation, which can be used for vendor specific operation. Some DSLAM manufacture is considering implementing CPE remote management through clear EOC channel. The purpose of this application report is to discuss the capability of clear EOC channel.

## 2 G.dmt Framing Mode

G.dmt defines four types of framing mode in Table 1. Many types are defined for complexity to support ATM, STM, dual latency, and single latency application. However, ATM mode with single latency dominates current ADSL market. Almost no one really use STM based ADSL modem, or dual latency ADSL modem. As a result, most silicon today only support framing mode three (3) to reduce the overhead. This application report mainly focuses on clear EOC capability in framing mode three (3).

| Framing   |                                                                                                                                                     |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Structure | Description                                                                                                                                         |

| 0         | Full overhead framing with asynchronous bit-to-modem timing. (i.e., enabled synchronization control mechanism)                                      |

| 1         | Full overhead framing with synchronous bit-to-modem timing. (i.e., disabled synchronization control mechanism)                                      |

| 2         | Reduced overhead framing with separate fast and sync byte in fast and interleaved latency buffer respectively. (i.e., 64K bits framing overhead)    |

| 3         | Reduced overhead framing with merged fast and sync byte, using either the fast or the interleaved latency buffer. (i.e., 32K bits framing overhead) |

### Table 1. Definition of Framing Modes

## 3 Clear EOC Capability Analysis

### 3.1 ADSL Superframe Structure

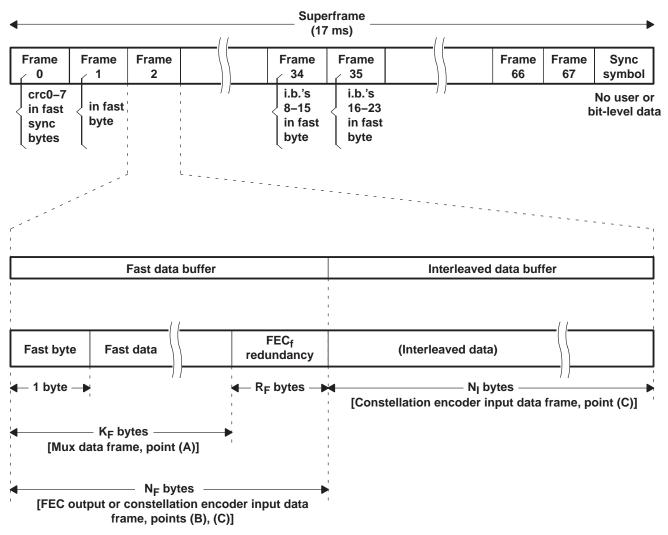

ADSL uses the superframe structure shown in Figure 1. Each superframe is composed of 68 data frames and one synchronization symbol. The period for whole superframe transmission is 68/4KHz=17ms.

## 3.2 Clear EOC Capability in Full Overhead Mode

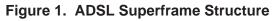

During each ADSL superframe in full overhead mode, the first byte of the fast data buffer ("fast byte") carries the CRC check bits in frame 0 and the OAM indicator bits in frames 1, 34, and 35 (refer to Figure 2). The fast byte in other frames is assigned in even-/odd-frame pairs to either the EOC or to synchronization control of the bearer channels assigned to the fast buffer. As a result, out of 68 data frames in a superframe in 17ms period, 64 frames (except frame 0,1,34, and 35) can carry an EOC byte in full overhead mode.

#### Figure 2. Fast Synchronization Byte ("fast byte") Format in Full Overhead Mode

One EOC message is composed of 13 bits, which are carried by two data frames' fast data buffer (refer to Table 2). When bit5=0, the EOC message is set to autonomous transfer (clear EOC). Bit 6~13, totally 8 bits are payload among 13 bits of an EOC message.

Assuming all EOC bandwidth is occupied by clear EOC, **64frame/2\*8bits payload/17ms=15Kbps** is EOC maximum capability in full overhead mode.

| Table 2 | . EOC | Message | Fields |

|---------|-------|---------|--------|

|---------|-------|---------|--------|

| Field No. | Bit (s) | Description                                                                                                                                                                                                  | Notes                                                                     |

|-----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 1         | 1, 2    | Address field                                                                                                                                                                                                | Can address 4 locations                                                   |

| 2         | 3       | Data (0) or opcode (1) field                                                                                                                                                                                 | Data used for read/write or when an autonomous data message is sent       |

| 3         | 4       | Byte parity field<br>Odd (1) or even (0)                                                                                                                                                                     | Byte order indication for multi-byte transmission                         |

| 4         | 5       | Autonomous message field:<br>ATU-C<br>set to 1 for ATU-C commands sent to ATU-R<br>set to 0 for autonomous transfers<br>ATU-R<br>set to 1 for response to ATU-C command<br>set to 0 for autonomous transfers | Set to 0 by ATU-R to send dying gasp message or autonomous data transfers |

| 5         | 6–13    | Information field                                                                                                                                                                                            | One out of 58 opcodes or 8 bits of data                                   |

## 3.3 Clear EOC Capability in Frame Mode 3

In reduced overhead framing with merged fast and sync bytes single latency mode, data is assigned to only one data buffer (fast or interleaved), see frame mode 3. If data is assigned to only the fast buffer, then only the fast byte shall be used to carry overhead information. If data is assigned to only the interleave buffer, then only the sync byte shall be used to carry overhead information.

The CRC, indicator, EOC, and AOC function shall be carried in a single overhead byte assigned to separate data frames within the superframe structure (refer to Table 3). The CRC remains in frame 0 and the indicator bits in frames 1, 34, and 35. The AOC and EOC bytes are assigned to alternate pairs of frames.

Assuming all EOC bandwidth is occupied by clear EOC, **32frame/2\*8bits payload/17ms=7.5Kbps** is Clear EOC maximum capability in frame mode 3.

### Table 3. Overhead Functions for Reduced Overhead Mode – With Merged Fast and Sync Bytes

| Frame Number                      | (Fast Buffer Only)<br>Fast Byte Format | (Interleaved Buffer Only)<br>Sync Byte Format |

|-----------------------------------|----------------------------------------|-----------------------------------------------|

| 0                                 | Fast CRC                               | Interleaved CRC                               |

| 1                                 | IB0-7                                  | IB0-7                                         |

| 34                                | IB8–15                                 | IB8–15                                        |

| 35                                | IB16–23                                | IB16–23                                       |

| 4n+2, 4n+3<br>with n = 016, n ≠ 8 | EOC or sync (see NOTE)                 | EOC or sync (see NOTE)                        |

| 4n, 4n+1<br>with n = 016, n ≠ 0   | AOC                                    | AOC                                           |

NOTE: In the reduced overhead mode only the "no synchronization action" code shall be used.

## 3.4 Clear EOC Capability in ADSL2

For Clear EOC capability in ADSL2, the answer is quite dynamic.

First of all, the overhead rate defined in ADSL2 varied between MSGMIN (Kbps) and 64 Kbps where MSGMIN is configurable by the far-end modem during G.HS (handshake) to any integer value between 4 Kbps and 64 Kbps.

Secondly, unlike ADSL1 (G.992.1), messages between modems in ADSL2 go over an HDLC-encapsulated overhead channel. This overhead channel is shared by many kinds of messages, including clear EOC, OLR (on-line reconfiguration), power management command, EOC, and other newly defined messages for retrieving OAM information for example.

Moreover, overhead protocol in ADSL2 requires an ACK before new messages are sent. All overhead messages are divided with three different priority. Different priority has different ACK time out limitation.

| Priority Value | Address Field Value<br>(2 LSBs) | Associated<br>Time-Out Value | Command Type                      |

|----------------|---------------------------------|------------------------------|-----------------------------------|

| 1              | 00 <sub>2</sub>                 | 400 ms                       | High-priority overhead messages   |

| 2              | 01 <sub>2</sub>                 | 800 ms                       | Normal-priority overhead messages |

| 3              | 10 <sub>2</sub>                 | 1 s                          | Low-priority overhead messages    |

Table 4. Overhead Message Priority

Although the bandwidth of clear EOC in ADSL2 is not predictable, G.997.1 (G.PLOAM) lists a requirement on the minimum bandwidth of the clear EOC channel at 4kbps.

## 4 References

- 1. DRAFT NEW RECOMMENDATION G.992.1, July 1999, ITU Study Group

- 2. ITU-T Recommendation G.992.3, July 2000, ITU Study Group

- 3. ITU-T Recommendation G.997.1, May 2000, ITU Study Group

## Appendix A Keywords

- EOC: Embedded operations channel

- AOC: ADSL overhead control channel

- **MSGMIN:** Minimum overhead message rate

- **CO:** Central office

- **CPE:** Customer Premise Equipment

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address:

Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2004, Texas Instruments Incorporated