# 20-A, 4.75-V to 14-V INPUT, NON-ISOLATED, WIDE-OUTPUT, DIGITAL POWERTRAIN™ MODULE

Check for Samples: PTD08A020W

#### **FEATURES**

- Up to 20-A Output Current

- 4.75-V to 14-V Input Voltage

- Programmable Wide-Output Voltage (0.7 V to 3.6 V)

- Efficiencies up to 96%

- Digital I/O

- PWM signal

- INHIBIT

- Current limit flag (FAULT)

- Sychronous Rectifier Enable (SRE)

- Analog I/O

- Temperature

- Output currrent

- Safety Agency Approvals: (Pending)

- UL/IEC/CSA-C22.2 60950-1

- Operating Temperature: –40°C to 85°C

#### **APPLICATIONS**

Digital Power Systems using UCD92XX Digital Controllers

## **DESCRIPTION**

The PTD08A020W is a high-performance 20-A rated, non-isolated digital PowerTrain module. This module is the power conversion section of a digital power system which incorporates TI's UCD7230 MOSFET driver IC. The PTD08A020W must be used in conjunction with a digital power controller such as the UCD9240 or UCD9110 family. The PTD08A020W receives control signals from the digital controller and provides parametric and status information back to the digital controller. Together, PowerTrain modules and a digital power controller form a sophisticated, robust, and easily configured power management solution.

Operating from an input voltage range of 4.75 V to 14 V, the PTD08A020W provides step-down power conversion to a wide range of output voltages from, 0.7 V to 3.6 V. The wide input voltage range makes the PTD08A020W particularly suitable for advanced computing and server applications that utilize a loosely regulated 8-V, 9.6-V or 12-V intermediate distribution bus. Additionally, the wide input voltage range increases design flexibility by supporting operation with tightly regulated 5-V or 12-V intermediate bus architectures.

The module incorporates output over-current and temperature monitoring which protects against most load faults. Output current and module temperature signals are provided for the digital controller to permit user defined over-current and over-temperature warning and fault scerarios.

The module uses double-sided surface mount construction to provide a low profile and compact footprint. Package options include both through-hole and surface mount configurations that are lead (Pb) - free and RoHS compatible.

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

POWERTRAIN is a trademark of Texas Instruments.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

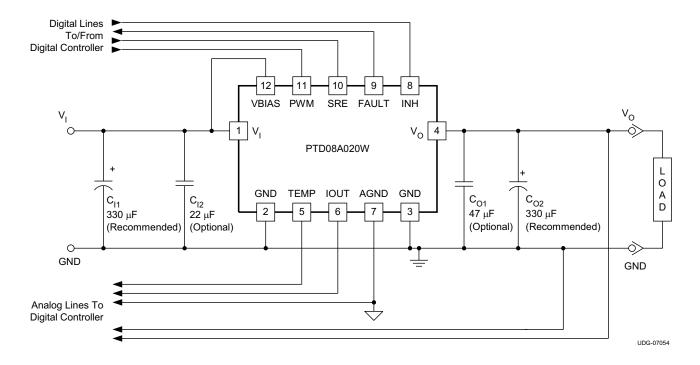

# Standard PTD08A020W Application

#### **ORDERING INFORMATION**

For the most current package and ordering information, see the Package Option Addendum at the end of this datasheet, or see the TI website at www.ti.com.

# **DATASHEET TABLE OF CONTENTS**

| DATASHEET SECTION                              | PAGE NUMBER |

|------------------------------------------------|-------------|

| ENVIRONMENTAL AND ABSOLUTE MAXIMUM RATINGS     | 3           |

| ELECTRICAL CHARACTERISTICS TABLE               | 4           |

| TERMINAL FUNCTIONS                             | 5           |

| TYPICAL CHARACTERISTICS (V <sub>I</sub> = 12V) | 6           |

| TYPICAL CHARACTERISTICS (V <sub>I</sub> = 5V)  | 8           |

| TYPICAL APPLICATION SCHEMATIC                  | 10          |

| GRAPHICAL USER INTERFACE VALUES                | 11          |

| TRAY DRAWINGS                                  | 12          |

# **ENVIRONMENTAL AND ABSOLUTE MAXIMUM RATINGS**

(Voltages are with respect to GND)

|                   |                             |                                                                       |             |            | UNIT               |

|-------------------|-----------------------------|-----------------------------------------------------------------------|-------------|------------|--------------------|

| VI                | Input voltage               |                                                                       |             | 16         | V                  |

| V <sub>B</sub>    | Bias voltage                |                                                                       |             | 16         | V                  |

| T <sub>A</sub>    | Operating temperature range | Over V <sub>I</sub> range                                             |             | -40 to 85  |                    |

| T <sub>wave</sub> | Wave soldering temperature  | Surface temperature of module body or pins for 5 seconds maximum.     | suffix AD   | 260        | °C                 |

| T <sub>stg</sub>  | Storage temperature         | Storage temperature of module removed from shipp                      | ing package | -55 to 125 |                    |

| T <sub>pkg</sub>  | Packaging temperature       | emperature Shipping Tray or Tape and Reel storage or bake temperature |             |            |                    |

|                   | Mechanical shock            | Per Mil-STD-883D, Method 2002.3, 1 msec, 1/2 sine, mounted            | suffix AD   | 250        | G                  |

|                   | Mechanical vibration        | Mil-STD-883D, Method 2007.2, 20-2000 Hz                               |             | 15         |                    |

|                   | Weight                      |                                                                       | 7.4         | grams      |                    |

| MTBF              | Reliability                 | Per Telcordia SR-332, 50% stress, T <sub>A</sub> = 40°C, ground       | nd benign   | 9.26       | 10 <sup>6</sup> Hr |

|                   | Flammability                | Meets UL94V-O                                                         |             |            |                    |

#### **ELECTRICAL CHARACTERISTICS**

#### PTD08A020W

$T_A$ = 25°C,  $F_{SW}$ = 350kHz,  $V_I$ = 12 V,  $V_O$ = 3.3 V,  $V_B$ =  $V_I$ ,  $C_{I1}$ = 330  $\mu$ F,  $C_{I2}$ = 22  $\mu$ F ceramic,  $C_{O1}$ = 47  $\mu$ F ceramic,  $C_{O2}$ = 330  $\mu$ F, and  $I_O$ =  $I_{O(max)}$  (unless otherwise stated)

|                   | PARAMETER                            |                                                         | TEST CONDITIONS                                    |                           | PT   | D08A010\ | N                 | UNIT    |

|-------------------|--------------------------------------|---------------------------------------------------------|----------------------------------------------------|---------------------------|------|----------|-------------------|---------|

|                   |                                      |                                                         |                                                    |                           | MIN  | TYP      | MAX               |         |

| lo                | Output current                       | Over V <sub>O</sub> range                               | Over V <sub>O</sub> range 25°C, natural convection |                           |      |          | 20                | Α       |

| VI                | Input voltage range                  | Over I <sub>O</sub> range                               |                                                    |                           | 4.75 |          | 14 <sup>(1)</sup> | V       |

| V <sub>OADJ</sub> | Output voltage adjust range          | Over I <sub>O</sub> range                               | Over I <sub>O</sub> range                          |                           |      |          | 3.6               | V       |

|                   |                                      |                                                         |                                                    | V <sub>O</sub> = 3.3 V    |      | 91%      |                   |         |

|                   |                                      |                                                         |                                                    |                           |      | 89%      |                   |         |

|                   | Efficiency                           | I <sub>O</sub> = 20 A,                                  |                                                    | V <sub>O</sub> = 1.8 V    |      | 86%      |                   |         |

| η                 | Efficiency                           | fs = 350 kHz                                            |                                                    | $V_0 = 1.5 \text{ V}$     |      | 84%      |                   |         |

|                   |                                      |                                                         |                                                    | V <sub>O</sub> = 1.2 V    |      | 83%      |                   |         |

|                   |                                      |                                                         |                                                    | V <sub>O</sub> = 1.0 V    |      | 80%      |                   |         |

| $V_{OPP}$         | V <sub>O</sub> Ripple (peak-to-peak) | 20-MHz bandwidth                                        | 20-MHz bandwidth                                   |                           |      | 20       |                   | $mV_PP$ |

| $V_{B}$           | Bias voltage                         |                                                         |                                                    |                           | 4.75 |          | 14                | V       |

| V <sub>B</sub>    | Bias voltage under voltage           |                                                         |                                                    | V <sub>B</sub> increasing | 4.25 | 4.5      | 4.75              | V       |

| บงั้เด            | lockout                              |                                                         |                                                    | V <sub>B</sub> decreasing | 4.0  | 4.25     | 4.5               | V       |

|                   | Dies surrent                         | Inhibit (pin 8) to AGN                                  | Standby                                            |                           | 5    |          | A                 |         |

| I <sub>B</sub>    | Bias current                         | Switching                                               |                                                    |                           |      | 42       |                   | mA      |

| V <sub>IH</sub>   | High-level input voltage             | SRE, INH, & PWM input levels                            |                                                    |                           | 2.0  |          | 5.5               | V       |

| $V_{IL}$          | Low-level input voltage              | SRE, INH, & PVVIVI II                                   |                                                    |                           | 0.8  | V        |                   |         |

|                   | DWM input                            | Frequency range                                         |                                                    |                           |      |          | 500               | kHz     |

|                   | PWM input                            | Pulse width limits                                      |                                                    |                           |      |          |                   | ns      |

|                   |                                      | Range                                                   |                                                    |                           |      |          | 125               | °C      |

|                   | TEMP output                          | Accuracy, -40°C ≤ T <sub>A</sub> ≤ 85°C                 |                                                    |                           |      |          | +6.0              | °C      |

|                   | TEMP output                          | Slope                                                   |                                                    |                           |      | 10       |                   | mV/°C   |

|                   |                                      | Offset, T <sub>A</sub> = 0°C                            |                                                    | 500                       |      | mV       |                   |         |

| $V_{OH}$          |                                      | High-level output vol                                   | Itage, I <sub>FAULT</sub> = 4mA                    |                           | 2.7  | 3.3      |                   | V       |

| $V_{OL}$          | FAULT output                         | Low-level output volt                                   | tage, I <sub>FAULT</sub> = 4mA                     |                           |      | 0        | 0.6               | V       |

| $I_{LIM}$         |                                      | Overcurrent threshold; Reset, followed by auto-recovery |                                                    |                           |      | 35       |                   | Α       |

|                   |                                      | Range                                                   |                                                    |                           |      |          | 3.5               | V       |

|                   | IOUT output                          | Gain                                                    |                                                    |                           |      | 66       | 86                | mV/A    |

|                   | 1001 output                          | Offset                                                  |                                                    |                           |      | 0.6      | 0.76              | V       |

|                   |                                      | Output Impedance                                        |                                                    |                           |      | 15       | 20                | kΩ      |

| Cı                | External input capacitance           |                                                         | Nonceramic                                         |                           |      | 330 (2)  |                   |         |

| <u></u>           | External input capacitance           | Ceramic                                                 |                                                    |                           |      | 22 (2)   |                   | μF      |

|                   |                                      | Canacitanas Valus                                       |                                                    | Nonceramic                |      | 330 (3)  | 10,000 (4)        |         |

| $C_{O}$           | External output capacitance          | Capacitance Value                                       |                                                    | Ceramic                   |      | 47 (3)   | (3)               | μF      |

|                   |                                      | Equivalent series res                                   | Equivalent series resistance (non-ceramic)         |                           |      |          | -                 | mΩ      |

- (1) The maximum input voltage is duty cycle limited to (V<sub>O</sub>/(130ns × F<sub>SW</sub>)) or 14 V, whichever is less. The maximum allowable input voltage is a function of switching frequency.

- (2) A 22 μF ceramic input capacitor is recommended for operation. An additional 330 μF bulk capacitor rated for a minimum of 500mA rms of ripple current is recommended. Refer to the UCD9240 controller datasheet and user interface for application specific capacitor specifications.

- (3) A 47 μF ceramic output capacitor is recommended for operation. An additional 330 μF bulk capacitor is recommended for improved transient response. See the related Application Information section for further guidance. Refer to the UCD9240 controller datasheet and user interface for application specific capacitor specifications.

- (4) 10,000 μF is the calculated maximum output capacitance given a 1V/msec output voltage rise time. Additional capacitance or increasing the output voltage rise rate may trigger the overcurrent threshold at start-up.

- (5) This is the minimum ESR for all non-ceramic output capacitance. Refer to the UCD9240 controller datasheet and user interface for application specific capacitor specifications.

Submit Documentation Feedback

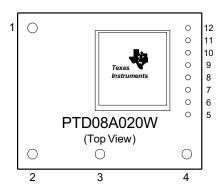

# **TERMINAL FUNCTIONS**

| TERMINAL           |     | DESCRIPTION                                                                                                                                                                                                                                                                                               |  |  |  |  |

|--------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME               | NO. | SCRIPTION                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| VI                 | 1   | The positive input voltage power node to the module, which is referenced to common GND.                                                                                                                                                                                                                   |  |  |  |  |

| 2                  |     | This is the common ground connection for the V and V neuron connections                                                                                                                                                                                                                                   |  |  |  |  |

| GND                | 3   | This is the common ground connection for the $V_I$ and $V_O$ power connections.                                                                                                                                                                                                                           |  |  |  |  |

| Vo                 | 4   | The regulated positive power output with respect to GND.                                                                                                                                                                                                                                                  |  |  |  |  |

| TEMP               | 5   | Temperature sense output. The voltage level on this pin represents the temperature of the module.                                                                                                                                                                                                         |  |  |  |  |

| IOUT               | 6   | Current sense output. The voltage level on this pin represents the average output current of the module.                                                                                                                                                                                                  |  |  |  |  |

| AGND               | 7   | Analog ground return. It is the 0 $V_{dc}$ reference for the control inputs.                                                                                                                                                                                                                              |  |  |  |  |

| INH <sup>(1)</sup> | 8   | The inhibit pin is a negative logic input that is referenced to AGND. Applying a low-level signal to this pin disables the module and turns off the output voltage. A 10 k $\Omega$ pull-up to 3.3 V or 5 V is required if the INH signal is not used.                                                    |  |  |  |  |

| FAULT              | 9   | Current limit flag. The Fault signal is a 3.3 V digital output which is latched high after an over-current condition. The Fault is reset after two complete PWM cycles without an over-current condition (third rising edge of the PWM).                                                                  |  |  |  |  |

| SRE                | 10  | Synchronized Rectifier Enable. This pin is a high impedance digital input. A 3.3 V or 5 V logic level signals is used to enable the synchronous rectifier switch. When this signal is high, the module will source and sink output current. When this signal is low, the module will only source current. |  |  |  |  |

| PWM                | 11  | This is the PWM input pin. It is a high impedance digital input that accepts 3.3 V or 5 V logic level signals up to 500 MHz.                                                                                                                                                                              |  |  |  |  |

| VBIAS              | 12  | Bias voltage supply required to power internal circuitry. For optimal performance connect VBIAS to $V_1$ .                                                                                                                                                                                                |  |  |  |  |

(1) Denotes negative logic: Open = Normal operation, Ground = Function active

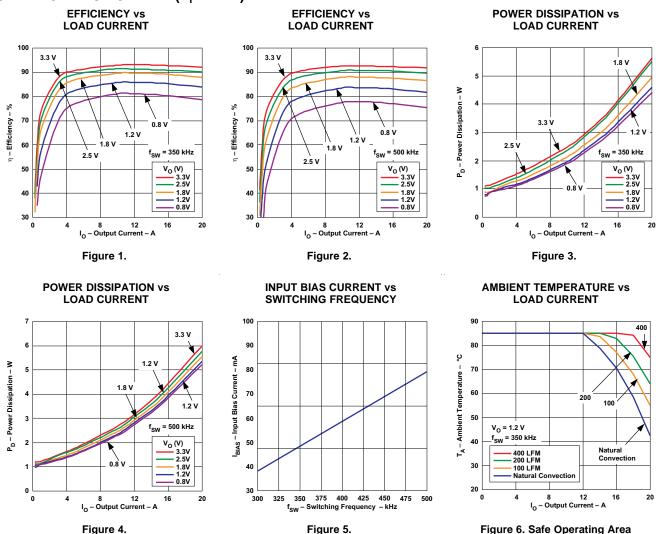

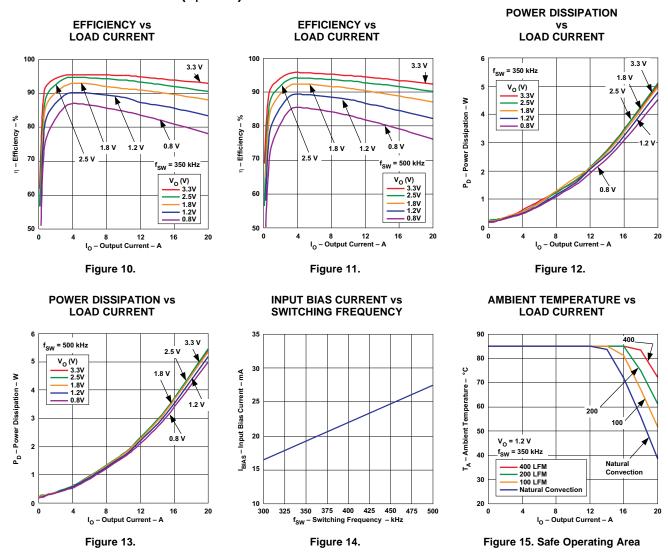

#### TYPICAL CHARACTERISTICS(1) (2)

# CHARACTERISTIC DATA $(V_1 = 12 V)$

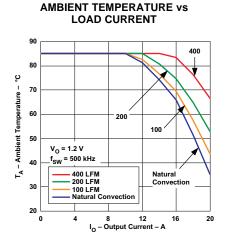

<sup>(1)</sup> The electrical characteristic data has been developed from actual products tested at 25°C. This data is considered typical for the converter. Applies to Figure 1 thru Figure 5.

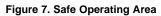

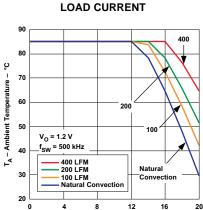

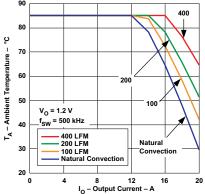

<sup>(2)</sup> The temperature derating curves represent the conditions at which internal components are at or below the manufacturer's maximum operating temperatures. Derating limits apply to modules soldered directly to a 100 mm x 100 mm double-sided PCB with 2 oz. copper. Please refer to the mechanical specification for more information. Applies to Figure 6 thru Figure 9.

# TYPICAL CHARACTERISTICS(3) (4) (continued)

Figure 8. Safe Operating Area

Figure 9. Safe Operating Area

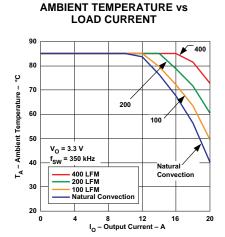

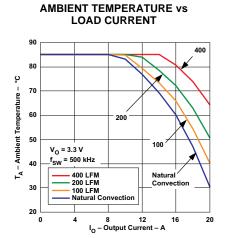

#### TYPICAL CHARACTERISTICS(1) (2)

# CHARACTERISTIC DATA $(V_1 = 5 V)$

<sup>(1)</sup> The electrical characteristic data has been developed from actual products tested at 25°C. This data is considered typical for the converter. Applies to Figure 10 thru Figure 14.

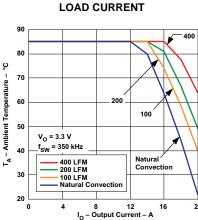

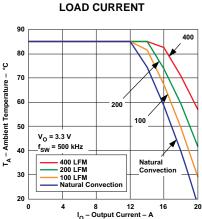

<sup>(2)</sup> The temperature derating curves represent the conditions at which internal components are at or below the manufacturer's maximum operating temperatures. Derating limits apply to modules soldered directly to a 100 mm x 100 mm double-sided PCB with 2 oz. copper. Please refer to the mechanical specification for more information. Applies to Figure 15 thru Figure 18.

**AMBIENT TEMPERATURE vs**

# TYPICAL CHARACTERISTICS(3) (4) (continued) **AMBIENT TEMPERATURE vs**

**AMBIENT TEMPERATURE vs**

Figure 16. Safe Operating Area

Figure 17. Safe Operating Area

Figure 18. Safe Operating Area

#### **APPLICATION INFORMATION**

# **Digital Power**

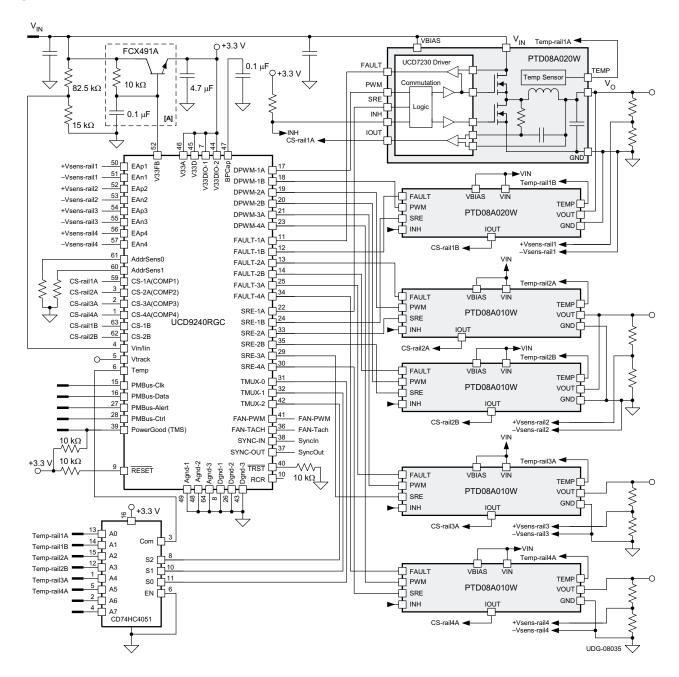

Figure 19. Typical Application Schematic

Figure 19 shows the UCD9240 power supply controller working in a system which requires the regulation of four independent power supplies. The loop for each power supply is created by the respective voltage outputs feeding into the Error ADC differential inputs, and completed by DPWM outputs feeding into the UCD7230 drivers which are shown on the PTD08A010W and PTD08A020W modules.

Submit Documentation Feedback

# **UCD9240 Graphical User Interface (GUI)**

When using the UCD9240 digital controller along with digital PowerTrain modules to design a digital power system, several internal parameters of the modules are required to run the Fusion Digital Power Designer GUI. See the plant parameters below for the PTD08A010W and PTD08A020W digital PowerTrain modules.

#### Table 1. PTD08A010W Plant Parameters

| PTD08A010W Plant Parameters                                              |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------|--|--|--|--|--|--|--|

| L (μH) DCR (m $\Omega$ ) Rds-on-hi (m $\Omega$ ) Rds-on-lo (m $\Omega$ ) |  |  |  |  |  |  |  |

| 0.90 2.2 3.6 3.6                                                         |  |  |  |  |  |  |  |

#### Table 2. PTD08A020W Plant Parameters

| PTD08A020W Plant Parameters                                              |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| L (μH) DCR (m $\Omega$ ) Rds-on-hi (m $\Omega$ ) Rds-on-lo (m $\Omega$ ) |  |  |  |  |  |  |  |  |

| 1.0 1.5 5.0 2.5                                                          |  |  |  |  |  |  |  |  |

Internal output capacitance is present on the digital PowerTrain modules themselves. When using the GUI interface this capacitance information must be included along with any additional external capacitance. See the capacitor parameters below for the PTD08A010W and PTD08A020W digital PowerTrain modules.

#### **Table 3. PTD08A010W Capacitor Parameters**

| PTD08A010W Capacitor Parameters   |     |     |   |  |  |  |  |

|-----------------------------------|-----|-----|---|--|--|--|--|

| C (μF) ESR (mΩ) ESL (nH) Quantity |     |     |   |  |  |  |  |

| 47                                | 1.5 | 2.5 | 1 |  |  |  |  |

## **Table 4. PTD08A020W Capacitor Parameters**

| PTD08A020W Capacitor Parameters   |     |     |   |  |  |  |  |

|-----------------------------------|-----|-----|---|--|--|--|--|

| C (μF) ESR (mΩ) ESL (nH) Quantity |     |     |   |  |  |  |  |

| 47                                | 1.5 | 2.5 | 2 |  |  |  |  |

Copyright © 2007–2010, Texas Instruments Incorporated

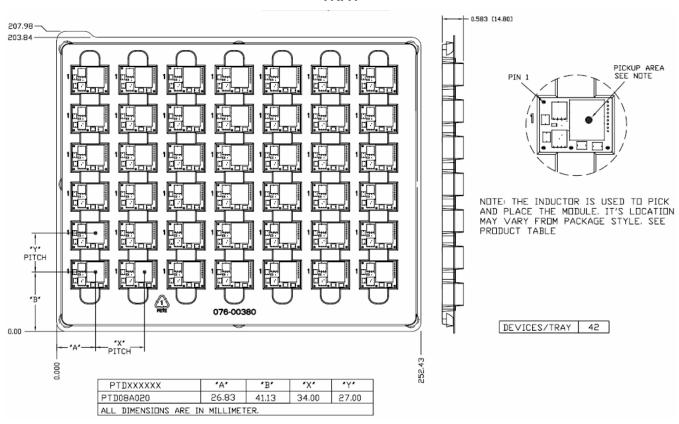

# **TRAY**

www.ti.com 11-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins                    | Package qty   Carrier | RoHS    | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow                 | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|-----------------------------------|-----------------------|---------|-------------------------------|--------------------------------------------|--------------|------------------|

|                       |        |               |                                   |                       |         | (4)                           | (5)                                        |              |                  |

| PTD08A020WAD          | Active | Production    | Through-Hole<br>Module (EGP)   12 | 42   TIW TRAY         | In-Work | SN                            | Level-1-235C-UNLIM/<br>Level-3-260C-168HRS | -40 to 85    |                  |

| PTD08A020WAD.B        | Active | Production    | Through-Hole<br>Module (EGP)   12 | 42   TIW TRAY         | In-Work | SN                            | Level-1-235C-UNLIM/<br>Level-3-260C-168HRS | -40 to 85    |                  |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

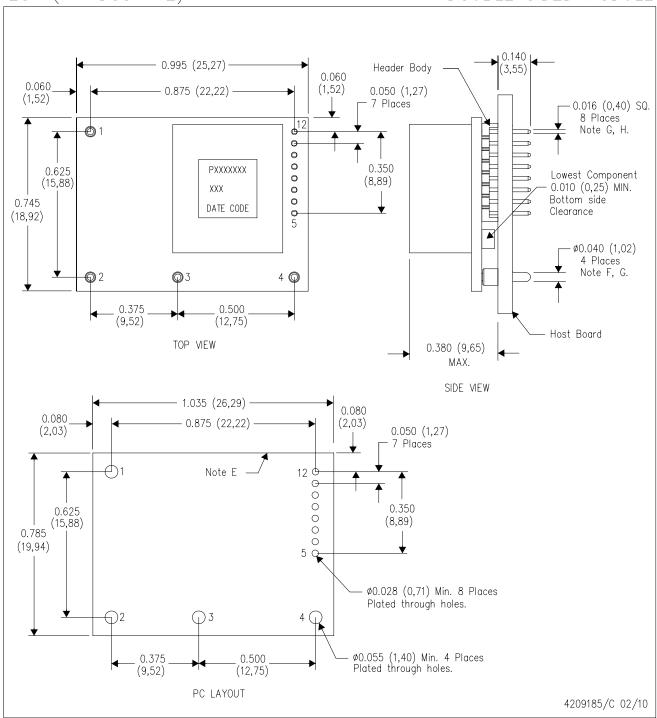

EGP (R-PDSS-T12)

DOUBLE SIDED MODULE

NOTES:

- A. All linear dimensions are in inches (mm). B. This drawing is subject to change without notice.

- C. 2 place decimals are  $\pm 0.030$  ( $\pm 0.76$ mm). D. 3 place decimals are  $\pm 0.010$  ( $\pm 0.25$ mm).

- E. Recommended keep out area for user components.

- F. Pins are 0.040" (1,02) diameter with 0.070" (1,78) diameter standoff shoulder.

- G. Header pins are 0.016 (0,40) SQ.

- H. All pins: Material Copper Alloy

Finish - Tin (100%) over Nickel plate

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025