www.ti.com

## ADC08B3000 8-Bit, 3 GSPS, High Performance, Low Power A/D Converter with 4K Buffer

Check for Samples: ADC08B3000

#### **FEATURES**

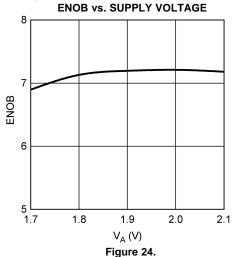

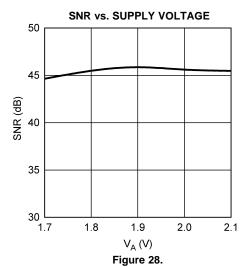

- Single +1.9V ±0.1V Operation

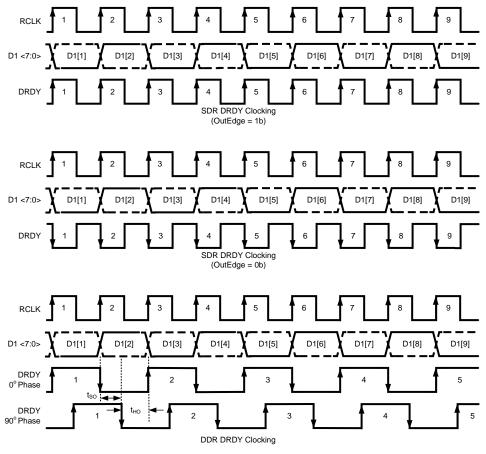

- Choice of SDR or DDR Output Clocking

- Internal selectable 4K Data Buffer

- Serial Interface for Extended Control

- Adjustment of Input Full-Scale Range, Offset and Clock Phase

- Duty Cycle Corrected Sample Clock

- Test Pattern Output Capability

#### **APPLICATIONS**

- Distance Ranging

- Test and Measurement

#### **KEY SPECIFICATIONS**

Resolution: 8 Bits

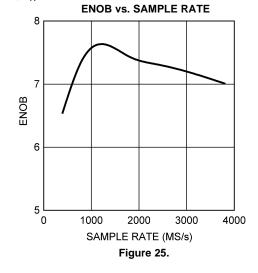

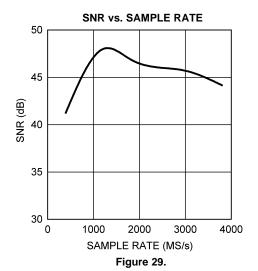

Max Conversion Rate: 3 Gsps (min)

Code Error Rate: 10<sup>-18</sup> (typ)

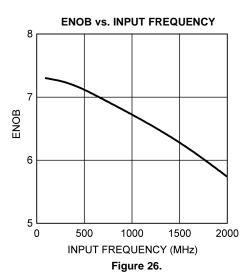

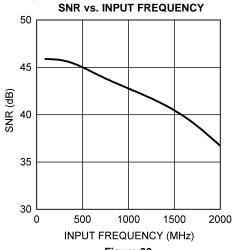

ENOB @ 748 MHz Input: 7.1 Bits (typ)

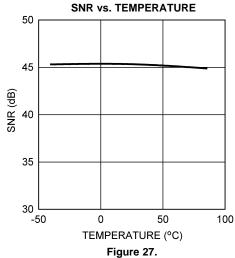

SNR @ 748 MHz: 44.9 dB (typ)

Full Power Bandwidth: 3 GHz (typ)

Power Consumption

Full Power Capure: 1.6 W (typ)Power Down Mode: 25 mW (typ)

#### DESCRIPTION

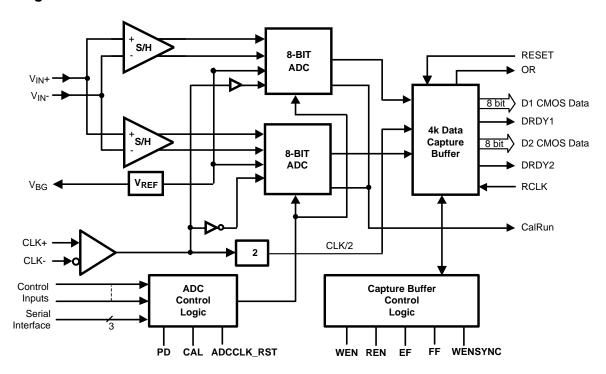

The ADC08B3000 is a single, low power, high performance CMOS analog-to-digital converter that digitizes signals to 8 bits resolution at sample rates up to 3.4 Gigasamples Per Second, (Gsps). Consuming a typical 1.6 Watts at 3 Gsps from a single 1.9 Volt supply, this device is ensured to have no missing codes over the full operating temperature The unique folding and interpolating architecture, the fully differential comparator design, the innovative design of the internal sample-and-hold amplifier and the calibration scheme enable an excellent response of all dynamic parameters up to Nyquist, producing a high 7.1 Effective Number Of Bits, (ENOB), with a 748 MHz input signal and a 3 GHz sample rate while providing a 10<sup>-18</sup> Code Error Rate. A sample rate of 3 Gsps is achieved by interleaving two ADCs, each operating at 1.5 Gsps. Output formatting is offset binary. The device contains a 4K Capture Buffer with output on two 8-bit Low Voltage CMOS (LVCMOS) output buses at rates up to 200MHz.

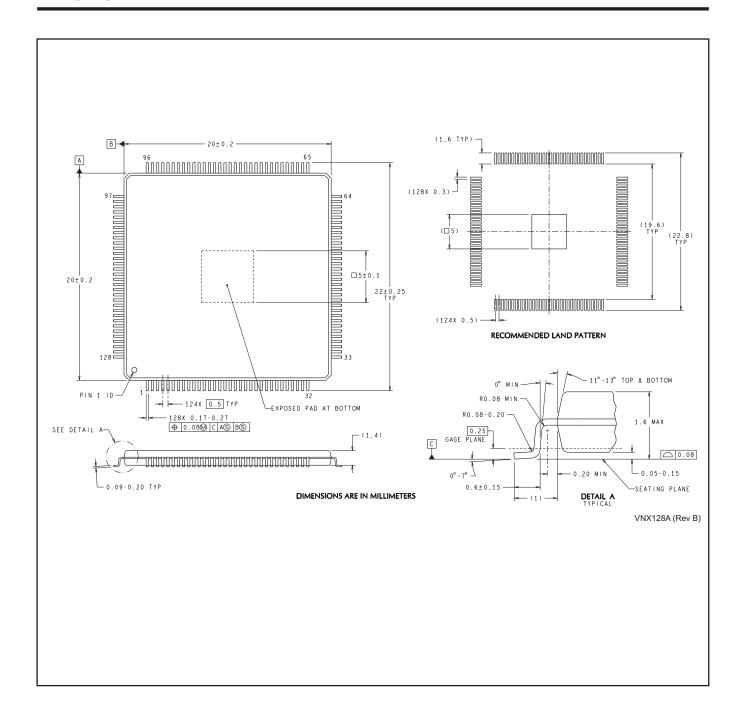

The converter typically consumes less than 25 mW in the Power Down Mode and is available in a 128-lead, thermally enhanced exposed pad HLQFP and operates over the Industrial (-40°C  $\leq$  T<sub>A</sub>  $\leq$  +85°C) temperature range.

### **Block Diagram**

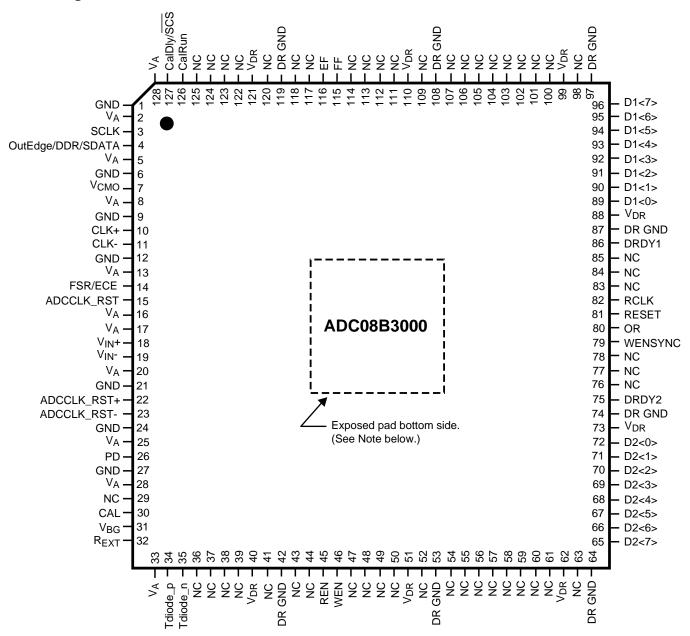

### **Pin Configuration**

Note: The exposed pad on the bottom of the package must be soldered to a ground plane to ensure rated performance.

Figure 1. HLQFP Package See Package Number NNB0128A

### Pin Descriptions and Equivalent Circuits

|         | Pin Descriptions and Equivalent Circuits |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|---------|------------------------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| - N     | Pin Functions                            |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

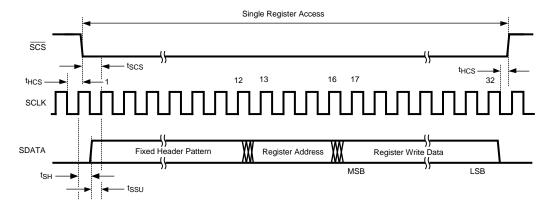

| Pin No. | Symbol<br>SCLK                           | Equivalent Circuit                             | Serial Interface Clock (Input): LVCMOS - When the extended control mode is enabled, this pin functions as the SCLK input which clocks in the serial data. See NORMAL/EXTENDED CONTROL for details on the extended control mode. See THE SERIAL INTERFACE for description of the serial interface. Ground this pin when the ADC is not in extended control mode.                                                                                                                                                                                                                                       |  |  |  |  |

| 4       | OutEdge / DDR /<br>SDATA                 | GND  VA  SOK  SOK  SOK  SOK  SOK  SOK  SOK  SO | Edge Select / Double Data Rate / Serial Data (Input): LVCMOS - When this input is low or high, it sets the edge of DRDY at which the output data transitions. (See OutEdge Setting). When this pin is floating or connected to 1/2 the supply voltage, DDR clocking is enabled. When the extended control mode is enabled, this pin functions as the SDATA input. See NORMAL/EXTENDED CONTROL for details on the extended control mode. See THE SERIAL INTERFACE for description of the serial interface.                                                                                             |  |  |  |  |

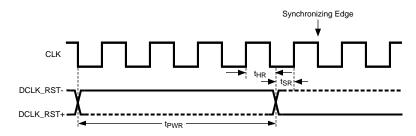

| 15      | ADCCLK_RST                               | V <sub>A</sub>                                 | ADC Sample Clock Reset (Input): LVCMOS - A positive pulse on this pin is used to reset and synchronize the ADC08B3000 with other ADC08B3000s in the system. See MULTIPLE ADC SYNCHRONIZATION. When bit 14 in the Configuration Register (address 1h) is set to 0b, this single-ended ADCCLK_RST pin is selected. See description of pins 22, 23.                                                                                                                                                                                                                                                      |  |  |  |  |

| 26      | PD                                       |                                                | Power Down (Input): LVCMOS - A logic high on the PD pin puts the device, except for the Capture Buffer, into the Power Down Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

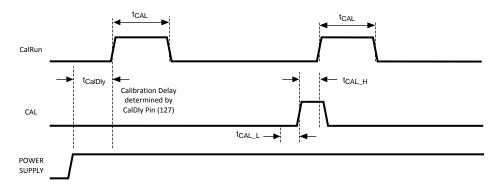

| 30      | CAL                                      | GND                                            | Calibration Cycle Initiate (Input): LVCMOS - A minimum 80 input clock cycles logic low followed by a minimum of 80 input clock cycles high on this pin initiates the self calibration sequence. See Calibration for an overview of calibration and On-Command Calibration for a description of on-command calibration.                                                                                                                                                                                                                                                                                |  |  |  |  |

| 14      | FSR/ECE                                  | VA 200k 200k 50k 8 pF                          | Full Scale Range Select / Extended Control Enable (Input): LVCMOS - In the Normal (Non-Extended) Control Mode, a logic low on this pin sets the full-scale differential input range to 600 mV <sub>P-P</sub> . A logic high on this pin sets the full-scale differential input range to 810 mV <sub>P-P</sub> . See The Analog Inputs. To enable the extended control mode, whereby the serial interface and control registers are employed, allow this pin to float or connect it to a voltage equal to V <sub>A</sub> /2. See NORMAL/EXTENDED CONTROL for information on the extended control mode. |  |  |  |  |

| 127     | CalDly / SCS                             | SOND SOND                                      | Calibration Delay / Serial Interface Chip Select (Input): LVCMOS - With a logic high or low on pin 14, this pin functions as Calibration Delay and sets the number of input clock cycles after power up before calibration begins (See Calibration). With pin 14 floating, this pin acts as the chip select pin for the serial interface input and the CalDly value becomes "0" (short delay with no provision for a long power-up calibration delay).                                                                                                                                                |  |  |  |  |

| Pin Functions |                                        |                                                         |                                                                                                                                                                                                                                                                                                                                                                           |  |

|---------------|----------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin No.       | Symbol                                 | Equivalent Circuit                                      | Description                                                                                                                                                                                                                                                                                                                                                               |  |

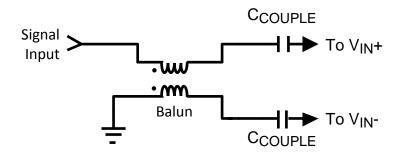

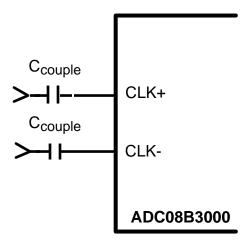

| 10<br>11      | CLK+<br>CLK-                           | AGND 50k VBIAS AGND                                     | Sample Clock Input (Input): LVDS - The differential clock signal must be a.c. coupled to these pins. The input signal is sampled on both the rising and falling edge of CLK. See Acquiring the Input for a description of acquiring the input, Clocking and THE SAMPLE CLOCK INPUT for an overview of the clock inputs.                                                   |  |

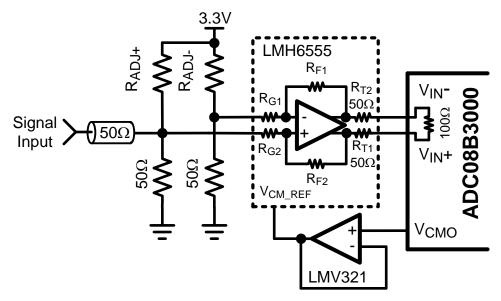

| 18<br>19      | V <sub>IN</sub> +<br>V <sub>IN</sub> - | VA<br>AGND  VCMO  Control from VCMO  AGND  AGND         | Signal Input (Input): Analog - Analog Signal Input that must be applied differentially. The differential full-scale input is defined by pin 14 in the Normal mode and by the Full-Scale Voltage Adjust register in the Extended Control mode. See REGISTER DESCRIPTION.                                                                                                   |  |

| 22<br>23      | ADCCLK_RST+<br>ADCCLK_RST-             | AGND NA 100                                             | Sample Clock Reset (Input): LVDS - A positive differential pulse on these pins is used to reset and synchronize the ADC sample clock when multiple ADCs are used. See MULTIPLE ADC SYNCHRONIZATION. When bit 14 in the Configuration Register (address 1h) is set to 1b, these differential ADCCLK_RST± pins are selected. See description for pin 15.                    |  |

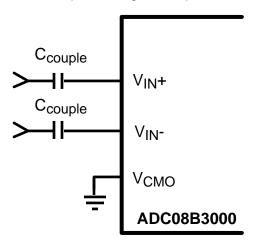

| 7             | V <sub>СМО</sub>                       | V <sub>CMO</sub> V <sub>CMO</sub> AC Couple Enable S pF | Common Mode Voltage (Output): ANALOG - The voltage output at this pin is required to be the common mode input voltage at $V_{IN}$ + and $V_{IN}$ - when d.c. coupling is used. This pin should be grounded when a.c. coupling is used at the analog input. This pin is capable of sourcing or sinking 100 $\mu$ A and can drive a load up to 80 pF. See THE ANALOG INPUT. |  |

| 31            | $V_{BG}$                               |                                                         | Bandgap Output Voltage (Output): Analog - Capable of 100 μA source/sink and can drive a load up to 80 pF.                                                                                                                                                                                                                                                                 |  |

Copyright © 2006–2013, Texas Instruments Incorporated

|                                              | Pin Functions                                                                 |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|----------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin No.                                      | Symbol                                                                        | Equivalent Circuit                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 126                                          | CalRun                                                                        | DGND                                                 | Calibration Running (Output): LVCMOS - This pin is at a logic high while a calibration is running.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 32                                           | R <sub>EXT</sub>                                                              | V <sub>A</sub> O  O  O  O  O  O  O  O  O  O  O  O  O | External Bias Resistor Connection Analog - Nominal value is 3.3k-Ohms (±0.1%) to ground. See Calibration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 34<br>35                                     | Tdiode_P<br>Tdiode_N                                                          | Tdiode_P O                                           | Temperature Diode Analog - Positive (Anode) and Negative (Cathode). These pins may be used for die temperature measurements, however no specified accuracy is implied or ensured. See Thermal Management.                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 72<br>71<br>70<br>69<br>68<br>67<br>66<br>65 | D2<0> D2<1> D2<1> D2<2> D2<3> D2<4> D2<5> D2<5> D2<5>                         |                                                      | Digital Data Output 2 (Output): LVCMOS - When the REN input is asserted and Two Port Enable, (TPE) is set to 1b in the Capture Buffer register (addr: Fh, bit: 12), half of the data is read from the capture buffer and presented at this port synchronous with each rising edge of Read CLK (RCLK). The data on this port is the earlier sample data vs. the Digital Data Output 1 data. When Two Port Enable is set to 0b in the Capture Buffer register, data output 2 is high-impedance.                                                                                                                                              |  |  |

| 75                                           | DRDY2                                                                         | V <sub>D</sub>                                       | Data Ready 2 (Output): LVCMOS - DRDY is generated by RCLK and is synchronized to the output data. The use of this pin assists in eliminating the latency uncertainty between when Read CLK (RCLK) transitions and when data transitions at the output.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 89<br>90<br>91<br>92<br>93<br>94<br>95<br>96 | D1<0><br>D1<1><br>D1<2><br>D1<3><br>D1<3><br>D1<5><br>D1<5><br>D1<6><br>D1<7> | DGND                                                 | Digital Data Output 1 (Output): LVCMOS - When the REN input is asserted, data is read from the capture buffer and presented at this port synchronous with each rising edge of Read CLK (RCLK). When the Two Port Enable bit (TPE) is set to 1b in the Capture Buffer register (addr: Fh, bit: 12), half of the data is presented at this port. The data on this port is the later sample data vs. the Digital Data Output 2 data. When REN is deasserted, this output holds the data from the previous read. When Two Port Enable is set to 0b in the Capture Buffer register, this port presents all of the data from the Capture Buffer. |  |  |

| 86                                           | DRDY1                                                                         |                                                      | Data Ready 1 (Output): LVCMOS - DRDY is generated by RCLK and is synchronized to the output data. The use of this pin assists in eliminating the latency uncertainty between when Read CLK (RCLK) transitions and when data transitions at the output.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|                                                   | Pin Functions  |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|---------------------------------------------------|----------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin No.                                           | Symbol         | Equivalent Circuit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

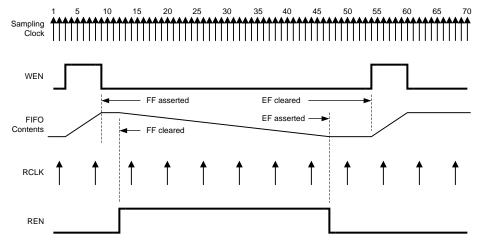

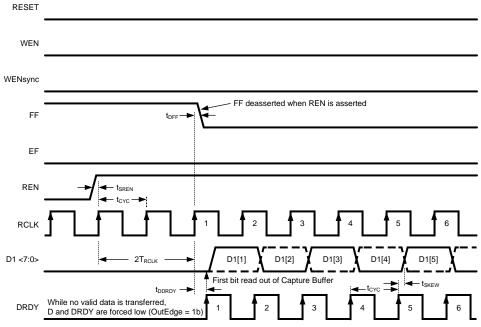

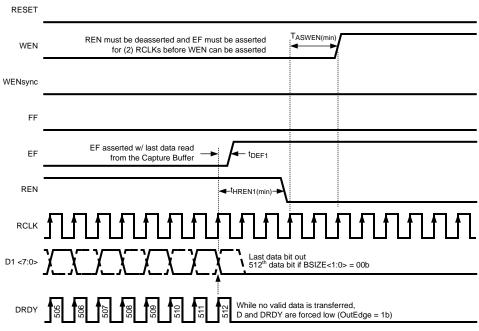

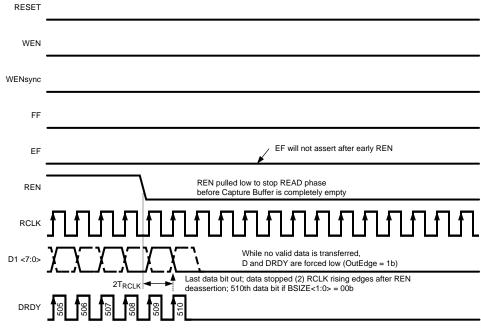

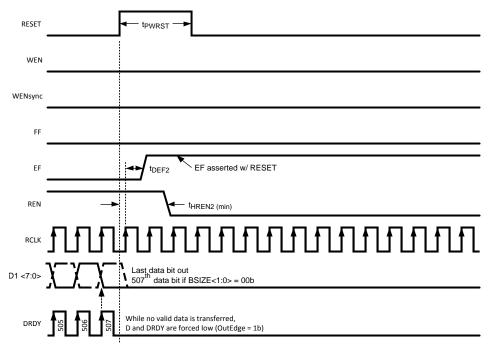

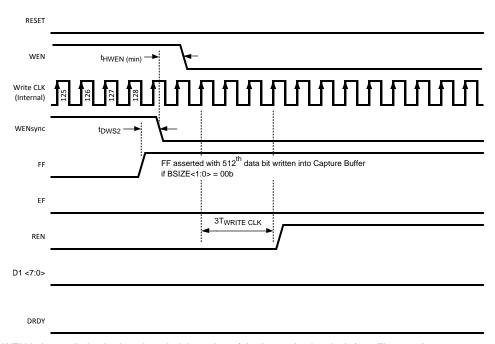

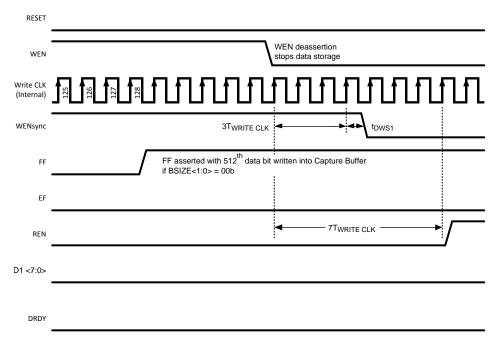

| 45                                                | REN            | VA                 | Read Enable (Input): LVCMOS - A logic high on this input causes a byte of data to be read from the Capture Buffer with each RCLK cycle. This signal must not be asserted while the WEN is already asserted. See Coordinating Read Enable (REN) and Write Enable (WEN).                                                                                                                                                                                                                   |  |  |

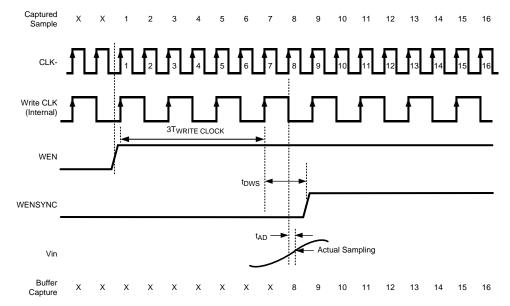

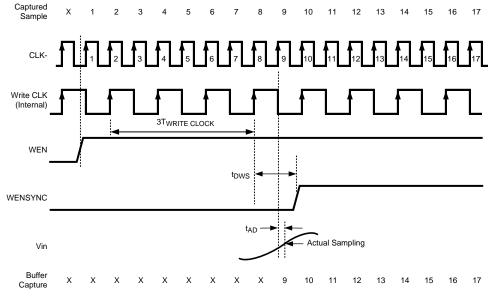

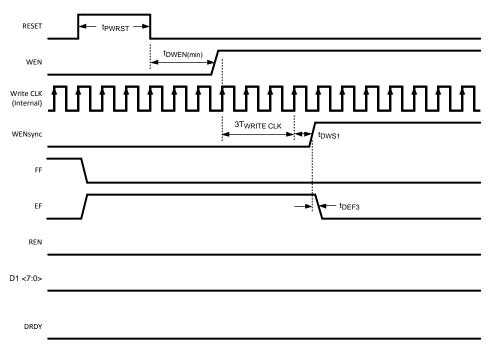

| 46                                                | WEN            |                    | Write Enable (Input): LVCMOS - A logic high on this input causes a byte of data to be written into the Capture Buffer with each sample clock cycle. This signal may be asserted asynchronously as it is internally synchronized with the internal sample clock.                                                                                                                                                                                                                          |  |  |

| 82                                                | RCLK           | GND                | Read Clock (Input): LVCMOS - Free running clock that is used to read data from the Capture Buffer. The parallel data at the output port and the EF flag are asserted synchronous with this clock.                                                                                                                                                                                                                                                                                        |  |  |

| 81                                                | RESET          |                    | Reset (Input): LVCMOS - A logic high at this input resets all Capture Buffer control logic in the chip.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 79                                                | WENSYNC        |                    | Synchronized WEN (Output): LVCMOS - The control input WEN is synchronized on-chip with the internal Sample Clock and is provided at this output.                                                                                                                                                                                                                                                                                                                                         |  |  |

| 80                                                | OR             | V <sub>D</sub>     | Out Of Range (Output): LVCMOS - A logic high on this pin indicates that the differential input is out of the linear range. This signal is asserted if the input signal has gone out of range at any time during the data capture operation. This pin is cleared after the Capture Buffer is read or after asserting the RESET pin.                                                                                                                                                       |  |  |

| 115                                               | FF             | DGND               | Buffer Full Flag (Output): LVCMOS - This signal is asserted synchronous with the clock when the capture buffer is full. If the WEN input remains asserted, the next CLK will cause an overflow, whereby the pointer will wrap around and begin overwriting the old data if the Auto Stop Write (ASW) bit is set to 0b in the Capture Buffer Control register. This signal is deasserted when a read cycle is initiated or a RESET is issued because the data buffer is no longer "full". |  |  |

| 116                                               | EF             |                    | Buffer Empty Flag (Output): LVCMOS - This signal is asserted synchronous with the RCLK signal when the Capture Buffer is empty. It is deasserted when a write cycle is initiated and the data buffer is no longer "empty".                                                                                                                                                                                                                                                               |  |  |

| 2, 5, 8, 13,<br>16, 17, 20,<br>25, 28, 33,<br>128 | V <sub>A</sub> |                    | Analog power supply pins (Power) - Bypass these pins to ground.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 40, 51, 62,<br>73, 88, 99,<br>110, 121            | $V_{DR}$       |                    | Output Driver power supply pins (Power) - Bypass these pins to DR GND.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 1, 6, 9, 12,<br>21, 24, 27                        | GND            |                    | (Gnd) - Ground return for V <sub>A</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 42, 53, 64,<br>74, 87, 97,<br>108, 119            | DR GND         |                    | (Gnd) - Ground return for V <sub>DR</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

Copyright © 2006–2013, Texas Instruments Incorporated

|                                                                                                                                                                                                                        | Pin Functions |                    |                                                 |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------|-------------------------------------------------|--|--|--|

| Pin No.                                                                                                                                                                                                                | Symbol        | Equivalent Circuit | Description                                     |  |  |  |

| 29, 36, 37, 38, 39, 41, 43, 44, 47, 48, 49, 50, 52, 54, 55, 56, 57, 58, 59, 60, 61, 63, 76, 77, 78, 83, 84, 85, 98, 100, 101, 102, 103, 104, 105, 106, 107, 109, 111, 112, 113, 114, 117, 118, 120, 122, 123, 124, 125 | NC            |                    | No Connection Make no connection to these pins. |  |  |  |

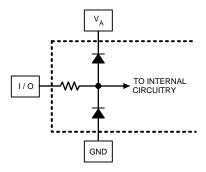

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### Absolute Maximum Ratings (1)(2)(3)

| ABOOTATO MAXIII AIII HATIII Y                                                |                  |                                    |

|------------------------------------------------------------------------------|------------------|------------------------------------|

| Analog Supply Voltage (V <sub>A</sub> )                                      |                  | 2.2V                               |

| $V_{DR}$                                                                     |                  | 0V to (V <sub>A</sub> + 300mV)     |

| Voltage on Any Input Pin (Except V <sub>IN</sub> +, V <sub>IN</sub> -)       |                  | -0.15V to (V <sub>A</sub> + 0.15V) |

| Voltage on V <sub>IN</sub> +, V <sub>IN</sub> -<br>(Maintaining Common Mode) |                  | -0.15V to 2.5V                     |

| Ground Difference<br>( GND - DR GND )                                        |                  | 0V to 100 mV                       |

| Input Current at Any Pin (4)                                                 |                  | ±25 mA                             |

| Package Input Current <sup>(4)</sup>                                         |                  | ±50 mA                             |

| Power Dissipation at T <sub>A</sub> ≤ 85°C                                   |                  | 2.3 W                              |

| ESD Susceptibility <sup>(5)</sup>                                            | Human Body Model | 2500V                              |

| ESD Susceptibility (7)                                                       | Machine Model    | 250V                               |

| Storage Temperature                                                          |                  | -65°C to +150°C                    |

- (1) All voltages are measured with respect to GND = DR GND = 0V, unless otherwise specified.

- (2) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. There is no specification of operation at the Absolute Maximum Ratings. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see Converter Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

- (3) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (4) When the input voltage at any pin exceeds the power supply limits (that is, less than GND or greater than V<sub>A</sub>), the current at that pin should be limited to 25 mA. The 50 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 25 mA to two. This limit is not placed upon the power and ground pins.

- (5) Human body model is 100 pF capacitor discharged through a 1.5 kΩ resistor. Machine model is 220 pF discharged through ZERO Ohms.

www.ti.com

### Operating Ratings<sup>(1)(2)</sup>

| -40°C ≤ T <sub>A</sub> ≤ +85°C                                     |

|--------------------------------------------------------------------|

| +1.8V to +2.0V                                                     |

| +1.8V to V <sub>A</sub>                                            |

| V <sub>CMO</sub> ±50mV                                             |

| 0V to 2.15V<br>(100% duty cycle)<br>0V to 2.5V<br>(10% duty cycle) |

| 0V                                                                 |

| 0V to V <sub>A</sub>                                               |

| 0.4V <sub>P-P</sub> to 2.0V <sub>P-P</sub>                         |

|                                                                    |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. There is no specification of operation at the Absolute Maximum Ratings. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see Converter Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

- All voltages are measured with respect to GND = DR GND = 0V, unless otherwise specified.

### Package Thermal Resistance (1)(2)

| Package                       | θ <sub>JA</sub> | θ <sub>JC</sub> (Top of Package) | θ <sub>J-PAD</sub> (Thermal Pad) |

|-------------------------------|-----------------|----------------------------------|----------------------------------|

| 128-Lead Exposed Pad<br>HLQFP | 26°C / W        | 10°C / W                         | 2.8°C / W                        |

- Soldering process must comply with Reflow Temperature Profile specifications. Refer to www.ti.com/packaging.

- (2) Reflow temperature profiles are different for lead-free and non-lead-free packages.

### Converter Electrical Characteristics (1)(2)

The following specifications apply after calibration for  $V_A = V_{DR} = 1.9V$ ,  $V_{IN}$  FSR (a.c. coupled) = differential 810mV<sub>P-P</sub>,  $C_L = 10$  pF, Differential a.c. coupled sine wave Input Clock,  $f_{CLK} = 1.5$  GHz at  $0.4V_{P-P}$  with 50% duty cycle, Duty Cycle Stabilizer enabled, RCLK = 100 MHz,  $V_{BG} =$  Floating, Non-Extended Control Mode, SDR Mode,  $R_{EXT} = 3300\Omega \pm 0.1\%$ , Analog Signal Source Impedance =  $100\Omega$  Differential, after calibration. **Boldface limits apply for T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>**. All other limits  $T_A = 25^{\circ}C$ , unless otherwise noted.

|                       | Parameter                                | Test Conditions                           | Typical <sup>(3)</sup> | Limits <sup>(3)</sup> | Units<br>(Limits) |  |  |

|-----------------------|------------------------------------------|-------------------------------------------|------------------------|-----------------------|-------------------|--|--|

| STATIC CO             | STATIC CONVERTER CHARACTERISTICS         |                                           |                        |                       |                   |  |  |

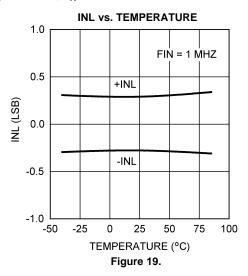

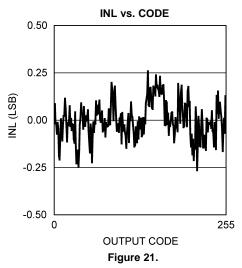

| INL                   | Integral Non-Linearity (Best fit)        | DC Coupled, 1MHz Sine Wave<br>Over Ranged | ±0.35                  | ±0.9                  | LSB (max)         |  |  |

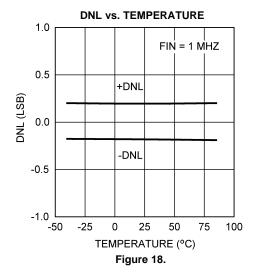

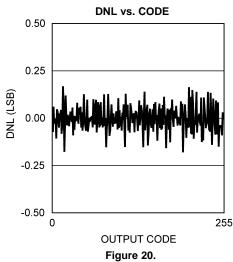

| DNL                   | Differential Non-Linearity               | DC Coupled, 1MHz Sine Wave<br>Over Ranged | ±0.20                  | ±0.6                  | LSB (max)         |  |  |

|                       | Resolution with No Missing Codes         |                                           |                        | 8                     | Bits              |  |  |

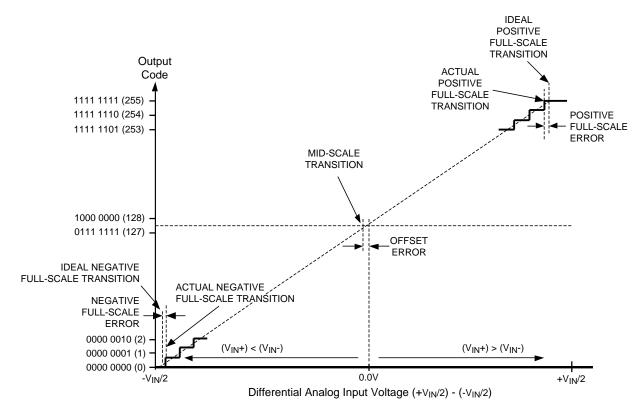

| $V_{OFF}$             | Offset Error                             |                                           | -0.10                  |                       | LSB               |  |  |

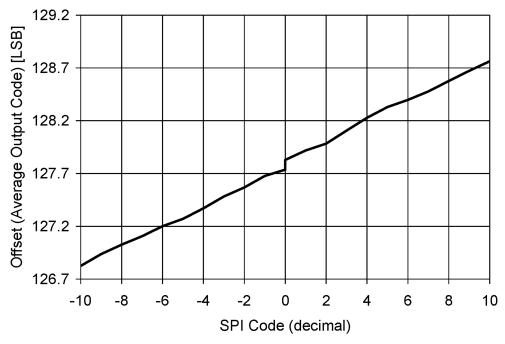

| V <sub>OFF</sub> _ADJ | Input Offset Adjustment Range            | Extended Control Mode                     | ±45                    |                       | mV                |  |  |

| PFSE                  | Positive Full-Scale Error <sup>(4)</sup> |                                           | -2.7                   | ±25                   | mV (max)          |  |  |

| NFSE                  | Negative Full-Scale Error <sup>(4)</sup> |                                           | -1.6                   | ±25                   | mV (max)          |  |  |

| FS_ADJ                | Full-Scale Adjustment Range              | Extended Control Mode                     | ±20                    | ±15                   | %FS               |  |  |

| DYNAMIC               | CONVERTER CHARACTERISTICS                |                                           |                        |                       | •                 |  |  |

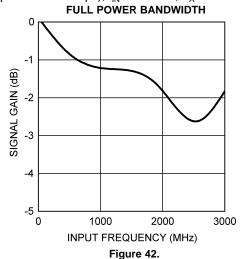

| FPBW                  | Full Power Bandwidth                     |                                           | 3                      |                       | GHz               |  |  |

- (1) The analog inputs are protected as shown below. Input voltage magnitudes beyond the Absolute Maximum Ratings may damage this device. See Figure 2

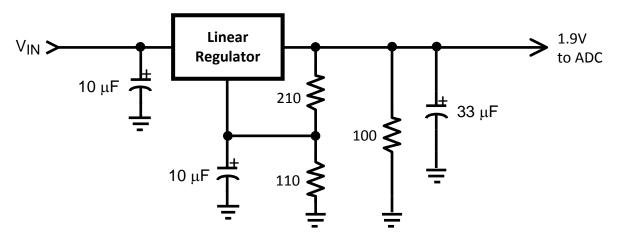

- (2) To ensure accuracy, it is required that V<sub>A</sub> and V<sub>DR</sub> be well bypassed. Each supply pin must be decoupled with separate bypass capacitors. Additionally, achieving rated performance requires that the backside exposed pad be well grounded.

- (3) Typical figures are at T<sub>A</sub> = 25°C, and represent most likely parametric norms. Test limits are ensured to AOQL (Average Outgoing Quality Level).

- (4) Calculation of Full-Scale Error for this device assumes that the actual reference voltage is exactly its nominal value. Full-Scale Error for this device, therefore, is a combination of Full-Scale Error and Reference Voltage Error. See Figure 3. For relationship between Gain Error and Full-Scale Error, see Specification Definitions for Gain Error.

Copyright © 2006–2013, Texas Instruments Incorporated

The following specifications apply after calibration for  $V_A = V_{DR} = 1.9V$ ,  $V_{IN}$  FSR (a.c. coupled) = differential 810mV<sub>P-P</sub>,  $C_L = 10$  pF, Differential a.c. coupled sine wave Input Clock,  $f_{CLK} = 1.5$  GHz at  $0.4V_{P-P}$  with 50% duty cycle, Duty Cycle Stabilizer enabled, RCLK = 100 MHz,  $V_{BG}$  = Floating, Non-Extended Control Mode, SDR Mode,  $R_{EXT} = 3300\Omega \pm 0.1\%$ , Analog Signal Source Impedance =  $100\Omega$  Differential, after calibration. **Boldface limits apply for T\_A = T\_{MIN} to T\_{MAX}**. All other limits  $T_A = 25^{\circ}\text{C}$ , unless otherwise noted.

|          | Parameter                             | Test Conditions                                                                                                                                                                                | Typical <sup>(3)</sup> | Limits <sup>(3)</sup> | Units<br>(Limits) |

|----------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|-------------------|

|          | Code Error Rate                       |                                                                                                                                                                                                | 10 <sup>-18</sup>      |                       | Errors/<br>Sample |

|          | Gain Flatness                         | 0.0 to -1.0 dBFS                                                                                                                                                                               | 50 to 950              |                       | MHz               |

|          |                                       | $f_{IN} = 373 \text{ MHz},$<br>$V_{IN} = \text{FSR} - 0.5 \text{ dB}$                                                                                                                          | 7.2                    | 6.7                   | Bits (min)        |

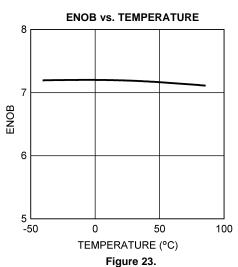

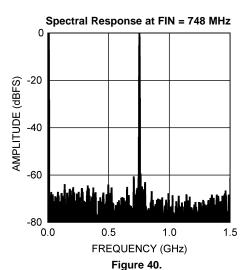

| ENOB     | Effective Number of Bits              | $f_{IN} = 748 \text{ MHz},$<br>$V_{IN} = FSR - 0.5 \text{ dB}$                                                                                                                                 | 7.1                    | 6.5                   | Bits (min)        |

|          |                                       | $f_{IN}$ = 1498 MHz,<br>$V_{IN}$ = FSR - 0.5 dB                                                                                                                                                | 6.4                    |                       | Bits              |

|          |                                       | $f_{IN} = 373 \text{ MHz},$<br>$V_{IN} = FSR - 0.5 \text{ dB}$                                                                                                                                 | 45.1                   | 41.8                  | dB (min)          |

| SINAD    | Signal-to-Noise Plus Distortion Ratio | $f_{\text{IN}} = 748 \text{ MHz},$ $V_{\text{IN}} = \text{FSR} - 0.5 \text{ dB}$                                                                                                               | 44.5                   | 44.5 <b>41.0</b>      | dB (min)          |

|          |                                       | $f_{IN} = 1498 \text{ MHz},$<br>$V_{IN} = \text{FSR} - 0.5 \text{ dB}$                                                                                                                         | 40.3                   |                       | dB                |

|          |                                       | $f_{IN} = 373 \text{ MHz},$<br>$V_{IN} = \text{FSR} - 0.5 \text{ dB}$                                                                                                                          | 45.3                   | 42.5                  | dB (min)          |

| SNR      | Signal-to-Noise Ratio                 | $f_{IN} = 748 \text{ MHz},$<br>$V_{IN} = \text{FSR} - 0.5 \text{ dB}$                                                                                                                          | 44.9                   | 42                    | dB (min)          |

|          |                                       | $f_{IN} = 1498 \text{ MHz},$ $V_{IN} = \text{FSR} - 0.5 \text{ dB}$                                                                                                                            | 42.4                   |                       | dB                |

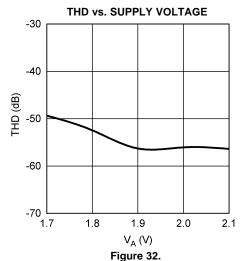

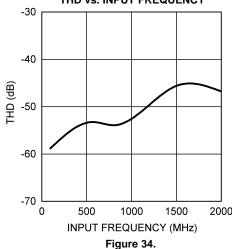

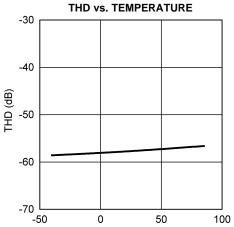

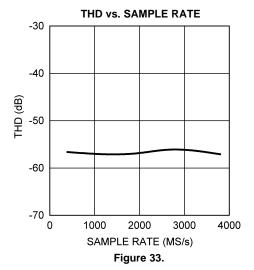

|          |                                       | $f_{IN} = 373 \text{ MHz},$<br>$V_{IN} = \text{FSR} - 0.5 \text{ dB}$                                                                                                                          | -57                    | -50                   | dB (max)          |

| THD      | Total Harmonic Distortion             | $f_{IN} = 748 \text{ MHz},$<br>$V_{IN} = FSR - 0.5 \text{ dB}$                                                                                                                                 | -54.8                  | -48                   | dB (max)          |

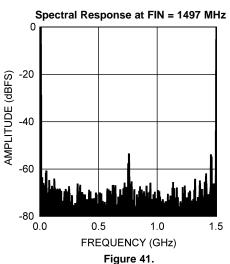

|          |                                       | $f_{IN}$ = 1498 MHz,<br>$V_{IN}$ = FSR - 0.5 dB                                                                                                                                                | -44.3                  |                       | dB                |

|          |                                       | $f_{IN} = 373 \text{ MHz},$<br>$V_{IN} = \text{FSR} - 0.5 \text{ dB}$                                                                                                                          | -68                    |                       | dB                |

| 2nd Harm | Second Harmonic Distortion            | $f_{IN} = 748 \text{ MHz},$<br>$V_{IN} = \text{FSR} - 0.5 \text{ dB}$                                                                                                                          | -65                    |                       | dB                |

|          |                                       | $f_{IN} = 1498 \text{ MHz},$ $V_{IN} = \text{FSR} - 0.5 \text{ dB}$                                                                                                                            | -45                    |                       | dB                |

|          |                                       | $f_{IN} = 373 \text{ MHz},$<br>$V_{IN} = \text{FSR} - 0.5 \text{ dB}$                                                                                                                          | -63                    |                       | dB                |

| 3rd Harm | Third Harmonic Distortion             | $f_{IN} = 748 \text{ MHz},$ $V_{IN} = \text{FSR} - 0.5 \text{ dB}$                                                                                                                             | -57                    |                       | dB                |

|          |                                       | $f_{IN} = 1498 \text{ MHz}, V_{IN} = FSR - 0.5 \text{ dB}$                                                                                                                                     | -51                    |                       | dB                |

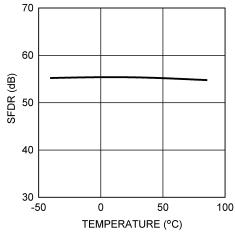

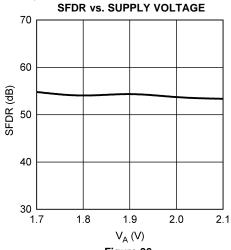

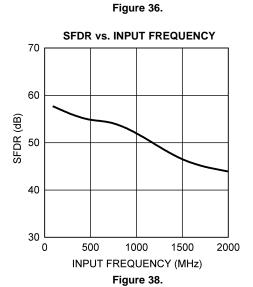

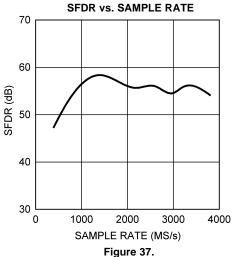

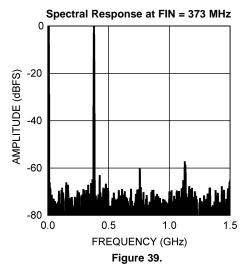

|          |                                       | $f_{IN} = 373 \text{ MHz},$<br>$V_{IN} = \text{FSR} - 0.5 \text{ dB}$                                                                                                                          | 55.4                   | 47                    | dB (min)          |

| SFDR     | Spurious-Free dynamic Range           | $f_{IN} = 748 \text{ MHz},$<br>$V_{IN} = \text{FSR} - 0.5 \text{ dB}$                                                                                                                          | 54.0                   | 46.5                  | dB (min)          |

|          |                                       | $f_{IN} = 1498 \text{ MHz},$<br>$V_{IN} = FSR - 0.5 \text{ dB}$                                                                                                                                | 45.3                   |                       | dB                |

| IMD      | Intermodulation Distortion            | $\begin{aligned} f_{\text{IN1}} &= 749.084 \text{ MHz}, \\ V_{\text{IN}} &= FSR - 7 \text{ dB} \\ f_{\text{IN2}} &= 756.042 \text{ MHz}, \\ V_{\text{IN}} &= FSR - 7 \text{ dB} \end{aligned}$ | -52                    |                       | dBFS              |

Submit Documentation Feedback

Copyright © 2006–2013, Texas Instruments Incorporated

The following specifications apply after calibration for  $V_A = V_{DR} = 1.9V$ ,  $V_{IN}$  FSR (a.c. coupled) = differential 810mV<sub>P-P</sub>,  $C_L = 10$  pF, Differential a.c. coupled sine wave Input Clock,  $f_{CLK} = 1.5$  GHz at  $0.4V_{P-P}$  with 50% duty cycle, Duty Cycle Stabilizer enabled, RCLK = 100 MHz,  $V_{BG} =$  Floating, Non-Extended Control Mode, SDR Mode,  $R_{EXT} = 3300\Omega \pm 0.1\%$ , Analog Signal Source Impedance =  $100\Omega$  Differential, after calibration. **Boldface limits apply for T\_A = T\_{MIN} to T\_{MAX}**. All other limits  $T_A = 25^{\circ}C$ , unless otherwise noted.

|                                       | Parameter                                                | Test Conditions                                      | Typical <sup>(3)</sup> | Limits <sup>(3)</sup>                          | Units<br>(Limits)                                |

|---------------------------------------|----------------------------------------------------------|------------------------------------------------------|------------------------|------------------------------------------------|--------------------------------------------------|

| ANALOG                                | INPUT AND REFERENCE CHARACTERISTICS                      |                                                      |                        |                                                |                                                  |

|                                       |                                                          | F0D :: 441                                           | 600                    | 550                                            | mV <sub>P-P</sub><br>(min)                       |

| V                                     | Full Scale Angles Differential Input Dance               | FSR pin 14 Low                                       | 800                    | 650                                            | mV <sub>P-P</sub><br>(max)                       |

| V <sub>IN</sub>                       | Full Scale Analog Differential Input Range               | FSR pin 14 High                                      | 810                    | 740                                            | mV <sub>P-P</sub><br>(min)                       |

|                                       |                                                          | PSK pili 14 riigii                                   | 810                    | 880                                            | mV <sub>P-P</sub><br>(max)                       |

| $V_{CMI}$                             | Analog Input Common Mode Voltage                         |                                                      | V <sub>CMO</sub>       | V <sub>CMO</sub> - 50<br>V <sub>CMO</sub> + 50 | mV (min)<br>mV (max)                             |

| ^                                     | Analog Input Capacitance <sup>(5)</sup>                  | Differential                                         | 0.8                    |                                                | pF                                               |

| C <sub>IN</sub>                       | Analog input Capacitance (**)                            | Each input pin to ground                             | 2.2                    |                                                | pF                                               |

| R <sub>IN</sub>                       | Differential Input Resistance                            |                                                      | 100                    | 95<br>103                                      | Ω (min)<br>Ω (max)                               |

| ANALOG                                | OUTPUT CHARACTERISTICS                                   | •                                                    | *                      | •                                              | •                                                |

| $V_{CMO}$                             | Common Mode Output Voltage                               | I <sub>CMO</sub> = ±100 μA                           | 1.26                   | 0.95<br>1.45                                   | V (min)<br>V (max)                               |

| V                                     | V input threshold to get DC Coupling mode                | V <sub>A</sub> = 1.8V                                | 0.60                   |                                                | V                                                |

| V <sub>CMO_LVL</sub>                  | V <sub>CMO</sub> input threshold to set DC Coupling mode | V <sub>A</sub> = 2.0V                                | 0.66                   |                                                | V                                                |

| TC V <sub>CMO</sub>                   | Common Mode Output Voltage Temperature Coefficient       | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$  | 118                    |                                                | ppm/°C                                           |

| C <sub>LOAD</sub><br>V <sub>CMO</sub> | Maximum V <sub>CMO</sub> load Capacitance                |                                                      |                        | 80                                             | pF                                               |

| $V_{BG}$                              | Bandgap Reference Output Voltage                         | I <sub>BG</sub> = ±100 μA                            | 1.26                   | 1.20<br>1.33                                   | V (min)<br>V (max)                               |

| TC V <sub>BG</sub>                    | Bandgap Reference Voltage Temperature Coefficient        | $T_A = -40$ °C to +85°C,<br>$I_{BG} = \pm 100 \mu A$ | 28                     |                                                | ppm/°C                                           |

| C <sub>LOAD</sub> V <sub>BG</sub>     | Maximum Bandgap Reference load Capacitance               |                                                      |                        | 80                                             | pF                                               |

| TEMPERA                               | TURE DIODE CHARACTERISTICS                               |                                                      |                        |                                                |                                                  |

| <b>A</b> \/                           | Temporatura Diada Valtaga                                | 192 μA vs. 12 μA,<br>Τ <sub>J</sub> = 25°C           | 71.23                  |                                                | mV                                               |

| $\Delta V_{BE}$                       | Temperature Diode Voltage                                | 192 μA vs. 12 μA,<br>Τ <sub>J</sub> = 85°C           | 85.54                  |                                                | mV                                               |

| LVDS INP                              | UT CHARACTERISTICS                                       |                                                      | ·                      |                                                |                                                  |

| .,                                    | Differential Clock Input Lovel                           | Sine Wave Clock                                      | 0.5                    | 0.4<br>0.7                                     | V <sub>P-P</sub> (min)<br>V <sub>P-P</sub> (max) |

| $V_{ID}$                              | Differential Clock Input Level                           | Square Wave Clock                                    | 0.5                    | 0.4<br>0.7                                     | V <sub>P-P</sub> (min)<br>V <sub>P-P</sub> (max) |

| I <sub>I</sub>                        | Input Current                                            | $V_{IN} = 0$ or $V_{IN} = V_A$                       | ±1                     |                                                | μΑ                                               |

| C                                     | Input Capacitance <sup>(5)</sup>                         | Differential                                         | 0.02                   |                                                | pF                                               |

| C <sub>IN</sub>                       | input Capacitance ·                                      | Each input to ground                                 | 1.5                    |                                                | pF                                               |

<sup>(5)</sup> The analog and clock input capacitances include packaging capacitance values of 0.7 pF differential and 1 pF each input pin to ground, which are isolated from the die capacitance by lead and bond wire inductances.

Product Folder Links: ADC08B3000

Incorporated Submit Documentation Feedback

The following specifications apply after calibration for  $V_A = V_{DR} = 1.9V$ ,  $V_{IN}$  FSR (a.c. coupled) = differential 810mV<sub>P-P</sub>,  $C_L = 10$  pF, Differential a.c. coupled sine wave Input Clock,  $f_{CLK} = 1.5$  GHz at  $0.4V_{P-P}$  with 50% duty cycle, Duty Cycle Stabilizer enabled, RCLK = 100 MHz,  $V_{BG} =$  Floating, Non-Extended Control Mode, SDR Mode,  $R_{EXT} = 3300\Omega \pm 0.1\%$ , Analog Signal Source Impedance =  $100\Omega$  Differential, after calibration. **Boldface limits apply for T\_A = T\_{MIN} to T\_{MAX}**. All other limits  $T_A = 25^{\circ}\text{C}$ , unless otherwise noted.

|                 | Parameter                         | Test Conditions                                                        | Typical <sup>(3)</sup> | Limits <sup>(3)</sup> | Units<br>(Limits) |

|-----------------|-----------------------------------|------------------------------------------------------------------------|------------------------|-----------------------|-------------------|

| LVCMO           | S INPUT CHARACTERISTICS           |                                                                        |                        |                       |                   |

|                 | Landa Historia Vallana            | ADCCLK_RST, PD, CAL                                                    |                        | 0.69 x V <sub>A</sub> | V (min)           |

| $V_{IH}$        | Logic High Input Voltage          | OutEdge, FSR, CalDly                                                   |                        | 0.79 x V <sub>A</sub> | V (min)           |

| V <sub>IL</sub> | Logic Low Input Voltage           | All LVCMOS Inputs                                                      |                        | 0.28 x V <sub>A</sub> | V (max)           |

| I <sub>IH</sub> | Logic High Input Current          | ADCCLK_RST, CAL, PD, CalDly                                            | 1                      |                       | μΑ                |

|                 |                                   | FSR/ECE                                                                | 30                     |                       | μΑ                |

| I <sub>IL</sub> | Logic Low Input Current           | ADCCLK_RST, CAL, PD,<br>CalDly                                         | 1                      |                       | μΑ                |

|                 |                                   | FSR/ECE                                                                | 30                     | 0.69 x V <sub>A</sub> | μΑ                |

| C <sub>IN</sub> | Input Capacitance <sup>(6)</sup>  | Each input to ground                                                   | 1.2                    |                       | pF                |

| LVCMO           | S OUTPUT CHARACTERISTICS          |                                                                        | ·                      | •                     |                   |

| $V_{OH}$        | CMOS High level output            | $I_{OH} = -400uA$                                                      | 1.65                   | 1.5                   | V (min)           |

| V <sub>OL</sub> | CMOS Low level output             | I <sub>OH</sub> = 400uA                                                | 0.15                   | 0.3                   | V (max)           |

| POWER           | SUPPLY CHARACTERISTICS            |                                                                        |                        |                       |                   |

|                 | Analog Congle Compat              | Full Power Capture Mode<br>WEN = High,<br>REN =PD = Low                | 723                    | 800                   | mA (max)          |

| I <sub>A</sub>  | Analog Supply Current             | Power Down Mode<br>WEN = Low,<br>REN = PD = High                       | 2.4                    | 800                   | mA                |

|                 |                                   | Full Power Capture Mode<br>WEN = High,<br>REN =PD = Low                | 135                    | 180                   | mA (max)          |

| I <sub>DR</sub> | Output Driver Supply Current      | Power Down Mode<br>WEN = Low,<br>REN = PD = High                       | 10.8                   |                       | mA                |

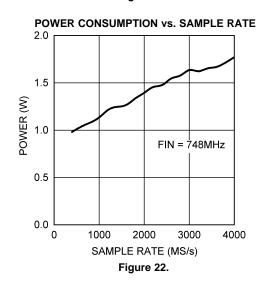

|                 | Barrer Construction               | Full Power Capture Mode<br>WEN = High,<br>REN =PD = Low                | 1.6                    | 1.9                   | W (max)           |

| $P_D$           | Power Consumption                 | Power Down Mode<br>WEN = Low,<br>REN = PD = High                       | 25                     |                       | mW                |

| PSRR1           | D.C. Power Supply Rejection Ratio | Change in Offset Error with change in V <sub>A</sub> from 1.8V to 2.0V | 70                     |                       | dB                |

| PSRR2           | A.C. Power Supply Rejection Ratio | 248 MHz, $100 \text{mV}_{P-P}$ riding on $V_A$                         | 50                     |                       | dB                |

<sup>6)</sup> The digital control pin capacitances are die capacitances only. Additional package capacitance of 1.6 pF each pin to ground are isolated from the die capacitances by lead and bond wire inductances.

The following specifications apply after calibration for  $V_A = V_{DR} = 1.9V$ ,  $V_{IN}$  FSR (a.c. coupled) = differential 810mV<sub>P-P</sub>,  $C_L = 10$  pF, Differential a.c. coupled sine wave Input Clock,  $f_{CLK} = 1.5$  GHz at  $0.4V_{P-P}$  with 50% duty cycle, Duty Cycle Stabilizer enabled, RCLK = 100 MHz,  $V_{BG}$  = Floating, Non-Extended Control Mode, SDR Mode,  $R_{EXT} = 3300\Omega \pm 0.1\%$ , Analog Signal Source Impedance =  $100\Omega$  Differential, after calibration. **Boldface limits apply for T\_A = T\_{MIN} to T\_{MAX}**. All other limits  $T_A = 25^{\circ}C$ , unless otherwise noted.

|                    | Parameter                                                                       | Test Conditions                                           | Typical <sup>(3)</sup> | Limits <sup>(3)</sup> | Units<br>(Limits)  |

|--------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------|-----------------------|--------------------|

| AC ELEC            | TRICAL CHARACTERISTICS - Sample Clock                                           |                                                           |                        |                       |                    |

| f <sub>CLK1</sub>  | Maximum Input Clock Frequency                                                   | Sample rate is 2x clock input                             |                        | 1.5                   | GHz (min)          |

| f <sub>CLK2</sub>  | Minimum Input Clock Frequency                                                   | Sample rate is 2x clock input                             | 500                    |                       | MHz                |

| t <sub>CYC</sub>   | Input Clock Duty Cycle  500MHz ≤ Input clock frequency ≤ 1.5 GHz <sup>(7)</sup> |                                                           | 50                     | 20<br>80              | % (min)<br>% (max) |

| t <sub>LC</sub>    | Input Clock Low Time                                                            | See <sup>(8)</sup>                                        | 333                    | 133                   | ps (min)           |

| t <sub>HC</sub>    | Input Clock High Time                                                           | See <sup>(8)</sup>                                        | 333                    | 133                   | ps (min)           |

| t <sub>AD</sub>    | Sample (Aperture) Delay  Input CLK transition to Acquisition of Data  1.4       |                                                           | 1.4                    |                       | ns                 |

| $t_{AJ}$           | Aperture Jitter                                                                 |                                                           | 0.55                   |                       | ps rms             |

| AC ELEC            | TRICAL CHARACTERISTICS - Capture Buffer Signa                                   | ls                                                        |                        |                       |                    |

| f <sub>RCLK</sub>  | Maximum Capture Buffer Read Clock Frequency                                     |                                                           | 200                    |                       | MHz                |

| t <sub>LHT</sub>   | Low to High Transition Time                                                     | 10% to 90%                                                | 250                    |                       | ps                 |

| $t_{HLT}$          | High to Low Transition Time                                                     | 10% to 90%                                                | 250                    |                       | ps                 |

| t <sub>DWS1</sub>  | Delay WENSYNC                                                                   | Delay after 3 Write Clock<br>Cycles                       | 7.0                    |                       | ns                 |

| t <sub>DWS2</sub>  | Delay WENSYNC                                                                   | Delay after FF assertion                                  | -1.3                   |                       | ns                 |

| t <sub>HWEN</sub>  | Minimum Hold Time WEN                                                           | Hold Time after WENSYNC deassertion                       | -5.0                   | 0                     | ns (min)           |

| T <sub>ASWEN</sub> | Minimum Assertion Delay WEN                                                     | RCLK cycle delay after deassertion of REN                 | 0                      | 1                     | RCLK<br>Cyc. (min) |

| 4                  | Dolov Full Flog                                                                 | Delay after REN assertion,<br>RCLK = 100 MHz              | 7.3                    |                       | ns                 |

| t <sub>DFF</sub>   | Delay Full Flag                                                                 | Delay after REN assertion,<br>RCLK = 200 MHz              | 5.0                    |                       | ns                 |

| t <sub>DEF1</sub>  | Delay Empty Flag                                                                | Delay after last DRDY pulse,<br>RCLK = 200 MHz            | 0                      |                       | ns                 |

| t <sub>DEF2</sub>  | Delay Empty Flag                                                                | Delay after RESET                                         | 2.0                    |                       | ns                 |

| t <sub>DEF3</sub>  | Delay Empty Flag                                                                | Delay after WENSYNC assertion                             | 9.5                    |                       | ns                 |

| t <sub>SREN</sub>  | Minimum Setup Time REN                                                          | Setup Time before rising edge of RCLK                     | 0.2                    | 0.3                   | ns (min)           |

| t <sub>HREN</sub>  | Minimum Hold Time REN                                                           | Hold Time after last DRDY pulse or positive edge of RESET | -5                     | 0                     | ns (min)           |

|                    | Dalan DOLK to DDDV                                                              | RCLK to DRDY Delay, RCLK =                                | 0.7                    | 1.8                   | ns (min)           |

| t <sub>DDRDY</sub> | Delay RCLK to DRDY                                                              | 100 MHz or 200 MHz                                        | 2.7                    | 4.0                   | ns (max)           |

| t <sub>SKEW</sub>  | Skew DRDY to Data                                                               | For SDR and DDR 0º modes.                                 | 0                      | ±200                  | ps (max)           |

| t <sub>so</sub>    | Setup Time Data Output                                                          | Data Output to DRDY<br>For DDR 90° mode                   | 5                      |                       | ns                 |

| t <sub>HO</sub>    | Hold Time Data Output                                                           | DRDY to Data Output<br>For DDR 90° mode                   | 5                      |                       | ns                 |

<sup>(7)</sup> This parameter is ensured by design and/or characterization and is not tested in production.

<sup>(8)</sup> This parameter is ensured by design and is not tested in production.

The following specifications apply after calibration for  $V_A = V_{DR} = 1.9V$ ,  $V_{IN}$  FSR (a.c. coupled) = differential 810mV<sub>P-P</sub>,  $C_L = 10$  pF, Differential a.c. coupled sine wave Input Clock,  $f_{CLK} = 1.5$  GHz at  $0.4V_{P-P}$  with 50% duty cycle, Duty Cycle Stabilizer enabled, RCLK = 100 MHz,  $V_{BG}$  = Floating, Non-Extended Control Mode, SDR Mode,  $R_{EXT} = 3300\Omega \pm 0.1\%$ , Analog Signal Source Impedance =  $100\Omega$  Differential, after calibration. **Boldface limits apply for T\_A = T\_{MIN} to T\_{MAX}**. All other limits  $T_A = 25^{\circ}\text{C}$ , unless otherwise noted.

|                     | Parameter                                          | Test Conditions                               | Typical <sup>(3)</sup> | Limits <sup>(3)</sup>  | Units<br>(Limits) |

|---------------------|----------------------------------------------------|-----------------------------------------------|------------------------|------------------------|-------------------|

| AC ELEC             | CTRICAL CHARACTERISTICS - Serial Interface         |                                               |                        | •                      |                   |

| f <sub>SCLK</sub>   | Serial Clock Frequency                             |                                               | 67                     |                        | MHz               |

| t <sub>SSU</sub>    | Data to Serial Clock Rising Setup Time             |                                               | 2.5                    |                        | ns (min)          |

| t <sub>SH</sub>     | Data to Serial Clock Rising Hold Time              |                                               | 1                      |                        | ns (min)          |

| t <sub>SCS</sub>    | CS to Serial Clock Rising Setup Time               |                                               | 2.5                    |                        | ns                |

| t <sub>HCS</sub>    | CS to Serial Clock Falling Hold Time               |                                               | 1.5                    |                        | ns                |

|                     | Serial Clock Low Time                              |                                               |                        | 6                      | ns (min)          |

|                     | Serial Clock High Time                             |                                               |                        | 6                      | ns (min)          |

| AC ELEC             | CTRICAL CHARACTERISTICS - General Signals          |                                               |                        |                        |                   |

| t <sub>SR</sub>     | Setup Time ADCCLK_RST±                             | Differential ADCCLK_RST                       | 90                     |                        | ps                |

| t <sub>HR</sub>     | Hold Time ADCCLK_RST±                              | Differential ADCCLK_RST                       | 30                     |                        | ps                |

| t <sub>PWR</sub>    | Pulse Width ADCCLK_RST±                            | See <sup>(9)</sup>                            |                        | 4                      | CLK± Cyc. (min)   |

| t <sub>WU</sub>     | PD low to Rated Accuracy Conversion (Wake-Up Time) |                                               | 1                      |                        | μs                |

| t <sub>CAL</sub>    | Calibration Cycle Time                             |                                               | 1.4 x 10 <sup>5</sup>  |                        | CLK± Cyc.         |

| t <sub>CAL_L</sub>  | CAL Pin Low Time                                   | See <sup>(9)</sup> and Figure 6               |                        | 80                     | CLK± Cyc. (min)   |

| t <sub>CAL_H</sub>  | CAL Pin High Time                                  | See <sup>(9)</sup> and Figure 6               |                        | 80                     | CLK± Cyc. (min)   |

|                     | Calibration delay CalDly = Low                     | See <sup>(9)</sup> , Calibration and Figure 6 |                        | <b>2</b> <sup>25</sup> | CLK± Cyc. (max)   |

| t <sub>CalDly</sub> | Calibration delay CalDly = High                    | See <sup>(9)</sup> , Calibration and Figure 6 |                        | 2 <sup>31</sup>        | CLK± Cyc. (max)   |

(9) This parameter is ensured by design and is not tested in production.

Figure 2.

#### SPECIFICATION DEFINITIONS

**APERTURE (SAMPLING) DELAY** is the amount of delay, measured from the sample edge of the Clock input, after which the signal present at the input pin is sampled inside the device.

**APERTURE JITTER**  $(t_{AJ})$  is the variation in aperture delay from sample to sample. Aperture jitter shows up as input noise.

CLOCK DUTY CYCLE is the ratio of the clock wave form logic high to the total time of one clock period.

**CODE ERROR RATE (C.E.R.)** is the probability of error and is defined as the probable number of errors per unit of time divided by the number of words seen in that amount of time. A Code Error Rate of 10<sup>-18</sup> corresponds to a statistical error in one conversion about every four (4) years.

**COMMON MODE VOLTAGE** is the d.c. potential that is common to both pins of a differential pair. For a voltage to be a common mode one, the signal departure from this d.c. common mode voltage at any given instant must be the same for each of the pins, but in opposite directions from each other.

**DIFFERENTIAL NON-LINEARITY (DNL)** is the maximum deviation from the ideal step size of 1 LSB. Measured at 3 Gsps with a sine wave input.

**EFFECTIVE NUMBER OF BITS (ENOB, or EFFECTIVE BITS)** is another method of specifying Signal-to-Noise and Distortion Ratio, or SINAD. ENOB is defined as (SINAD - 1.76) / 6.02 and says that the converter is equivalent to a perfect ADC of this (ENOB) number of bits.

**FULL POWER BANDWIDTH (FPBW)** is a measure of the frequency at which the reconstructed output fundamental drops 3 dB below its low frequency value for a full scale input.