Sample &

Buy

LMH6642, LMH6643, LMH6644

SNOS966Q - MAY 2001 - REVISED SEPTEMBER 2014

## LMH664x Low Power, 130 MHz, 75 mA Rail-to-Rail Output Amplifiers

Technical

Documents

## 1 Features

(V<sub>S</sub> =  $\pm 5$  V, T<sub>A</sub> =  $25^{\circ}$ C, R<sub>L</sub> = 2 k $\Omega$ , A<sub>V</sub> = +1. Typical Values Unless Specified).

- $-3 \text{ dB BW} (A_V = +1) 130 \text{ MHz}$

- Supply Voltage Range 2.7 V to 12.8 V

- Slew Rate,  $(A_V = -1) 130V/\mu s^{(1)}$

- Supply Current (no load) 2.7 mA/amp

- Output Short Circuit Current +115 mA to 145 mA

- Linear Output Current ±75 mA

- Input Common Mode Volt. 0.5 V Beyond V<sup>-</sup>, 1 V from V<sup>+</sup>

- Output Voltage Swing 40 mV from Rails

- Input Voltage Noise (100 kHz) 17nV/√Hz

- Input Current Noise (100 kHz) 0.9pA/VHz

- THD (5MHz,  $R_L = 2k\Omega$ ,  $V_O = 2V_{PP}$ ,  $A_V = +2$ ) -62 dBc

- Settling Time 68 ns

- Fully Characterized for 3 V, 5 V, and ±5 V

- Overdrive Recovery 100 ns

- Output Short Circuit Protected<sup>(2)</sup>

- No Output Phase Reversal with CMVR Exceeded

<sup>(1)</sup> Slew rate is the average of the rising and falling slew rates

$^{(2)}$  Output short circuit duration is infinite for V<sub>S</sub> < 6 V at room temperature and below. For V<sub>S</sub> > 6 V, allowable short circuit duration is 1.5 ms.

#### Applications 2

- Active Filters

- CD/DVD ROM

- ADC Buffer Amp

- Portable Video

- **Current Sense Buffer**

## 3 Description

Tools &

Software

The LMH664X family true single supply voltage feedback amplifiers offer high speed (130 MHz), low distortion (-62 dBc), and exceptionally high output current (approximately 75 mA) at low cost and with reduced power consumption when compared against existing devices with similar performance.

Support &

Community

Input common mode voltage range extends to 0.5 V below V<sup>-</sup> and 1 V from V<sup>+</sup>. Output voltage range extends to within 40 mV of either supply rail, allowing wide dynamic range especially desirable in low voltage applications. The output stage is capable of approximately 75 mA in order to drive heavy loads. Fast output Slew Rate (130 V/µs) ensures large peak-to-peak output swings can be maintained even at higher speeds, resulting in exceptional full power bandwidth of 40 MHz with a 3 V supply. These characteristics, along with low cost, are ideal features a multitude of industrial and commercial for applications.

| Device miormation * |            |                   |  |  |  |  |  |

|---------------------|------------|-------------------|--|--|--|--|--|

| PART NUMBER         | PACKAGE    | BODY SIZE (NOM)   |  |  |  |  |  |

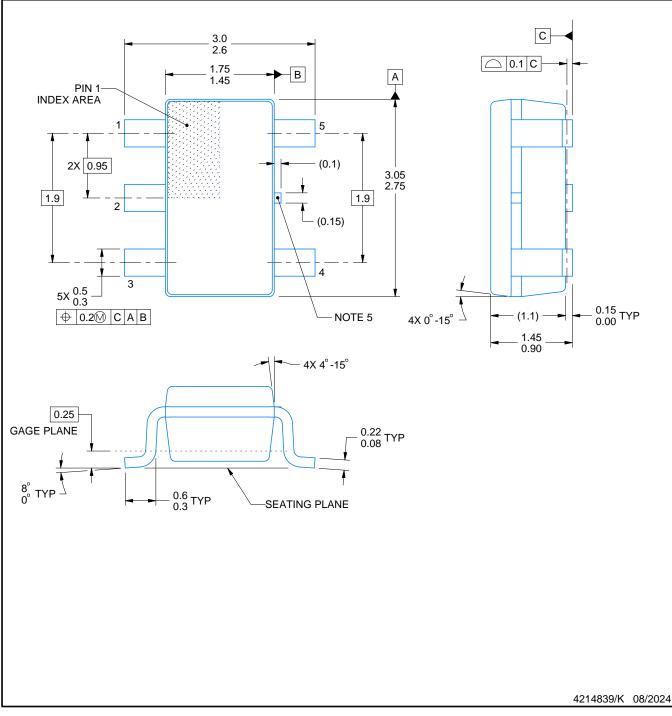

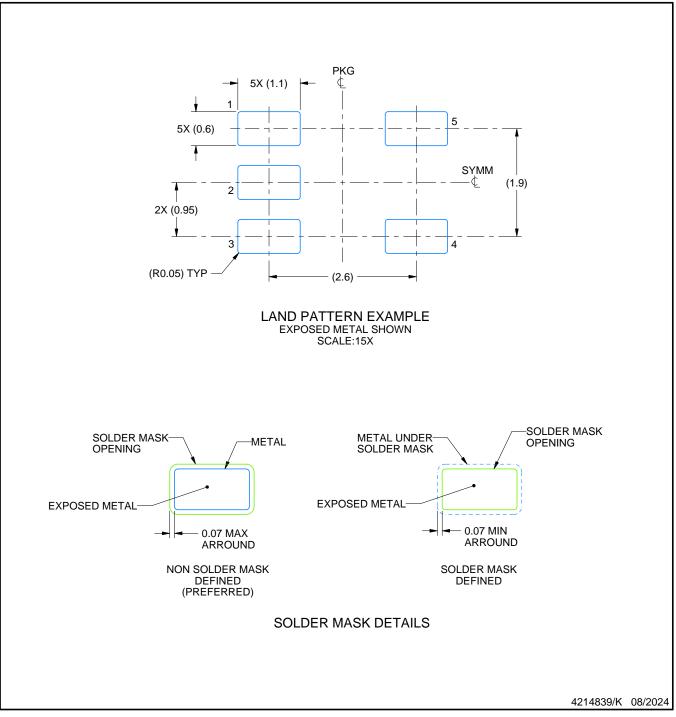

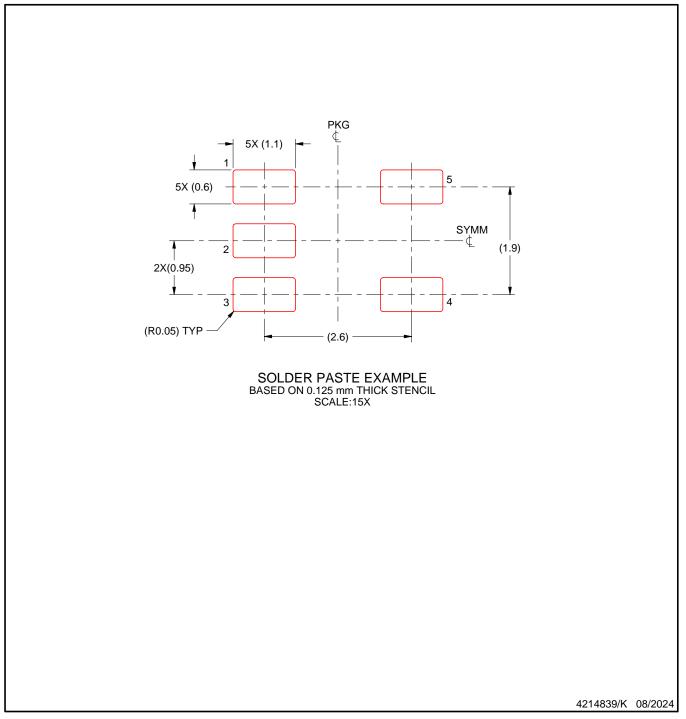

| LMH6642             | SOT-23 (5) | 2.90 mm × 1.60 mm |  |  |  |  |  |

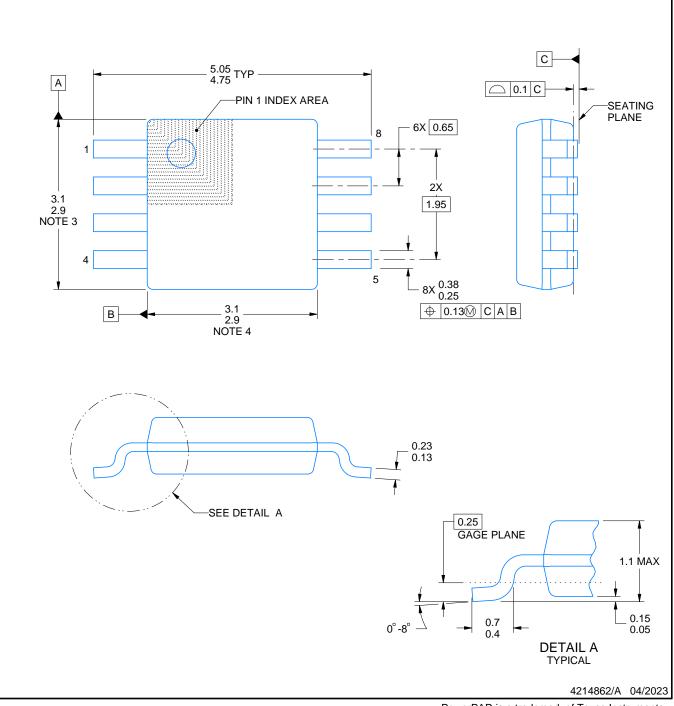

|                     | SOIC (8)   | 4.90 mm × 3.91 mm |  |  |  |  |  |

| 1 141 100 40        | SOIC (8)   | 2.00              |  |  |  |  |  |

| LMH6643             | VSSOP (8)  | 3.00 mm × 3.00 mm |  |  |  |  |  |

| LMH6644             | SOIC (14)  | 8.64 mm × 3.91 mm |  |  |  |  |  |

|                     | TSSOP (14) | 5.00 mm × 4.40 mm |  |  |  |  |  |

#### Device Information<sup>(1)</sup>

(1) For all available packages, see the orderable addendum at the end of the datasheet.

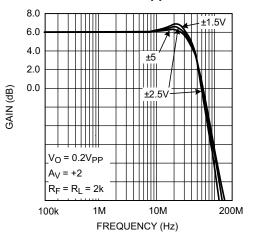

#### **Closed Loop Gain vs. Frequency** for Various Supplies

Page

## **Table of Contents**

| 1 | Feat | tures 1                                |

|---|------|----------------------------------------|

| 2 | Арр  | lications 1                            |

| 3 | Des  | cription1                              |

| 4 | Rev  | ision History 2                        |

| 5 | Des  | cription (continued) 3                 |

| 6 | Pin  | Configuration and Functions 4          |

| 7 | Spe  | cifications5                           |

|   | 7.1  | Absolute Maximum Ratings 5             |

|   | 7.2  | Handling Ratings5                      |

|   | 7.3  | Recommended Operating Conditions 5     |

|   | 7.4  | Thermal Information 5                  |

|   | 7.5  | 3V Electrical Characteristics 6        |

|   | 7.6  | 5V Electrical Characteristics 8        |

|   | 7.7  | ±5V Electrical Characteristics 10      |

|   | 7.8  | Typical Performance Characteristics 12 |

| 8 | Deta | ailed Description                      |

|   | 8.1  | Overview 21                            |

|   |      |                                        |

| 8.3       Feature Description       2         8.4       Device Functional Modes       2         9       Application and Implementation       2         9.1       Application Information       2         9.2       Typical Application       2         10       Power Supply Recommendations       2         11       Layout       2         11.1       Layout Guidelines       2         11.2       Layout Example       2         12       Device and Documentation Support       2         12.1       Related Links       2         12.2       Trademarks       2         12.3       Electrostatic Discharge Caution       2         12.4       Glossary       2         13       Mechanical, Packaging, and Orderable Information       2 |    | 8.2  | Functional Block Diagram        | <mark>21</mark> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|---------------------------------|-----------------|

| 9       Application and Implementation       2         9.1       Application Information       2         9.2       Typical Application       2         10       Power Supply Recommendations       2         11       Layout       2         11.1       Layout Guidelines       2         11.2       Layout Example       2         12       Device and Documentation Support       2         12.1       Related Links       2         12.2       Trademarks       2         12.3       Electrostatic Discharge Caution       2         12.4       Glossary       2         13       Mechanical, Packaging, and Orderable                                                                                                                     |    | 8.3  | Feature Description             | 21              |

| 9.1       Application Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | 8.4  | Device Functional Modes         | 21              |

| 9.2 Typical Application       2         10 Power Supply Recommendations       2         11 Layout       2         11.1 Layout Guidelines       2         11.2 Layout Example       2         12 Device and Documentation Support       2         12.1 Related Links       2         12.2 Trademarks       2         12.3 Electrostatic Discharge Caution       2         12.4 Glossary       2         13 Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                                                                                | 9  | App  | lication and Implementation     | 22              |

| 10 Power Supply Recommendations       2         11 Layout       2         11.1 Layout Guidelines       2         11.2 Layout Example       2         11.2 Layout Example       2         12 Device and Documentation Support       2         12.1 Related Links       2         12.2 Trademarks       2         12.3 Electrostatic Discharge Caution       2         12.4 Glossary       2         13 Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                                                                                    |    | 9.1  | Application Information         | 22              |

| 11       Layout       2         11.1       Layout Guidelines       2         11.2       Layout Example       2         12       Device and Documentation Support       2         12.1       Related Links       2         12.2       Trademarks       2         12.3       Electrostatic Discharge Caution       2         12.4       Glossary       2         13       Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                                                                                                                  |    | 9.2  | Typical Application             | 22              |

| 11.1       Layout Guidelines       2         11.2       Layout Example       2         12       Device and Documentation Support       2         12.1       Related Links       2         12.2       Trademarks       2         12.3       Electrostatic Discharge Caution       2         12.4       Glossary       2         13       Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                                                                                                                                                  | 10 | Pow  | er Supply Recommendations       | 24              |

| 11.2       Layout Example       2         12       Device and Documentation Support       2         12.1       Related Links       2         12.2       Trademarks       2         12.3       Electrostatic Discharge Caution       2         12.4       Glossary       2         13       Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                                                                                                                                                                                               | 11 | Lay  | out                             | 25              |

| 12 Device and Documentation Support       2         12.1 Related Links       2         12.2 Trademarks       2         12.3 Electrostatic Discharge Caution       2         12.4 Glossary       2         13 Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | 11.1 | Layout Guidelines               | 25              |

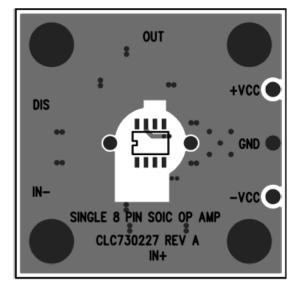

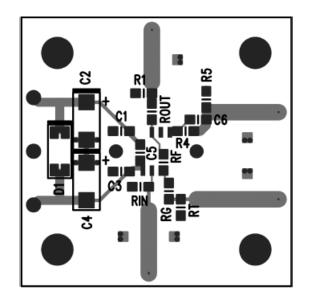

| 12.1       Related Links       2         12.2       Trademarks       2         12.3       Electrostatic Discharge Caution       2         12.4       Glossary       2         13       Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 11.2 | Layout Example                  | 25              |

| 12.2       Trademarks       2         12.3       Electrostatic Discharge Caution       2         12.4       Glossary       2         13       Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12 | Dev  | ice and Documentation Support   | 26              |

| <ul> <li>12.3 Electrostatic Discharge Caution</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    | 12.1 | Related Links                   | 26              |

| 12.4 Glossary 2<br>13 Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | 12.2 | Trademarks                      | 26              |

| 13 Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    | 12.3 | Electrostatic Discharge Caution | <mark>26</mark> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    | 12.4 | Glossary                        | 26              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13 |      |                                 | 26              |

## **4** Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Ch | anges from Revision P (March 2013) to Revision Q P                                                                                                                                                                           | age |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| •  | Added, revised, or updated the following sections: Device Information Table, Application and Implementation; Power Supply Recommendations; Device and Documentation Support; Mechanical, Packaging, and Ordering Information | 1   |

| •  | Changed "Junction Temperature Range" to "Operating Temperature Range"                                                                                                                                                        | 5   |

| •  | Deleted T <sub>J</sub> = 25°C for Electrical Characteristics tables.                                                                                                                                                         | 6   |

| •  | Changed from "R <sub>L</sub> " to "Rf"                                                                                                                                                                                       | 6   |

|    | Deleted T <sub>J</sub> = 25°C for Typical Performance Characteristics                                                                                                                                                        |     |

### Changes from Revision O (March 2013) to Revision P

| • | Changed layout of National Data Sheet to TI format |

|---|----------------------------------------------------|

|---|----------------------------------------------------|

## **5** Description (continued)

Careful attention has been paid to ensure device stability under all operating voltages and modes. The result is a very well behaved frequency response characteristic (0.1dB gain flatness up the 12 MHz under 150  $\Omega$  load and A<sub>V</sub> = +2) with minimal peaking (typically 2dB maximum) for any gain setting and under both heavy and light loads. This along with fast settling time (68ns) and low distortion allows the device to operate well in an ADC buffer as well as high frequency filter applications.

This device family offers professional quality video performance with low DG (0.01%) and DP (0.01°) characteristics. Differential Gain and Differential Phase characteristics are also well maintained under heavy loads (150  $\Omega$ ) and throughout the output voltage range. The LMH664X family is offered in single (LMH6642), dual (LMH6643), and quad (LMH6644) options.

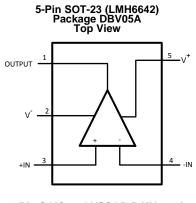

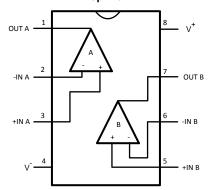

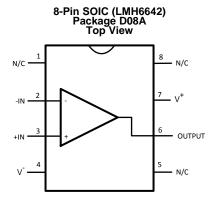

## 6 Pin Configuration and Functions

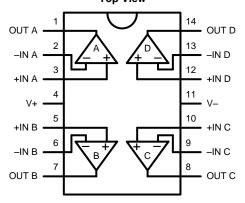

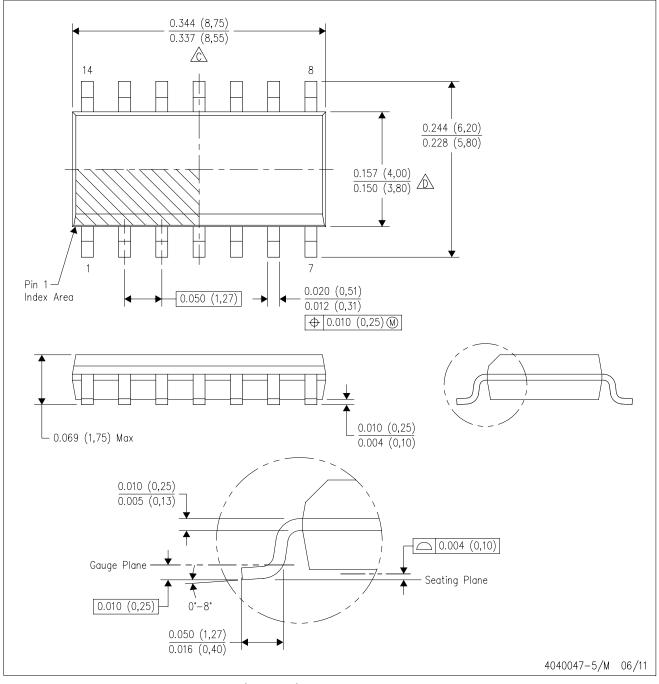

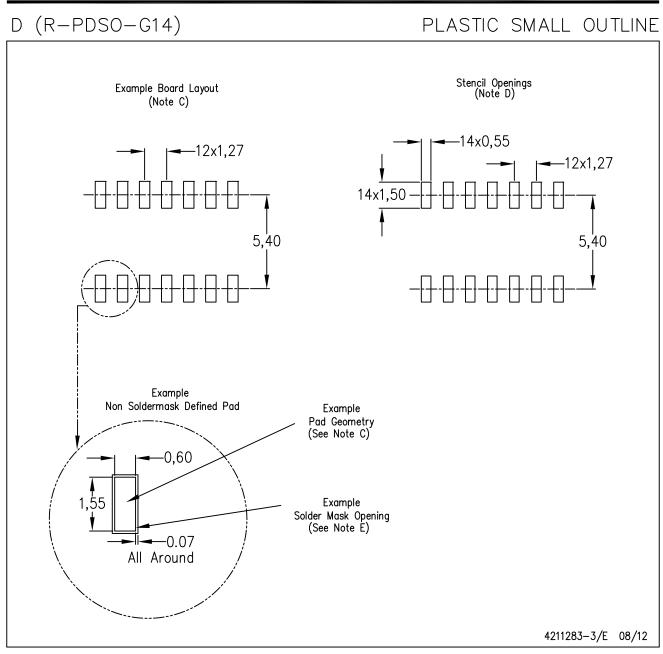

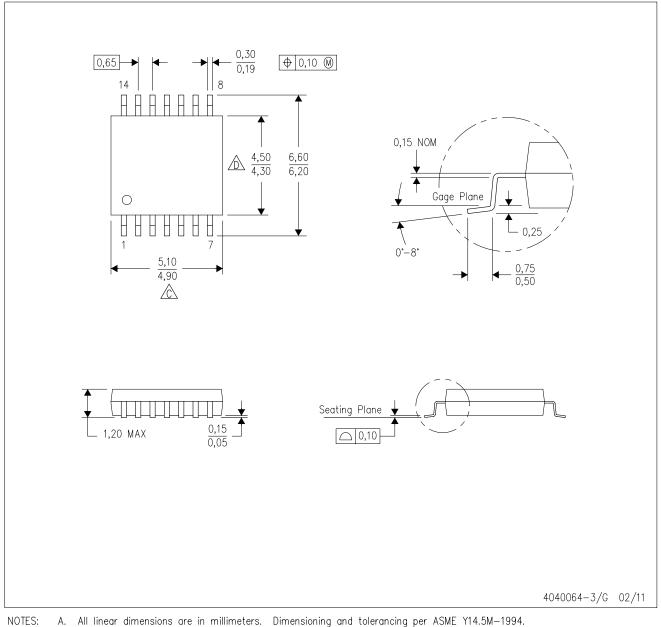

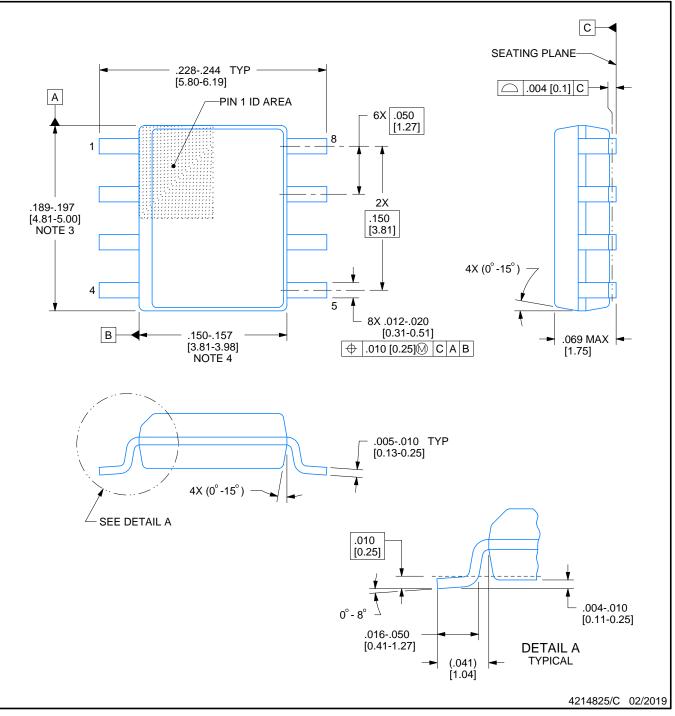

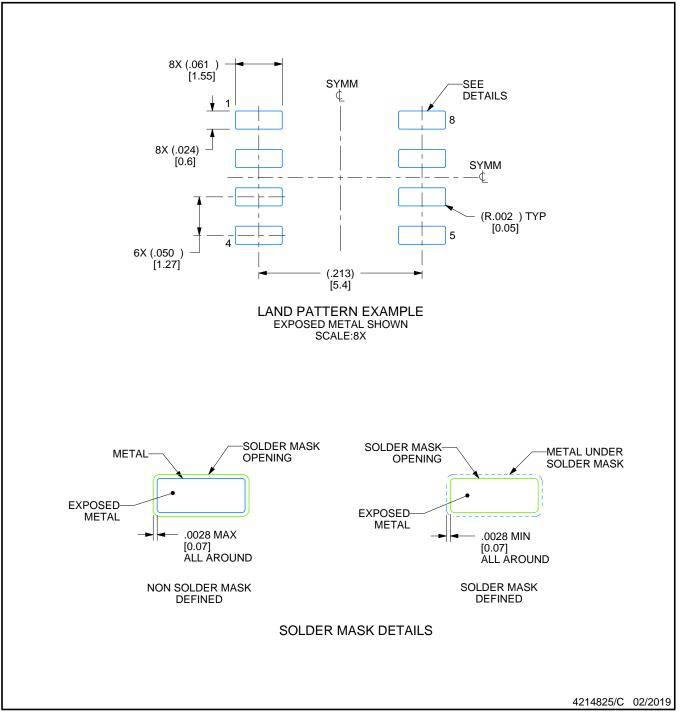

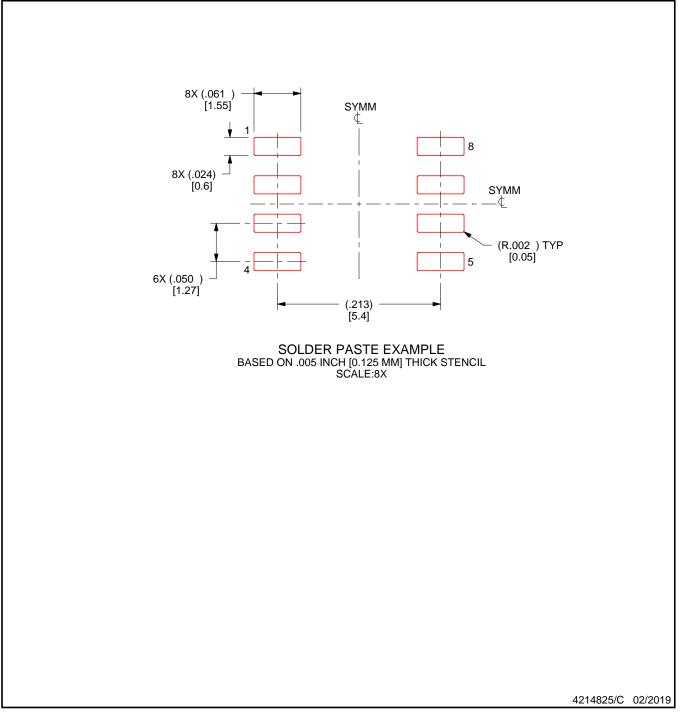

14-Pin SOIC and 14-Pin TSSOP (LMH6644) Package D14A, PW14A Top View

#### Pin Functions

| PIN            |        |       |         |                   |     |                         |

|----------------|--------|-------|---------|-------------------|-----|-------------------------|

|                | LMH    | 6642  | LMH6643 | LMH6644           | I/O | DESCRIPTION             |

| NAME           | DBV05A | D08A  | DGK08A  | D14A and<br>PW14A |     |                         |

| -IN            | 4      | 2     |         |                   | I   | Inverting Input         |

| +IN            | 3      | 3     |         |                   | I   | Non-inverting Input     |

| -IN A          |        |       | 2       | 2                 | I   | ChA Inverting Input     |

| +IN A          |        |       | 3       | 3                 | I   | ChA Non-inverting Input |

| -IN B          |        |       | 6       | 6                 | I   | ChB Inverting Input     |

| +IN B          |        |       | 5       | 5                 | I   | ChB Non-inverting Input |

| -IN C          |        |       |         | 9                 | I   | ChC Inverting Input     |

| +IN C          |        |       |         | 10                | I   | ChC Non-inverting Input |

| -IN D          |        |       |         | 13                | I   | ChD Inverting Input     |

| +IN D          |        |       |         | 12                | I   | ChD Non-inverting Input |

| N/C            |        | 1,5,8 |         |                   |     | No connection           |

| OUT A          |        |       | 1       | 1                 | 0   | ChA Output              |

| OUT B          |        |       | 7       | 7                 | 0   | ChB Output              |

| OUT C          |        |       |         | 8                 | 0   | ChC Output              |

| OUT D          |        |       |         | 14                | 0   | ChD Output              |

| OUTPUT         | 1      | 6     |         |                   | 0   | Output                  |

| V-             | 2      | 4     | 4       | 11                | I   | Negative Supply         |

| V <sup>+</sup> | 5      | 7     | 8       | 4                 | I   | Positive Supply         |

4

## 7 Specifications

## 7.1 Absolute Maximum Ratings<sup>(1)(2)</sup>

over operating free-air temperature range (unless otherwise noted)

|                                                   |                                        | MIN MAX                                                                                                                                                        | UNIT |

|---------------------------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| V <sub>IN</sub> Differential                      |                                        | ±2.5                                                                                                                                                           | V    |

| Output Short Circuit Duration                     |                                        | See $^{(3)}$ and $^{(4)}$                                                                                                                                      |      |

| Supply Voltage (V <sup>+</sup> - V <sup>-</sup> ) |                                        | 13.5                                                                                                                                                           | V    |

| Voltage at Input/Output pins                      |                                        |                                                                                                                                                                | V    |

| Input Current                                     |                                        | ±10                                                                                                                                                            | mA   |

| Junction Temperature <sup>(5)</sup>               |                                        | +150                                                                                                                                                           | °C   |

| Coldoring Information                             | Infrared or Convection Reflow (20 sec) | V <sup>+</sup> +0.8<br>V <sup>−</sup> -0.8         V           ±10         mA           +150         °C           ction Reflow (20 sec)         235         °C | °C   |

| Soldering Information                             | Wave Soldering Lead Temp.(10 sec)      | 260                                                                                                                                                            | °C   |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications and the test conditions, see the Electrical Characteristics.

(2) If Military/Aerospace specified devices are required, please contact the TI Sales Office/Distributors for availability and specifications.

(3) Applies to both single-supply and split-supply operation. Continuous short circuit operation at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of 150°C.

(4) Output short circuit duration is infinite for  $V_S < 6V$  at room temperature and below. For  $V_S > 6V$ , allowable short circuit duration is 1.5ms.

(5) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $R_{\theta JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A)/R_{\theta JA}$ . All numbers apply for packages soldered directly onto a PC board.

## 7.2 Handling Ratings

|                    |                                           |                                                                                          | MIN | MAX  | UNIT |

|--------------------|-------------------------------------------|------------------------------------------------------------------------------------------|-----|------|------|

| T <sub>stg</sub>   | stg Storage temperature range             |                                                                                          |     | +150 | °C   |

|                    |                                           | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(2)</sup>              |     | 2000 |      |

| V <sub>(ESD)</sub> | Electrostatic<br>discharge <sup>(1)</sup> | Machine model (MM) <sup>(3)</sup>                                                        |     | 200  | V    |

| V <sub>(ESD)</sub> |                                           | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(4)</sup> |     | 1000 |      |

(1) Human body model, 1.5 k $\Omega$  in series with 100 pF. Machine Model, 0  $\Omega$  in series with 200 pF.

(2) JEDEC document JEP155 states that 2000-V HBM allows safe manufacturing with a standard ESD control process.

(3) JEDEC document JEP157 states that 200-V MM allows safe manufacturing with a standard ESD control process.

(4) JEDEC document JEP157 states that 1000-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                                            | MIN | MAX  | UNIT |  |

|--------------------------------------------|-----|------|------|--|

| Supply Voltage $(V^+ - V^-)$               | 2.7 | 12.8 | V    |  |

| Operating Temperature Range <sup>(2)</sup> | -40 | +85  | °C   |  |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications and the test conditions, see the Electrical Characteristics.

(2) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $R_{\theta JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A)/R_{\theta JA}$ . All numbers apply for packages soldered directly onto a PC board.

### 7.4 Thermal Information

|                |                                                       | LMH    | 6642   | LMH6643 | LMH     | 6644    |      |

|----------------|-------------------------------------------------------|--------|--------|---------|---------|---------|------|

|                | THERMAL METRIC <sup>(1)</sup>                         | DBV05A | D08A   | DGK08A  | D14A    | PW14A   | UNIT |

|                |                                                       | 5 PINS | 8 PINS | 8 PINS  | 14 PINS | 14 PINS |      |

| $R_{\thetaJA}$ | Junction-to-ambient Thermal Resistance <sup>(2)</sup> | 265    | 190    | 235     | 145     | 155     | °C/W |

For more information about traditional and new thermal metrics, see the *IC Package Thermal Metrics* application report, SPRA953.

The maximum power dissipation is a function of T<sub>J(MAX)</sub>, R<sub>θJA</sub>, and T<sub>A</sub>. The maximum allowable power dissipation at any ambient temperature is P<sub>D</sub> = (T<sub>J(MAX)</sub> - T<sub>A</sub>)/ R<sub>θJA</sub>. All numbers apply for packages soldered directly onto a PC board.

### LMH6642, LMH6643, LMH6644

SNOS966Q - MAY 2001 - REVISED SEPTEMBER 2014

www.ti.com

#### 7.5 **3V Electrical Characteristics**

Unless otherwise specified, all limits ensured for V<sup>+</sup> = 3V, V<sup>-</sup> = 0V, V<sub>CM</sub> = V<sub>0</sub> = V<sup>+</sup>/2, V<sub>ID</sub> (input differential voltage) as noted (where applicable) and  $R_1 = 2k\Omega$  to V<sup>+</sup>/2.

|                    | PARAMETER                       | TEST CONDITIONS                                                                       |     | AT<br>MPERATU<br>EXTREME | _     | V <sub>CM</sub> =  | 3V, V <sup>-</sup> =<br>V <sub>O</sub> = V <sup>+</sup> /2<br>2 kΩ to \ | 2, V <sub>ID</sub> | UNIT   |

|--------------------|---------------------------------|---------------------------------------------------------------------------------------|-----|--------------------------|-------|--------------------|-------------------------------------------------------------------------|--------------------|--------|

|                    |                                 |                                                                                       | MIN | TYP                      | MAX   | MIN <sup>(1)</sup> | TYP <sup>(2)</sup>                                                      | MAX <sup>(1)</sup> |        |

| BW                 | -3dB BW                         | $A_V = +1, V_{OUT} = 200 mV_{PP}$                                                     |     |                          |       | 80                 | 115                                                                     |                    | MHz    |

|                    |                                 | $A_V = +2, -1, V_{OUT} = 200 mV_{PP}$                                                 |     |                          |       |                    | 46                                                                      |                    |        |

| $BW_{0.1dB}$       | 0.1dB Gain<br>Flatness          | $A_V = +2$ , $R_L = 150\Omega$ to V+/2,<br>Rf = 402 $\Omega$ , $V_{OUT} = 200mV_{PP}$ |     |                          |       |                    | 19                                                                      |                    | MHz    |

| PBW                | Full Power<br>Bandwidth         | $A_V = +1$ , $-1dB$ , $V_{OUT} = 1V_{PP}$                                             |     |                          |       |                    | 40                                                                      |                    | MHz    |

| e <sub>n</sub>     | Input-Referred                  | f = 100kHz                                                                            |     |                          |       |                    | 17                                                                      |                    | nV/√Hz |

|                    | Voltage Noise                   | f = 1kHz                                                                              |     |                          |       |                    | 48                                                                      |                    | nv/vHz |

| i <sub>n</sub>     | Input-Referred                  | f = 100kHz                                                                            |     |                          |       |                    | 0.90                                                                    |                    | pA/√Hz |

|                    | Current Noise                   | f = 1kHz                                                                              |     |                          |       |                    | 3.3                                                                     |                    | рал па |

| THD                | Total Harmonic<br>Distortion    | $    f = 5MHz, V_O = 2V_{PP}, A_V = -1, \\ R_L = 100\Omega \text{ to } V^+\!/2 $      |     |                          |       |                    | -48                                                                     |                    | dBc    |

| DG                 | Differential Gain               | $V_{CM}$ = 1V, NTSC, $A_V$ = +2<br>R <sub>L</sub> =150 $\Omega$ to V <sup>+</sup> /2  |     |                          |       |                    | 0.17%                                                                   |                    |        |

|                    |                                 | $R_L = 1k\Omega$ to V <sup>+</sup> /2                                                 |     |                          |       |                    | 0.03%                                                                   |                    |        |

| DP                 | Differential<br>Phase           | $V_{CM}$ = 1V, NTSC, $A_V$ = +2<br>R <sub>L</sub> =150 $\Omega$ to V <sup>+</sup> /2  |     |                          |       |                    | 0.05                                                                    |                    | deg    |

|                    |                                 | $R_L = 1k\Omega$ to V <sup>+</sup> /2                                                 |     |                          |       |                    | 0.03                                                                    |                    | -      |

| CT Rej.            | Cross-Talk<br>Rejection         | f = 5MHz, Receiver:<br>$R_f = R_g = 510\Omega$ , $A_V = +2$                           |     |                          |       |                    | 47                                                                      |                    | dB     |

| Τ <sub>S</sub>     | Settling Time                   | $V_O = 2V_{PP}, \pm 0.1\%$ , 8pF Load,<br>$V_S = 5V$                                  |     |                          |       |                    | 68                                                                      |                    | ns     |

| SR                 | Slew Rate (3)                   | $A_V = -1, V_I = 2V_{PP}$                                                             |     |                          |       | 90                 | 120                                                                     |                    | V/µs   |

| V <sub>OS</sub>    | Input Offset                    | For LMH6642 and LMH6644                                                               |     |                          | ±7    |                    | ±1                                                                      | ±5                 | mV     |

| Vol                | Voltage                         | For LMH6643                                                                           |     |                          | ±7    |                    | ±1                                                                      | ±3.4               | IIIV   |

| TC V <sub>OS</sub> | Input Offset<br>Average Drift   | See <sup>(4)</sup>                                                                    |     |                          |       |                    | ±5                                                                      |                    | µV/°C  |

| I <sub>B</sub>     | Input Bias<br>Current           | See <sup>(5)</sup>                                                                    |     |                          | -3.25 |                    | -1.50                                                                   | -2.60              | μA     |

| I <sub>OS</sub>    | Input Offset<br>Current         |                                                                                       |     |                          | 1000  |                    | 20                                                                      | 800                | nA     |

| R <sub>IN</sub>    | Common Mode<br>Input Resistance |                                                                                       |     |                          |       |                    | 3                                                                       |                    | MΩ     |

All limits are ensured by testing or statistical analysis. (1)

(2)

Typical values represent the most likely parametric norm. Slew rate is the average of the rising and falling slew rates. (3)

(4) (5) Offset voltage average drift determined by dividing the change in Vos at temperature extremes by the total temperature change.

Positive current corresponds to current flowing into the device.

6

## **3V Electrical Characteristics (continued)**

Unless otherwise specified, all limits ensured for V<sup>+</sup> = 3V, V<sup>-</sup> = 0V, V<sub>CM</sub> = V<sub>O</sub> = V<sup>+</sup>/2, V<sub>ID</sub> (input differential voltage) as noted (where applicable) and R<sub>L</sub> =  $2k\Omega$  to V<sup>+</sup>/2.

|                  | PARAMETER                                   | AMETER TEST CONDITIONS AT<br>TEMPERATURE<br>EXTREMES                              |     |     | -    | $V^+ = 3V, V^- = 0V,$<br>$V_{CM} = V_0 = V^+/2, V_{ID}$<br>$R_L = 2 k\Omega$ to V <sup>+</sup> /2 |                    |                    | UNIT |

|------------------|---------------------------------------------|-----------------------------------------------------------------------------------|-----|-----|------|---------------------------------------------------------------------------------------------------|--------------------|--------------------|------|

|                  |                                             |                                                                                   | MIN | TYP | MAX  | MIN <sup>(1)</sup>                                                                                | TYP <sup>(2)</sup> | MAX <sup>(1)</sup> |      |

| C <sub>IN</sub>  | Common Mode<br>Input<br>Capacitance         |                                                                                   |     |     |      |                                                                                                   | 2                  |                    | pF   |

| CMVR             | Input Common-<br>Mode Voltage               | CMRR ≥ 50dB                                                                       |     |     | -0.1 |                                                                                                   | -0.5               | -0.2               | V    |

|                  | Range                                       |                                                                                   | 1.6 |     |      | 1.8                                                                                               | 2.0                |                    | v    |

| CMRR             | Common Mode<br>Rejection Ratio              | V <sub>CM</sub> Stepped from 0V to 1.5V                                           |     |     |      | 72                                                                                                | 95                 |                    | dB   |

| A <sub>VOL</sub> | Large Signal<br>Voltage Gain                | $V_{O} = 0.5V \text{ to } 2.5V$<br>R <sub>L</sub> = 2k\Omega to V <sup>+</sup> /2 | 75  |     |      | 80                                                                                                | 96                 |                    |      |

|                  |                                             | $V_O = 0.5V$ to 2.5V<br>R <sub>L</sub> = 150 $\Omega$ to V <sup>+</sup> /2        | 70  |     |      | 74                                                                                                | 82                 |                    | dB   |

| Vo               | Output Swing                                | $R_L = 2k\Omega$ to V <sup>+</sup> /2, $V_{ID} = 200mV$                           |     |     |      | 2.90                                                                                              | 2.98               |                    | V    |

|                  | High                                        | $R_{L} = 150\Omega$ to V <sup>+</sup> /2, V <sub>ID</sub> = 200mV                 |     |     |      | 2.80                                                                                              | 2.93               |                    | V    |

|                  | Output Swing                                | $R_L = 2k\Omega$ to V <sup>+</sup> /2, $V_{ID} = -200mV$                          |     |     |      |                                                                                                   | 25                 | 75                 | mV   |

|                  | Low                                         | $R_L = 150\Omega$ to V <sup>+</sup> /2, $V_{ID} = -200$ mV                        |     |     |      |                                                                                                   | 75                 | 150                | mv   |

| I <sub>SC</sub>  | Output Short<br>Circuit Current             | Sourcing to V <sup>+</sup> /2<br>V <sub>ID</sub> = 200mV <sup>(6)</sup>           | 35  |     |      | 50                                                                                                | 95                 |                    | mA   |

|                  |                                             | Sinking to V <sup>+</sup> /2<br>V <sub>ID</sub> = $-200$ mV <sup>(6)</sup>        | 40  |     |      | 55                                                                                                | 110                |                    | ША   |

| I <sub>OUT</sub> | Output Current                              | V <sub>OUT</sub> = 0.5V from either supply                                        |     |     |      |                                                                                                   | ±65                |                    | mA   |

| +PSRR            | Positive Power<br>Supply<br>Rejection Ratio | $V^{+} = 3.0V$ to 3.5V, $V_{CM} = 1.5V$                                           |     |     |      | 75                                                                                                | 85                 |                    | dB   |

| I <sub>S</sub>   | Supply Current (per channel)                | No Load                                                                           |     |     | 4.50 |                                                                                                   | 2.70               | 4.00               | mA   |

(6) Short circuit test is a momentary test. See Note 7 under 5 V Electrical Characteristics.

Copyright © 2001–2014, Texas Instruments Incorporated

Submit Documentation Feedback 7

### LMH6642, LMH6643, LMH6644

SNOS966Q - MAY 2001 - REVISED SEPTEMBER 2014

www.ti.com

### 7.6 5V Electrical Characteristics

Unless otherwise specified, all limits ensured for  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = V_O = V^+/2$ ,  $V_{ID}$  (input differential voltage) as noted (where applicable) and  $R_L = 2k\Omega$  to V<sup>+</sup>/2.

|                     |                                     | TEST CONDITIONS                                                                            | AT TEMPERATUR<br>EXTREMES | E,    | / <sub>см</sub> = | : 5V, V <sup>−</sup> = 0<br>: V <sub>O</sub> = V <sup>+</sup> /2<br>: 2kΩ to V <sup>−</sup> | , V <sub>ID</sub>  | UNIT               |

|---------------------|-------------------------------------|--------------------------------------------------------------------------------------------|---------------------------|-------|-------------------|---------------------------------------------------------------------------------------------|--------------------|--------------------|

|                     |                                     |                                                                                            | MIN TYP M                 | MAX M | N <sup>(1)</sup>  | TYP <sup>(2)</sup>                                                                          | MAX <sup>(1)</sup> |                    |

| BW                  | -3dB BW                             | $A_V = +1, V_{OUT} = 200 m V_{PP}$                                                         |                           |       | 90                | 120                                                                                         |                    |                    |

|                     |                                     | $A_V = +2, -1, V_{OUT} = 200 mV_{PP}$                                                      |                           |       |                   | 46                                                                                          |                    | MHz                |

| BW <sub>0.1dB</sub> | 0.1dB Gain<br>Flatness              | $A_V =$ +2, $R_L =$ 150 $\Omega$ to V+/2, $R_f =$ 402 $\Omega$ , $V_{OUT} =$ 200m $V_{PP}$ |                           |       |                   | 15                                                                                          |                    | MHz                |

| PBW                 | Full Power<br>Bandwidth             | $A_V = +1$ , -1dB, $V_{OUT} = 2V_{PP}$                                                     |                           |       |                   | 22                                                                                          |                    | MHz                |

| en                  | Input-Referred                      | f = 100kHz                                                                                 |                           |       |                   | 17                                                                                          |                    | nV/√ <del>Hz</del> |

|                     | Voltage Noise                       | f = 1kHz                                                                                   |                           |       |                   | 48                                                                                          |                    |                    |

| i <sub>n</sub>      | Input-Referred                      | f = 100kHz                                                                                 |                           |       |                   | 0.90                                                                                        |                    | ~ ^ / / I =        |

|                     | Current Noise                       | f = 1kHz                                                                                   |                           |       |                   | 3.3                                                                                         |                    | pA/√Hz             |

| THD                 | Total Harmonic<br>Distortion        | $f = 5MHz, V_O = 2V_{PP}, A_V = +2$                                                        |                           |       |                   | -60                                                                                         |                    | dBc                |

| DG                  | Differential Gain                   | NTSC, $A_V = +2$<br>R <sub>L</sub> =150 $\Omega$ to V <sup>+</sup> /2                      |                           |       |                   | 0.16%                                                                                       |                    |                    |

|                     |                                     | $R_L = 1k\Omega$ to V <sup>+</sup> /2                                                      |                           |       |                   | 0.05%                                                                                       |                    |                    |

| DP                  | Differential<br>Phase               | NTSC, $A_V = +2$<br>R <sub>L</sub> = 150Ω to V <sup>+</sup> /2                             |                           |       |                   | 0.05                                                                                        |                    | deg                |

|                     |                                     | $R_L = 1k\Omega$ to V <sup>+</sup> /2                                                      |                           |       |                   | 0.01                                                                                        |                    |                    |

| CT Rej.             | Cross-Talk<br>Rejection             | f = 5MHz, Receiver:<br>$R_f = R_g = 510\Omega$ , $A_V = +2$                                |                           |       |                   | 47                                                                                          |                    | dB                 |

| Ts                  | Settling Time                       | V <sub>O</sub> = 2V <sub>PP</sub> , ±0.1%, 8pF Load                                        |                           |       |                   | 68                                                                                          |                    | ns                 |

| SR                  | Slew Rate (3)                       | $A_V = -1, V_I = 2V_{PP}$                                                                  |                           |       | 95                | 125                                                                                         |                    | V/µs               |

| V <sub>OS</sub>     | Input Offset                        | For LMH6642 and LMH6644                                                                    |                           | ±7    |                   | ±1                                                                                          | ±5                 |                    |

|                     | Voltage                             | For LMH6643                                                                                |                           | ±7    |                   | ±1                                                                                          | ±3.4               | mV                 |

| TC V <sub>OS</sub>  | Input Offset<br>Average Drift       | See <sup>(4)</sup>                                                                         |                           |       |                   | ±5                                                                                          |                    | µV/°C              |

| I <sub>B</sub>      | Input Bias<br>Current               | See <sup>(5)</sup>                                                                         |                           | 3.25  |                   | -1.70                                                                                       | -2.60              | μA                 |

| I <sub>OS</sub>     | Input Offset<br>Current             |                                                                                            | 1                         | 000   |                   | 20                                                                                          | 800                | nA                 |

| R <sub>IN</sub>     | Common Mode<br>Input<br>Resistance  |                                                                                            |                           |       |                   | 3                                                                                           |                    | MΩ                 |

| C <sub>IN</sub>     | Common Mode<br>Input<br>Capacitance |                                                                                            |                           |       |                   | 2                                                                                           |                    | pF                 |

| CMVR                | Input Common-                       | CMRR ≥ 50dB                                                                                | -                         | -0.1  |                   | -0.5                                                                                        | -0.2               |                    |

|                     | Mode Voltage<br>Range               |                                                                                            | 3.6                       |       | 3.8               | 4.0                                                                                         |                    | V                  |

| CMRR                | Common Mode<br>Rejection Ratio      | $V_{CM}$ Stepped from 0V to 3.5V                                                           |                           |       | 72                | 95                                                                                          |                    | dB                 |

| A <sub>VOL</sub>    | Large Signal<br>Voltage Gain        |                                                                                            | 82                        |       | 86                | 98                                                                                          |                    | 40                 |

|                     |                                     | $V_{O} = 0.5V$ to 4.25V<br>R <sub>L</sub> = 150 $\Omega$ to V <sup>+</sup> /2              | 72                        |       | 76                | 82                                                                                          |                    | dB                 |

All limits are ensured by testing or statistical analysis. (1)

(2)

Typical values represent the most likely parametric norm. Slew rate is the average of the rising and falling slew rates. (3)

Offset voltage average drift determined by dividing the change in V<sub>OS</sub> at temperature extremes by the total temperature change. (4)

(5) Positive current corresponds to current flowing into the device.

Submit Documentation Feedback 8

### **5V Electrical Characteristics (continued)**

Unless otherwise specified, all limits ensured for V<sup>+</sup> = 5V, V<sup>-</sup> = 0V, V<sub>CM</sub> = V<sub>0</sub> = V<sup>+</sup>/2, V<sub>ID</sub> (input differential voltage) as noted (where applicable) and R<sub>L</sub> =  $2k\Omega$  to V<sup>+</sup>/2.

|                  | PARAMETER                                   | TEST CONDITIONS                                                               |     | MPERA<br>XTREME |      | V <sup>+</sup> =<br>V <sub>СМ</sub> =<br>R <sub>L</sub> = | , V <sub>ID</sub>  | UNIT               |     |

|------------------|---------------------------------------------|-------------------------------------------------------------------------------|-----|-----------------|------|-----------------------------------------------------------|--------------------|--------------------|-----|

|                  |                                             |                                                                               | MIN | TYP             | MAX  | MIN <sup>(1)</sup>                                        | TYP <sup>(2)</sup> | MAX <sup>(1)</sup> |     |

| Vo               | Output Swing                                | $R_L = 2k\Omega$ to V <sup>+</sup> /2, $V_{ID} = 200mV$                       |     |                 |      | 4.90                                                      | 4.98               |                    | V   |

|                  | High                                        | $R_L = 150\Omega$ to V <sup>+</sup> /2, $V_{ID} = 200mV$                      |     |                 |      | 4.65                                                      | 4.90               |                    | v   |

|                  | Output Swing                                | $R_L = 2k\Omega$ to V <sup>+</sup> /2, $V_{ID} = -200mV$                      |     |                 |      |                                                           | 25                 | 100                | ~\/ |

| Low              |                                             | $R_L = 150\Omega$ to V <sup>+</sup> /2, $V_{ID} = -200$ mV                    |     |                 |      |                                                           | 100                | 150                | mV  |

| I <sub>SC</sub>  | Output Short<br>Circuit Current             | Sourcing to V <sup>+</sup> /2<br>V <sub>ID</sub> = 200mV $^{(6)(7)}$          | 40  |                 |      | 55                                                        | 115                |                    | 0   |

|                  |                                             | Sinking to V <sup>+</sup> /2<br>V <sub>ID</sub> = $-200$ mV <sup>(6)(7)</sup> | 55  |                 |      | 70                                                        | 140                |                    | mA  |

| I <sub>OUT</sub> | Output Current                              | $V_{O} = 0.5V$ from either supply                                             |     |                 |      |                                                           | ±70                |                    | mA  |

| +PSRR            | Positive Power<br>Supply<br>Rejection Ratio | V <sup>+</sup> = 4.0V to 6V                                                   |     |                 |      | 79                                                        | 90                 |                    | dB  |

| I <sub>S</sub>   | Supply Current (per channel)                | No Load                                                                       |     |                 | 5.00 |                                                           | 2.70               | 4.25               | mA  |

(6) Short circuit test is a momentary test. See Note 7.

(7) Output short circuit duration is infinite for V<sub>S</sub> < 6V at room temperature and below. For V<sub>S</sub> > 6V, allowable short circuit duration is 1.5ms.

SNOS966Q - MAY 2001 - REVISED SEPTEMBER 2014

www.ti.com

### 7.7 ±5V Electrical Characteristics

Unless otherwise specified, all limits ensured for V<sup>+</sup> = 5V, V<sup>-</sup> = -5V, V<sub>CM</sub> = V<sub>O</sub> = 0V, V<sub>ID</sub> (input differential voltage) as noted (where applicable) and R<sub>L</sub> =  $2k\Omega$  to ground.

|                     | PARAMETER                           | TEST CONDITIONS                                                                    |            | MPERATI<br>TREMES |       | V <sup>+</sup> =<br>V <sub>CM</sub> | UNIT               |                    |                    |

|---------------------|-------------------------------------|------------------------------------------------------------------------------------|------------|-------------------|-------|-------------------------------------|--------------------|--------------------|--------------------|

|                     |                                     |                                                                                    | MIN        | TYP               | MAX   | MIN <sup>(1)</sup>                  | TYP <sup>(2)</sup> | MAX <sup>(1)</sup> |                    |

| BW                  | -3dB BW                             | $A_V = +1$ , $V_{OUT} = 200 m V_{PP}$                                              |            |                   |       | 95                                  | 130                |                    | N 41 1-            |

|                     |                                     | $A_V = +2, -1, V_{OUT} = 200 mV_{PP}$                                              |            |                   |       |                                     | 46                 |                    | MHz                |

| BW <sub>0.1dB</sub> | 0.1dB Gain<br>Flatness              | $A_V = +2, R_L = 150\Omega \text{ to V+/2}, R_f = 806\Omega, V_{OUT} = 200mV_{PP}$ |            |                   |       |                                     | 12                 |                    | MHz                |

| PBW                 | Full Power<br>Bandwidth             | $A_V = +1$ , -1dB, $V_{OUT} = 2V_{PP}$                                             |            |                   |       |                                     | 24                 |                    | MHz                |

| en                  | Input-Referred                      | f = 100kHz                                                                         |            |                   |       |                                     | 17                 |                    | nV/√ <del>Hz</del> |

|                     | Voltage Noise                       | f = 1kHz                                                                           |            |                   |       |                                     | 48                 |                    |                    |

| i <sub>n</sub>      | Input-Referred                      | f = 100kHz                                                                         |            |                   |       |                                     | 0.90               |                    | pA/√Hz             |

|                     | Current Noise                       | f = 1kHz                                                                           | = 1kHz 3.3 |                   |       | ра/ т                               |                    |                    |                    |

| THD                 | Total Harmonic<br>Distortion        | f = 5MHz, $V_O = 2V_{PP}$ , $A_V = +2$                                             |            |                   |       |                                     | -62                |                    | dBc                |

| DG                  | Differential Gain                   | NTSC, $A_V = +2$<br>$R_L = 150\Omega$ to V <sup>+</sup> /2                         |            |                   |       |                                     | 0.15%              |                    |                    |

|                     |                                     | $R_L = 1k\Omega$ to V <sup>+</sup> /2                                              |            |                   |       |                                     | 0.01%              |                    |                    |

| DP                  | Differential<br>Phase               | NTSC, $A_V = +2$<br>$R_L = 150\Omega$ to V <sup>+</sup> /2                         |            |                   |       |                                     | 0.04               |                    | deg                |

|                     |                                     | $R_L = 1k\Omega$ to V <sup>+</sup> /2                                              |            |                   |       |                                     | 0.01               |                    | 5                  |

| CT Rej.             | Cross-Talk<br>Rejection             | f = 5MHz, Receiver:<br>$R_f = R_g = 510\Omega$ , $A_V = +2$                        |            |                   |       |                                     | 47                 |                    | dB                 |

| Τ <sub>S</sub>      | Settling Time                       | $V_O = 2V_{PP}, \pm 0.1\%, 8pF Load, V_S = 5V$                                     |            |                   |       |                                     | 68                 |                    | ns                 |

| SR                  | Slew Rate (3)                       | $A_V = -1, V_I = 2V_{PP}$                                                          |            |                   |       | 100                                 | 135                |                    | V/µs               |

| V <sub>OS</sub>     | Input Offset                        | For LMH6642 and LMH6644                                                            |            |                   | ±7    |                                     | ±1                 | ±5                 | m)/                |

|                     | Voltage                             | For LMH6643                                                                        |            |                   | ±7    |                                     | ±1                 | ±3.4               | mV                 |

| TC $V_{OS}$         | Input Offset<br>Average Drift       | See (4)                                                                            |            |                   |       |                                     | ±5                 |                    | µV/°C              |

| I <sub>B</sub>      | Input Bias<br>Current               | See <sup>(5)</sup>                                                                 |            |                   | -3.25 |                                     | -1.60              | -2.60              | μA                 |

| I <sub>OS</sub>     | Input Offset<br>Current             |                                                                                    |            |                   | 1000  |                                     | 20                 | 800                | nA                 |

| R <sub>IN</sub>     | Common Mode<br>Input<br>Resistance  |                                                                                    |            |                   |       |                                     | 3                  |                    | MΩ                 |

| C <sub>IN</sub>     | Common Mode<br>Input<br>Capacitance |                                                                                    |            |                   |       |                                     | 2                  |                    | pF                 |

| CMVR                | Input Common-                       | CMRR ≥ 50dB                                                                        |            |                   | -5.1  |                                     | -5.5               | -5.2               |                    |

|                     | Mode Voltage<br>Range               |                                                                                    | 3.6        |                   |       | 3.8                                 | 4.0                |                    | V                  |

| CMRR                | Common Mode<br>Rejection Ratio      | $V_{CM}$ Stepped from –5V to 3.5V                                                  |            |                   |       | 74                                  | 95                 |                    | dB                 |

(1) All limits are ensured by testing or statistical analysis.

(2) Typical values represent the most likely parametric norm.

(3) Slew rate is the average of the rising and falling slew rates.

(4) Offset voltage average drift determined by dividing the change in V<sub>OS</sub> at temperature extremes by the total temperature change.

(5) Positive current corresponds to current flowing into the device.

## ±5V Electrical Characteristics (continued)

Unless otherwise specified, all limits ensured for V<sup>+</sup> = 5V, V<sup>-</sup> = -5V, V<sub>CM</sub> = V<sub>O</sub> = 0V, V<sub>ID</sub> (input differential voltage) as noted (where applicable) and  $R_L = 2k\Omega$  to ground.

|                                     | PARAMETER                                                 | TEST CONDITIONS                                                        |     | MPERATI<br>TREMES | -    | V <sup>+</sup> =<br>V <sub>CM</sub> |                    | UNIT               |    |

|-------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------|-----|-------------------|------|-------------------------------------|--------------------|--------------------|----|

|                                     |                                                           |                                                                        | MIN | ТҮР               | MAX  | MIN <sup>(1)</sup>                  | TYP <sup>(2)</sup> | MAX <sup>(1)</sup> |    |

| A <sub>VOL</sub>                    | Large Signal<br>Voltage Gain                              | $V_{O} = -4.5V$ to 4.5V,<br>$R_{L} = 2k\Omega$                         | 84  |                   |      | 88                                  | 96                 |                    | dB |

|                                     | $V_{O} = -4.0V$ to 4.0V,<br>R <sub>L</sub> = 150 $\Omega$ | 74                                                                     |     |                   | 78   | 82                                  |                    | uв                 |    |

| V <sub>O</sub> Output Swing<br>High |                                                           | $R_L = 2k\Omega$ , $V_{ID} = 200mV$                                    |     |                   |      | 4.90                                | 4.96               |                    | N/ |

|                                     |                                                           | $R_{L} = 150\Omega, V_{ID} = 200mV$                                    |     |                   |      | 4.65                                | 4.80               |                    | V  |

|                                     | Output Swing                                              | $R_L = 2k\Omega, V_{ID} = -200mV$                                      |     |                   |      |                                     | -4.96              | -4.90              | V  |

|                                     | Low                                                       | R <sub>L</sub> = 150Ω, V <sub>ID</sub> = −200mV                        |     |                   |      |                                     | -4.80              | -4.65              | v  |

| I <sub>SC</sub>                     | Output Short<br>Circuit Current                           | Sourcing to Ground $V_{ID} = 200 \text{mV}^{(6)(7)}$                   | 35  |                   |      | 60                                  | 115                |                    | 0  |

|                                     |                                                           | Sinking to Ground<br>$V_{ID} = -200 \text{mV}^{(6)(7)}$                | 65  |                   |      | 85                                  | 145                |                    | mA |

| I <sub>OUT</sub>                    | Output Current                                            | $V_{O} = 0.5V$ from either supply                                      |     |                   |      | ±75                                 |                    |                    | mA |

| PSRR                                | Power Supply<br>Rejection Ratio                           | (V <sup>+</sup> , V <sup>−</sup> ) = (4.5V, −4.5V) to (5.5V,<br>−5.5V) |     |                   |      | 78                                  | 90                 |                    | dB |

| I <sub>S</sub>                      | Supply Current (per channel)                              | No Load                                                                |     |                   | 5.50 |                                     | 2.70               | 4.50               | mA |

(6) Short circuit test is a momentary test. See  $^{(7)}$ . (7) Output short circuit duration is infinite for V<sub>S</sub> < 6V at room temperature and below. For V<sub>S</sub> > 6V, allowable short circuit duration is 1.5ms.

TEXAS INSTRUMENTS

www.ti.com

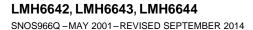

## 7.8 Typical Performance Characteristics

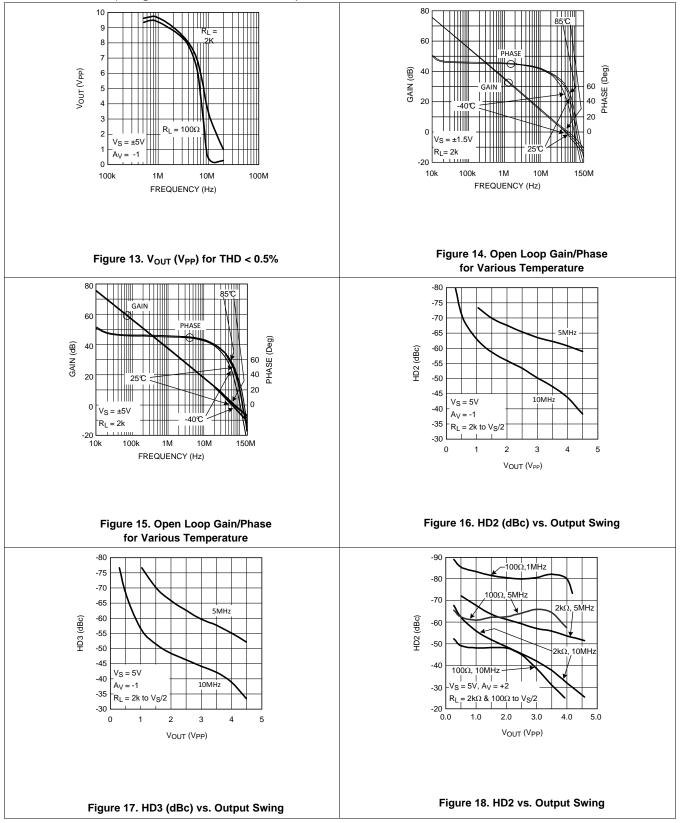

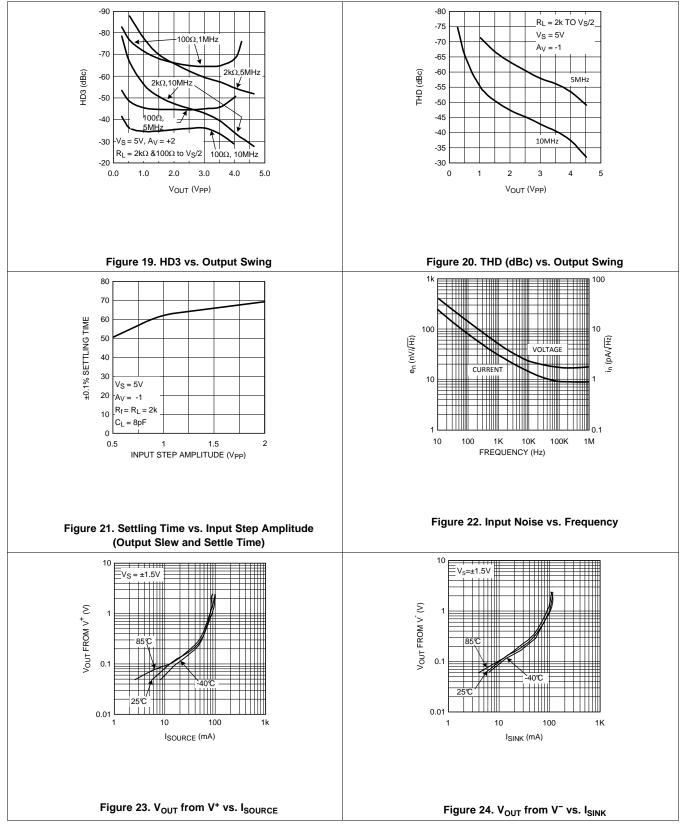

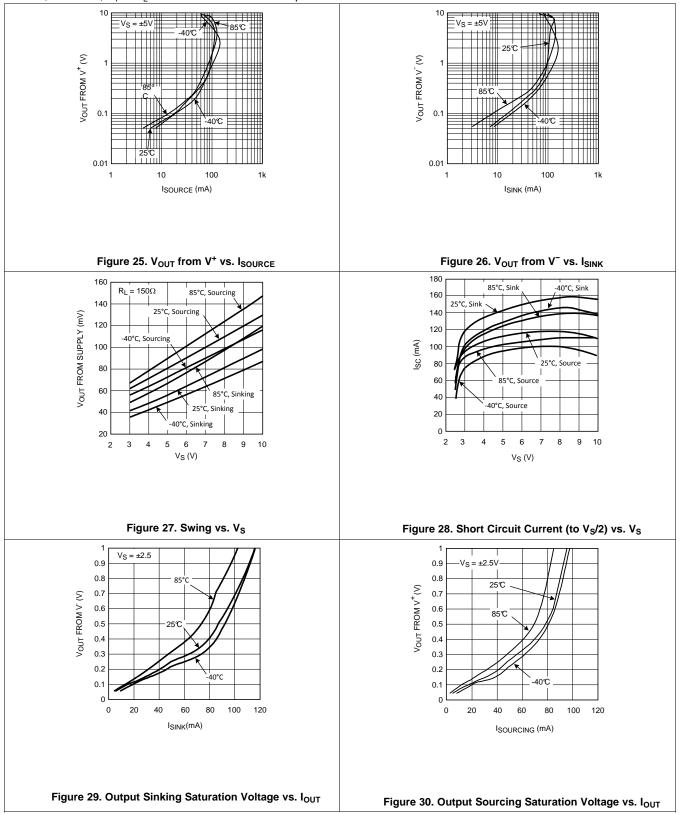

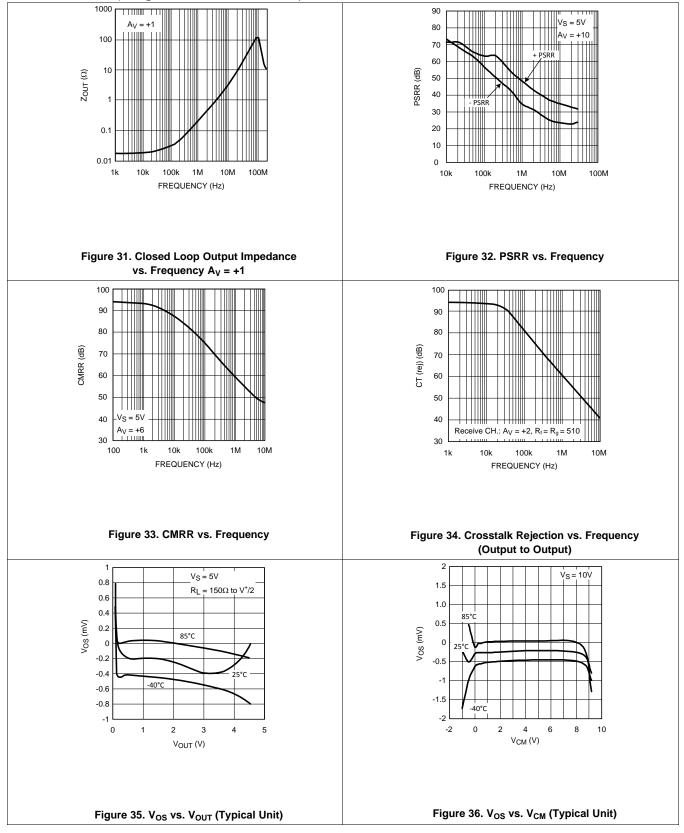

V<sup>+</sup> = +5, V<sup>-</sup> = -5V, R<sub>F</sub> = R<sub>L</sub> = 2 k $\Omega$ . Unless otherwise specified.

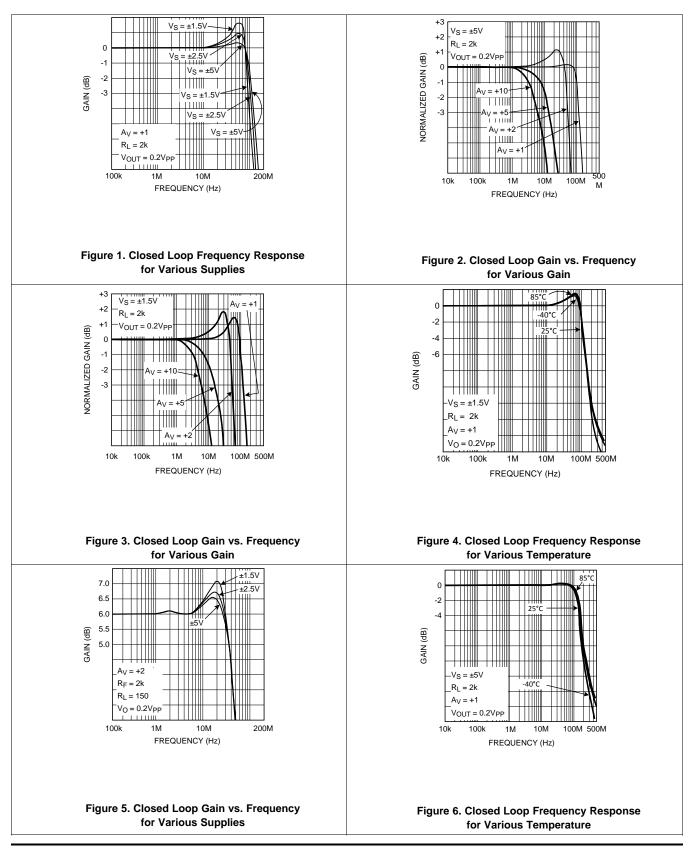

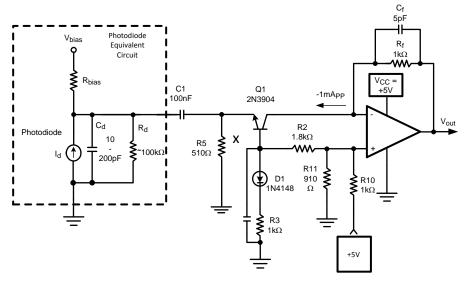

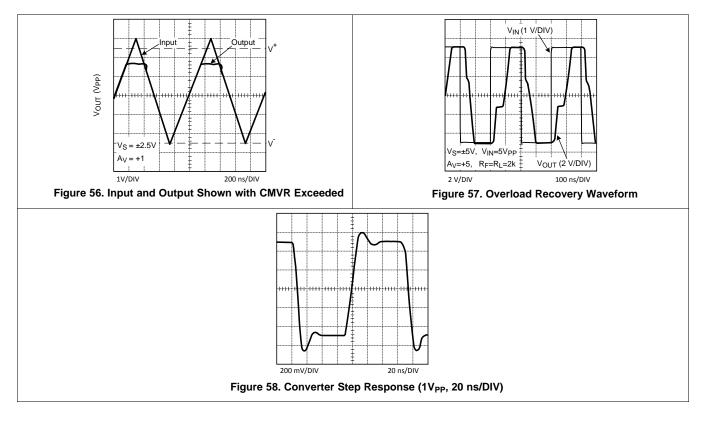

## **Typical Performance Characteristics (continued)**

$V^+$  = +5,  $V^-$  = -5V,  $R_F$  =  $R_L$  = 2 k $\Omega$ . Unless otherwise specified.

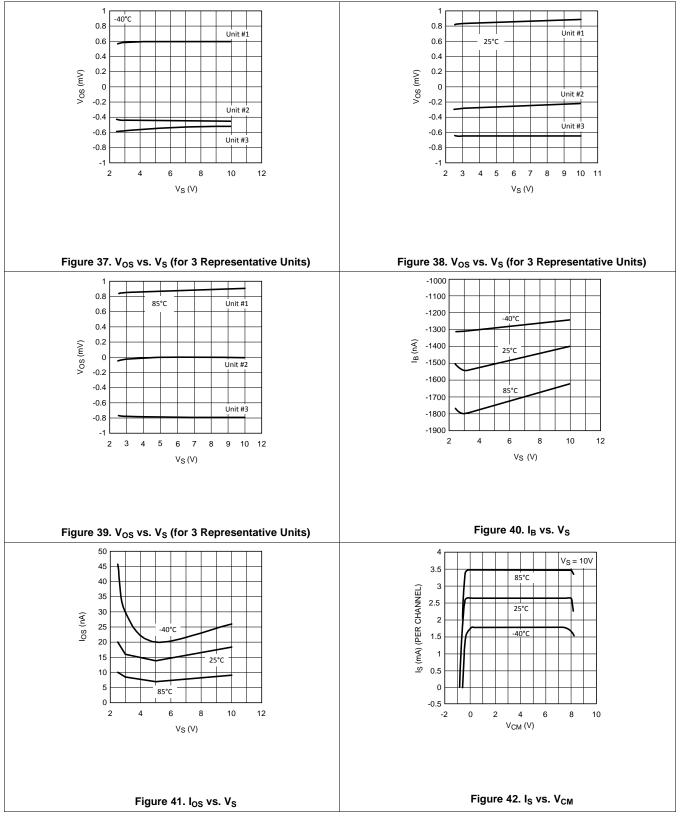

## **Typical Performance Characteristics (continued)**

$V^+$  = +5,  $V^-$  = -5V,  $R_F$  =  $R_L$  = 2 k $\Omega$ . Unless otherwise specified.

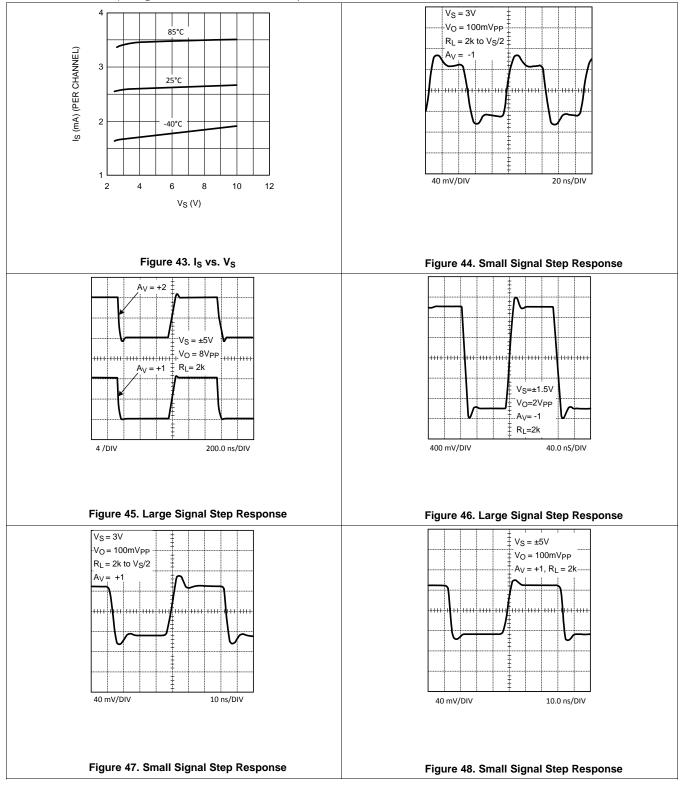

## **Typical Performance Characteristics (continued)**

$V^+$  = +5,  $V^-$  = -5V,  $R_F$  =  $R_L$  = 2 k $\Omega$ . Unless otherwise specified.

TEXAS INSTRUMENTS

www.ti.com

## **Typical Performance Characteristics (continued)**

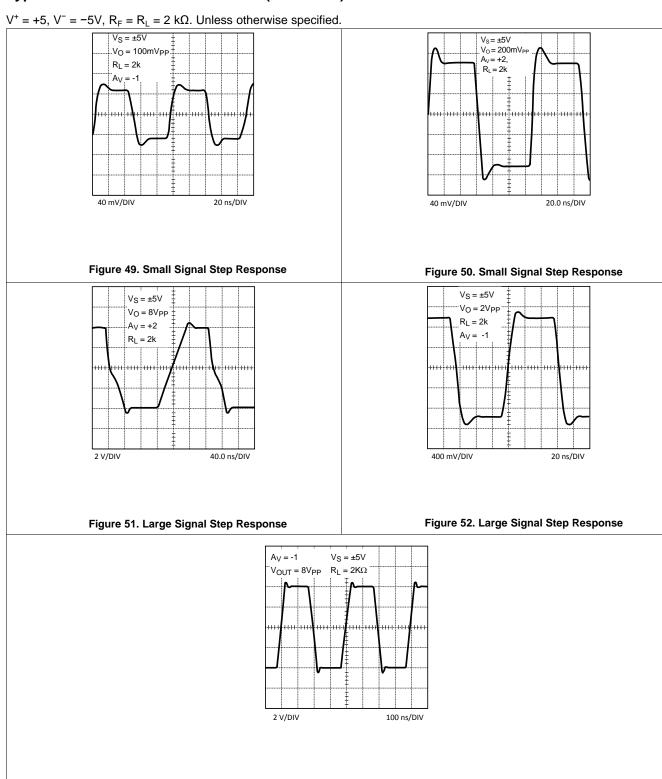

$V^+$  = +5,  $V^-$  = -5V,  $R_F = R_L = 2 \text{ k}\Omega$ . Unless otherwise specified.

## **Typical Performance Characteristics (continued)**

Copyright © 2001–2014, Texas Instruments Incorporated

## **Typical Performance Characteristics (continued)**

$V^+$  = +5,  $V^-$  = -5V,  $R_F$  =  $R_L$  = 2 k $\Omega$ . Unless otherwise specified.

## **Typical Performance Characteristics (continued)**

$V^+$  = +5,  $V^-$  = -5V,  $R_F$  =  $R_L$  = 2 k $\Omega$ . Unless otherwise specified.

## **Typical Performance Characteristics (continued)**

Figure 53. Large Signal Step Response

Copyright © 2001–2014, Texas Instruments Incorporated

## 8 Detailed Description

### 8.1 Overview

The LMH664X family is based on proprietary VIP10 dielectrically isolated bipolar process. This device family architecture features the following:

- Complimentary bipolar devices with exceptionally high f<sub>t</sub> (~8 GHz) even under low supply voltage (2.7 V) and low bias current.

- A class A-B "turn-around" stage with improved noise, offset, and reduced power dissipation compared to similar speed devices (patent pending).

- Common Emitter push-push output stage capable of 75 mA output current (at 0.5 V from the supply rails) while consuming only 2.7 mA of total supply current per channel. This architecture allows output to reach within mV of either supply rail.

- Consistent performance over the entire operating supply voltage range with little variation for the most important specifications (for example, BW, SR, I<sub>OUT</sub>, and so forth)

- Significant power saving (~40%) compared to competitive devices on the market with similar performance.

### 8.2 Functional Block Diagram

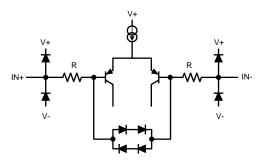

Figure 54. Input Equivalent Circuit

### 8.3 Feature Description

The LMH664X family is a drop-in replacement for the AD805X family of high speed Op Amps in most applications. In addition, the LMH664X will typically save about 40% on power dissipation, due to lower supply current, when compared to competition. All AD805X family's specified parameters are included in the list of LMH664X ensured specifications in order to ensure equal or better level of performance. However, as in most high performance parts, due to subtleties of applications, it is strongly recommended that the performance of the part to be evaluated is tested under actual operating conditions to ensure full compliance to all specifications.

### 8.4 Device Functional Modes