Sample &

Buy

TUSB1210-Q1

SLLSEL4A-SEPTEMBER 2014-REVISED OCTOBER 2014

# TUSB1210-Q1 Standalone USB Transceiver Chip Silicon

# 1 Features

- AEC-Q100 Qualified with:

- Temperature Grade 3: -40°C to 85°C

- HBM ESD Classification 1C

- CDM ESD Classification C4B

- USB2.0 PHY Transceiver Chip, Designed to Interface with a USB Controller via a ULPI 12-pin Interface, Fully Compliant With:

- Universal Serial Bus Specification Rev. 2.0

- On-The-Go Supplement to the USB 2.0 Specification Rev. 1.3

- UTMI+ Low Pin Interface (ULPI) Specification Rev. 1.1

- DP/DM Line External Component Compensation (Patent #US7965100 B1)

- Interfaces to Host, Peripheral and OTG Device Cores; Optimized for Portable Devices or System ASICs with Built-in USB OTG Device Core

- Complete USB OTG Physical Front-End that Supports Host Negotiation Protocol (HNP) and Session Request Protocol (SRP)

- ULPI Interface:

- I/O Interface (1.8 V) Optimized for Non-Terminated 50 Ω Line Impedance

- ULPI CLOCK Pin (60 MHz) Supports Both Input and Output Clock Configurations

- Fully Programmable ULPI-Compliant Register Set

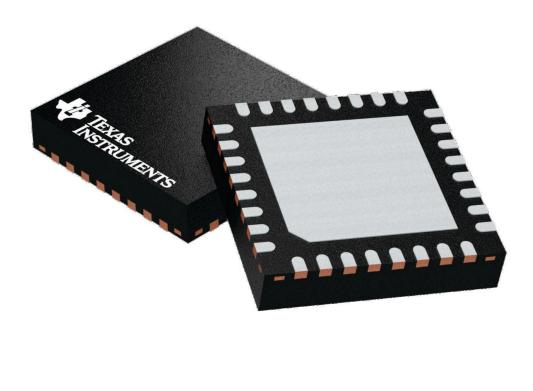

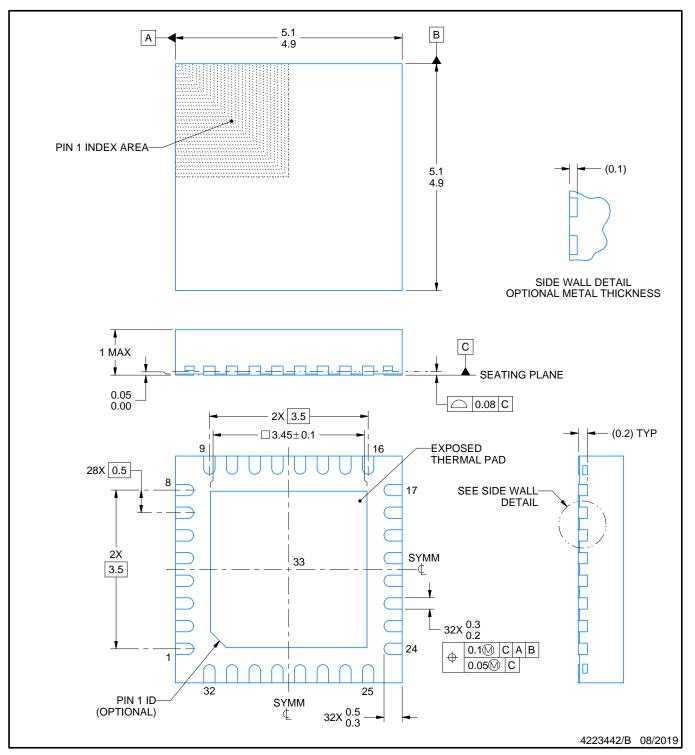

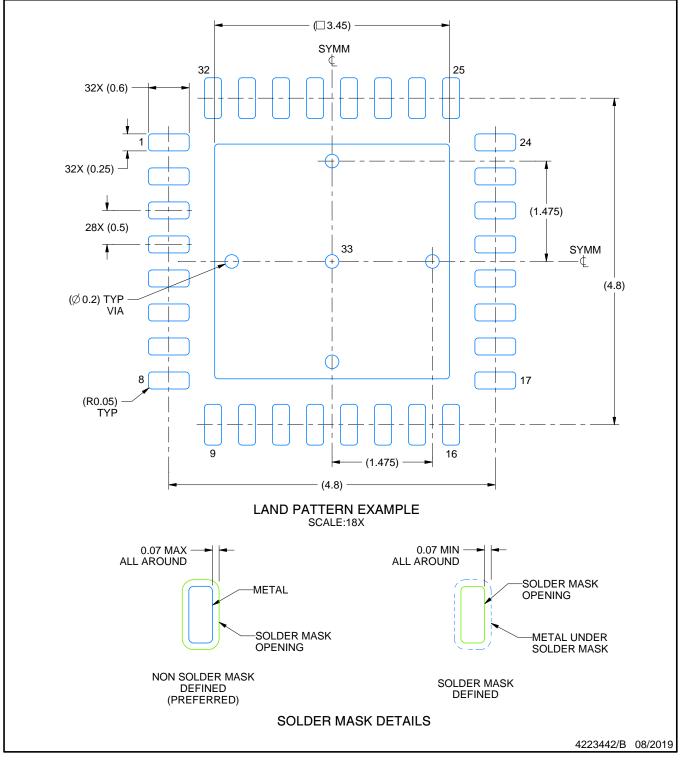

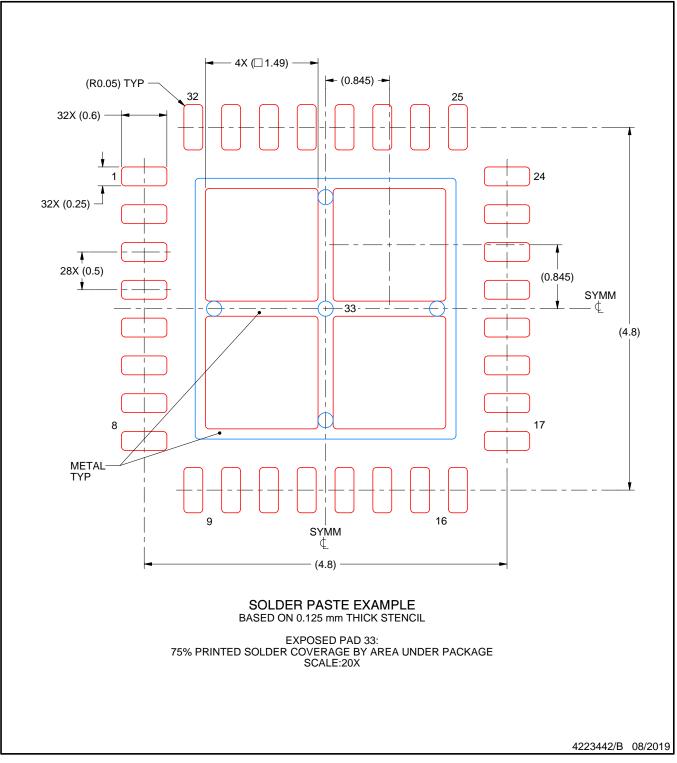

- Available in a 32-Pin Quad Flat No Lead [QFN (RHB)] Package

# 2 Applications

- Mobile Phones

- Tablet Devices

- Desktop Computers

- Portable Computers

- Video Game Consoles

- Portable Music Players

# **3** Description

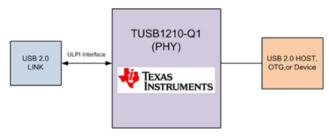

The TUSB1210-Q1 is a USB2.0 transceiver chip, designed to interface with a USB controller via a ULPI interface. It supports all USB2.0 data rates (High-Speed 480 Mbps, Full-Speed 12 Mbps and Low-Speed 1.5 Mbps), and is compliant to both Host and Peripheral modes. It additionally supports a UART mode and legacy ULPI serial modes.

TUSB1210-Q1 also supports the OTG (Ver1.3) optional addendum to the USB 2.0 Specification, including Host Negotiation Protocol (HNP) and Session Request Protocol (SRP).

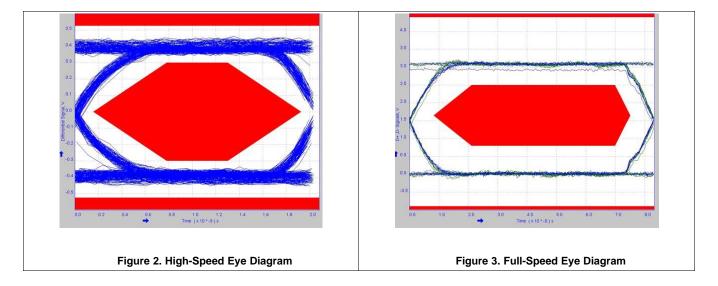

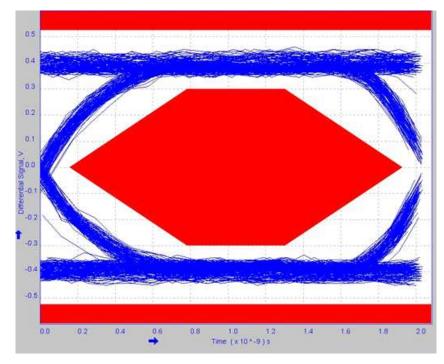

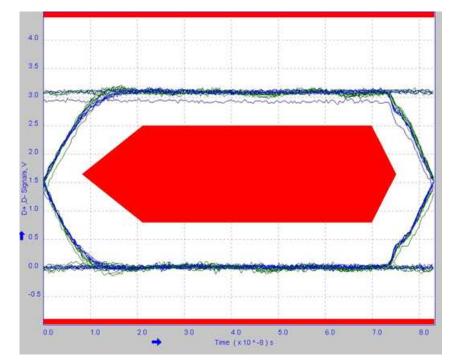

The DP/DM external component compensation in the transmitter compensates for variations in the series impendence in order to match with the data line impedance and the receiver input impedance, to limit data reflections, and thereby, improve eye diagrams.

| Device | Inform     | nation | (1) |

|--------|------------|--------|-----|

| DEVICE | IIII OI II | ιαιισπ |     |

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |  |  |  |  |

|-------------|-----------|-------------------|--|--|--|--|

| TUSB1210-Q1 | VQFN (32) | 5.00 mm x 5.00 mm |  |  |  |  |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

7

2

# **Table of Contents**

| Features 1                                   |

|----------------------------------------------|

| Applications 1                               |

| Description 1                                |

| Revision History 2                           |

| Pin Configuration and Functions 3            |

| Specifications 4                             |

| 6.1 Absolute Maximum Ratings 4               |

| 6.2 Handling Ratings 4                       |

| 6.3 Recommended Operating Conditions 5       |

| 6.4 Thermal Information 5                    |

| 6.5 Analog I/O Electrical Characteristics 5  |

| 6.6 Digital I/O Electrical Characteristics 5 |

| 6.7 Digital IO Pins (Non-ULPI)5              |

| 6.8 PHY Electrical Characteristics 6         |

| 6.9 Pullup/Pulldown Resistors8               |

| 6.10 OTG Electrical Characteristics          |

| 6.11 Power Characteristics 10                |

| 6.12 Switching Characteristics 10            |

| 6.13 Timing Requirements 11                  |

| 6.14 Typical Characteristics 13              |

| Detailed Description 14                      |

| 7.1 Overview 14                              |

| 7.2 Functional Block Diagram 14              |

| 7.3 Feature Description 15                   |

|                                              |

|    | 7.4  | Device Functional Modes           | 18 |

|----|------|-----------------------------------|----|

|    | 7.5  | Register Map                      | 20 |

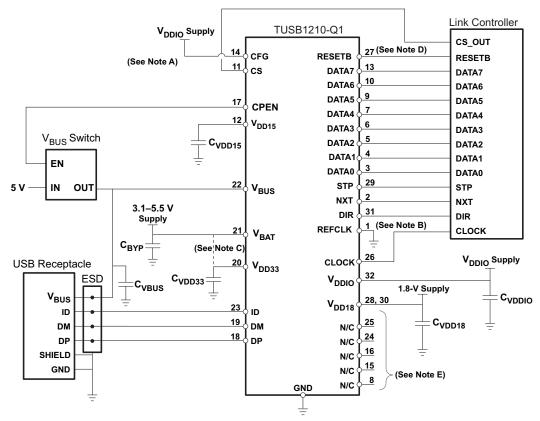

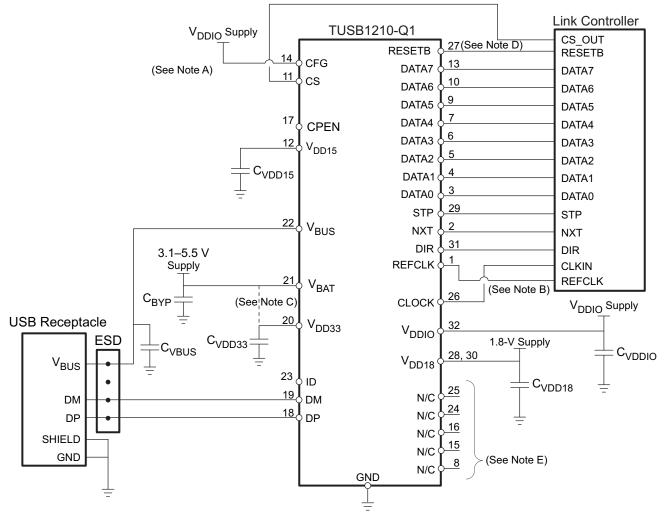

| 8  | App  | lication and Implementation       | 49 |

|    | 8.1  | Application Information           | 49 |

|    | 8.2  | Typical Application               | 49 |

|    | 8.3  | External Components               | 53 |

| 9  | Pow  | er Supply Recommendations         | 54 |

|    | 9.1  | TUSB1210 Power Supply             | 54 |

|    | 9.2  | Ground                            | 54 |

|    | 9.3  | Power Providers                   | 54 |

|    | 9.4  | Power Modules                     | 54 |

|    | 9.5  | Power Consumption                 | 55 |

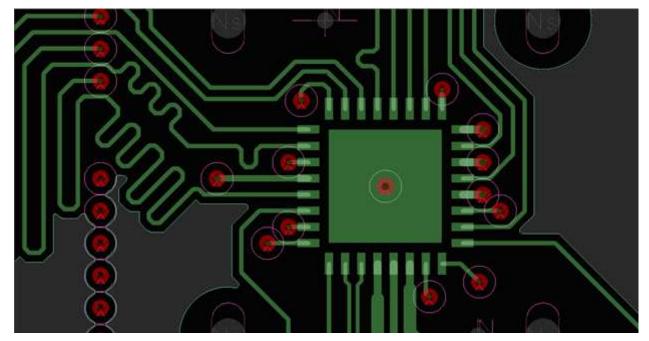

| 10 | Lay  | out                               | 56 |

|    | 10.1 | Layout Guidelines                 | 56 |

|    | 10.2 | Layout Example                    | 56 |

| 11 | Dev  | ice and Documentation Support     | 57 |

|    | 11.1 | Documentation Support             | 57 |

|    | 11.2 | Community Resources               | 57 |

|    | 11.3 | Trademarks                        | 57 |

|    | 11.4 | Electrostatic Discharge Caution   | 57 |

|    | 11.5 | Glossary                          | 57 |

| 12 | Mec  | hanical, Packaging, and Orderable |    |

|    | Info | rmation                           |    |

|    | 12.1 | Via Channel                       |    |

|    | 12.2 | Packaging Information             | 58 |

# 4 Revision History

#

www.ti.com

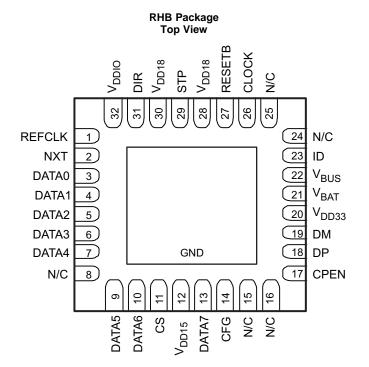

# 5 Pin Configuration and Functions

### **Pin Functions**

| PIN   |                  | A/D | ТҮРЕ | LEVEL             | DESCRIPTION                                                                                                                                              |

|-------|------------------|-----|------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | NO.              | A/D | ITPE | LEVEL             | DESCRIPTION                                                                                                                                              |

| CFG   | 14               | D   | I    | V <sub>DDIO</sub> | REFCLK clock frequency configuration pin. Two frequencies are supported: 19.2 MHz when 0, or 26 MHz when 1.                                              |

|       |                  |     |      |                   | ULPI 60 MHz clock on which ULPI data is synchronized.                                                                                                    |

|       |                  |     |      |                   | Two modes are possible:                                                                                                                                  |

| CLOCK | 26               | D   | 0    | V <sub>DDIO</sub> | Input Mode: CLOCK defaults as an input.                                                                                                                  |

|       |                  |     |      |                   | Output Mode: When an input clock is detected on REFCLK pin (after 4 rising edges) then CLOCK will change to an output.                                   |

| CPEN  | 17               | D   | 0    | V <sub>DD33</sub> | CMOS active-high digital output control of external 5V VBUS supply                                                                                       |

| CS    | 11               | D   | I    | V <sub>DDIO</sub> | Active-high chip select pin. When low the IC is in power down and ULPI bus is tristated. When high normal operation. Tie to $V_{\text{DDIO}}$ if unused. |

| DATA0 | 3                | D   | I/O  | V <sub>DDIO</sub> | ULPI DATA input/output signal 0 synchronized to CLOCK                                                                                                    |

| DATA1 | 4                | D   | I/O  | V <sub>DDIO</sub> | ULPI DATA input/output signal 1 synchronized to CLOCK                                                                                                    |

| DATA2 | 5                | D   | I/O  | V <sub>DDIO</sub> | ULPI DATA input/output signal 2 synchronized to CLOCK                                                                                                    |

| DATA3 | 6                | D   | I/O  | V <sub>DDIO</sub> | ULPI DATA input/output signal 3 synchronized to CLOCK                                                                                                    |

| DATA4 | 7                | D   | I/O  | V <sub>DDIO</sub> | ULPI DATA input/output signal 4 synchronized to CLOCK                                                                                                    |

| DATA5 | 9                | D   | I/O  | V <sub>DDIO</sub> | ULPI DATA input/output signal 5 synchronized to CLOCK                                                                                                    |

| DATA6 | 10               | D   | I/O  | V <sub>DDIO</sub> | ULPI DATA input/output signal 6 synchronized to CLOCK                                                                                                    |

| DATA7 | 13               | D   | I/O  | V <sub>DDIO</sub> | ULPI DATA input/output signal 7 synchronized to CLOCK                                                                                                    |

| DIR   | 31               | D   | 0    | V <sub>DDIO</sub> | ULPI DIR output signal                                                                                                                                   |

| DM    | 19               | А   | I/O  | V <sub>DD33</sub> | DM pin of the USB connector                                                                                                                              |

| DP    | 18               | А   | I/O  | V <sub>DD33</sub> | DP pin of the USB connector                                                                                                                              |

| ID    | 23               | А   | I/O  | V <sub>DD33</sub> | Identification (ID) pin of the USB connector                                                                                                             |

| N/C   | 8                | -   | -    | V <sub>DDIO</sub> | No connect                                                                                                                                               |

| N/C   | 15,16, 24,<br>24 | -   | -    | -                 | No connect                                                                                                                                               |

| NXT   | 2                | D   | 0    | V <sub>DDIO</sub> | ULPI NXT output signal                                                                                                                                   |

TUSB1210-Q1 SLLSEL4A-SEPTEMBER 2014-REVISED OCTOBER 2014

www.ti.com

**STRUMENTS**

EXAS

# **Pin Functions (continued)**

| PIN               |                | A/D | TYPE  | LEVEL             | DESCRIPTION                                                                                                                                                                                                                                                                                                                    |  |

|-------------------|----------------|-----|-------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME              | NO.            | A/D | TIPE  | LEVEL             | DESCRIPTION                                                                                                                                                                                                                                                                                                                    |  |

| REFCLK            | 1              | A   | I     | 3.3 V             | $V_{\text{DD33}}$ Reference clock input (square-wave only). Tie to GND when pin 26 (CLOCK) is required to be Input mode. Connect to square-wave reference clock of amplitude in the range of 3 V to 3.6 V when Pin 26 (CLOCK) is required to be Output mode. See pin 14 (CFG) description for REFCLK input frequency settings. |  |

| RESETB            | 27             | D   | I     | V <sub>DDIO</sub> | When low, all digital logic (except 32 kHz logic required for power up sequencing) including registers are reset to their default values, and ULPI bus is tri-stated. Whe high, normal USB operation.                                                                                                                          |  |

| STP               | 29             | D   | I     | V <sub>DDIO</sub> | ULPI STP input signal                                                                                                                                                                                                                                                                                                          |  |

| VBAT              | 21             | А   | power | V <sub>BAT</sub>  | Input supply voltage or battery source                                                                                                                                                                                                                                                                                         |  |

| V <sub>BUS</sub>  | 22             | А   | power | V <sub>BUS</sub>  | V <sub>BUS</sub> pin of the USB connector                                                                                                                                                                                                                                                                                      |  |

| VDD15             | 12             | А   | power |                   | 1.5-V internal LDO output. Connect to external filtering capacitor.                                                                                                                                                                                                                                                            |  |

| V <sub>DD18</sub> | 28, 30         | А   | power | V <sub>DD18</sub> | External 1.8-V supply input. Connect to external filtering capacitor.                                                                                                                                                                                                                                                          |  |

| V <sub>DD33</sub> | 20             | А   | power | V <sub>DD33</sub> | 3.3-V internal LDO output. Connect to external filtering capacitor.                                                                                                                                                                                                                                                            |  |

| V <sub>DDIO</sub> | 32             | А   | I     | V <sub>DDIO</sub> | External 1.8V supply input for digital I/Os. Connect to external filtering capacitor.                                                                                                                                                                                                                                          |  |

| GND               | Thermal<br>Pad | А   | power |                   | Reference Ground                                                                                                                                                                                                                                                                                                               |  |

#### **Specifications** 6

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                   |                                            |                                                                                                                        | MIN  | MAX                      | UNIT |

|-------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------|--------------------------|------|

| V <sub>CC</sub>   | Main battery supply voltage <sup>(2)</sup> |                                                                                                                        | 0    | 5                        | V    |

|                   | Voltage on any input <sup>(3)</sup>        | Where supply represents the voltage applied to the power supply pin associated with the input                          | -0.3 | 1 × V <sub>CC</sub> +0.3 | V    |

|                   | V <sub>BUS</sub> input                     |                                                                                                                        | -2   | 20                       | V    |

|                   | ID, DP, DM inputs                          | Stress condition specified 24h                                                                                         | -0.3 | 5.25                     | V    |

| V <sub>DDIO</sub> | IO supply voltage                          | Continuous                                                                                                             | -0.3 | 1.98                     | V    |

| T <sub>A</sub>    | Ambient temperature range                  |                                                                                                                        | -40  | 85                       | °C   |

| TJ                | Junction temperature range                 |                                                                                                                        | -40  | 150                      | °C   |

|                   | Ambient temperature for parametric         | Parametric compliance                                                                                                  | -14  | 125                      | °C   |

|                   | compliance                                 | With max 125°C as junction temperature                                                                                 | -40  | 85                       | °C   |

|                   | DP, DM, ID high voltage short circuit      | DP, DM or ID pins short circuited to $V_{BUS}$ supply, in any mode of TUSB1210-Q1 operation, continuously for 24 hours | 0    | 5.25                     | V    |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. The product will have negligible reliability impact if voltage spikes of 5.5 V occur for a total (cumulative over lifetime) duration of 5

(2) milliseconds.

Except V<sub>BAT</sub> input, V<sub>BUS</sub>, ID, DP, and DM pads (3)

# 6.2 Handling Ratings

|                                     |                                     |                                                                                               |            | MIN  | MAX  | UNIT |

|-------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------|------------|------|------|------|

| T <sub>stg</sub>                    | Storage temperature range           |                                                                                               | -65        | 150  | °C   |      |

|                                     | Electrostatic discharge             | Human body model (HBM), per AEC Q100-002<br>Classification Level H1C, all pins <sup>(1)</sup> |            | 1500 | 1500 |      |

| V <sub>ESD</sub> (ESD) performance: | Charged device model (CDM), per AEC | Corner pins                                                                                   | -750       | 750  | V    |      |

|                                     |                                     | Q100-011 Classification Level C4B                                                             | Other pins | -500 | 500  |      |

(1) AEC Q100-002 indicates HBM stressing is done in accordance with ANSI/ESDA/JEDEC JS-001 specifications.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                        | PARAMETER                          | TEST CONDITIONS                                    | MIN                      | NOM | MAX                            | UNIT |

|------------------------|------------------------------------|----------------------------------------------------|--------------------------|-----|--------------------------------|------|

| Battery supply voltage |                                    |                                                    | 2.7                      | 3.6 | 4.8                            | V    |

|                        | Battery supply voltage for USB 2.0 | When V <sub>DD33</sub> is supplied internally      | 3.15                     |     |                                | V    |

|                        | compliancy (USB 2.0 certification) | When $V_{DD33}$ is shorted to $V_{BAT}$ externally | 3.05                     |     |                                |      |

| V <sub>DDIO</sub>      | Digital IO pin supply              |                                                    | 1.71                     |     | 1.98                           | V    |

| V <sub>IL</sub>        | Low-level input voltage            | CLOCK, STP, DIR, NXT, DATA0 to DATA7               |                          |     | $0.35 	ext{ x V}_{	ext{DDIO}}$ | V    |

| VIH                    | High-level output voltage          | CLOCK, STP, DIR, NXT, DATA0 to DATA7               | 0.65 x V <sub>DDIO</sub> |     |                                | V    |

| T <sub>A</sub>         | Ambient temperature range          |                                                    | -40                      |     | 85                             | °C   |

# 6.4 Thermal Information

|                          | THERMAL METRIC <sup>(1)</sup>                |           |       |

|--------------------------|----------------------------------------------|-----------|-------|

|                          |                                              | (16 Pins) | UNIT  |

| $R_{\thetaJA}$           | Junction-to-ambient thermal resistance       | 34.72     |       |

| R <sub>0JC(top)</sub>    | Junction-to-case(top) thermal resistance     | 37.3      |       |

| $R_{\theta JB}$          | Junction-to-board thermal resistance         | 10.3      | °C/W  |

| ΨJT                      | Junction-to-top characterization parameter   | 0.5       | °C/VV |

| $\psi_{JB}$              | Junction-to-board characterization parameter | 10.5      |       |

| R <sub>0JC(bottom)</sub> | Junction-to-case(bottom) thermal resistance  | 3.6       |       |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

# 6.5 Analog I/O Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                 | PARAMETER CONDITIONS           |                         | MIN                     | TYP | MAX | UNIT |

|-----------------|--------------------------------|-------------------------|-------------------------|-----|-----|------|

| CPEN (          | Output Pin                     |                         |                         |     |     |      |

| V <sub>OL</sub> | CPEN low-level output voltage  | I <sub>OL</sub> = 3 mA  |                         |     | 0.3 | V    |

| V <sub>OH</sub> | CPEN high-level output voltage | I <sub>OH</sub> = –3 mA | V <sub>DD33</sub> - 0.3 |     |     | V    |

# 6.6 Digital I/O Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

| PARAMETER       |                           | TEST CONDITIONS                  | MIN                      | TYP MAX | UNIT |

|-----------------|---------------------------|----------------------------------|--------------------------|---------|------|

| CLOCK           |                           |                                  |                          |         |      |

| V <sub>OL</sub> | Low-level output voltage  | Fraguerov 60 Mila Lood 10 pF     |                          | 0.45    | V    |

| V <sub>OH</sub> | High-level output voltage | Frequency = 60 MHz, Load = 10 pF | V <sub>DDIO</sub> - 0.45 |         | V    |

| STP, DIR        | R, NXT, DATA0 to DATA7    |                                  |                          |         |      |

| V <sub>OL</sub> | Low-level output voltage  | Fraguency 20 Mile Lood 10 pF     |                          | 0.45    |      |

| V <sub>OH</sub> | High-level output voltage | Frequency = 30 MHz, Load = 10 pF | V <sub>DDIO</sub> - 0.45 |         |      |

# 6.7 Digital IO Pins (Non-ULPI)

|                              | PARAMETER                           | TEST CONDITIONS | MIN                    | TYP MAX                       | UNIT |  |  |  |  |

|------------------------------|-------------------------------------|-----------------|------------------------|-------------------------------|------|--|--|--|--|

| CS, CFG, RESETB Input Pins   |                                     |                 |                        |                               |      |  |  |  |  |

| V <sub>IL</sub>              | Maximum low-level input voltage     |                 |                        | $0.35 \times V_{\text{DDIO}}$ | V    |  |  |  |  |

| VIH                          | Minimum high-level input voltage    |                 | $0.65 \times V_{DDIO}$ |                               | V    |  |  |  |  |

| RESETB Input Pin Timing Spec |                                     |                 |                        |                               |      |  |  |  |  |

| t <sub>w(POR)</sub>          | Internal power-on reset pulse width |                 | 0.2                    |                               | μs   |  |  |  |  |

SLLSEL4A - SEPTEMBER 2014 - REVISED OCTOBER 2014

www.ti.com

# Digital IO Pins (Non-ULPI) (continued)

over operating free-air temperature range (unless otherwise noted)

| PARAMETER      |                             | TEST CONDITIONS                                        | MIN | TYP MAX | UNIT            |

|----------------|-----------------------------|--------------------------------------------------------|-----|---------|-----------------|

| $t_{w(RESET)}$ | External RESETB pulse width | Applied to external RESETB pin when CLOCK is toggling. | 8   |         | CLOCK<br>cycles |

# 6.8 PHY Electrical Characteristics

|                      | PARAMETER                                           |                        | COMMENTS                                                    | MIN    | TYP MAX | UNIT |

|----------------------|-----------------------------------------------------|------------------------|-------------------------------------------------------------|--------|---------|------|

| LS/FS Single         | e-Ended Receivers                                   |                        |                                                             |        |         |      |

|                      | USB single-ended receivers                          |                        |                                                             |        |         |      |

| SK <sub>WVP_VM</sub> | Skew between VP and VM                              |                        | Driver outputs unloaded                                     | -2     | 0 2     | ns   |

| V <sub>SE_HYS</sub>  | Single-ended hysteresis                             |                        |                                                             | 50     |         | mV   |

| V <sub>IH</sub>      | High (driven)                                       |                        |                                                             | 2      |         | V    |

| V <sub>IL</sub>      | Low                                                 |                        |                                                             |        | 0.8     | V    |

| V <sub>TH</sub>      | Switching threshold                                 |                        |                                                             | 0.8    | 2       | V    |

| LS/FS Differ         | ential Receiver                                     |                        |                                                             |        |         |      |

| V <sub>DI</sub>      | Differential input sensitivity                      |                        | Ref. USB2.0                                                 | 200    |         | mV   |

| V <sub>CM</sub>      | Differential Common mode range                      |                        | Ref. USB2.0                                                 | 0.8    | 2.5     | V    |

| LS Transmit          | ter                                                 |                        |                                                             |        |         |      |

| V <sub>OL</sub>      | Low                                                 |                        | Ref. USB2.0                                                 | 0      | 300     | mV   |

| V <sub>OH</sub>      | High (driven)                                       |                        | Ref. USB2.0                                                 | 2.8    | 3.6     | V    |

| V <sub>CRS</sub>     | Output signal crossover voltage                     |                        | Ref. USB2.0, covered by eye diagram                         | 1.3    | 2       | V    |

| tr                   | Rise time                                           |                        | Ref. USB2.0, covered by eye diagram                         | 75     | 300     | ns   |

| t <sub>f</sub>       | Fall time                                           |                        |                                                             | 75     | 300     | ns   |

| t <sub>FRFM</sub>    | Differential rise and fall time matching            |                        |                                                             | 80%    | 125%    |      |

| t <sub>FDRATE</sub>  | Low-speed data rate                                 |                        | Ref. USB2.0, covered by eye diagram                         | 1.4775 | 1.5225  | Mb/s |

| t <sub>DJ1</sub>     |                                                     | To next transition     |                                                             | -25    | 25      |      |

| t <sub>DJ2</sub>     | Source jitter total (including frequency tolerance) | For paired transitions | <ul> <li>Ref. USB2.0, covered by eye<br/>diagram</li> </ul> | -10    | 10      | ns   |

| t <sub>FEOPT</sub>   | Source SE0 interval of EOP                          |                        | Ref. USB2.0, covered by eye diagram                         | 1.25   | 1.5     | μs   |

|                      | Downstream eye diagram                              |                        | Ref. USB2.0, covered by eye diagram                         |        |         |      |

| V <sub>CM</sub>      | Differential common mode range                      |                        | Ref. USB2.0                                                 | 0.8    | 2.5     | V    |

| FS Transmit          | ter                                                 |                        |                                                             |        |         |      |

| V <sub>OL</sub>      | Low                                                 |                        | Ref. USB2.0                                                 | 0      | 300     | mV   |

| V <sub>OH</sub>      | High (driven)                                       |                        | Ref. USB2.0                                                 | 2.8    | 3.6     | V    |

| VCRS                 | Output signal crossover voltage                     |                        | Ref. USB2.0, covered by eye diagram                         | 1.3    | 2       | V    |

| t <sub>FR</sub>      | Rise time                                           |                        | Ref. USB2.0                                                 | 4      | 20      | ns   |

| t <sub>FF</sub>      | Fall time                                           |                        | Ref. USB2.0                                                 | 4      | 20      | ns   |

| t <sub>FRFM</sub>    | Differential rise and fall time matching            |                        | Ref. USB2.0, covered by eye diagram                         | 90%    | 111.11% |      |

| Z <sub>DRV</sub>     | Driver output resistance                            |                        | Ref. USB2.0                                                 | 28     | 44      | Ω    |

| TFDRATE              | Full-speed data rate                                |                        | Ref. USB2.0, covered by eye diagram                         | 11.97  | 12.03   | Mb/s |

| t <sub>DJ1</sub>     | Course litter total /in-ludio - fram                | To next transition     | Def LICD2 0. environd human                                 | -2     | 2       |      |

| t <sub>DJ2</sub>     | Source jitter total (including frequency tolerance) | For paired transitions | Ref. USB2.0, covered by eye<br>diagram                      | -1     | 1       | ns   |

| TFEOPT               | Source SE0 interval of EOP                          |                        | Ref. USB2.0, covered by eye diagram                         | 160    | 175     | ns   |

|                      | Downstream eye diagram                              |                        | Ref. USB2.0, covered by eye diagram                         |        |         |      |

# **PHY Electrical Characteristics (continued)**

|                           | PARAMETER                                                                     | COMMENTS                                        | MIN    | TYP | MAX    | UNIT |

|---------------------------|-------------------------------------------------------------------------------|-------------------------------------------------|--------|-----|--------|------|

|                           | Upstream eye diagram                                                          |                                                 |        |     |        |      |

| HS Differentia            | I Receiver                                                                    | L L                                             |        |     |        |      |

| VHSSQ                     | High-speed squelch detection threshold (differential signal amplitude)        | Ref. USB2.0                                     | 100    |     | 150    | mV   |

| VHSDSC                    | High-speed disconnect detection threshold (differential signal amplitude)     | Ref. USB2.0                                     | 525    |     | 625    | mV   |

|                           | High-speed differential input signaling levels                                | Ref. USB2.0, specified by eye pattern templates |        |     |        | mV   |

| VHSCM                     | High-speed data signaling common mode voltage range (guidelines for receiver) | Ref. USB2.0                                     | -50    |     | 500    | mV   |

|                           | Receiver jitter tolerance                                                     | Ref. USB2.0, specified by eye pattern templates |        |     | 150    | ps   |

| HS Transmitte             | er                                                                            |                                                 |        |     |        |      |

| V <sub>HSOI</sub>         | High-speed idle level                                                         | Ref. USB2.0                                     | -10    |     | 10     | mV   |

| V <sub>HSOH</sub>         | High-speed data signaling high                                                | Ref. USB2.0                                     | 360    |     | 440    | mV   |

| V <sub>HSOL</sub>         | High-speed data signaling low                                                 | Ref. USB2.0                                     | -10    |     | 10     | mV   |

| VCHIRPJ                   | Chirp J level (differential voltage)                                          | Ref. USB2.0                                     | 700    |     | 1100   | mV   |

| VCHIRPK                   | Chirp K level (differential voltage)                                          | Ref. USB2.0                                     | -900   |     | -500   | mV   |

| t <sub>r</sub>            | Rise Time (10% - 90%)                                                         | Ref. USB2.0, covered by eye diagram             | 500    |     |        | ps   |

| t <sub>f</sub>            | Fall time (10% - 90%)                                                         | Ref. USB2.0, covered by eye diagram             | 500    |     |        | ps   |

| ZHSDRV                    | Driver output resistance (which also serves as high-speed termination)        | Ref. USB2.0                                     | 40.5   |     | 49.5   | Ω    |

| THSDRAT                   | High-speed data range                                                         | Ref. USB2.0, covered by eye diagram             | 479.76 | 4   | 480.24 | Mb/s |

|                           | Data source jitter                                                            | Ref. USB2.0, covered by eye diagram             |        |     |        |      |

|                           | Downstream eye diagram                                                        | Ref. USB2.0, covered by eye diagram             |        |     |        |      |

|                           | Upstream eye diagram                                                          | Ref. USB2.0, covered by eye diagram             |        |     |        |      |

| CEA-2011/UAI              | RT Transceiver                                                                |                                                 |        |     |        |      |

|                           | UART Transmitter CEA-2011                                                     |                                                 |        |     |        |      |

| t <sub>PH_UART_EDGE</sub> | Phone UART edge rates                                                         | DP_PULLDOWN asserted                            |        |     | 1      | Ms   |

| V <sub>OH_SER</sub>       | Serial interface output high                                                  | ISOURCE = 4 mA                                  | 2.4    | 3.3 | 3.6    | V    |

| V <sub>OL_SER</sub>       | Serial interface output low                                                   | ISINK = -4 mA                                   | 0      | 0.1 | 0.4    | V    |

|                           | UART Receiver CEA-2011                                                        |                                                 |        |     |        |      |

| VI <sub>H_SER</sub>       | Serial interface input high                                                   | DP_PULLDOWN asserted                            | 2      |     |        | V    |

| V <sub>IL_SER</sub>       | Serial interface input low                                                    | DP_PULLDOWN asserted                            |        |     | 0.8    | V    |

| V <sub>TH</sub>           | Switching threshold                                                           |                                                 | 0.8    |     | 2      | V    |

SLLSEL4A-SEPTEMBER 2014-REVISED OCTOBER 2014

TEXAS INSTRUMENTS

www.ti.com

# 6.9 Pullup/Pulldown Resistors

|                           | PARAMETER                                        | COMMENTS                                  | MIN   | TYP | MAX   | UNIT |

|---------------------------|--------------------------------------------------|-------------------------------------------|-------|-----|-------|------|

| RPUI                      | Bus pullup resistor on upstream port (idle bus)  | Bus idle                                  | 0.9   | 1.1 | 1.575 | kΩ   |

| RPUA                      | Bus pullup resistor on upstream port (receiving) | Bus driven/driver's outputs unloaded      | 1.425 | 2.2 | 3.09  |      |

| VIHZ                      | High (floating)                                  | Pullups/pulldowns on both DP and DM lines | 2.7   |     | 3.6   | V    |

| VPH_DP_UP                 | Phone D+ pullup voltage                          | Driver's outputs unloaded                 | 3     | 3.3 | 3.6   | V    |

|                           | Pulldown resistors                               |                                           |       |     |       |      |

| RPH_DP_DWN                | Phone D+/- pulldown                              | Driver's outputs unloaded                 | 14.25 | 18  | 24.8  | kΩ   |

| RPH_DM_DWN                |                                                  |                                           |       |     |       |      |

| V <sub>IHZ</sub>          | High (floating)                                  | Pullups/pulldowns on both DP and DM lines | 2.7   |     | 3.6   | V    |

|                           | D+/- Data line                                   |                                           |       |     |       |      |

| C <sub>INUB</sub>         | Upstream facing port                             | [1.0]                                     |       | 22  | 75    | pF   |

| V <sub>OTG_DATA_LKG</sub> | On-the-go device leakage                         | [2]                                       |       |     | 0.342 | V    |

| Z <sub>INP</sub>          | Input impedance exclusive of<br>pullup/pulldown  | Driver's outputs unloaded                 | 300   |     |       | kΩ   |

# 6.10 OTG Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                              | PARAMETER                                                                     | COM                                                                   | MENTS                                                      | MIN   | TYP | MAX   | UNIT |

|------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------|-------|-----|-------|------|

| 0                            | TG V <sub>BUS</sub> Electrical                                                |                                                                       |                                                            |       |     |       |      |

| V <sub>BUS</sub> Comparato   | rs                                                                            |                                                                       |                                                            |       |     |       |      |

| VA_SESS_VLD                  | A-device session valid                                                        |                                                                       |                                                            | 0.8   | 1.4 | 2.0   | V    |

| VA_VBUS_VLD                  | A-device V <sub>BUS</sub> valid                                               |                                                                       |                                                            | 4.4   | 4.5 | 4.625 | V    |

| VB_SESS_END                  | B-device session end                                                          |                                                                       |                                                            | 0.2   | 0.5 | 0.8   | V    |

| VB_SESS_VLD                  | B-device session valid                                                        |                                                                       |                                                            | 2.1   | 2.4 | 2.7   | V    |

| V <sub>BUS</sub> Line        |                                                                               | •                                                                     | •                                                          |       |     |       |      |

| RA_BUS_IN                    | A-device $V_{\text{BUS}}$ input impedance to ground                           | SRP (V <sub>BUS</sub> pulsing) capable A-device not driving $V_{BUS}$ |                                                            | 40    | 70  | 100   | kΩ   |

| RB_SRP_DWN                   | B-device V <sub>BUS</sub> SRP pulldown                                        | 5.25 V / 8 mA, Pullup vo                                              | 0.656                                                      | 10    |     | kΩ    |      |

| RB_SRP_UP                    | B-device V <sub>BUS</sub> SRP pullup                                          | (5.25 V – 3 V) / 8 mA, P                                              | ullup voltage = 3 V                                        | 0.281 | 1   | 2     | kΩ   |

|                              | B-device V <sub>BUS</sub> SRP rise time<br>maximum for OTG-A<br>communication |                                                                       | $RV_{BUS} = 0 \Omega$<br>and R1KSERIES = '0'               |       |     | 31.4  |      |

| •                            |                                                                               | 0 to 2.1 V with < 13 μF<br>load                                       | $RV_{BUS}$ = 1000 $\Omega$ ±10% and R1KSERIES = '1'        |       |     | 57.8  |      |

| <sup>t</sup> RISE_SRP_UP_MAX |                                                                               |                                                                       | $RV_{BUS}$ = 1200 $\Omega$ ±10% and R1KSERIES = '1'        |       |     | 64    | ms   |

|                              |                                                                               |                                                                       | $RV_{BUS}$ = 1800 $\Omega$ ±10% and R1KSERIES = '1'        |       |     | 85.4  |      |

|                              |                                                                               |                                                                       | $RV_{BUS} = 0 \Omega$<br>and R1KSERIES = '0'               | 46.2  |     |       |      |

|                              | B-device V <sub>BUS</sub> SRP rise time                                       | 0.8 to 2 V with > 97 μF                                               | $RV_{BUS}$ = 1000 $\Omega$ ±10% and R1KSERIES = '1'        | 96    |     |       |      |

| <sup>t</sup> RISE_SRP_UP_MIN | minimum for standard host connection                                          | load                                                                  | $RV_{BUS}$ = 1200 $\Omega$ ±10% and R1KSERIES = '1'        | 100   |     |       | ms   |

|                              |                                                                               |                                                                       | $RV_{BUS} = 1800 \ \Omega \pm 10\%$<br>and R1KSERIES = '1' | 100   |     |       |      |

# Table 1. OTG ID Electrical

|                                                       | PARAMETER                    | COMMENTS                         | MIN | TYP | MAX  | UNIT |  |  |  |

|-------------------------------------------------------|------------------------------|----------------------------------|-----|-----|------|------|--|--|--|

| ID Comparators — ID External Resistors Specifications |                              |                                  |     |     |      |      |  |  |  |

| R <sub>ID_GND</sub>                                   | ID ground comparator         | ID_GND interrupt                 | 12  | 20  | 28   | kΩ   |  |  |  |

| R <sub>ID_FLOAT</sub>                                 | ID Float comparator          | ID_FLOAT interrupt               | 200 |     | 500  | kΩ   |  |  |  |

|                                                       | ID Line                      |                                  |     |     |      |      |  |  |  |

| R <sub>PH_ID_UP</sub>                                 | Phone ID pullup to VPH_ID_UP | ID unloaded (V <sub>RUSB</sub> ) | 70  | 90  | 286  | kΩ   |  |  |  |

| VP <sub>H_ID_UP</sub>                                 | Phone ID pullup voltage      | Connected to V <sub>RUSB</sub>   | 2.5 |     | 3.2  | V    |  |  |  |

|                                                       | ID line maximum voltage      |                                  |     |     | 5.25 | V    |  |  |  |

SLLSEL4A - SEPTEMBER 2014 - REVISED OCTOBER 2014

www.ti.com

ISTRUMENTS

ÈXAS

# 6.11 Power Characteristics

over operating free-air temperature range (unless otherwise noted)

|                         | PARAMETER                 |                      | TEST CONDITIONS                                     | MIN                          | TYP  | MAX  | UNIT  |  |

|-------------------------|---------------------------|----------------------|-----------------------------------------------------|------------------------------|------|------|-------|--|

| V <sub>DD33</sub> Inter | rnal LDO Regulator Charac | cteristics           |                                                     |                              |      |      |       |  |

| V <sub>INVDD33</sub>    | Input voltage             | V <sub>BAT</sub> USB |                                                     | V <sub>VDD33</sub> typ + 0.2 | 3.6  | 4.5  | V     |  |

|                         |                           |                      | VUSB3V3_VSEL = '000                                 | 2.4                          | 2.5  | 2.6  |       |  |

|                         |                           |                      | VUSB3V3_VSEL = '001                                 | 2.65                         | 2.75 | 2.85 |       |  |

| V <sub>VDD33</sub>      |                           |                      | VUSB3V3_VSEL = '010                                 | 2.9                          | 3.0  | 3.1  |       |  |

|                         | Output voltage            | ON mode              | VUSB3V3_VSEL = '011 (default)                       | 3.0                          | 3.1  | 3.2  | V     |  |

|                         |                           | ON mode,             | VUSB3V3_VSEL = '100                                 | 3.1                          | 3.2  | 3.3  | • • • |  |

|                         |                           |                      | VUSB3V3_VSEL = '101                                 | 3.2                          | 3.3  | 3.4  |       |  |

|                         |                           |                      | VUSB3V3_VSEL = '110                                 | 3.3                          | 3.4  | 3.5  |       |  |

|                         |                           |                      | VUSB3V3_VSEL = '111                                 | 3.4                          | 3.5  | 3.6  |       |  |

|                         | Detail and a summer t     | V 1105               | Active mode                                         |                              |      | 15   |       |  |

| VDD33                   | Rated output current      | V <sub>BAT</sub> USB | Suspend/reset mode                                  |                              |      | 1    | mA    |  |

| V <sub>DD15</sub> Inter | rnal LDO Regulator Charac | cteristics           |                                                     |                              |      |      |       |  |

| VIN VDD15               | Input voltage             |                      | On mode, V <sub>IN VDD15</sub> = V <sub>BAT</sub>   | 2.7                          | 3.6  | 4.5  | V     |  |

| V <sub>VDD15</sub>      | Output voltage            |                      | V <sub>INVDD15</sub> min - V <sub>INVDD15</sub> max | 1.45                         | 1.56 | 1.65 | V     |  |

| I <sub>VDD15</sub>      | Rated output current      |                      | On mode                                             |                              |      | 30   | mA    |  |

# 6.12 Switching Characteristics

|                     | PARAMETER                            | TEST CONDITIONS                                        | MIN | TYP  | MAX | UNIT   |

|---------------------|--------------------------------------|--------------------------------------------------------|-----|------|-----|--------|

| Electrica           | I Characteristics: Clock Input       |                                                        |     |      |     |        |

|                     | Clock input duty cycle               |                                                        | 40  |      | 60% |        |

| f <sub>CLK</sub>    | Clock nominal frequency              |                                                        |     | 60   |     | MHz    |

|                     | Clock input rise/fall time           | In % of clock period $t_{CLK}$ ( = 1/ $f_{CLK}$ )      |     |      | 10% |        |

|                     | Clock input frequency accuracy       |                                                        |     |      | 250 | ppm    |

|                     | Clock input integrated jitter        |                                                        |     |      | 600 | ps rms |

| Electrica           | al Characteristics: REFCLK           |                                                        |     |      |     |        |

|                     | REFCLK input duty cycle              |                                                        | 40  |      | 60% |        |

| ,                   |                                      | When CFG pin is tied to GND                            |     | 19.2 |     | MHz    |

| f <sub>REFCLK</sub> | REFCLK nominal frequency             | When CFG pin is tied to V <sub>DDIO</sub>              |     | 26   |     | IVITIZ |

|                     | REFCLK input rise/fall time          | In % of clock period $t_{REFCLK}$ ( = $1/f_{REFCLK}$ ) |     |      | 20% |        |

|                     | REFCLK input frequency accuracy      |                                                        |     |      | 250 | ppm    |

|                     | REFCLK input integrated jitter       |                                                        |     |      | 600 | ps rms |

|                     | REFCLK HIZ Leakage current           |                                                        |     |      | 3   | ۵      |

|                     | REFCLK HIZ Leakage current           |                                                        | -3  |      |     | μA     |

| Digital IC          | D Electrical Characteristics: CLOCK  |                                                        |     |      |     |        |

| t <sub>r</sub>      | Rise time                            | Frequency = 60 MHz, Load = 10 pF                       |     |      | 1   | ns     |

| t <sub>f</sub>      | Fall time                            | Frequency = 30 MHz, Load = 10 pF                       |     |      | 1   | ns     |

| Digital IC          | D Electrical Characteristics: STP, D | IR, NXT, DATA0 to DATA7                                |     |      |     |        |

| t <sub>r</sub>      | Rise time                            | Frequency 20 Mile Lord 40 rF                           |     |      | 1   | ns     |

| t <sub>f</sub>      | Fall time                            | Frequency = 30 MHz, Load = 10 pF                       |     |      | 1   | ns     |

# 6.13 Timing Requirements

|                                   | PARAMETER                                  | INPUT CLC | INPUT CLOCK |     | оск | UNIT |  |  |  |  |

|-----------------------------------|--------------------------------------------|-----------|-------------|-----|-----|------|--|--|--|--|

|                                   | PARAMETER                                  | MIN       | MAX         | MIN | MAX | UNIT |  |  |  |  |

| ULPI Interface Timing             |                                            |           |             |     |     |      |  |  |  |  |

| t <sub>SC</sub> , t <sub>SD</sub> | Set-up time (control in, 8-bit data in)    |           | 3           |     | 6   | ns   |  |  |  |  |

| t <sub>SC</sub> , t <sub>HD</sub> | Hold time (control in, 8-bit data in)      | 1.5       |             | 0   |     | ns   |  |  |  |  |

| t <sub>DC</sub> , t <sub>DD</sub> | Output delay (control out, 8-bit data out) |           | 6           |     | 9   | ns   |  |  |  |  |

| USB UART Int                      | terface Timing                             |           |             |     |     |      |  |  |  |  |

| t <sub>PH_DP_CON</sub>            | Phone D+ connect time                      | 100       |             |     |     | ms   |  |  |  |  |

| t <sub>PH_DISC_DET</sub>          | Phone D+ disconnect time                   | 150       |             |     |     | ms   |  |  |  |  |

| f <sub>UART_DFLT</sub>            | Default UART signaling rate (typical rate) |           | 9600        |     |     | bps  |  |  |  |  |

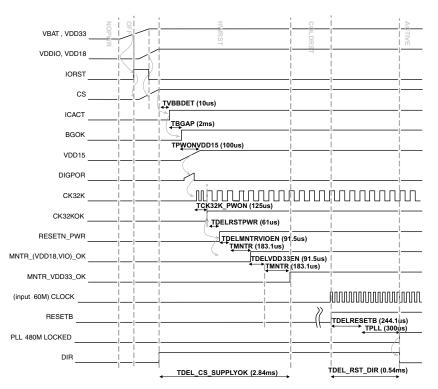

Figure 1. TUSB1210-Q1 Power-Up Timing (ULPI Clock Input Mode)

| Table | 2. | Timers | and | Debounce |

|-------|----|--------|-----|----------|

|-------|----|--------|-----|----------|

|                              | PARAMETER                                               | COMMENTS | MIN | TYP   | MAX   | UNIT |

|------------------------------|---------------------------------------------------------|----------|-----|-------|-------|------|

| t <sub>DEL_CS_SUPPLYOK</sub> | Chip-select-to-supplies OK delay                        |          |     | 2.84  | 4.10  | ms   |

| t <sub>DEL_RST_DIR</sub>     | RESETB to PHY PLL locked and DIR falling-<br>edge delay |          |     | 0.54  | 0.647 | ms   |

| t <sub>VBBDET</sub>          | V <sub>BAT</sub> detection delay                        |          |     | 10    |       | μs   |

| t <sub>BGAP</sub>            | Bandgap power-on delay                                  |          |     | 2     |       | ms   |

| t <sub>PWONVDD15</sub>       | V <sub>DD15</sub> power-on delay                        |          |     | 100   |       | μs   |

| t <sub>PWONCK32K</sub>       | 32-KHz RC-OSC power-on delay                            |          |     | 125   |       | μs   |

| t <sub>DELRSTPWR</sub>       | Power control reset delay                               |          |     | 61    |       | μs   |

| t <sub>DELMNTRVIOEN</sub>    | Monitor enable delay                                    |          |     | 91.5  |       | μs   |

| t <sub>MNTR</sub>            | Supply monitoring debounce                              |          |     | 183.1 |       | μs   |

| t <sub>DELVDD33EN</sub>      | V <sub>DD33</sub> LDO enable delay                      |          |     | 93.75 |       | μs   |

| t <sub>DELRESETB</sub>       | RESETB internal delay                                   |          |     | 244.1 |       | μs   |

| t <sub>PLL</sub>             | PLL lock time                                           |          |     | 300   |       | μs   |

Copyright © 2014, Texas Instruments Incorporated

SLLSEL4A-SEPTEMBER 2014-REVISED OCTOBER 2014

### 6.13.1 Timing Parameter Definitions

The timing parameter symbols used in the timing requirement and switching characteristic tables are created in accordance with JEDEC Standard 100. To shorten the symbols, some pin names and other related terminologies have been abbreviated as shown in Table 3.

| LOWERCASE SUBSCRIPTS |                                        |  |  |  |  |  |

|----------------------|----------------------------------------|--|--|--|--|--|

| SYMBOL               | PARAMETER                              |  |  |  |  |  |

| С                    | Cycle time (period)                    |  |  |  |  |  |

| D                    | Delay time                             |  |  |  |  |  |

| Dis                  | Disable time                           |  |  |  |  |  |

| En                   | Enable time                            |  |  |  |  |  |

| Н                    | Hold time                              |  |  |  |  |  |

| Su                   | Setup time                             |  |  |  |  |  |

| START                | Start bit                              |  |  |  |  |  |

| Т                    | Transition time                        |  |  |  |  |  |

| V                    | Valid time                             |  |  |  |  |  |

| W                    | Pulse duration (width)                 |  |  |  |  |  |

| Х                    | Unknown, changing, or don't care level |  |  |  |  |  |

| н                    | High                                   |  |  |  |  |  |

| L                    | Low                                    |  |  |  |  |  |

| V                    | Valid                                  |  |  |  |  |  |

| IV                   | Invalid                                |  |  |  |  |  |

| AE                   | Active edge                            |  |  |  |  |  |

| FE                   | First edge                             |  |  |  |  |  |

| LE                   | Last edge                              |  |  |  |  |  |

| Z                    | High impedance                         |  |  |  |  |  |

### **Table 3. Timing Parameter Definitions**

### 6.13.2 Interface Target Frequencies

Table 4 assumes testing over the recommended operating conditions.

| IO<br>INTERFACE | INTERFACE            | E DESIGNATION | TARGET FREQUENCY<br>1.5 V |

|-----------------|----------------------|---------------|---------------------------|

|                 |                      | High speed    | 480 Mbits/s               |

| USB             | Universal serial bus | Full speed    | 12 Mbits/s                |

|                 |                      | Low speed     | 1.5 Mbits/s               |

# 6.14 Typical Characteristics

TEXAS INSTRUMENTS

www.ti.com

# 7 Detailed Description

### 7.1 Overview

The TUSB1210-Q1 is a USB2.0 transceiver chip, designed to interface with a USB controller via a ULPI interface. It supports all USB2.0 data rates High-Speed, Full-Speed, and Low-Speed. Compliant to both Host and Peripheral (OTG) modes. It additionally supports a UART mode and legacy ULPI serial modes. TUSB1210-Q1 Integrates a 3.3-V LDO, which makes it flexible to work with either battery operated systems or pure 3.3 V supplied systems. Also, it has an integrated PLL Supporting 2 Clock Frequencies 19.2 MHz/26 MHz. The ULPI clock pin (60 MHz) supports both input and output clock configurations. TUSB1210-Q1 has low power consumption, optimized for portable devices, and complete USB OTG Physical Front-End that supports Host Negotiation Protocol (HNP) and Session Request Protocol (SRP).

TUSB1210-Q1 is optimized to be interfaced through a 12-pin SDR UTMI Low Pin Interface (ULPI), supporting both input clock and output clock modes, with 1.8 V interface supply voltage.

TUSB1210-Q1 integrates a 3.3 V LDO, which makes it flexible to work with either battery operated systems or pure 3.3 V supplied systems. Both the main supply and the 3.3 V power domain can be supplied through an external switched-mode converter for optimized power efficiency.

TUSB1210-Q1 includes a POR circuit to detect supply presence on  $V_{BAT}$  and  $V_{DDIO}$  pins. TUSB1210-Q1 can be disabled or configured in low power mode for energy saving.

TUSB1210-Q1 is protected against accidental shorts to 5 V or ground on its exposed interface (DP/DM/ID). It is also protected against up to 20 V surges on  $V_{BUS}$ .

TUSB1210-Q1 integrates a high-performance low-jitter 480 MHz PLL and supports two clock configurations. Depending on the required link configuration, TUSB1210-Q1 supports both ULPI input and output clock mode : input clock mode, in which case a square-wave 60 MHz clock is provided to TUSB1210-Q1 at the ULPI interface CLOCK pin; and output clock mode in which case TUSB1210-Q1 can accept a square-wave reference clock at REFCLK of either 19.2 MHz, 26 MHz. Frequency is indicated to TUSB1210-Q1 via the configuration pin CFG. This can be useful if a reference clock is already available in the system.

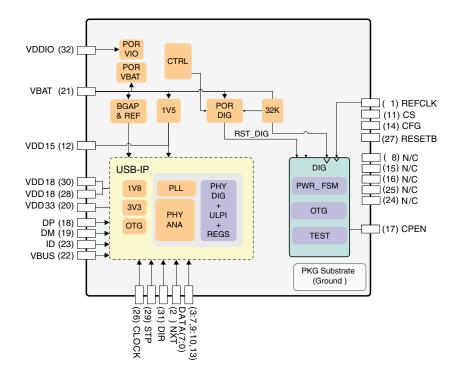

# 7.2 Functional Block Diagram

### 7.3 Feature Description

### 7.3.1 Processor Subsystem

### 7.3.1.1 Clock Specifications

### 7.3.1.1.1 USB PLL Reference Clock

The USB PLL block generates the clocks used to synchronize :

- the ULPI interface (60 MHz clock)

- the USB interface (depending on the USB data rate, 480 Mbps, 12 Mbps or 1.5 Mbps)

TUSB1210-Q1 requires an external reference clock which is used as an input to the 480 MHz USB PLL block. Depending on the clock configuration, this reference clock can be provided either at REFCLK pin or at CLOCK pin. By default CLK pin is configured as an input.

Two clock configurations are possible:

- Input clock configuration (see ULPI Input Clock Configuration)

- Output clock configuration (see ULPI Output Clock Configuration)

### 7.3.1.1.2 ULPI Input Clock Configuration

In this mode REFCLK must be externally tied to GND. CLOCK remains configured as an input.

When the ULPI interface is used in input clock configuration, that is, the 60 MHz ULPI clock is provided to TUSB1210-Q1 on Clock pin, then this is used as the reference clock for the 480 MHz USB PLL block. See *Switching Characteristics*.

#### 7.3.1.1.3 ULPI Output Clock Configuration

In this mode a reference clock must be externally provided on REFCLK pin When an input clock is detected on REFCLK pin then CLK will automatically change to an output, i.e., 60 MHz ULPI clock is output by TUSB1210-Q1 on CLK pin.

Two reference clock input frequencies are supported. REFCLK input frequency is communicated to TUSB1210-Q1 via a configuration pin, CFG, see  $f_{REFCLK}$  in Table 11 for frequency correspondence. TUSB1210-Q1 supports square-wave reference clock input only. Reference clock input must be square-wave of amplitude in the range 3 V to 3.6 V. See *Switching Characteristics*.

### 7.3.1.1.4 Clock 32 kHz

An internal clock generator running at 32 kHz has been implemented to provide a low-speed, low-power clock to the system See *Clock 32 kHz*

#### 7.3.1.1.5 Reset

All logic is reset if CS = 0 or  $V_{BAT}$  are not present.

All logic (except 32 kHz logic) is reset if V<sub>DDIO</sub> is not present.

PHY logic is reset when any supplies are not present (V<sub>DDI0</sub>, V<sub>DD15</sub>, V<sub>DD18</sub>, V<sub>DD33</sub>) or if RESETB pin is low.

TUSB1210-Q1 may be reset manually by toggling the RESETB pin to GND for at lease 200 ns.

If manual reset via RESETB is not required then RESETB pin may be tied to V<sub>DDIO</sub> permanently.

### 7.3.1.2 USB Transceiver

The TUSB1210-Q1 device includes a universal serial bus (USB) on-the-go (OTG) transceiver that supports USB 480 Mb/s high-speed (HS), 12 Mb/s full-speed (FS), and USB 1.5 Mb/s low-speed (LS) through a 12-pin UTMI+ low pin interface (ULPI).

### Feature Description (continued)

# NOTE

LS device mode is not allowed by a USB2.0 HS capable PHY, therefore it is not supported by TUSB1210-Q1. This is stated in USB2.0 standard Chapter 7, page 119, second paragraph: "*A high-speed capable upstream facing transceiver must not support low-speed signaling mode..*" There is also some related commentary in Chapter 7.1.2.3.

### 7.3.1.2.1 PHY Electrical Characteristics

The PHY is the physical signaling layer of the USB 2.0. It essentially contains all the drivers and receivers required for physical data and protocol signaling on the DP and DM lines.

The PHY interfaces to the USB controller through a standard 12-pin digital interface called UTMI+ low pin interface (ULPI).

The transmitters and receivers inside the PHY are classified into two main classes.

- The full-speed (FS) and low-speed (LS) transceivers. These are the legacy USB1.x transceivers.

- The HS (HS) transceivers

In order to bias the transistors and run the logic, the PHY also contains reference generation circuitry which consists of:

- A DPLL which does a frequency multiplication to achieve the 480-MHz low-jitter lock necessary for USB and also the clock required for the switched capacitor resistance block.

- A switched capacitor resistance block which is used to replicate an external resistor on chip.

Built-in pullup and pulldown resistors are used as part of the protocol signaling.

Apart from this, the PHY also contains circuitry which protects it from accidental 5-V short on the DP and DM lines.

### 7.3.1.2.1.1 LS/FS Single-Ended Receivers

In addition to the differential receiver, there is a single-ended receiver (SE–, SE+) for each of the two data lines D+/–. The main purpose of the single-ended receivers is to qualify the D+ and D– signals in the full-speed/low-speed modes of operation. See *PHY Electrical Characteristics*.

#### 7.3.1.2.1.2 LS/FS Differential Receiver

A differential input receiver (Rx) retrieves the LS/FS differential data signaling. The differential voltage on the line is converted into digital data by a differential comparator on DP/DM. This data is then sent to a clock and data recovery circuit which recovers the clock from the data. An additional serial mode exists in which the differential data is directly output on the RXRCV pin. See *Switching Characteristics*.

#### 7.3.1.2.1.3 LS/FS Transmitter

The USB transceiver (Tx) uses a differential output driver to drive the USB data signal D+/– onto the USB cable. The driver's outputs support 3-state operation to achieve bidirectional half-duplex transactions. See *Switching Characteristics*.

### 7.3.1.2.1.4 HS Differential Receiver

The HS receiver consists of the following blocks:

A differential input comparator to receive the serial data

- A squelch detector to qualify the received data

- An oversampler-based clock data recovery scheme followed by a NRZI decoder, bit unstuffing, and serial-toparallel converter to generate the ULPI DATAOUT See Switching Characteristics.

#### Feature Description (continued)

### 7.3.1.2.1.5 HS Differential Transmitter

The HS transmitter is always operated via the ULPI parallel interface. The parallel data on the interface is serialized, bit stuffed, NRZI encoded, and transmitted as a dc output current on DP or DM depending on the data. Each line has an effective  $22.5-\Omega$  load to ground, which generates the voltage levels for signaling.

A disconnect detector is also part of the HS transmitter. A disconnect on the far end of the cable causes the impedance seen by the transmitter to double thereby doubling the differential amplitude seen on the DP/DM lines of *Switching Characteristics*.

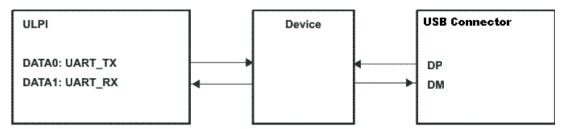

#### 7.3.1.2.1.6 UART Transceiver

In this mode, the ULPI data bus is redefined as a 2-pin UART interface, which exchanges data through a direct access to the FS/LS analog transmitter and receiver. See *Switching Characteristics*.

Figure 4. USB UART Data Flow

### 7.3.1.2.2 OTG Characteristics

The on-the-go (OTG) block integrates three main functions:

- The USB plug detection function on V<sub>BUS</sub> and ID

- The ID resistor detection

- The V<sub>BUS</sub> level detection

See OTG Electrical Characteristics.

# 7.4 Device Functional Modes

### 7.4.1 TUSB1210-Q1 Modes vs ULPI Pin Status

Table 5, Table 6, and Table 7 show the status of each of the 12 ULPI pins including input/output direction and whether output pins are driven to '0' or to '1', or pulled up/pulled down via internal pullup/pulldown resistors.

Note that pullup/pulldown resistors are automatically replaced by driven '1'/'0' levels respectively once internal IORST is released, with the exception of the pullup on STP which is maintained in all modes.

Pin assignment changes in ULPI 3-pin serial mode, ULPI 6-pin serial mode, and UART mode. Unused pins are tied low in these modes as shown below.

|            |          |            | ULPI SYNCHRONOUS MODE POWER-UP |          |          |                |       |             |       |  |  |  |

|------------|----------|------------|--------------------------------|----------|----------|----------------|-------|-------------|-------|--|--|--|

|            |          | UNTIL IORS | PLL O                          | FF       | PLL ON + | STP HIGH PLL O |       | N + STP LOW |       |  |  |  |

| PIN<br>NO. | PIN NAME | DIR        | PU/PD                          | DIR      | PU/PD    | DIR            | PU/PD | DIR         | PU/PD |  |  |  |

| 26         | CLOCK    | Hiz        | PD                             | I        | PD       | IO             | -     | IO          | -     |  |  |  |

| 31         | DIR      | Hiz        | PU                             | O, ('1') | -        | O, ('0')       | -     | 0           | -     |  |  |  |

| 2          | NXT      | Hiz        | PD                             | O, ('0') | -        | O, ('0')       | -     | 0           | -     |  |  |  |

| 29         | STP      | Hiz        | PU                             | I        | PU       | I              | PU    | I           | PU    |  |  |  |

| 3          | DATA0    | Hiz        | PD                             | O, ('0') | -        | I              | PD    | 10          | -     |  |  |  |

| 4          | DATA1    | Hiz        | PD                             | O, ('0') | -        | I              | PD    | Ю           | -     |  |  |  |

| 5          | DATA2    | Hiz        | PD                             | O, ('0') | -        | I              | PD    | Ю           | -     |  |  |  |

| 6          | DATA3    | Hiz        | PD                             | O, ('0') | -        | I              | PD    | Ю           | -     |  |  |  |

| 7          | DATA4    | Hiz        | PD                             | O, ('0') | -        | I              | PD    | 10          | -     |  |  |  |

| 9          | DATA5    | Hiz        | PD                             | O, ('0') | -        | I              | PD    | IO          | -     |  |  |  |

| 10         | DATA6    | Hiz        | PD                             | O, ('0') | -        | I              | PD    | Ю           | -     |  |  |  |

| 13         | DATA7    | Hiz        | PD                             | O, ('0') | -        | I              | PD    | ю           | -     |  |  |  |

Table 5. TUSB1210-Q1 Modes vs ULPI Pin Status:ULPI Synchronous Mode Power-Up

### Table 6. TUSB1210-Q1 Modes vs ULPI Pin Status: USB Suspend Mode

|         |          | SUSPEND         | MODE              | LINK / EXTERNAL RECOMMENDED SETTING DURING<br>SUSPEND MODE |       |  |  |

|---------|----------|-----------------|-------------------|------------------------------------------------------------|-------|--|--|

| PIN NO. | PIN NAME | DIR             | PU/PD             | DIR                                                        | PU/PD |  |  |

| 26      | CLOCK    | I               | -                 | 0                                                          | -     |  |  |

| 31      | DIR      | O, ('1')        | -                 | I                                                          | -     |  |  |

| 2       | NXT      | O, ('0')        | -                 | I                                                          | -     |  |  |

| 29      | STP      | I               | PU <sup>(1)</sup> | O, ('0')                                                   | -     |  |  |