# **ADC081000**

ADC081000 High Performance, Low Power 8-Bit, 1 GSPS A/D Converter

Literature Number: JAJSA49

National Semiconductor 2007年10月

### ADC081000

高性能、低消費電力、8 ビット、1GSPS A/D コンバータ

### 概要

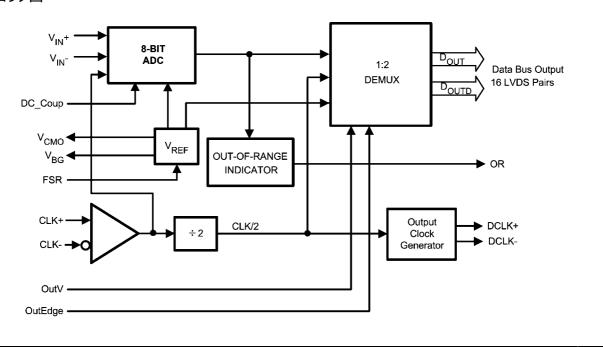

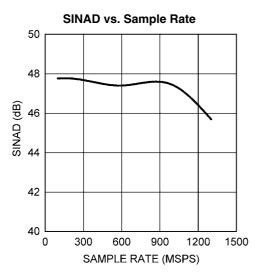

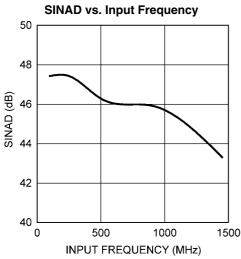

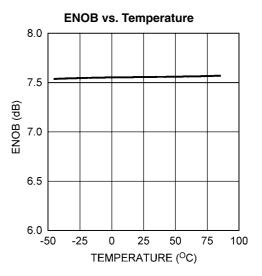

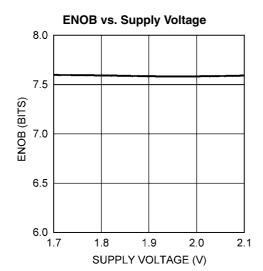

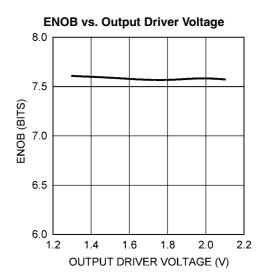

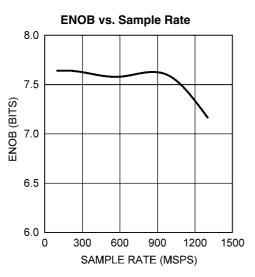

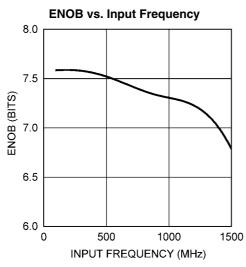

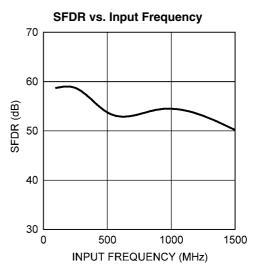

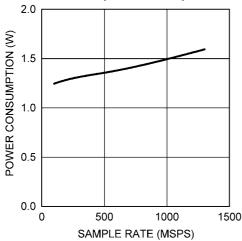

ADC081000 は、最高サンプリング・レート 1.6 GSPS にてアナロ グ信号を分解能 8 ビットでデジタイズできる、低消費電力かつ高 性能な CMOS A/D コンバータです。1.9V の単一電源で 1GSPS 動作時に代表値で 1.4W を消費する ADC081000 は、全動作温 度範囲にわたってミッシング・コードを生じないことが保証されてい ます。独自のセルフキャリプレーション・フォールディング・アーキテ クチャ、完全な差動コンパレータ設計、画期的な内部サンプル・ アンド・ホールド・アンプ回路、さらには自己較正方式の採用に よって、すべてのダイナミック・パラメータはナイキスト周波数を上 回る周波数帯まで平坦な応答を示し、入力信号が 500MHz でサ ンプリング周波数が 1GHz のときに 7.5ENOB を達成しています。 出力フォーマットはオフセット・バイナリ形式です。 LVDS デジタル 出力は、同相電圧(オフセット電圧)を0.8Vに下げている点を除 いて、IEEE1596.3-1996と互換性があります。

このコンバータは 2 組の LVDS バスを出力する 1:2 のデマルチプ レクサを備え、それぞれのバスのデータ・レートをサンプリング・ レートの半分に抑えています。2組のコンバータ回路をインタリーブ 構成にすることでバスあたりのデータ・レートは 500MHz になり、出 力を組み合わせることで 1GSPS が達成されます。

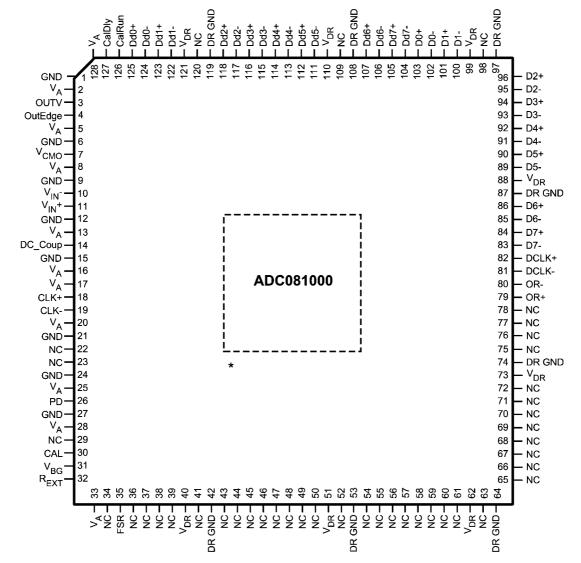

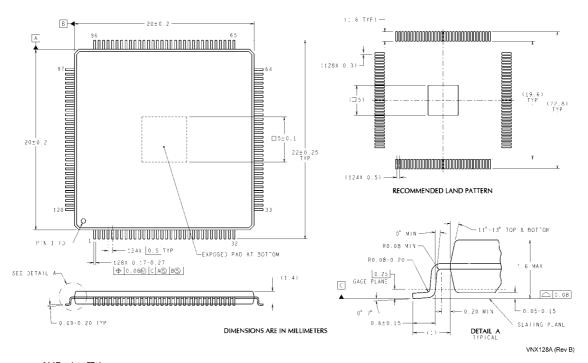

コンバータの消費電力はパワーダウン・モード時に代表値で 10mW 未満です。 熱特性を高めた 128 ピンの露出パッド LOFP で供給され、工業温度範囲(-40 T<sub>A</sub> + 85 )で動作 します。

### 特長

サンプル/ホールド機能内蔵 単一+ 1.9V ± 0.1V 電源動作 出力レベル切り換え機能 ノーミッシング・コード保証 低消費スタンバイ・モード

### 主な仕様

8ビット 分解能 最大変換レート 1GSPS (min) 有効ビット (ENOB) 500MHz 入力時 7.5 ビット (typ)  $\pm$  0.25 LSB (typ) 变換遅延時間 7 および 8 クロック

消費電力

- 動作時 1.45W (typ) - パワーダウン・モード 9mW (typ)

### アプリケーション

RF のダイレクトダウン・コンバージョン デジタル・オシロスコープ セットトップ・ボックス 通信システム 試験測定機器

### ブロック図

### 製品情報

| Extended Commercial Temperature Range (-40°C < T <sub>A</sub> < +85°C) | NS Package               |

|------------------------------------------------------------------------|--------------------------|

| ADC081000CIYB                                                          | 128-Pin Exposed Pad LQFP |

| ADC081000EVAL                                                          | Evaluation Board         |

| ADC08D1000DEV (use <i>Dual</i> product)                                | Development Board        |

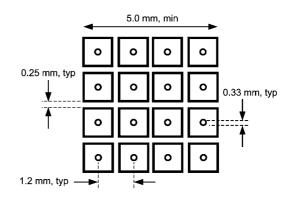

### ピン配置図

## ピン説明および等価回路

| 機能説明     |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                   |

|----------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ピン番号     | シンボル                        | 等価回路                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 説明                                                                                                                                                                                                                |

| 3        | OutV                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 出力電圧振幅の選択。通常の差動出力振幅を得るにはこの<br>ピンを High に接続します。振幅を小さくして同時に消費電力を<br>抑えるには、このピンをグラウンドに接続します。 セクション 1.5<br>を参照してください。                                                                                                 |

| 4        | OutEdge                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 出力エッジの選択。出力データ信号が切り換わる DCLK + (82 ピン ) のエッジを設定します。このピンを High にすると出力は DCLK + の立ち上がりエッジで遷移し、Low にすると立ち下がリフェッジで遷移します。 セクション 5.3 を参照してください。                                                                           |

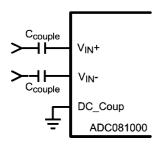

| 14       | DC_Coup                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DC 結合の選択。このピンを High にするとアナログ入力 $V_{\rm IN}$ + と $V_{\rm IN}$ - は DC 結合となり、 $V_{\rm CMO}(7$ ピン ) 出力電圧と等しい入力同相を与えなければなりません。このピンを Low にするとアナログ入力は内部でバイアスされ、入力信号を AC 結合によってアナログ入力に与えなければなりません。 セクション $3.0$ を参照してください。 |

| 26       | PD                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | パワーダウン・ピン。このピンを High にすると A/D コンバータはパワーダウン・モードに移行します。このピンを Low にすると通常動作になります。                                                                                                                                     |

| 30       | CAL                         | <b>b</b><br>GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 較正機能。このピンを10クロック以上 Lowにしたあと続けて10クロック以上 High にすると自己較正シーケンスが始まります。セクション1.1を参照してください。                                                                                                                                |

| 35       | FSR                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | フルスケール・レンジの選択。このピンを Low にするとフルスケール差動入力は $600 \mathrm{mV_{P-P}}$ になます。このピンを High にするとフルスケール差動入力は $800 \mathrm{mV_{P-P}}$ になます。 セクション $1.3$ を参照してください。                                                              |

| 127      | CalDly                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 較正遅延。パワーアップ後、較正を開始するまでのクロック・サイクル数を設定します。 セクション 1.1 を参照してください。                                                                                                                                                     |

| 18<br>19 | CLK+<br>CLK-                | 18 Solve Value Val | A/D コンバータのクロック入力ピン。 差動クロックを AC 結合して<br>このピンに与えてください。 入力信号は CLK +の立ち下がり<br>エッジでサンプリングされます。                                                                                                                         |

| 11<br>10 | $ m V_{IN}^+$ $ m V_{IN}^-$ | AGND  AGND  Control from DC_Coup  AGND  AGND  AGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | A/D コンバータのアナログ信号差動入力です。                                                                                                                                                                                           |

## ピン説明および等価回路(つづき)

## 機能説明 ピン番号 等価回路 シンボル 説明 入力をDC 結合で用いる場合に、このピンの出力電圧を $V_{\rm IN}$ +と $V_{\rm IN}$ - の同相入力電圧とする必要があります。 セクション 3.0 を参照してください。 7 $V_{CMO}$ DGND バンドギャップ出力電圧。 このピンは 1.0 µA までソースまたはシ $V_{BG}$ 31 ンクが可能です。 較正処理の実行中。較正処理の実行中はこのピンが High に 126 CalRun なます。 DGND 外付けバイアス抵抗の接続。このピンとグラウンドとの間に 3.3k (± 0.1%)を接続してください。 セクション 1.1 を参照し 32 $R_{EXT}$ てください。

## ピン説明および等価回路(つづき)

| 機能説明           |                  |                                                |                                      |

|----------------|------------------|------------------------------------------------|--------------------------------------|

| ピン番号           | シンボル             | 等価回路                                           | 説明                                   |

|                | D7-              | 구 IM ID IDI                                    | מאיזעם                               |

| 83<br>84       | D/-<br>D7+       |                                                |                                      |

| 84<br>85       | D/+<br>D6-       |                                                |                                      |

| 85<br>86       | D6+              |                                                |                                      |

| 89             | D5-              |                                                |                                      |

| 90             | D5+              |                                                |                                      |

| 91             | D3+<br>D4-       |                                                |                                      |

| 92             | D4+              |                                                | 時間シーケンスの中でサンプリングされた LVDS データ出力       |

| 93             | D3-              |                                                | ビット。各出力は差動 100 抵抗でからなず終端しなければな       |

| 94             | D3+              |                                                | はなせん。                                |

| 95             | D2-              | .,                                             |                                      |

| 96             | D2+              | $V_{DR}$                                       |                                      |

| 100            | D1-              | Υ                                              |                                      |

| 101            | D1+              |                                                |                                      |

| 102            | D0-              |                                                |                                      |

| 103            | D0+              | ΙΥΙ                                            |                                      |

| 104            | Dd7-             | <del>                                   </del> |                                      |

| 104            | Dd7-<br>Dd7+     | │ <b>╽</b> ┩ <i>╅</i> <b>★</b> ┡╢              |                                      |

| 105            | Dd/∓<br>Dd6-     | ▎╶ <del>▘</del> ┡┪╀  ╀┍╩╸                      |                                      |

| 107            | Dd6+             | <del>   (</del> )                              |                                      |

| 111            | Ddo <sup>+</sup> |                                                |                                      |

| 112            | Dd5+             |                                                |                                      |

| 113            | Dd4-             | ▎▗ <del>▕</del> ▐▘ <del>▘</del>                |                                      |

| 114            | Dd4+             | <sup>†</sup> -77   † 77   1                    | 時間シーケンスの中でサンプリングされた LVDS データ出力       |

| 115            | Dd3-             | <del>'  •   '</del>                            | ビット。各出力は差動 100 抵抗でからなず終端しなければな       |

| 116            | Dd3+             |                                                | はなせん。                                |

| 117            | Dd2-             | $     \Psi  $                                  |                                      |

| 118            | Dd2+             |                                                |                                      |

| 122            | Dd1-             | DR GND                                         |                                      |

| 123            | Dd1+             | DI GIAD                                        |                                      |

| 124            | Dd0-             |                                                |                                      |

| 125            | Dd0+             |                                                |                                      |

| 79             |                  |                                                | アウト・オブ・レンジ出力。差動 High は差動入力がレンジ外      |

| 80             | OR+              |                                                | にあることを示します (FSR ピンで規定される± 300mV または  |

|                | OR-              |                                                | ± 400mV のレンジ外)。 セクション 1.6 を参照してください。 |

|                |                  |                                                |                                      |

| 82             | DCLK+            |                                                | 出力データのラッチに使用する差動クロック出力。このクロック        |

| 81             | DCLK-            |                                                | 信号に同期して、遅延データと非遅延データが出力されます。         |

| 2, 5, 8, 13,   |                  |                                                |                                      |

| 16, 17, 20,    | ***              |                                                | 悪に& #『ヘキサキサ ・CUD に対していていったに、マノが対し    |

| 25, 28, 33,    | $V_{A}$          |                                                | 電源ピンを除きます。 GND に対してバイパスを行ってください。     |

| 128            |                  |                                                |                                      |

| 40, 51, 62,    |                  |                                                |                                      |

| 73, 88, 99,    | $V_{DR}$         |                                                | 出力ドライバの電源ピン。 DR GND に対してバイパスを行ってく    |

| 110, 121       | * DR             |                                                | ださい。                                 |

|                |                  |                                                |                                      |

| 1, 6, 9, 12,   | GND              |                                                | $V_A$ のグラウンド・リターン。                   |

| 15, 21, 24, 27 |                  |                                                | A .                                  |

| 42, 53, 64,    |                  |                                                |                                      |

| 74, 87, 97,    | DR GND           |                                                | V <sub>DR</sub> のグラウンド・リターン。         |

| 108, 119       |                  |                                                |                                      |

| 22, 23, 29,    | ·                |                                                |                                      |

| 34, 36 - 39,   |                  |                                                |                                      |

| 41, 43 - 50,   |                  |                                                |                                      |

| 52, 54 - 61,   | NC               |                                                | 未接続ピン。これらのピンには何も接続しないでください。          |

| 63, 65 - 72,   |                  |                                                |                                      |

| 75 - 78, 98,   |                  |                                                |                                      |

| 109, 120       |                  |                                                |                                      |

| <u> </u>       |                  | ı                                              | •                                    |

|                |                  |                                                |                                      |

### 絶対最大定格 (Note 1、2)

本データシートには軍用・航空宇宙用の規格は記載されていません。 関連する電気的信頼性試験方法の規格を参照ください。

| アナログ電源電圧 ( ${ m V}_{ m A}$ 、 ${ m V}_{ m DR}$ ) | 2.2V                                                    |

|-------------------------------------------------|---------------------------------------------------------|

| デジタル電源とアナログ電源の電位差                               | $\frac{1}{2}$ (V <sub>DR</sub> - V <sub>A</sub> ) 300mV |

| ドライバ電源電圧                                        | $(V_{DR})V_A100mV)$                                     |

| 各入力ピン電圧                                         | $-0.15V \sim (V_A + 0.15V)$                             |

| グラウンド電圧差  GND - DR GND                          | $0V \sim 100 \text{mV}$                                 |

| 各入力ピン電流 (Note 3)                                | ± 25mA                                                  |

| パッケージの入力電流 (Note 3)                             | ± 50 mA                                                 |

| <b>パッケー</b> ジ消費電力 (T <sub>A</sub> = 25 )        | 2.0 W                                                   |

| ESD 耐性 (Note 4)<br>人体モデル<br>マシン・モデル             | 2500V<br>250V                                           |

| ハンダ付け温度赤外線 (10 秒 ) (Not                         | e 5) 235                                                |

| 保存温度範囲                                          | - 65 ~ + 150                                            |

|                                                 |                                                         |

### 定格温度範囲 (Note 1、2)

| 周囲温度範囲                        | $-40$ $T_A$ $+85$            |

|-------------------------------|------------------------------|

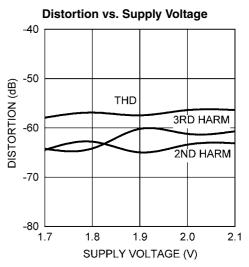

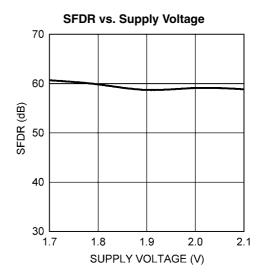

| 電源電圧 V <sub>A</sub>           | + 1.8V ~ + 2.0V              |

| ドライバ電源電圧 ( ${ m V}_{ m DR}$ ) | + 1.8V $\sim V_A$            |

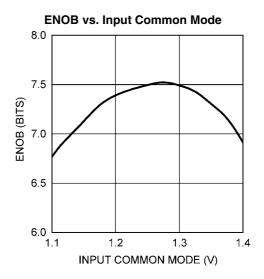

| アナログ入力同相電圧                    | + 1.2V ~ + 1.3V              |

| $ m V_{IN}$ 差動電圧範囲            | - $V_{FS}/2 \sim + V_{FS}/2$ |

| グラウンド電圧差 ( GND - DR GND )     | 0V                           |

| CLK ピン電圧範囲                    | $0V \sim V_A$                |

| 差動 CLK 振幅                     | $0.6V_{P-P} \sim 2.0V_{P-P}$ |

### パッケージ熱抵抗

| Package                      | θ <sub>J-C</sub><br>(Top of<br>Package) | θ <sub>J-PAD</sub><br>(Thermal Pad) |

|------------------------------|-----------------------------------------|-------------------------------------|

| 128-Lead Exposed Pad<br>LQFP | 10°C/W                                  | 2.8°C / W                           |

ハンダ付けのプロセスは、National Semiconductor's Reflow Temperature Profile 規格に準拠してください。www.national.com/JPN/packaging をご覧ください。

### コンバータの電気的特性

以下の仕様は較正後に適用され条件は次のとおりです。  $V_A = V_{DR} = + 1.9 V_{DC}$ 、 OutV = 1.9 V、  $V_{IN}$  FSR(AC 結合 ) = 差動  $800 \text{mV}_{P-P}$ 、  $C_L = 10 \text{pF}$ 、  $0.5 \text{V}_{P-P}$  でデューティ・サイクル 50% の差動 AC 結合正弦波クロック  $f_{CLK} = 1 \text{GHz}$ 、  $R_{EXT} = 3300 \pm 0.1\%$ 、 アナログ信号 ソース・インピーダンス = 100 。 太文字表記のリミット値は  $\mathbf{T_A} = \mathbf{T_{MIN}} \sim \mathbf{T_{MAX}}$  にわたって適用されます。特記のない限り、すべてのリミット値は、  $T_A = 25$  です。 (Note 6、7)

| Symbol              | Parameter                             | Conditions                                                | Typical<br>(Note 8)                    | Limits<br>(Note 8) | Units<br>(Limits)      |

|---------------------|---------------------------------------|-----------------------------------------------------------|----------------------------------------|--------------------|------------------------|

| STATIC CO           | ONVERTER CHARACTERISTICS              |                                                           | ······································ |                    |                        |

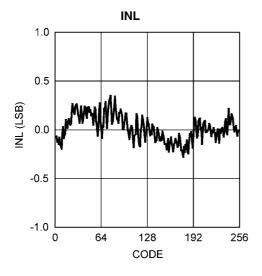

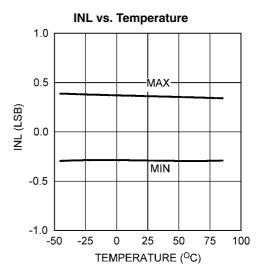

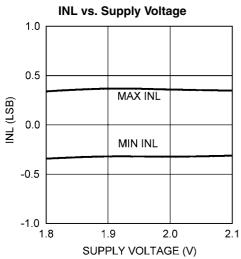

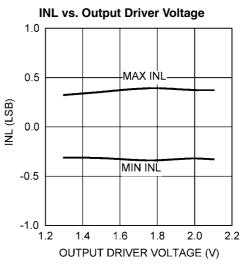

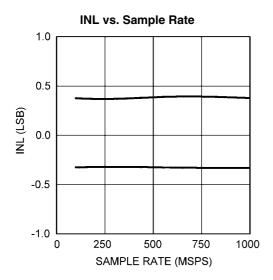

| INL.                | Integral Non-Linearity                |                                                           | ±0.35                                  | ±0.9               | LSB (max)              |

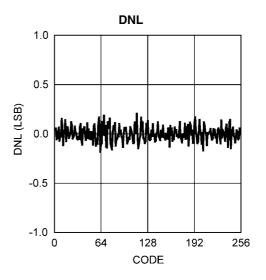

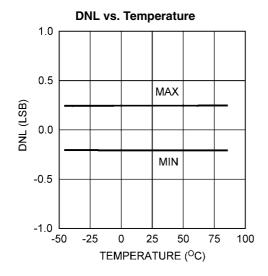

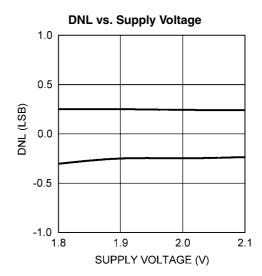

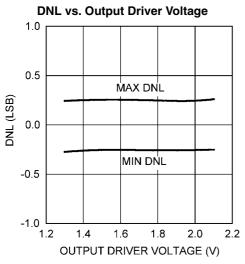

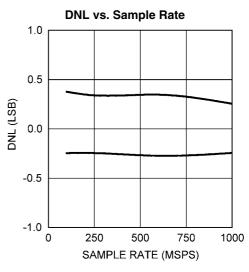

| DNL                 | Differential Non-Linearity            |                                                           | ±0.25                                  | ±0.7               | LSB (max)              |

|                     | Resolution with No Missing Codes      |                                                           |                                        | 8                  | Bits                   |

| V <sub>OFF</sub>    | Offset Error                          |                                                           | -0.45                                  | -1.5<br>0.5        | LSB (min)<br>LSB (max) |

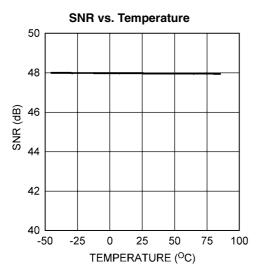

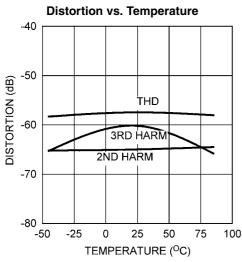

| TC V <sub>OFF</sub> | Offset Error Tempco                   | -40°C to +85°C                                            | -3                                     |                    | ppm/°C                 |

| PFSE                | Positive Full-Scale Error (Note 9)    |                                                           | -2.2                                   | ±25                | mV (max)               |

| NFSE                | Negative Full-Scale Error (Note 9)    |                                                           | -1.1                                   | ±25                | mV (max)               |

| TC PFSE             | Positive Full Scale Error Tempco      | -40°C to +85°C                                            | 20                                     |                    | ppm/°C                 |

| TC NFSE             | Negative Full Scale Error Tempco      | -40°C to +85°C                                            | 13                                     |                    | ppm/°C                 |

| Dynamic C           | Converter Characteristics             |                                                           |                                        |                    |                        |

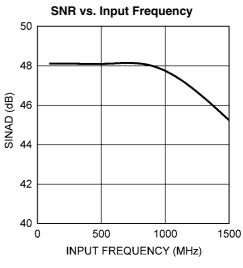

| FPBW                | Full Power Bandwidth                  |                                                           | 1.7                                    |                    | GHz                    |

| B.E.R.              | Bit Error Rate                        |                                                           | 10-18                                  |                    | Error/Bit              |

|                     | Gain Flatness                         | d.c. to 500 MHz                                           | ±0.5                                   |                    | dBFS                   |

|                     | Gain Flatness                         | d.c. to 1 GHz                                             | ±1.0                                   |                    | dBFS                   |

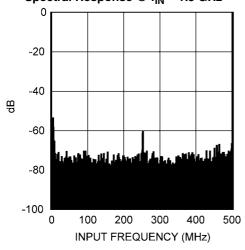

|                     |                                       | $f_{IN} = 100 \text{ MHz}, V_{IN} = FSR - 0.5 \text{ dB}$ | 7.5                                    |                    | Bits                   |

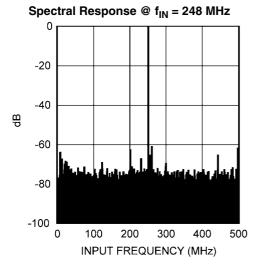

| ENOB                | Effective Number of Bits              | $f_{IN} = 248 \text{ MHz}, V_{IN} = FSR - 0.5 \text{ dB}$ | 7.5                                    | 7.1                | Bits (min)             |

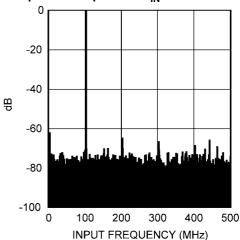

|                     |                                       | $f_{IN} = 498 \text{ MHz}, V_{IN} = FSR - 0.5 \text{ dB}$ | 7.5                                    | 7.1                | Bits (min)             |

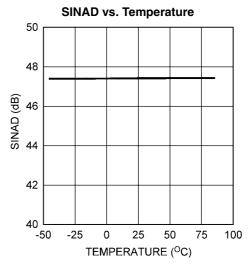

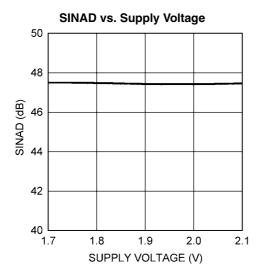

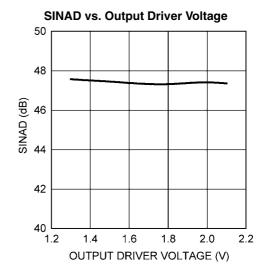

|                     |                                       | f <sub>IN</sub> = 100 MHz, V <sub>IN</sub> = FSR - 0.5 dB | 47                                     |                    | dB                     |

| SINAD               | Signal-to-Noise Plus Distortion Ratio | f <sub>IN</sub> = 248 MHz, V <sub>IN</sub> = FSR - 0.5 dB | 47                                     | 44.8               | dB (min)               |

|                     |                                       | $f_{IN} = 498 \text{ MHz}, V_{IN} = FSR - 0.5 \text{ dB}$ | 47                                     | 44.8               | dB (min)               |

### コンバータの電気的特性(つづき)

以下の仕様は較正後に適用され条件は次のとおりです。  $V_A=V_{DR}=+1.9V_{DC}$ 、 OutV=1.9V、  $V_{IN}$  FSR(AC 結合 ) = 差動  $800 \text{mV}_{P.P.}$   $C_L=10 \text{pF}$ 、  $0.5 \text{V}_{P.P}$  でデューティ・サイクル 50% の差動 AC 結合正弦波クロック  $f_{CLK}=1 \text{GHz}$ 、  $R_{EXT}=3300$   $\pm 0.1\%$ 、 アナログ信号 ソース・インピーダンス= 100 。 太文字表記のリミット値は  $\mathbf{T_A}=\mathbf{T_{MIN}}\sim\mathbf{T_{MAX}}$  にわたって適用されます。特記のない限り、すべてのリミット値は、  $T_A=25$  です。 (Note 6,7)

| Symbol                                             | Parameter                                                                                                                                                          | Conditions                                                                                                           | Typical<br>(Note 8) | Limits<br>(Note 8)    | Units<br>(Limits)                                                                              |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------|------------------------------------------------------------------------------------------------|

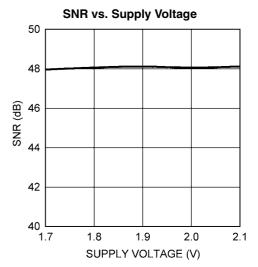

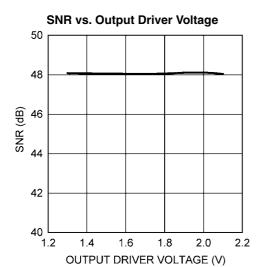

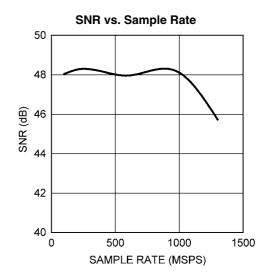

|                                                    |                                                                                                                                                                    | f <sub>IN</sub> = 100 MHz, V <sub>IN</sub> = FSR - 0.5 dB                                                            | 48                  | 1                     | dB                                                                                             |

| SNR                                                | Signal-to-Noise Ratio                                                                                                                                              | f <sub>IN</sub> = 248 MHz, V <sub>IN</sub> = FSR + 0.5 dB                                                            | 48                  | 45.5                  | dB (min)                                                                                       |

|                                                    | <u>L</u>                                                                                                                                                           | f <sub>IN</sub> = 498 MHz, V <sub>IN</sub> = FSR - 0.5 dB                                                            | 48                  | 45.5                  | dB (min)                                                                                       |

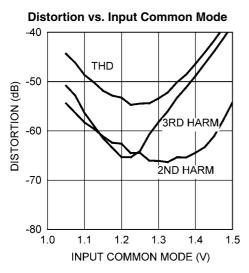

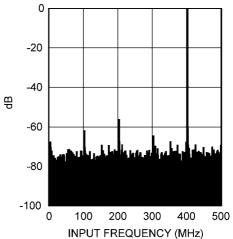

|                                                    |                                                                                                                                                                    | $f_{IN} = 100 \text{ MHz}, V_{IN} = FSR - 0.5 \text{ dB}$                                                            | -57                 |                       | dB                                                                                             |

| THD                                                | Total Harmonic Distortion                                                                                                                                          | f <sub>IN</sub> = 248 MHz, V <sub>IN</sub> = FSR - 0.5 dB                                                            | -57                 | -50                   | dB (max)                                                                                       |

|                                                    | 4                                                                                                                                                                  | f <sub>IN</sub> = 498 MHz, V <sub>IN</sub> = FSR - 0.5 dB                                                            | -57                 | -50                   | dB (max)                                                                                       |

|                                                    |                                                                                                                                                                    | f <sub>IN</sub> = 100 MHz, V <sub>IN</sub> = FSR - 0.5 dB                                                            | -64                 |                       | dB                                                                                             |

| 2nd Harm                                           | Second Harmonic Distortion                                                                                                                                         | f <sub>IN</sub> = 248 MHz, V <sub>IN</sub> = FSR - 0.5 dB                                                            | -64                 |                       | d₿                                                                                             |

|                                                    |                                                                                                                                                                    | f <sub>IN</sub> = 498 MHz, V <sub>IN</sub> = FSR - 0.5 dB                                                            | -64                 |                       | dB                                                                                             |

|                                                    |                                                                                                                                                                    | f <sub>IN</sub> = 100 MHz, V <sub>IN</sub> = FSR - 0.5 dB                                                            | -64                 |                       | dB                                                                                             |

| 3rd Harm                                           | Third Harmonic Distortion                                                                                                                                          | f <sub>IN</sub> = 248 MHz, V <sub>IN</sub> = FSR - 0.5 dB                                                            | -64                 |                       | dB                                                                                             |

|                                                    |                                                                                                                                                                    | f <sub>IN</sub> = 498 MHz, V <sub>IN</sub> = FSR - 0.5 dB                                                            | -64                 |                       | dB                                                                                             |

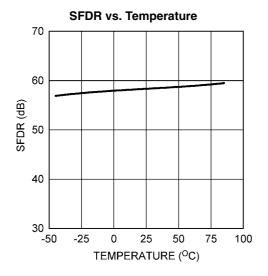

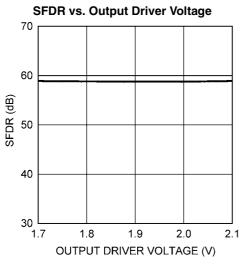

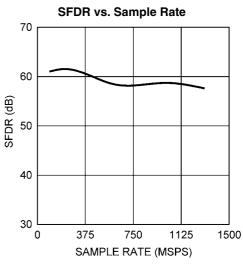

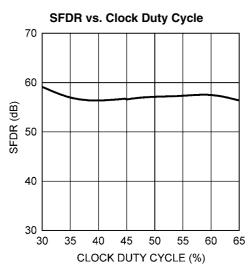

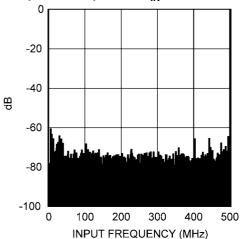

|                                                    |                                                                                                                                                                    | f <sub>IN</sub> = 100 MHz, V <sub>IN</sub> = FSR - 0.5 dB                                                            | 58.5                |                       | dB                                                                                             |

| SFDR                                               | Spurious-Free dynamic Range                                                                                                                                        | f <sub>IN</sub> = 248 MHz, V <sub>IN</sub> = FSR - 0.5 dB                                                            | 58.5                | 50                    | dB (min)                                                                                       |

|                                                    |                                                                                                                                                                    | $f_{IN} = 498 \text{ MHz}, V_{IN} = FSR - 0.5 \text{ dB}$                                                            | 58.5                | 50                    | dB (min)                                                                                       |

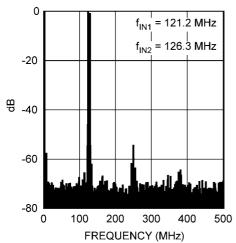

|                                                    |                                                                                                                                                                    | f <sub>IN1</sub> = 121 MHz, V <sub>IN</sub> = FSR - 7 dB                                                             |                     |                       | GD (IIIII)                                                                                     |

| IMD                                                | Intermodulation Distortion                                                                                                                                         | $f_{IN2} = 126 \text{ MHz}, V_{IN} = FSR - 7 \text{ dB}$                                                             | -51                 |                       | dB                                                                                             |

|                                                    | Out of Range Output Code                                                                                                                                           | (V <sub>IN</sub> +) - (V <sub>IN</sub> ) > + Full Scale                                                              |                     | 255                   |                                                                                                |

|                                                    | (In addition to OR Output high)                                                                                                                                    | $(V_{IN}^+) - (V_{IN}^-) < -$ Full Scale                                                                             |                     | 0                     | 7                                                                                              |

| ANALOG I                                           | NPUT AND REFERENCE CHARACTE                                                                                                                                        |                                                                                                                      | <b>-L</b>           | <u> </u>              |                                                                                                |

|                                                    | Full Scale Analog Differential Input<br>Range                                                                                                                      | FSR pin Low                                                                                                          |                     | 550                   | mV <sub>P-P</sub> (min                                                                         |

| V <sub>IN</sub>                                    |                                                                                                                                                                    |                                                                                                                      | 600                 | 650                   | mV <sub>P-P</sub> (max                                                                         |

|                                                    |                                                                                                                                                                    | FSR pin High                                                                                                         | 800                 | 750                   | mV <sub>P-P</sub> (min                                                                         |

|                                                    |                                                                                                                                                                    |                                                                                                                      |                     | 850                   | mV <sub>P-P</sub> (max                                                                         |

|                                                    |                                                                                                                                                                    |                                                                                                                      |                     | V <sub>CMO</sub> - 50 | mV (min)                                                                                       |

| CMI                                                | Common Mode Analog Input Voltage                                                                                                                                   |                                                                                                                      | V <sub>CMO</sub>    | V <sub>CMO</sub> + 50 | mV (max)                                                                                       |

| •                                                  | Analog Input Capacitance                                                                                                                                           | Differential                                                                                                         | 0.02                | CIVIO                 | pF                                                                                             |

| O <sub>IN</sub>                                    | (Note 10)                                                                                                                                                          | Each input to ground                                                                                                 | 1.6                 |                       | pF                                                                                             |

|                                                    |                                                                                                                                                                    |                                                                                                                      |                     | 94                    | Ω (min)                                                                                        |

| R <sub>IN</sub>                                    | Differential Input Resistance                                                                                                                                      |                                                                                                                      | 100                 | 106                   | Ω (max)                                                                                        |

| ANALOG C                                           | OUTPUT CHARACTERISTICS                                                                                                                                             |                                                                                                                      |                     | l                     |                                                                                                |

| V <sub>CMO</sub>                                   | Common Mode Output Voltage                                                                                                                                         |                                                                                                                      | 1.01                | 0.95                  | V (min)                                                                                        |

| CMO                                                | Common wiede Output Voltage                                                                                                                                        | I <sub>CMO</sub> = ±1 μA                                                                                             | 1.21                | 1.45                  | V (max)                                                                                        |

|                                                    |                                                                                                                                                                    |                                                                                                                      |                     |                       |                                                                                                |

| rc v <sub>cmo</sub>                                | Common Mode Output Voltage<br>Temperature Coefficient                                                                                                              | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                                                  | 118                 | 1                     | ppm/°C                                                                                         |

| rc v <sub>cmo</sub>                                |                                                                                                                                                                    | $T_A = -40$ °C to +85°C<br>$I_{BG} = \pm 100 \mu A$                                                                  | 118                 | 1.22<br>1.33          | ppm/°C<br>V (min)<br>V (max)                                                                   |

| / <sub>BG</sub>                                    | Temperature Coefficient  Bandgap Reference Output Voltage  Bandgap Reference Voltage                                                                               | · ·                                                                                                                  | 1.26                |                       | V (min)<br>V (max)                                                                             |

| BG<br>C V <sub>BG</sub>                            | Temperature Coefficient  Bandgap Reference Output Voltage  Bandgap Reference Voltage  Temperature Coefficient                                                      | I <sub>BG</sub> = ±100 μA                                                                                            |                     |                       | V (min)                                                                                        |

| BG<br>C V <sub>BG</sub>                            | Temperature Coefficient  Bandgap Reference Output Voltage  Bandgap Reference Voltage                                                                               | $I_{BG} = \pm 100 \ \mu A$ $T_A = -40^{\circ}C \text{ to } +85^{\circ}C,$                                            | 1.26                |                       | V (min)<br>V (max)                                                                             |

| / <sub>BG</sub><br>TC V <sub>BG</sub><br>CLOCK INF | Temperature Coefficient  Bandgap Reference Output Voltage  Bandgap Reference Voltage  Temperature Coefficient  PUT CHARACTERISTICS                                 | $I_{BG} = \pm 100 \ \mu A$ $T_A = -40^{\circ}C \text{ to } +85^{\circ}C,$                                            | 1.26                |                       | V (min)<br>V (max)                                                                             |

| BG<br>CV <sub>BG</sub>                             | Temperature Coefficient  Bandgap Reference Output Voltage  Bandgap Reference Voltage  Temperature Coefficient                                                      | $I_{BG} = \pm 100 \mu\text{A}$ $T_{A} = -40^{\circ}\text{C to } +85^{\circ}\text{C},$ $I_{BG} = \pm 100 \mu\text{A}$ | 1.26                | 0.4                   | V (min)<br>V (max)<br>ppm/°C                                                                   |

| BG<br>CV <sub>BG</sub>                             | Temperature Coefficient  Bandgap Reference Output Voltage  Bandgap Reference Voltage  Temperature Coefficient  PUT CHARACTERISTICS                                 | $I_{BG}$ = ±100 μA<br>$T_A$ = -40°C to +85°C,<br>$I_{BG}$ = ±100 μA<br>Square Wave Clock                             | 1.26<br>-28         | 0.4<br>2.0<br>0.4     | V (min) V (max)  ppm/°C  V <sub>P-P</sub> (min) V <sub>P-P</sub> (max)  V <sub>P-P</sub> (max) |

| / <sub>BG</sub>                                    | Temperature Coefficient  Bandgap Reference Output Voltage  Bandgap Reference Voltage  Temperature Coefficient  PUT CHARACTERISTICS  Differential Clock Input Level | $I_{BG}$ = ±100 μA $T_A$ = -40°C to +85°C, $I_{BG}$ = ±100 μA  Square Wave Clock  Sine Wave Clock                    | 1.26<br>-28<br>0.6  | 0.4<br>2.0<br>0.4     | V (min) V (max)  ppm/°C  V <sub>P-P</sub> (min) V <sub>P-P</sub> (max) V <sub>P-P</sub> (min)  |

### コンバータの電気的特性(つづき)

以下の仕様は較正後に適用され条件は次のとおりです。  $V_A=V_{DR}=+1.9V_{DC}$ 、 OutV=1.9V、  $V_{IN}$  FSR(AC 結合 ) = 差動  $800 \text{mV}_{P.P.}$   $C_L=10 \text{pF}$ 、  $0.5 \text{V}_{P.P}$  でデューティ・サイクル 50% の差動 AC 結合正弦波クロック  $f_{CLK}=1 \text{GHz}$ 、  $R_{EXT}=3300\pm0.1\%$ 、 アナログ信号 ソース・インピーダンス= 100 。 太文字表記のリミット値は  $\mathbf{T_A}=\mathbf{T_{MIN}}\sim\mathbf{T_{MAX}}$  にわたって適用されます。特記のない限り、すべてのリミット値は、  $T_A=25$  です。 (Note 6,7)

| Symbol                 | Parameter                                           | Conditions                                                             | Typical<br>(Note 8) | Limits<br>(Note 8) | Units<br>(Limits)       |

|------------------------|-----------------------------------------------------|------------------------------------------------------------------------|---------------------|--------------------|-------------------------|

|                        | CONTROL PIN CHARACTERISTICS                         |                                                                        |                     |                    |                         |

| V <sub>IH</sub>        | Logic High Input Voltage                            | (Note 12)                                                              |                     | 1.4                | V (min)                 |

| V <sub>IL</sub>        | Logic Low Input Voltage                             | (Note 12)                                                              |                     | 0.5                | V (max)                 |

| 1                      | Input Current                                       | $V_{iN} = 0$ or $V_{iN} = V_A$                                         | ±1                  |                    | μΑ                      |

| C <sub>IN</sub>        | Logic Input Capacitance (Note 13)                   | Each input to ground                                                   | 1.2                 |                    | pF                      |

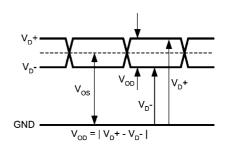

| DIGITAL O              | OUTPUT CHARACTERISTICS                              |                                                                        |                     |                    |                         |

|                        |                                                     | OutV - V managered single anded                                        | 200                 | 200                | mV <sub>P-P</sub> (min) |

| v                      | LVDS Differential Output Voltage                    | OutV = V <sub>A</sub> , measured single-ended                          | 300                 | 450                | mV <sub>P-P</sub> (max  |

| V <sub>OD</sub>        | LVDS Differential Output Voltage                    | Out CND managed single and d                                           | 005                 | 140                | mV <sub>P-P</sub> (min) |

|                        | *                                                   | OutV = GND, measured single-ended                                      | 225                 | 340                | mV <sub>P-P</sub> (max  |

| Δ V <sub>OD DIFF</sub> | Change in LVDS Output Swing<br>Between Logic Levels |                                                                        | ±1                  |                    | mV                      |

| V <sub>os</sub>        | Output Offset Voltage                               |                                                                        | 800                 |                    | mV                      |

|                        | Output Offset Voltage Change                        |                                                                        | . 4                 | <del></del>        |                         |

| ΔV <sub>os</sub>       | Between Logic Levels                                |                                                                        | ±1                  |                    | mV                      |

| l <sub>os</sub>        | Output Short Circuit Current                        | Output+ & Output- connected to 0.8V                                    | -4                  |                    | mA                      |

| z <sub>o</sub>         | Differential Output Impedance                       |                                                                        | 100                 |                    | Ohms                    |

| POWER S                | UPPLY CHARACTERISTICS                               | -                                                                      |                     |                    |                         |

| I <sub>A</sub>         | Analog Supply Current                               | PD = Low                                                               | 646                 | 792                | mA (max)                |

|                        |                                                     | PD = High                                                              | 4.5                 |                    | mA                      |

| DR                     | Output Driver Supply Current                        | PD = Low                                                               | 108                 | 160                | mA (max)                |

|                        |                                                     | PD = High                                                              | 0.1                 |                    | mA                      |

| P <sub>D</sub>         | Power Consumption                                   | PD = Low                                                               | 1.43                | 1.8                | W (max)                 |

|                        |                                                     | PD = High                                                              | 8.7                 |                    | mW                      |

| PSRR1                  | D.C. Power Supply Rejection Ratio                   | Change in Offset Error with change in V <sub>A</sub> from 1.8V to 2.0V | 73                  |                    | dB                      |

| AC ELECT               | RICAL CHARACTERISTICS                               |                                                                        |                     |                    |                         |

|                        |                                                     | T <sub>A</sub> = 85°C                                                  | 1.1                 | 1.0                | GHz (min)               |

| f <sub>CLK1</sub>      | Maximum Conversion Rate                             | T <sub>A</sub> ≤ 75°C                                                  | 1.3                 |                    | GHz                     |

|                        |                                                     | T <sub>A</sub> ≤ 70°C                                                  | 1.6                 |                    | GHz                     |

| f <sub>CLK2</sub>      | Minimum Conversion Rate                             |                                                                        | 200                 |                    | MHz                     |

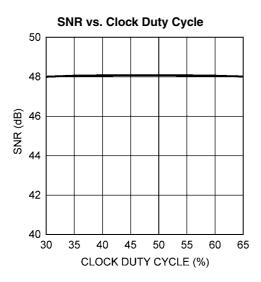

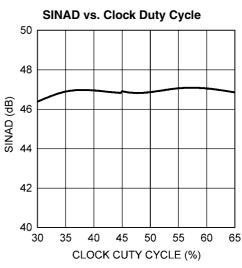

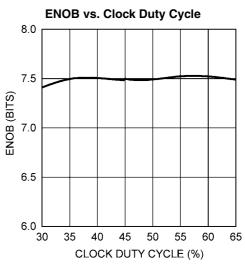

|                        | Input Clock Duty Cycle                              | 200 MHz ≤ Input clock frequency < 1<br>GHz                             | 50                  | 20<br>80           | % (min)<br>% (max)      |

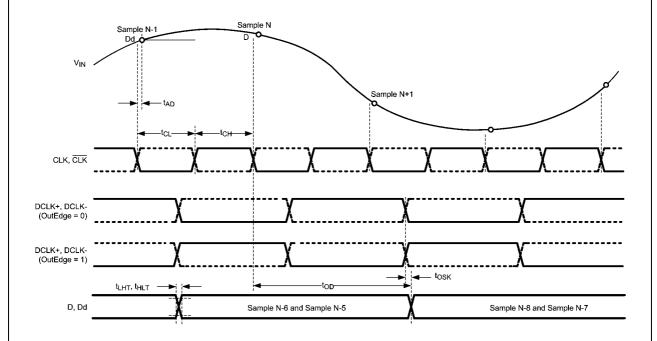

| t <sub>CL</sub>        | Input Clock Low Time (Note 12)                      |                                                                        | 500                 | 200                | ps (min)                |

| t <sub>ch</sub>        | Input Clock High Time (Note 12)                     |                                                                        | 500                 | 200                | ps (min)                |

| 011                    | DCLK Duty Cycle (Note 12)                           |                                                                        | 50                  | 45<br>55           | % (min)<br>% (max)      |

| t <sub>LHT</sub>       | Differential Low to High Transition<br>Time         | 10% to 90%, C <sub>L</sub> = 2.5 pF                                    | 250                 |                    | ps                      |

| t <sub>HLT</sub>       | Differential High to Low Transition<br>Time         | 10% to 90%, C <sub>L</sub> = 2.5 pF                                    | 250                 |                    | ps                      |

| t <sub>osk</sub>       | DCLK to Data Output Skew (Note 11)                  | 50% of DCLK transition to 50% of Data transition                       | 0                   | ±200               | ps (max)                |

| t <sub>AD</sub>        | Sampling (Aperture) Delay                           | Input CLK+ Fall to Acquisition of Data                                 | 930                 |                    | ps                      |

| AJ                     | Aperture Jitter                                     |                                                                        | 0.4                 |                    | ps rms                  |

| t <sub>od</sub>        | Input Clock to Data Output Delay                    | 50% of Input Clock transition to 50% of Data transition                | 2.7                 |                    | ns                      |

|                        | Pingling Dolay (Latency) (Note 14)                  | "D" Outputs                                                            |                     | 7                  | Closk Core              |

|                        | Pipeline Delay (Latency) (Note 11)                  | "Dd" Outputs                                                           |                     | 8                  | Clock Cycles            |

www.national.com/jpn/

### コンバータの電気的特性(つづき)

以下の仕様は較正後に適用され条件は次のとおりです。 $V_A = V_{DR} = + 1.9V_{DC}$ 、OutV = 1.9V、 $V_{IN}$  FSR(AC 結合) = 差動 800mV $_{P.P.}$  C $_L = 10$ pF、0.5V $_{P.P}$  でデューティ・サイクル 50% の差動 AC 結合正弦波クロック  $f_{CLK} = 1$ GHz、 $R_{EXT} = 3300 \pm 0.1$ %、アナログ信号 ソース・インピーダンス = 100 。 太文字表記のリミット値は  $T_A = T_{MIN} \sim T_{MAX}$  にわたって適用されます。特記のない限り、すべてのリミット値は、 $T_A = 25$  です。(Note 6、7)

| Symbol           | Parameter                                          | Conditions | Typical<br>(Note 8) | Limits<br>(Note 8) | Units<br>(Limits) |

|------------------|----------------------------------------------------|------------|---------------------|--------------------|-------------------|

| t <sub>WU</sub>  | PD low to Rated Accuracy Conversion (Wake-Up Time) |            | 500                 |                    | ns                |

| t <sub>CAL</sub> | Calibration Cycle Time                             |            | 46,000              |                    | Clock Cycles      |

- Note 1: 絶対最大定格とは、デバイスに破壊が発生する可能性のある制限値をいいます。絶対最大定格での動作は保証されません。動作定格とはデバイスが機能する条件を示しますが、特定の性能リミット値を保証するものではありません。保証された仕様、および試験条件については「電気的特性」を参照してください。保証された仕様はリストに示された試験条件でのみ適用されます。リストに示されている試験条件の下で動作していない場合には、いくつかの性能特性は低下することがあります。

- Note 2: 特記のない限り、すべての電圧は GND = DRGND = 0V を基準にして測定されています。

- Note 3: いずれかのピンで入力電圧  $(V_{\rm IN})$  が電源電圧を超えた場合(すなわち  $V_{\rm IN} < {\rm GND}$ 、または  $V_{\rm IN} > {\rm V_A}$  のとき)、そのピンの入力電流を  $25{\rm mA}$  以下に制限しなければなりません。 最大パッケージ入力定格電流  $(50{\rm mA})$  により、電源電圧を超えて  $25{\rm mA}$  の電流を流すことができるピン数は 2 本に制限されます。これらのリニット値は、電源ピン、グラウンド・ピン、デジタル出力ピンには適用されません。

- Note 4: 人体モデルの場合、100pF のコンデンサから直列抵抗 1.5 k を通して各ピンに放電させます。 マシン・モデルの場合は、220pF のコンデンサから直接各ピンに放電させます。

- Note 5: 面実装デバイスのハンダ付け方法については、1986 年以降に発行された「National Semiconductor Linear Data Book」の "Surface Mount" セクションを参照してください。

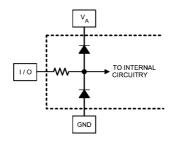

- Note 6: アナログ入力は、以下に示されるように保護されています。絶対最大定格を超える入力電圧振幅はデバイスを破壊することがあります。

- Note 7: 精度を保証するために、 $V_A$  および  $V_{DR}$  電源ピンにはそれぞれ別個のパイパス・コンデンサを設けて同一電源に接続します。また、定格性能を達成するには、裏面の露出パッドをグラウンドに適切にハンダ付けする必要があります。

- **Note 8:** 代表値 (Typical) は、T<sub>J</sub> = 25 で得られる最も標準的な数値です。テスト・リミット値はナショナル セミコンダクターの平均出荷品質レベル AOQL に基づき保証されます。

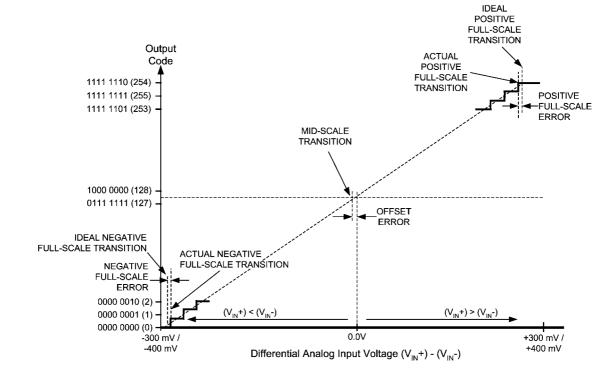

- Note 9: 本デバイスのフルスケール誤差の計算では、実際のリファレンス電圧はその公称値に正確に一致していると仮定しています。 そのためデバイスのフルスケール誤差は、フルスケール誤差とリファレンス電圧誤差の組み合わせになります。 Figure 2 の伝達特性を参照してください。 ゲイン誤差とフルスケール誤差の関係についてはゲイン誤差の仕様定義を参照してください。

- Note 10: アナログ入力容量とクロック入力容量はダイ容量のみです。リードとボンディング・ワイヤが持つインダクタンスによってダイ容量から分離された状態で、差動 とつにはグラウンドに対して 0.65pF の容量が、他のピンには 0.95pF の容量が、それぞれ存在します。

- Note 11: このパラメータは設計によって保証されています。製造時の試験は行っていません。

- Note 12: このパラメータは設計と特性評価によって保証されています。 製造時の試験は行っていません。

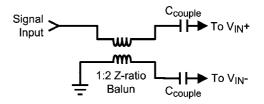

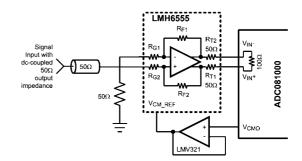

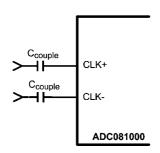

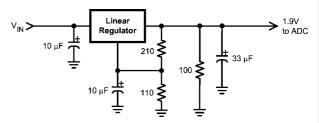

- Note 13: デジタル制御ピン容量はダイ容量のみです。リードとボンディング・ワイヤのインダクタンスによってダイ容量から分離された状態で、各ピンにはグラウンドに対して 1.6pF の容量が存在します。