**DRV2901**

JAJSPK9 - JANUARY 2023

# DRV2901 超音波クリーニング用、電源電圧範囲の広い シングル・チャネル PWM 入力ピエゾ・トランスデューサ・ドライバ

#### 1 特長

- 広い動作電源電圧範囲 (12V~48V)

- 最大 50W のピーク電力をサポート

- 90mΩ の出力 MOSFET による高効率の出力段

- パワーオン・リセットにより、電源シーケンシングなしで 電源立ち上げ時の保護を実現

- 以下の自己保護回路を内蔵

- 低電圧保護

- 過熱保護

- 過負荷保護

- 短絡保護

- 44 ピン HTSSOP パッケージ (DDV) で供給

# 2 アプリケーション

- サーマル・イメージング・カメラ

- 交通監視カメラ

- マシン・ビジョン・カメラ

- ワイヤレス・セキュリティ・カメラ

- ドローン・ビジョン

# 3 概要

DRV2901 は高性能レンズ・クリーナ・トランスデューサ・ド ライバです。このシステムで必要とされるのは、シンプルな 受動 LC 復調フィルタだけであり、実績のある EMI 規格に 準拠した、高品質かつ高効率の増幅を実現します。この デバイスには、2 系統の電源 (1 系統は GVDD および VDD 用の 12 V、もう 1 系統は PVDD 用の 12V~48 V) が必要です。DRV2901 は、パワーオン・リセットを内蔵し ており、電源オン・シーケンスを必要としません。

DRV2901 のチップ上には革新的な保護システムが搭載 されており、システムに損傷を与える可能性のあるさまざま な故障状態からデバイスを保護します。これらの保護機能 には、短絡保護、過電流保護、低電圧保護、および過熱 に対する保護があります。 DRV2901 には独自に新設計さ れた電流制限回路が備わっており、高レベルの過渡状態 において、デバイスがシャットダウンする可能性を低減しま

#### 製品情報(1)

| 部品番号    | パッケージ      | 本体サイズ (公称)   |

|---------|------------|--------------|

| DRV2901 | 44ピンHTSSOP | 14.0mm×6.1mm |

利用可能なパッケージについては、このデータシートの末尾にあ る注文情報を参照してください。

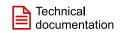

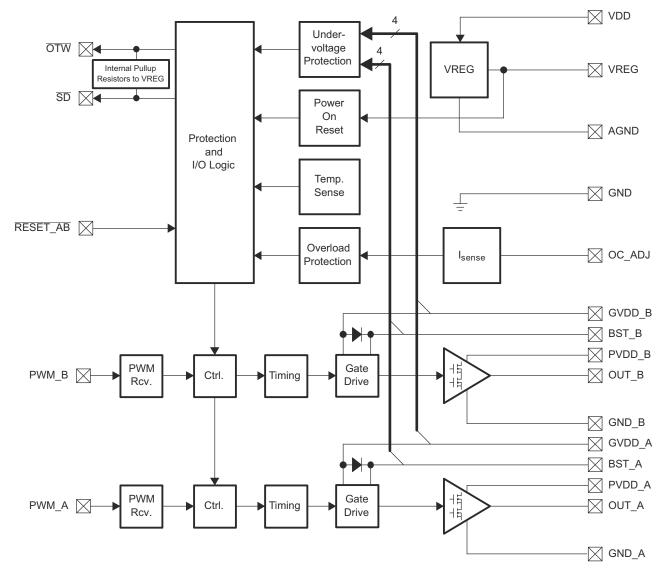

DRV2901 機能ブロック図

# **Table of Contents**

| 1 特長                                 | 1 | 7 Detailed Description                  |    |

|--------------------------------------|---|-----------------------------------------|----|

| 2 アプリケーション                           |   | 7.1 Block Diagrams                      |    |

| 3 概要                                 |   | 7.2 Feature Description                 | 10 |

| 4 Revision History                   |   | 8 Applications and Implementation       | 13 |

| 5 Pin Configuration and Functions    |   | 8.1 Application Information             | 13 |

| 6 Specifications                     |   | 8.2 Typical Application                 | 14 |

| 6.1 Absolute Maximum Ratings         |   | 9 Power Supply Recommendations          | 15 |

| 6.2 ESD Ratings                      |   | 9.1 System Power-up/power-down Sequence | 15 |

| 6.3 Recommended Operating Conditions |   | 9.2 System Design Recommendations       | 15 |

| 6.4 Thermal Information              |   | 10 Mechanical, Packaging, and Orderable |    |

| 6.5 Electrical Characteristics       |   | Information                             | 16 |

| 6.6 Typical Characteristics          | 8 |                                         |    |

|                                      |   |                                         |    |

4 Revision History 資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| DATE         | REVISION | NOTES            |

|--------------|----------|------------------|

| January 2023 | *        | Initial release. |

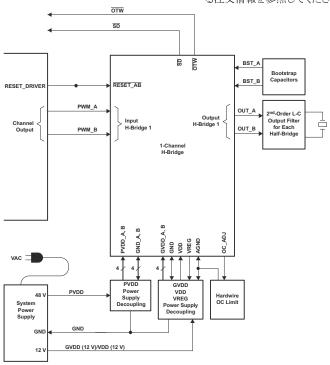

# **5 Pin Configuration and Functions**

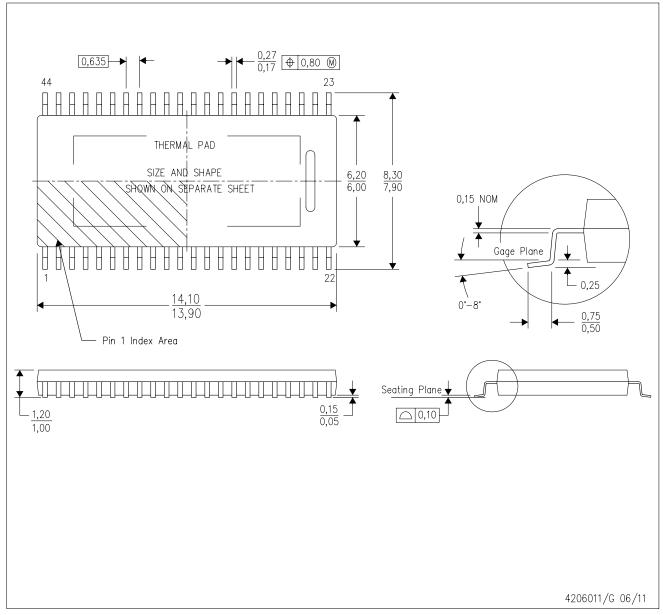

#### **DDV PACKAGE** (TOP VIEW)

図 5-1. DDV Package 44-Pin HTSSOP PowerPad Top View

表 5-1. Pin Functions

| ı      | PIN                                                | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                       |

|--------|----------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO.                                                | ITPE                | DESCRIPTION                                                                                                                       |

| AGND   | 11                                                 | Р                   | Analog ground                                                                                                                     |

| BST_A  | 34                                                 | Р                   | HS bootstrap supply (BST), external .033-µF capacitor to OUT_A required                                                           |

| BST_B  | 33                                                 | Р                   | HS bootstrap supply (BST), external .033-µF capacitor to OUT_B required                                                           |

| GND    | 6, 10, 14, 18, 28,<br>29, 38, 39                   | Р                   | Ground.                                                                                                                           |

| GND_A  | 37                                                 | Р                   | Power ground for half-bridge A                                                                                                    |

| GND_B  | 30                                                 | Р                   | Power ground for half-bridge B                                                                                                    |

| GVDD_A | 1, 44                                              | Р                   | Gate-drive voltage supply requires 0.1-µF capacitor to AGND                                                                       |

| GVDD_B | 22, 23                                             | Р                   | Gate-drive voltage supply requires 0.1-µF capacitor to AGND                                                                       |

| NC     | 3, 4, 19, 20, 24,<br>25, 26, 27, 40, 41,<br>42, 43 | _                   | Do not connect.                                                                                                                   |

| OC_ADJ | 9                                                  | 0                   | Analog overcurrent programming pin requires resistor to ground                                                                    |

| OTW    | 2                                                  | 0                   | Overtemperature warning signal, open-drain, active-low                                                                            |

| OUT_A  | 36                                                 | 0                   | Output, half-bridge A                                                                                                             |

| OUT_B  | 31                                                 | 0                   | Output, half-bridge B                                                                                                             |

| PVDD_A | 35                                                 | Р                   | Power supply input for half-bridge A requires close decoupling of 0.01-μF capacitor in parallel with a 1.0-μF capacitor to GND_A. |

| PVDD_B | 32                                                 | Р                   | Power supply input for half-bridge B requires close decoupling of 0.01-μF capacitor in parallel with a 1.0-μF capacitor to GND_B. |

| PWM_A  | 8                                                  | 1                   | Input signal for half-bridge A                                                                                                    |

# 表 5-1. Pin Functions (continued)

| NAME NO. |            | TVDE <sup>(1)</sup> | DESCRIPTION                                                                                                                      |

|----------|------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------|

|          |            | 1115                | DESCRIPTION                                                                                                                      |

| PWM_B    | 16         | I                   | Input signal for half-bridge B                                                                                                   |

| RESET    | 7, 17      | I                   | Reset signal for half-bridge A and B, active-low                                                                                 |

| SD       | 5          | 0                   | Shutdown signal, open-drain, active-low                                                                                          |

| VDD      | 21         | Р                   | Power supply for digital voltage regulator requires a 47-μF capacitor in parallel with a 0.1-μF capacitor to GND for decoupling. |

| VREG     | 12, 13, 15 | Р                   | Digital regulator supply filter pin requires 0.1-μF capacitor to AGND.                                                           |

(1) I = input, O = output, P = power

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

over operating free-air temperature range unless otherwise noted (1)

| VDD to AGND                                                   | –0.3 V to 13.2 V |

|---------------------------------------------------------------|------------------|

| GVDD_X to AGND                                                | −0.3 V to 13.2 V |

| PVDD_X to GND_X (2)                                           | –0.3 V to 71 V   |

| OUT_X to GND_X (2)                                            | -0.3 V to 71V    |

| BST_X to GND_X (2)                                            | −0.3 V to 79.7 V |

| VREG to AGND                                                  | -0.3 V to 4.2 V  |

| GND_X to GND                                                  | –0.3 V to 0.3 V  |

| GND_X to AGND                                                 | -0.3 V to 0.3 V  |

| GND to AGND                                                   | -0.3 V to 0.3 V  |

| PWM_X, OC_ADJ, M1, M2, M3 to AGND                             | -0.3 V to 4.2 V  |

| RESET_X, SD, OTW to AGND                                      | –0.3 V to 7 V    |

| Maximum continuous sink current ( SD, OTW)                    | 9 mA             |

| Maximum operating junction temperature range, T <sub>J</sub>  | 0°C to 125°C     |

| Storage temperature                                           | -40°C to 125°C   |

| Lead temperature, 1,6 mm (1/16 inch) from case for 10 seconds | 260°C            |

| Minimum pulse duration, low                                   | 50 ns            |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                         | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per AEC Q100-011            | ±500  | V    |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# **6.3 Recommended Operating Conditions**

|                     |                                                      |                                                         | MIN  | TYP | MAX  | UNIT |

|---------------------|------------------------------------------------------|---------------------------------------------------------|------|-----|------|------|

| PVDD_X              | Half-bridge supply                                   | DC supply voltage                                       | 0    | 50  | 52.5 | V    |

| GVDD_X              | Supply for logic regulators and gate-drive circuitry | DC supply voltage                                       | 10.8 | 12  | 13.2 | V    |

| VDD                 | Digital regulator input                              | DC supply voltage                                       | 10.8 | 12  | 13.2 | V    |

| L <sub>Output</sub> | Output-filter inductance                             | Minimum output inductance under short-circuit condition | 5    | 10  |      | μH   |

| F <sub>PWM</sub>    | PWM frame rate                                       |                                                         | 192  | 384 | 432  | kHz  |

| TJ                  | Junction temperature                                 |                                                         | 0    |     | 125  | °C   |

#### **6.4 Thermal Information**

|                               |                                           | DRV2901                    |      |

|-------------------------------|-------------------------------------------|----------------------------|------|

| THERMAL METRIC <sup>(1)</sup> |                                           | DDV 44-PINS HTSSOP         | UNIT |

|                               |                                           | JEDEC STANDARD 4 LAYER PCB | 0    |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance    | 50.7                       | °C/W |

| R <sub>θJC(top)</sub>         | Junction-to-case (top) thermal resistance | 0.36                       | °C/W |

<sup>(2)</sup> These voltages represent the dc voltage + peak ac waveform measured at the terminal of the device in all conditions.

| THERMAL METRIC <sup>(1)</sup> |                                              | DRV2901  DDV 44-PINS HTSSOP  JEDEC STANDARD 4 LAYER PCB | UNIT |  |

|-------------------------------|----------------------------------------------|---------------------------------------------------------|------|--|

| $R_{\theta JB}$               | Junction-to-board thermal resistance         | 24.4                                                    | °C/W |  |

| ΨЈТ                           | Junction-to-top characterization parameter   | 0.19                                                    | °C/W |  |

| ΨЈВ                           | Junction-to-board characterization parameter | 24.2                                                    | °C/W |  |

| R <sub>θJC(bot)</sub>         | Junction-to-case (bottom) thermal resistance | n/a                                                     | °C/W |  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

# 6.5 Electrical Characteristics

$R_L$ = 6  $\Omega$ ,  $F_{PWM}$  = 384 kHz, unless otherwise noted. All performance is in accordance with recommended operating conditions unless otherwise specified.

|                                    | DADAMETED                                                                          | TEST CONDITIONS                                                                           | D    | RV2900 |      | UNIT |

|------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|--------|------|------|

|                                    | PARAMETER                                                                          | TEST CONDITIONS                                                                           | MIN  | TYP    | MAX  | UNII |

| Internal Voltage R                 | legulator and Current Consumption                                                  |                                                                                           |      |        |      |      |

| VREG                               | Voltage regulator, only used as a reference node                                   | VDD = 12 V                                                                                | 2.95 | 3.3    | 3.65 | V    |

| IVDD                               | VDD supply current                                                                 | Operating, 50% duty cycle                                                                 |      | 10     |      | mA   |

| IVDD                               | VDD supply current                                                                 | Idle, reset mode                                                                          |      | 6      |      | ША   |

| IGVDD_X                            | Gate supply current per half-bridge                                                | 50% duty cycle                                                                            |      | 8      |      | mA   |

| IGVDD_X                            | Gate supply current per half-bridge                                                | Reset mode                                                                                |      | 0.3    |      | ША   |

| IPVDD X                            | Half-bridge idle current                                                           | 50% duty cycle, without output filter or load                                             |      | 15     |      | mA   |

| 11 VDD_X                           | Trail-bridge fale current                                                          | Reset mode, no switching                                                                  |      | 500    |      | μΑ   |

| Output Stage MO                    | SFETs                                                                              |                                                                                           |      |        |      |      |

| R <sub>DSon,LS</sub>               | Drain-to-source resistance, LS                                                     | T <sub>J</sub> = 25°C, includes metallization resistance,<br>GVDD = 12 V                  |      | 90     |      | mΩ   |

| R <sub>DSon,HS</sub>               | Drain-to-source resistance, HS                                                     | T <sub>J</sub> = 25°C, includes metallization resistance,<br>GVDD = 12 V                  |      | 90     |      | mΩ   |

| I/O Protection                     |                                                                                    |                                                                                           |      |        |      |      |

| $V_{uvp,G}$                        | Undervoltage protection limit, GVDD_X                                              |                                                                                           |      | 8.5    |      | V    |

| V <sub>uvp,hyst</sub> (1)          |                                                                                    |                                                                                           |      | 400    |      | mV   |

| OTW <sup>(1)</sup>                 | Overtemperature warning                                                            |                                                                                           | 115  | 125    | 135  | °C   |

| OTW <sub>HYST</sub> <sup>(1)</sup> | Temperature drop needed below OTW temp. for OTW to be inactive after the OTW event |                                                                                           |      | 25     |      | °C   |

| OTE <sup>(1)</sup>                 | Overtemperature error                                                              |                                                                                           | 145  | 155    | 165  | °C   |

| OTE-OTW <sub>differential</sub>    | OTE-OTW differential                                                               |                                                                                           |      | 25     |      | °C   |

| OTE <sub>HYST</sub> (1)            | A reset needs to occur for $\overline{SD}$ for be released following an OTE event. |                                                                                           |      | 25     |      | °C   |

| OLPC                               | Overload protection counter                                                        | F <sub>PWM</sub> = 384 kHz                                                                |      | 1.3    |      | ms   |

| I <sub>oc</sub>                    | Overcurrent limit protection                                                       | Resistor—programmable, nominal, $R_{OCP} = 22 \text{ k}\Omega$                            |      | 12     |      | Α    |

| I <sub>OCT</sub>                   | Overcurrent response time                                                          | Time from application of short condition to Hi-Z of affected 1/2 bridge                   |      | 250    |      | ns   |

| R <sub>OCP</sub>                   | OC programming resistor range                                                      | Resistor tolerance = 5%                                                                   | 22   |        | 69   | kΩ   |

| R <sub>PD</sub>                    | Internal pulldown resistor at the output of each half-bridge                       | Connected when RESET is active to provide bootstrap capacitor charge. Not used in SE mode |      | 1.0    |      | kΩ   |

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

$R_L$ = 6  $\Omega$ ,  $F_{PWM}$  = 384 kHz, unless otherwise noted. All performance is in accordance with recommended operating conditions unless otherwise specified.

|                     | PARAMETER                                           | TEST CONDITIONS                  | DRV2900 |     |      | UNIT    |

|---------------------|-----------------------------------------------------|----------------------------------|---------|-----|------|---------|

|                     | PARAMETER                                           | TEST CONDITIONS                  | MIN     | TYP | MAX  | UNII    |

| Static Digital Spe  | cifications                                         |                                  |         |     |      |         |

| V <sub>IH</sub>     | High-level input voltage                            | PWM A, PWM B, RESET AB           | 2       |     |      | V       |

| V <sub>IL</sub>     | Low-level input voltage                             | FWWI_A, FWWI_B, RESET_AB         |         |     | 0.8  | V       |

| Leakage             | Input leakage current                               |                                  | -100    |     | 100  | μA      |

| OTW/SHUTDOWI        | N (SD)                                              |                                  |         |     |      |         |

| R <sub>INT_PU</sub> | Internal pullup resistance, OTW to VREG, SD to VREG |                                  | 20      | 26  | 35   | kΩ      |

| V                   | High-level output voltage                           | Internal pullup resistor         | 2.95    | 3.3 | 3.65 | V       |

| V <sub>OH</sub>     | nigri-level output voltage                          | External pullup of 4.7 kΩ to 5 V | 4.5     |     | 5    | V       |

| V <sub>OL</sub>     | Low-level output voltage                            | I <sub>O</sub> = 4 mA            |         | 0.2 | 0.4  | V       |

| FANOUT              | Device fanout OTW, SD                               | No external pullup               |         | 30  |      | Devices |

(1) Specified by design

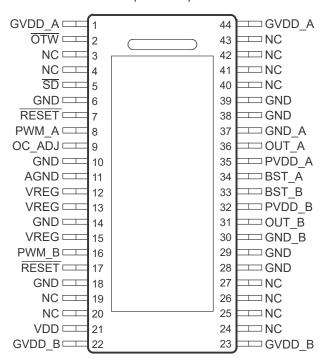

# **6.6 Typical Characteristics**

# 7 Detailed Description

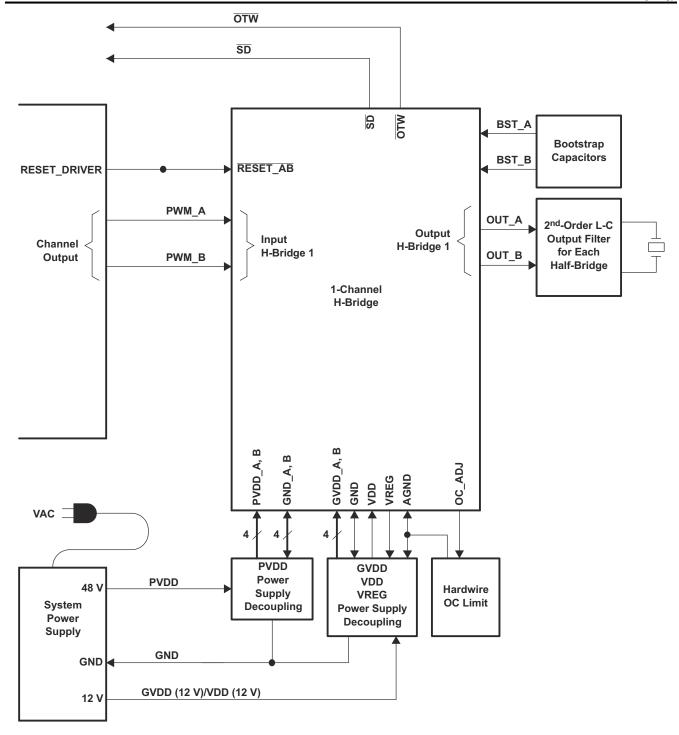

# 7.1 Block Diagrams

図 7-1. System Block Diagram

図 7-2. Functional Block Diagram

# 7.2 Feature Description

#### 7.2.1 Error Reporting

The  $\overline{SD}$  and  $\overline{OTW}$  pins are both active-low, open-drain outputs. Their function is for protection-mode signaling to a PWM controller or other system-control device.

Any fault resulting in device shutdown, such as overtemperatue shut down, overcurrent shut-down, or undervoltage protection, is signaled by the  $\overline{SD}$  pin going low. Likewise,  $\overline{OTW}$  goes low when the device junction temperature exceeds 125°C (see  $\gtrsim$  7-1).

表 7-1 Protection Mode Signal Descriptions

|    | ₹ 7-1.1 Totection Mode Signal Descriptions |                                                                                                                      |  |  |  |  |  |  |  |  |

|----|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| SD | OTW                                        | DESCRIPTION                                                                                                          |  |  |  |  |  |  |  |  |

| 0  | 0                                          | Overtemperature warning and (overtemperature shut down or overcurrent shut down or undervoltage protection) occurred |  |  |  |  |  |  |  |  |

| 0  | 1                                          | Overcurrent shut-down or GVDD undervoltage protection occurred                                                       |  |  |  |  |  |  |  |  |

| 1  | 0                                          | Overtemperature warning                                                                                              |  |  |  |  |  |  |  |  |

| 1  | 1                                          | Device under normal operation                                                                                        |  |  |  |  |  |  |  |  |

TI recommends monitoring the  $\overline{OTW}$  signal using the system microcontroller and responding to an  $\overline{OTW}$  signal by reducing the load current to prevent further heating of the device resulting in device overtemperature shutdown (OTSD).

To reduce external component count, an internal pullup resistor to internal VREG (3.3 V) is provided on both  $\overline{SD}$  and  $\overline{OTW}$  outputs. Level compliance for 5-V logic can be obtained by adding external pullup resistors to 5 V (see the *Electrical Characteristics* section of this data sheet for further specifications).

#### 7.2.2 Device Reset

Reset pin is provided for control of the H-bridge. When RESET\_AB is asserted low, the power-stage FETs in H-bridge are forced into a high-impedance (Hi-Z) state.

A rising-edge transition on reset input allows the device to resume operation after a shut-down fault and clears the fault and  $\overline{SD}$  pin.

#### 7.2.3 Device Protection System

#### 7.2.3.1 Overcurrent (OC) Protection With Current Limiting and Overload Detection

The device has independent, fast-reacting current detectors with programmable trip threshold (OC threshold) on all high-side and low-side power-stage FETs. See the following table for OC-adjust resistor values. The detector outputs are closely monitored by two protection systems. The first protection system controls the power stage in order to prevent the output current from further increasing, i.e., it performs a current-limiting function rather than prematurely shutting down during combinations of high-level transients and extreme load impedance drops. If the high-current situation persists, i.e., the power stage is being overloaded, a second protection system triggers a latching shutdown, resulting in the power stage being set in the high-impedance (Hi-Z) state. Current limiting and overload protection are independent for half-bridges A and B

- For the lowest-cost bill of materials in terms of component selection, the OC threshold measure should be limited, considering the power output requirement and minimum load impedance. Higher-impedance loads require a lower OC threshold.

- The demodulation-filter inductor must retain at least 5 µH of inductance at twice the OC threshold setting.

Unfortunately, most inductors have decreasing inductance with increasing temperature and increasing current (saturation). To some degree, an increase in temperature naturally occurs when operating at high output currents, due to core losses and the dc resistance of the inductor's copper winding. A thorough analysis of inductor saturation and thermal properties is strongly recommended.

Setting the OC threshold too low might cause issues such as lack of enough output power and/or unexpected shutdowns due to too-sensitive overload detection.

For added flexibility, the OC threshold is programmable within a limited range using a single external resistor connected between the OC\_ADJ pin and AGND. (See the *Electrical Characteristics* section of this data sheet for information on the correlation between programming-resistor value and the OC threshold.) It should be noted that a properly functioning overcurrent detector assumes the presence of a properly designed demodulation filter at the power-stage output. Short-circuit protection is not provided directly at the output pins of the power stage but only on the transducer terminals (after the demodulation filter). It is required to follow certain guidelines when selecting the OC threshold and an appropriate demodulation inductor:

| OC-Adjust Resistor Values (kΩ) | Max. Current Before OC Occurs (A) |  |  |  |  |

|--------------------------------|-----------------------------------|--|--|--|--|

| 22                             | 12.2                              |  |  |  |  |

| OC-Adjust Resistor Values (kΩ) | Max. Current Before OC Occurs (A) |

|--------------------------------|-----------------------------------|

| 27                             | 10.5                              |

| 47                             | 6.4                               |

| 68                             | 4.0                               |

| 100                            | 3.0                               |

#### 7.2.3.2 Overtemperature Protection

The DRV2901 has a two-level temperature-protection system that asserts an active-low warning signal ( $\overline{OTW}$ ) when the device junction temperature exceeds 125°C (nominal) and, if the device junction temperature exceeds 155°C (nominal), the device is put into thermal shutdown, resulting in all half-bridge outputs being set in the high-impedance (Hi-Z) state and  $\overline{SD}$  being asserted low. OTE is latched in this case and  $\overline{RESET\_AB}$  must be asserted low.

# 7.2.3.3 Undervoltage Protection (UVP) and Power-On Reset (POR)

The UVP and POR circuits of the DRV2901 fully protect the device in any power-up/down and brownout situation. While powering up, the POR circuit resets the overload circuit (OLP) and ensures that all circuits are fully operational when the GVDD\_X and VDD supply voltages reach 9.8 V (typical). Although GVDD\_X and VDD are independently monitored, a supply voltage drop below the UVP threshold on any VDD or GVDD\_X pin results in all half-bridge outputs immediately being set in the high-impedance (Hi-Z) state and  $\overline{\text{SD}}$  being asserted low. The device automatically resumes operation when all supply voltage on the bootstrap capacitors have increased above the UVP threshold.

Product Folder Links: DRV2901

# 8 Applications and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

# **8.1 Application Information**

The DRV2901 is a high performance lens cleaner transducer driver. This device requires two power supplies, at 12 V for GVDD and VDD, and 12 V to 48 V for PVDD. The DRV2901 does not require power-up sequencing due to internal power-on reset.

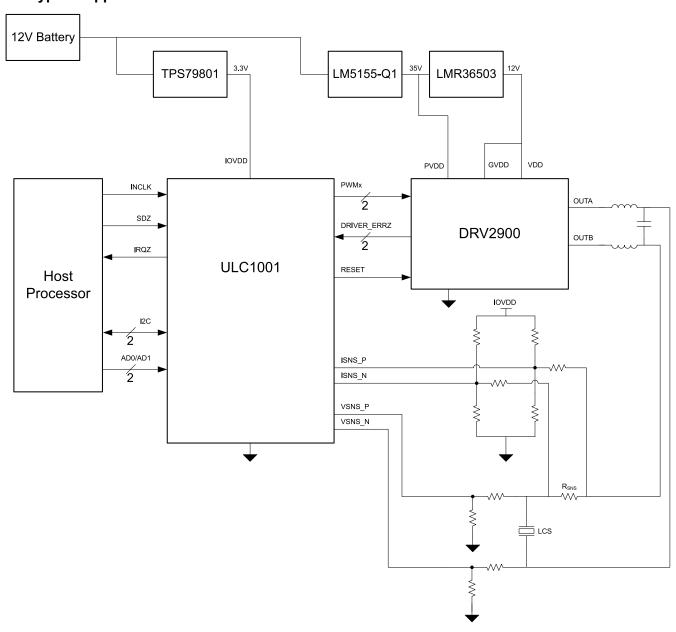

# 8.2 Typical Application

図 8-1. Typical System Diagram

# 9 Power Supply Recommendations

# 9.1 System Power-up/power-down Sequence

# 9.1.1 Powering Up

The DRV2901 does not require a power-up sequence. The outputs of the H-bridges remain in a highimpedance state until the gate-drive supply voltage (GVDD\_X) and VDD voltage are above the undervoltage protection (UVP) voltage threshold (see the *Electrical Characteristics* section of this data sheet). Although not specifically required, it is recommended to hold RESET\_AB in a low state while powering up the device. This allows an internal circuit to charge the external bootstrap capacitors by enabling a weak pulldown of the half-bridge output.

#### 9.1.2 Powering Down

The DRV2901 does not require a power-down sequence. The device remains fully operational as long as the gate-drive supply (GVDD\_X) voltage and VDD voltage are above the undervoltage protection (UVP) voltage threshold (see the *Electrical Characteristics* section of this data sheet). Although not specifically required, it is a good practice to hold RESET\_AB low during power down, thus preventing any artifacts.

#### 9.2 System Design Recommendations

#### 9.2.1 VDD Pin

The transient current in VDD pin could be significantly higher than average current through VDD pin. A low resistive path to GVDD should be used. A  $22-\mu F$  to  $47-\mu F$  capacitor should be placed on VDD pin beside the 100-nF to  $1-\mu F$  decoupling capacitor to provide a constant voltage during transient.

#### **9.2.2 VREG Pin**

The VREG pin is used for internal logic and should not be used as a voltage source for external circuitry. The capacitor on VREG pin should be connected to AGND.

#### 9.2.3 OTW Pin

OTW reporting indicates the device approaching high junction temperature. This signal can be used with MCU to decrease system power when OTW is low in order to prevent OT shut down at a higher temperature.

No external pull up resistor or 3.3 V power supply is needed for 3.3 V logic. The  $\overline{\text{OTW}}$  pin has an internal pullup resistor connecting to an internal 3.3 V to reduce external component count. For 5 V logic, an external pull up resistor to 5 V is needed.

# 10 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

www.ti.com 6-Sep-2023

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| DRV2901DDVR      | ACTIVE | HTSSOP       | DDV                | 44   | 2000           | RoHS & Green | NIPDAU                        | Level-3-260C-168 HR | 0 to 125     | DRV2901                 | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 5-Dec-2023

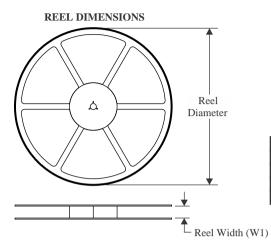

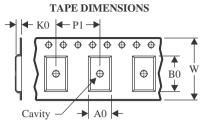

# TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

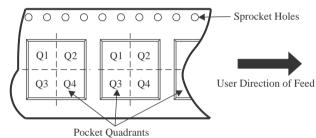

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| DRV2901DDVR | HTSSOP          | DDV                | 44 | 2000 | 330.0                    | 24.4                     | 8.6        | 15.6       | 1.8        | 12.0       | 24.0      | Q1               |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 5-Dec-2023

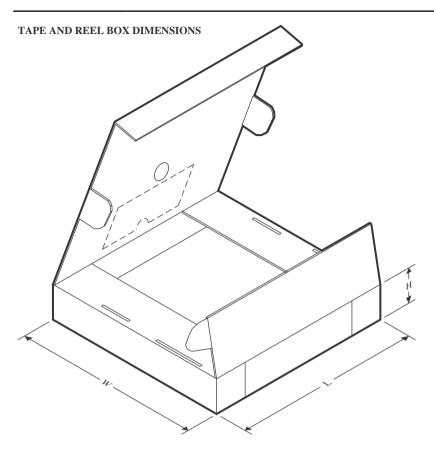

#### \*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DRV2901DDVR | HTSSOP       | DDV             | 44   | 2000 | 350.0       | 350.0      | 43.0        |

PLASTIC SMALL OUTLINE

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4206011/H

DDV (R-PDSO-G44) PowerPAD TM PLASTIC SMALL OUTLINE PACKAGE (DIE DOWN)

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

- D. This package is designed to be attached directly to an external heatsink. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="https://www.ti.com">http://www.ti.com</a>. See the product data sheet for details regarding the exposed thermal pad dimensions.

PowerPAD is a trademark of Texas Instruments.

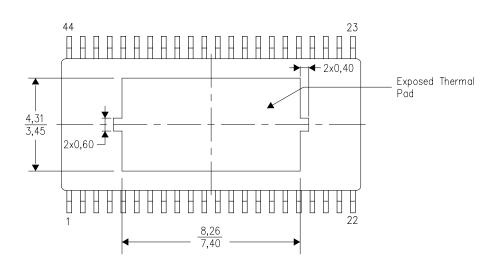

# DDV (R-PDSO-G44)

PowerPAD ™SMALL O<u>UTLINE PACKAGE</u>

# THERMAL INFORMATION

This PowerPAD<sup> $\mathbf{M}$ </sup> package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

4206975-4/D 07/11

Top View

Exposed Thermal Pad Dimensions

NOTE: All linear dimensions are in millimeters

PowerPAD is a trademark of Texas Instruments

# 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、TI の販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated