# LM3754 Scalable 2-Phase Synchronous Buck Controller with Integrated FET Drivers and Linear Regulator Controller

Check for Samples: LM3754

#### **FEATURES**

- Wide Input Voltage Range of 4.5V to 18V

- Up to 12 Channels for 300A Load

- System Accuracy Better Than 1%

- 0.6V to 3.6V Output Voltage Range

- Switching Frequency From 200 kHz to 1 MHz

- Phase Current Sharing ±12% Max Over Temperature

- Integrated 4.35V ±2.3% LDO

- Inductor DCR or Sense Resistor Current Sensing

- Interleaved Switching for Low I/O Ripple Current

- Integrated Synchronous NFET Drivers

- Programmable Soft-Start

- Pre-Biased Startup

- Output Voltage Differential Remote Sensing

- Minimum Controllable On-Time of Only 50 ns

- Programmable Enable and Input UVLO

- Power Good flag

- OVP, UVP and Hiccup Over-Current Protection

#### **APPLICATIONS**

- CPUs, GPUs (Graphic Cards), ASICs, FPGAs, Large Memory Arrays, DDR

- High Current POL Converters

- · Networking Systems

- Power Distribution Systems

- Telecom/Datacom DC/DC Converters

- Desktops, Servers and Workstations

#### **DESCRIPTION**

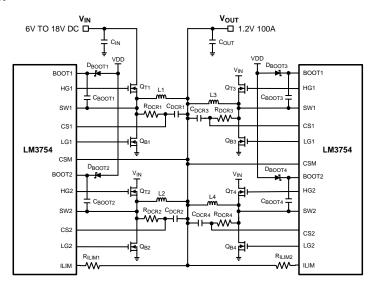

The LM3754 is a full featured single-output dualphase voltage-mode synchronous PWM buck controller. It can be configured to control from 2 to 12 interleaved power stages creating a single high power output. This controller utilizes voltage-mode control with input voltage feed-forward for high noise immunity. An internal average current loop forces real time current sharing between phases during load transients.

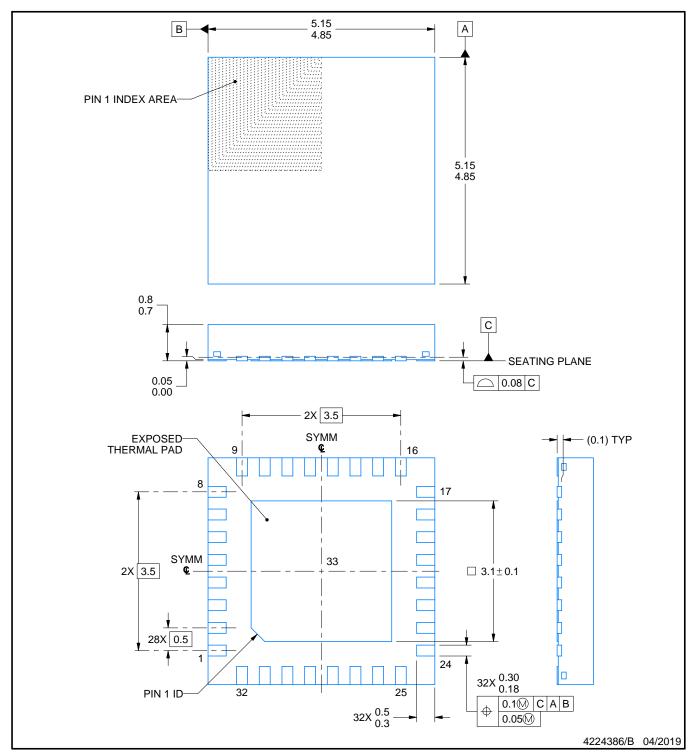

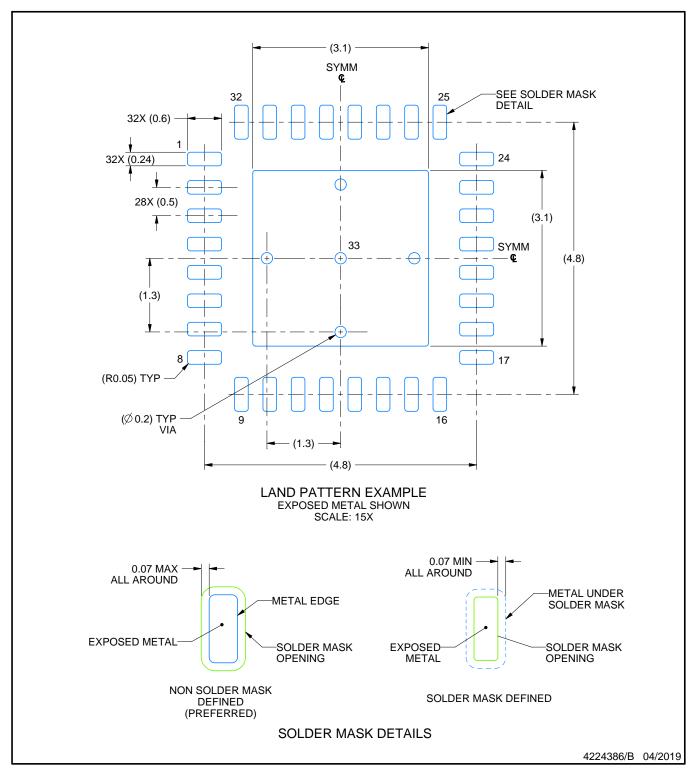

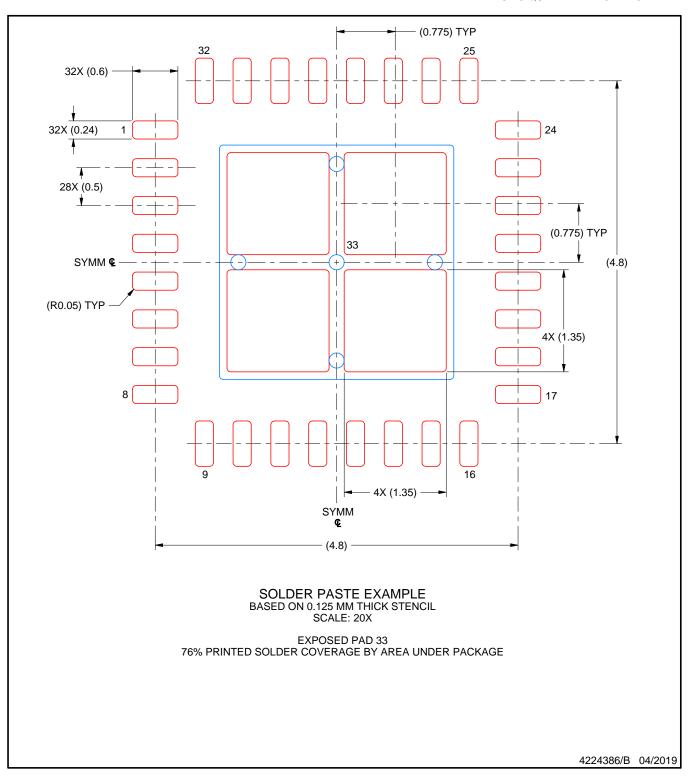

The LM3754 supports adjustable Soft-Start. The Soft-Start function can only drive the output upwards – it will not pull it down, therefore, pre-biased loads will not be discharged. Available in the 5 mm x 5 mm thermally enhanced 32-lead WQFN package with a thermal pad.

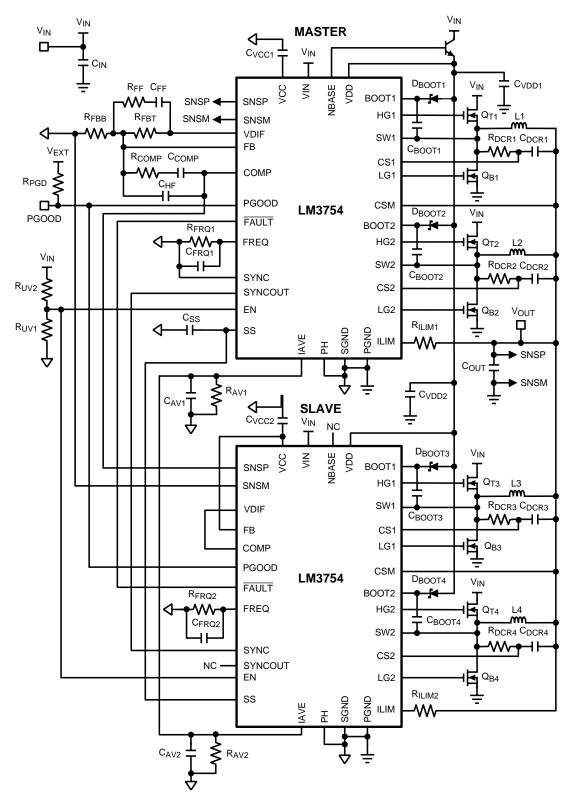

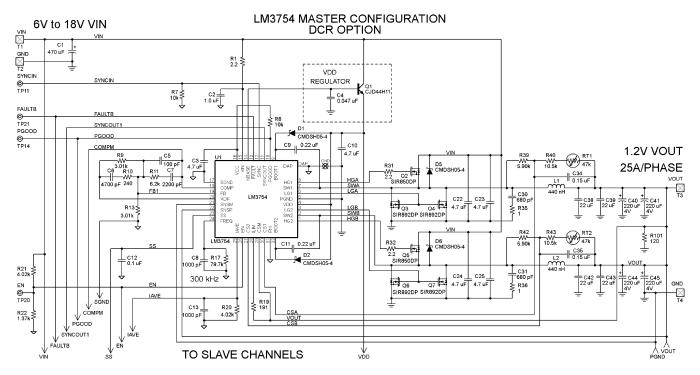

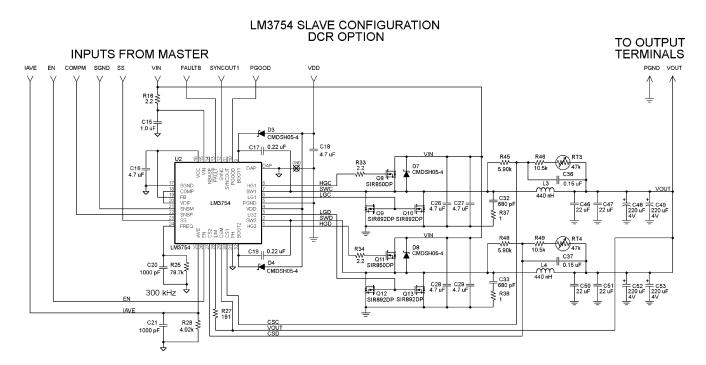

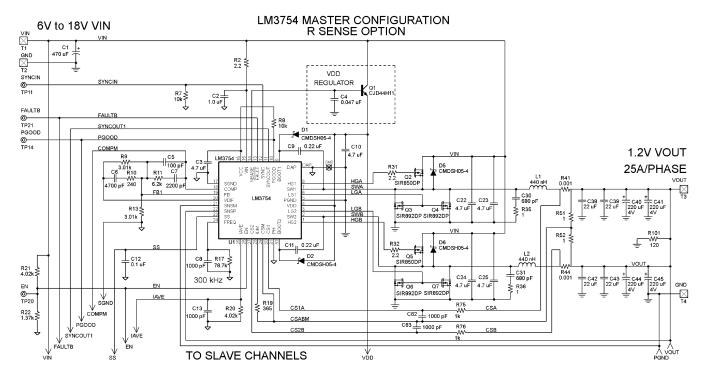

#### **Simplified Application**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

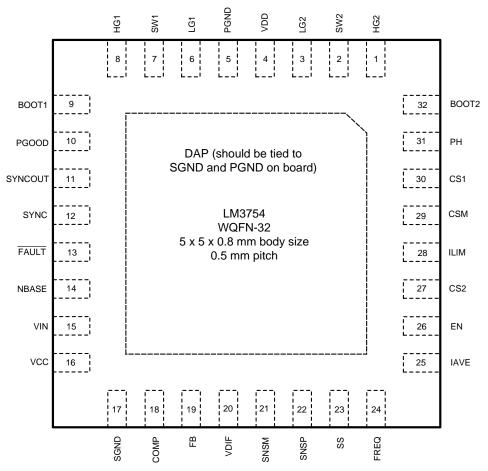

#### **Connection Diagram**

Figure 1. Top View 32-Lead WQFN

#### **Pin Descriptions**

| Pin Number | Pin Name | Description                                                                                                                                                                                                                                                                                    |  |  |  |

|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1          | HG2      | Gate drive of the high-side N-channel MOSFET for Phase 2.                                                                                                                                                                                                                                      |  |  |  |

| 2          | SW2      | Switching node of the power stage of Phase 2.                                                                                                                                                                                                                                                  |  |  |  |

| 3          | LG2      | Gate drive of the low-side N-channel MOSFETs for Phase 2.                                                                                                                                                                                                                                      |  |  |  |

| 4          | VDD      | Power supply for gate drivers. Decouple VDD to PGND with a ceramic capacitor. VDD can either be supplied by an external 5V ±10% bus, or by the internal regulator, which uses an external NPN pass device. If using the internal regulator, connect VDD to the emitter of the NPN pass device. |  |  |  |

| 5          | PGND     | Power Ground. Tie PGND and SGND together on the board through the DAP.                                                                                                                                                                                                                         |  |  |  |

| 6          | LG1      | Gate drive of the low-side N-channel MOSFETs for Phase 1.                                                                                                                                                                                                                                      |  |  |  |

| 7          | SW1      | witching node of the power stage of Phase 1.                                                                                                                                                                                                                                                   |  |  |  |

| 8          | HG1      | Gate drive of the high-side N-channel MOSFET for Phase 1.                                                                                                                                                                                                                                      |  |  |  |

| 9          | BOOT1    | Bootstrap of Phase 1 for the high-side gate drive power supply.                                                                                                                                                                                                                                |  |  |  |

| 10         | PGOOD    | Power Good open-drain output. Active HIGH.                                                                                                                                                                                                                                                     |  |  |  |

| 11         | SYNCOUT  | Synchronization Output. For multi-controller systems this pin should be connected to the SYNC pin of the next controller in daisy-chain configuration                                                                                                                                          |  |  |  |

## Pin Descriptions (continued)

| Pin Number | Pin Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12         | SYNC     | Synchronization Input. SYNCOUT of one controller is connected to SYNC of the next controller in a daisy-chain fashion. To synchronize the whole chain of controllers to an external clock, wire the externa clock to the SYNC pin of the first controller of the chain (called the Master controller). Otherwise, connect the SYNC input of the Master controller to ground and all of the controllers will be controlled by the internal oscillator of the Master. |

| 13         | FAULT    | Input/Output. Wire the FAULT pin of all controllers together. FAULT gets pulled Low during startup, an over-current fault, or an over-voltage fault. FAULT = Low signals all controllers to stop switching and prepare for the next startup sequence. The first LM3754 in the system (the Master) supplies the FAULT pin pull-up current for all of the controllers.                                                                                                |

| 14         | NBASE    | Connect to the base of external series-pass NPN if using the LM3754 internal LDO controller to generate VDD. Otherwise leave unconnected.                                                                                                                                                                                                                                                                                                                           |

| 15         | VIN      | Input Voltage. Connect VIN to the input supply rail used to supply the power stages. This input is used to provide the feed-forward for the voltage control of V <sub>OUT</sub> and for generating the internal VCC voltage.                                                                                                                                                                                                                                        |

| 16         | VCC      | Supply for internal control circuitry. Decouple VCC to PGND with a ceramic capacitor. When VIN > 5.5V the internal LDO will supply 4.35V to this pin. When 4.5V < VIN < 5.5V, connect VIN to VCC. In this case the internal VCC LDO will turn off and VCC current will be supplied directly by VIN.                                                                                                                                                                 |

| 17         | SGND     | Signal Ground. Tie PGND and SGND together on the board through the DAP.                                                                                                                                                                                                                                                                                                                                                                                             |

| 18         | COMP     | Error Amplifier Output. For the Master, a compensation network is placed between the COMP pin and the FB pin. The COMP pin of the Master should be connected to the SNSP pin of each of the Slaves. The COMP pin of each of the Slaves must be connected to its VDIF pin                                                                                                                                                                                            |

| 19         | FB       | Feedback Input. This is the inverting input of the error amplifier. Connect the Master FB pin to the output voltage divider and compensation network. Connect each Slave FB pin to its own VCC pin. This will put that controller in Slave mode and disable its error amplifier.                                                                                                                                                                                    |

| 20         | VDIF     | Output of the remote-sense differential amplifier. Connect the Master VDIF pin to the output voltage divider and compensation network. The Slave differential amplifier is used to buffer COMP from the Master controller. Connect each Slave VDIF pin to its own COMP pin.                                                                                                                                                                                         |

| 21         | SNSM     | Inverting input of the remote-sense differential amplifier. Connect SNSM of the Master controller to PGND at the load point. On Slave controllers, the differential amplifier is used to buffer COMP from the Master controller. Connect SNSM of each Slave controller directly to the Master controller SGND pin.                                                                                                                                                  |

| 22         | SNSP     | Non-inverting input of the remote-sense differential amplifier. Connect the SNSP of the Master controller to $V_{\text{OUT}}$ at the load point. On Slave controllers, the differential amplifier is used to buffer COMP of the Master controller. Connect SNSP of each Slave controller to the Master controller COMP pin.                                                                                                                                         |

| 23         | SS       | Soft-Start. Connect the SS pins of all of the controllers in the system together. At the Master controller, connect a soft-start capacitor between SS and SGND. Only the Master controller supplies the pull up current to the SS capacitor.                                                                                                                                                                                                                        |

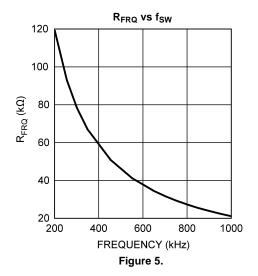

| 24         | FREQ     | Frequency Adjust. A frequency adjust resistor and decoupling capacitor are connected between FREQ and SGND to program the switching frequency between 200 kHz to 1 MHz (each phase). These components must be supplied on the Master and Slaves, even if the system is synchronized to an external clock.                                                                                                                                                           |

| 25         | IAVE     | Current Averaging. Connect a $4.02~k\Omega$ , 1%, resistor between each controller's IAVE pin and SGND. In the case where one phase is not used, connect an $8.06~k\Omega$ resistor. Connect a filter capacitor between IAVE and SGND at each controller,                                                                                                                                                                                                           |

| 26         | EN       | Enable Input. Used for VIN UVLO function, connect EN to the midpoint of a voltage divider from VIN to SGND. The EN pins of all controllers must be wired together. For an on/off EN function, wire the EN pins of all controllers together and control with an open drain output.                                                                                                                                                                                   |

| 27         | CS2      | Positive current-sense input of Phase 2. Connect to the DCR network or the current-sense resistor of Phase 2. The negative current-sense input is the CSM pin.                                                                                                                                                                                                                                                                                                      |

| 28         | ILIM     | Current Limit Set. Connect a resistor between ILIM and CSM. The resistance between ILIM and CSM programs the current limit.                                                                                                                                                                                                                                                                                                                                         |

| 29         | CSM      | Negative current-sense input of the internal current-sense amplifiers. Connect to V <sub>OUT</sub> .                                                                                                                                                                                                                                                                                                                                                                |

| 30         | CS1      | Positive current-sense input of Phase 1. Connect to the DCR network or the current-sense resistor of Phase 1. The negative current-sense input is the CSM pin.                                                                                                                                                                                                                                                                                                      |

| 31         | PH       | Phase Select Input. Connect this pin to the middle of a resistor divider between VCC and SGND to program the number of phases in the system.                                                                                                                                                                                                                                                                                                                        |

| 32         | BOOT2    | Bootstrap pin of Phase 2 for the high-side gate drive power supply.                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | DAP      | Die Attach Pad. Must be connected to PGND and SGND but cannot be used as the primary ground connection; do not place any traces or vias other than GND in the outer layer under the DAP; see application note AN-1187 (literature number SNOA401).                                                                                                                                                                                                                  |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

Absolute Maximum Ratings (1)(2)

| Absolute Maximum Natings                                   |                                                |

|------------------------------------------------------------|------------------------------------------------|

| VIN to SGND, PGND                                          | -0.3V to 24V                                   |

| SGND to PGND                                               | -0.3V to 0.3V                                  |

| VCC and VDD to VIN                                         | +0.3V                                          |

| VDD to PGND                                                | -0.3V to 6V                                    |

| PGOOD, FAULT to SGND                                       | -0.3V to 6V                                    |

| VCC, EN, SS, SYNC, CS1, CS2, CSM, ILIM, SNSM, SNSP to SGND | -0.3V to 6V                                    |

| FREQ, PH, FB to SGND                                       | -0.3 to VCC + 0.3V                             |

| BOOT1, BOOT2 to PGND <sup>(3)</sup>                        | -0.3V to 24V Peak                              |

| SW1, SW2 to PGND <sup>(3)</sup>                            | -0.3VDC to 24V Peak<br>-3V for less than 40 ns |

| BOOT1 to SW1,<br>BOOT2 to SW2 <sup>(3)</sup>               | -0.3V to 6.0V Peak                             |

| SYNCOUT                                                    | ±20 mA                                         |

| PGOOD, FAULT                                               | ±20 mA                                         |

| VDIF                                                       | ±5 mA                                          |

| COMP                                                       | ±4 mA                                          |

| ESD Rating, HBM <sup>(4)</sup>                             | 2 kV                                           |

| Junction Temperature (T <sub>J-MAX</sub> )                 | +150°C                                         |

| Storage Temperature Range                                  | −65°C to +150°C                                |

|                                                            |                                                |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. Operating Range conditions indicate the conditions at which the device is functional and the device should not be operated beyond such conditions. For ensured specifications and conditions, see the Electrical Characteristics table.

- (2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

- (3) Peak is the dc plus transient voltage including switching spikes.

- (4) Human Body Model (HBM) is a 100 pF capacitor discharged through a 1.5 kΩ resistor into each pin. Applicable standard is JESD22-A114C. All pins pass 2 kV HBM except VDD, VIN and VCC which are rated for 1.5 kV.

## Operating Ratings<sup>(1)</sup>

| 4.5V to 5.5V    |

|-----------------|

| 5.5V to 18V     |

| 6V to 18V       |

| 4.5V to 5.5V    |

| 4.5V to 5.5V    |

| 0.6V to 3.6V    |

| 0V to 5.5V      |

| -0.25V to 1.0V  |

| 0V to 3.6V      |

| 0V to 1.15V     |

| −15 mV to 45 mV |

| 0V to 3.6V      |

| 0V to 200 mV    |

| −5°C to +125°C  |

|                 |

<sup>(1)</sup> Absolute Maximum Ratings indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. Operating Range conditions indicate the conditions at which the device is functional and the device should not be operated beyond such conditions. For ensured specifications and conditions, see the Electrical Characteristics table.

## Operating Ratings<sup>(1)</sup> (continued)

| Thermal Data                                                                              |          |

|-------------------------------------------------------------------------------------------|----------|

| Junction-to-Ambient Thermal Resistance (θ <sub>JA</sub> ), WQFN-32 Package <sup>(2)</sup> | 26.4°C/W |

(2) Tested on a four layer JEDEC board. Four vias provided under the exposed pad. See JEDEC standards JESD51-5 and JESD51-7.

#### **Electrical Characteristics**

Limits in standard type are for  $T_J$  = 25°C only; limits in boldface type apply over the junction temperature ( $T_J$ ) range of -5°C to +125°C. Minimum and Maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J$  = 25°C, and are provided for reference purposes only. Unless otherwise stated  $V_{VIN}$  = 12V,  $V_{VDD}$  = 5V,  $V_{VCC}$  = internal LDO,  $V_{EN}$  = 2V,  $R_{FRQ}$  = 78.7 k $\Omega$ ,  $V_{PH}$  = 0V,  $V_{CS1}$  =  $V_{CS2}$  =  $V_{CSM}$  =  $V_{SS}$  =  $V_{SNSP}$  = 1.8V,  $V_{ILIM}$  -  $V_{CSM}$  = 100 mV,  $V_{SNSM}$  =  $V_{SYNC}$  = 0V,  $V_{SYNCOUT}$  floating.

| Symbol                 | Parameter                                                      | Conditions                                                                                                | Min   | Тур    | Max  | Units |

|------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------|--------|------|-------|

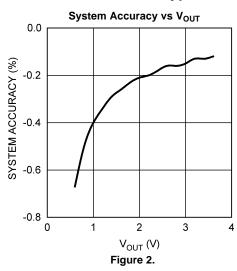

| System Accur           | acy                                                            |                                                                                                           |       |        |      |       |

| V <sub>OUT</sub>       | Output Voltage Accuracy                                        | V <sub>OUT</sub> = 3.6V                                                                                   | -0.65 | -0.11  | 0.45 | %     |

|                        | Includes trimmed EA and diff amplifier offset and gain errors; | V <sub>OUT</sub> = 2.5V                                                                                   | -0.75 | -0.134 | 0.6  | %     |

|                        | 0.5 mA load at VDIF                                            | V <sub>OUT</sub> = 1.8V                                                                                   | -0.9  | -0.165 | 0.7  | %     |

|                        |                                                                | V <sub>OUT</sub> = 0.6V                                                                                   | -2.25 | -0.4   | 1.25 | %     |

| Phase Current          | t Equalization                                                 |                                                                                                           | ·     | •      | •    | •     |

| ΔI <sub>PH</sub>       | Current Equalization (from average per phase current)          | $V_{CSM} = 1.8V, V_{CS1} = V_{CS2} = V_{CSM} + 30 \text{ mV}, V_{IAVE} = 740 \text{ mV}, V_{COMP} = 1.9V$ | -12   |        | 12   | %     |

| System Suppl           | ies and UVLO                                                   |                                                                                                           |       |        |      |       |

| VIN                    |                                                                |                                                                                                           |       |        |      |       |

| $I_{VIN}$              | VIN Operating Current                                          | 2-phase switching gate drivers unloaded                                                                   |       | 15     |      | mA    |

| $I_{VIN-Q}$            | VIN Quiescent Current                                          | V <sub>FB</sub> = 650 mV, no PWM switching,<br>NBASE is floating (no NPN)                                 |       | 9      | 18   | mA    |

| I <sub>VIN-SD</sub>    | VIN Shutdown Current                                           | V <sub>EN</sub> = 0V                                                                                      |       | 200    | 450  | μΑ    |

| VCC                    |                                                                |                                                                                                           |       |        |      |       |

| V <sub>VCC</sub>       | VCC Linear Regulator Output<br>Voltage                         | 0 to 3 mA sourced to an external load;<br>V <sub>VIN</sub> = 5.5V to 18V                                  | 4.25  | 4.35   | 4.45 | V     |

| I <sub>VCC</sub>       | VCC Input Current from External Supply                         | V <sub>VIN</sub> = 5.5V, V <sub>VCC</sub> = 5.5V                                                          |       | 10     | 20   | mA    |

| I <sub>VCC-SD</sub>    | VCC Input Shutdown Current from External Supply                | $V_{EN} = 0V, V_{VIN} = 12V, V_{VCC} = 5V$                                                                |       | 260    |      | μA    |

| I <sub>VCC-LIM</sub>   | VCC Output Current Limit                                       | V <sub>VCC</sub> = 2.5V                                                                                   | 9     | 30     | 53   | mA    |

|                        |                                                                | V <sub>VCC</sub> = 0V                                                                                     |       | 50     |      |       |

| V <sub>VCC-EN</sub>    | VCC UVLO Thresholds                                            | V <sub>VCC</sub> Rising                                                                                   | 4.04  | 4.14   | 4.24 | V     |

|                        |                                                                | V <sub>VCC</sub> Falling                                                                                  | 3.9   | 4      | 4.1  |       |

| V <sub>VCC-HYS</sub>   | VCC Threshold Hysteresis                                       |                                                                                                           |       | 140    |      | mV    |

| t <sub>D-VCC</sub>     | VCC UVLO/UVP Debounce Time                                     |                                                                                                           |       | 8      |      | μs    |

| VDD, NBASE,            | BOOT1, BOOT2, SW1, SW2                                         |                                                                                                           |       |        |      |       |

| $V_{VDD}$              | VDD Controller Regulation<br>Voltage                           | V <sub>VIN</sub> = 6V to 18V                                                                              | 4.6   | 4.85   | 5.1  | V     |

| V <sub>NBASE</sub>     | VIN-to-NBASE Dropout                                           | V <sub>VIN</sub> = 5.5V, 700 mV source connected from VDD to NBASE, I <sub>NBASE</sub> = 5 mA             |       | 330    |      | mV    |

|                        |                                                                | V <sub>VIN</sub> - 5.5V, 700 mV source connected from VDD to NBASE, I <sub>NBASE</sub> = 1 mA             |       | 130    |      |       |

| V <sub>NBASE-REG</sub> | NBASE Load Regulation                                          | V <sub>VIN</sub> = 18V, 700 mV source connected from VDD to NBASE, I <sub>NBASE</sub> steps 1 mA to 5 mA  |       | 4      |      | mV    |

| $I_{VDD}$              | VDD Operating Current from<br>External Power Supply            | $V_{VDD} = V_{VIN} = V_{VCC} = 5.5V$ , $f_{SW} = 300$ kHz, Gate Drivers unloaded                          |       | 1      |      | mA    |

| I <sub>VDD-SD</sub>    | VDD Shutdown Current                                           | V <sub>EN</sub> = 0V, V <sub>VIN</sub> = 12V, V <sub>VDD</sub> = 5V                                       |       | 2      | 30   | μΑ    |

| I <sub>NBASE-CL</sub>  | NBASE Current Limit                                            | $V_{NBASE} = V_{VDD} + 0.7V$ , $\Delta V_{VDD} = -100 \text{ mV}$                                         | 5.8   | 10     |      | mA    |

|                        |                                                                | $V_{NBASE} = V_{VDD} = 0V$                                                                                |       | 20     |      |       |

Limits in standard type are for  $T_J$  = 25°C only; limits in boldface type apply over the junction temperature ( $T_J$ ) range of -5°C to +125°C. Minimum and Maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J$  = 25°C, and are provided for reference purposes only. Unless otherwise stated  $V_{VIN}$  = 12V,  $V_{VDD}$  = 5V,  $V_{VCC}$  = internal LDO,  $V_{EN}$  = 2V,  $V_{FRQ}$  = 78.7 k $\Omega$ ,  $V_{PH}$  = 0V,  $V_{CS1}$  =  $V_{CS2}$  =  $V_{CSM}$  =  $V_{SS}$  =  $V_{SNSP}$  = 1.8V,  $V_{ILIM}$  -  $V_{CSM}$  = 100 mV,  $V_{SNSM}$  =  $V_{SYNC}$  = 0V,  $V_{SYNCOUT}$  floating.

| Symbol                | Parameter                                          | Conditions                                                                          | Min   | Тур   | Max   | Units |

|-----------------------|----------------------------------------------------|-------------------------------------------------------------------------------------|-------|-------|-------|-------|

| I <sub>BOOT-SD</sub>  | BOOT1, BOOT2 Shutdown<br>Current                   | $V_{EN} = 0V, V_{SW1(2)} = 0V, V_{BOOT} - V_{SW} = 5V$                              |       | 4.5   | 15    | μA    |

| I <sub>BOOT</sub>     | BOOT1, BOOT2 Operating<br>Current                  |                                                                                     |       | 650   |       | μΑ    |

| I <sub>SW</sub>       | SW1, SW2 Leakage Current with<br>Pre-Biased Output | $V_{VCC} = 0V, V_{EN} = 0V, V_{SW1(2)} = 3.6V$                                      |       | 3     |       | μA    |

| $V_{VDD-TH}$          | VDD UVLO Thresholds                                | V <sub>VDD</sub> Rising                                                             | 3.8   | 4.02  | 4.28  | V     |

|                       |                                                    | V <sub>VDD</sub> Falling                                                            | 3.37  | 3.71  | 4.03  | V     |

| V <sub>VDD-HYS</sub>  | VDD UVLO/UVP Hysteresis                            |                                                                                     |       | 310   |       | mV    |

| t <sub>D-VDD</sub>    | VDD UVLO/UVP Debounce Time                         |                                                                                     |       | 11    |       | μs    |

| Thermal Shutd         | lown                                               |                                                                                     | 11    |       | Ш     |       |

| T <sub>J-SD</sub>     | Thermal Shutdown Threshold                         | Rising                                                                              |       | 160   |       | °C    |

| T <sub>J-HYS</sub>    | Thermal Shutdown Threshold Hysteresis              |                                                                                     |       | 30    |       | °C    |

| EN                    |                                                    |                                                                                     |       |       | +     |       |

| V <sub>EN-H</sub>     | HIGH Level Input Voltage                           |                                                                                     | 1.51  |       |       | V     |

| V <sub>EN-L</sub>     | LOW Level Input Voltage                            |                                                                                     |       |       | 1.14  | V     |

| V <sub>EN-TH</sub>    | EN Threshold                                       | V <sub>VIN</sub> = 4.5V to 18V, V <sub>VCC</sub> = 4.5V (Rising)                    | 1.26  | 1.39  | 1.51  | V     |

|                       |                                                    | $V_{VIN} = 4.5V$ to 18V, $V_{VCC} = 4.5V$ (Falling)                                 | 1.14  | 1.25  | 1.35  | V     |

| V <sub>EN-HYS</sub>   | EN Threshold Hysteresis                            |                                                                                     |       | 140   |       | mV    |

| I <sub>EN</sub>       | EN Input Bias Current                              | V <sub>EN</sub> = 1.5V                                                              |       | 0.1   |       | μA    |

|                       |                                                    | V <sub>EN</sub> = 1.0V                                                              |       | 0.4   | 1.7   | 1     |

| Reference, Fee        | edback & Error Amplifier: FB, COI                  |                                                                                     |       |       | 1     |       |

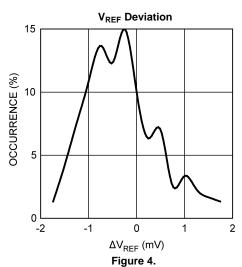

| V <sub>FB</sub>       | FB Voltage Under Regulation                        | V <sub>COMP</sub> = 1.8V                                                            | 0.593 | 0.599 | 0.605 | V     |

| V <sub>FB-REG1</sub>  | FB Voltage VIN Line Regulation                     | V <sub>VIN</sub> = 5.5V to 18V                                                      |       | ±0.01 |       | %     |

| V <sub>FB-REG2</sub>  | FB Voltage VCC Line Regulation                     | V <sub>VCC</sub> = V <sub>VIN</sub> = V <sub>VDD</sub> = 4.5V to 5.5V (same source) |       | ±0.15 |       | %     |

| I <sub>FB</sub>       | FB Input Bias Current                              | ,                                                                                   |       | 45    | 130   | nA    |

| V <sub>FB-PTH</sub>   | FB Pin Master/Slave<br>Programming Threshold       |                                                                                     |       | 3.2   |       | V     |

| A <sub>OL</sub>       | DC Gain                                            | FB to COMP, V <sub>COMP</sub> = V <sub>FB</sub> + 1.0V                              |       | 70    |       | dB    |

| f <sub>BW</sub>       | Error Amplifier<br>Unity Gain Bandwidth            | $R_{COMP-SGND} = 1.5 \text{ k}\Omega, C_{COMP-SGND} = 50 \text{ pF}$                |       | 15    |       | MHz   |

| $V_{COMP-SLEW}$       | Error Amplifier Slew Rate                          |                                                                                     |       | 6     |       | V/µS  |

| V <sub>COMP-REG</sub> | COMP Load Regulation,<br>Sourcing                  | $V_{COMP}$ = 2.7V, $\Delta I_{COMP}$ = +1 mA, DC Gain = 40                          |       | -3    |       | mV    |

| PWM Ramp an           | d Input Voltage Feed-Forward                       |                                                                                     | •     |       | •     |       |

| D <sub>MAX</sub>      | Maximum Duty Cycle Controlled by Clock             | $V_{VIN} = 6V$ , $V_{COMP} = 3.5V$                                                  | 81    |       |       | %     |

| D <sub>FF</sub>       | Duty Cycle Controlled by VIN Feed-Forward          | $V_{VIN} = 9V$ , $V_{COMP} = 2.2V$                                                  |       | 42    |       | %     |

| t <sub>ON-MIN</sub>   | Minimum Controllable On-Time                       |                                                                                     |       | 50    |       | ns    |

| V <sub>RAMP-MIN</sub> | PWM Ramp Range                                     | Ramp Minimum                                                                        |       | 1.3   |       | ٧     |

| V <sub>RAMP-MAX</sub> |                                                    | Ramp Maximum                                                                        |       | 2.8   |       | V     |

|                       |                                                    |                                                                                     |       |       |       |       |

Submit Documentation Feedback

Copyright © 2012–2013, Texas Instruments Incorporated

Limits in standard type are for  $T_J$  = 25°C only; limits in boldface type apply over the junction temperature ( $T_J$ ) range of -5°C to +125°C. Minimum and Maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J$  = 25°C, and are provided for reference purposes only. Unless otherwise stated  $V_{VIN}$  = 12V,  $V_{VDD}$  = 5V,  $V_{VCC}$  = internal LDO,  $V_{EN}$  = 2V,  $V_{FRQ}$  = 78.7 k $\Omega$ ,  $V_{PH}$  = 0V,  $V_{CS1}$  =  $V_{CS2}$  =  $V_{CSM}$  =  $V_{SS}$  =  $V_{SNSP}$  = 1.8V,  $V_{ILIM}$  -  $V_{CSM}$  = 100 mV,  $V_{SNSM}$  =  $V_{SYNC}$  = 0V,  $V_{SYNCOUT}$  floating.

| Symbol                   | Parameter                                                                           | Conditions                                                                                                       | Min   | Тур  | Max   | Units            |

|--------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------|------|-------|------------------|

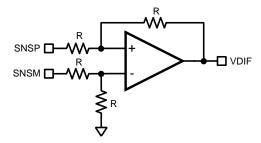

| Differential Am          | plifier: SNSP, SNSM, VDIF                                                           |                                                                                                                  | ,     |      |       |                  |

| V <sub>OS-INPUT</sub>    | Input Offset Voltage                                                                | V <sub>SNSP</sub> = 1.8V                                                                                         |       | 3    |       | mV               |

| R <sub>INPUT-SNSP</sub>  | Input Resistance of SNSP                                                            |                                                                                                                  |       | 30   |       | kΩ               |

| A <sub>V-DIF</sub>       | Gain                                                                                | V <sub>SNSP</sub> = 0.6V to 3.6V                                                                                 | 0.996 | 1    | 1.004 | V/V              |

| f <sub>BW-DIF</sub>      | 3dB Bandwidth                                                                       |                                                                                                                  |       | 2    |       | MHz              |

| V <sub>DIF-REG1</sub>    | VDIF Load Regulation, Sourcing                                                      | V <sub>VDIF</sub> = 3.6V, I <sub>VDIF</sub> = 0.5 mA                                                             | -3    |      |       | mV               |

| V <sub>DIF-REG2</sub>    | VDIF Load Regulation, Sourcing                                                      | V <sub>VDIF</sub> = 0.6V, I <sub>VDIF</sub> = 0.5 mA                                                             | -3    |      |       | mV               |

| Current-Sense            | , Current Limit and Hiccup Mode:                                                    | CS1, CS2, CSM, ILIM                                                                                              | l.    |      | Ш     |                  |

| V <sub>CS-OS</sub>       | Current-Sense Input Offset<br>Voltage Range, V <sub>CS1(2)</sub> – V <sub>CSM</sub> | V <sub>OUT</sub> = 1.8V                                                                                          |       | ±2   |       | mV               |

| I <sub>CS</sub>          | CS1, CS2 Input Bias Current                                                         | $V_{CSM}$ = 3.6V, $V_{CS1(2)}$ – $V_{CSM}$ = -15 mV and +40 mV                                                   | -200  |      | 200   | nA               |

|                          |                                                                                     | $V_{CSM}$ = 0.6V, $V_{CS1(2)}$ – $V_{CSM}$ = -15 mV and +40 mV                                                   | -450  |      | 450   | nA               |

| I <sub>CSM</sub>         | CSM Input Source Bias Current                                                       | $V_{CSM}$ = 0.6V and 3.6V, $V_{CS1(2)}$ – $V_{CSM}$ = 40 mV                                                      |       | 150  | 240   | μA               |

| I <sub>CSL</sub>         | CS1+ CS2 + CSM + ILIM<br>Leakage Current with Pre-Biased<br>Output                  | $ \begin{array}{l} V_{VCC} = 0V, \ V_{EN} = 0V, \ V_{CSM} = V_{CS1} = V_{CS2} = \\ V_{ILIM} = 3.6V \end{array} $ |       | 0.1  |       | μА               |

| f <sub>BW-CS</sub>       | 3dB Bandwidth, CS1(2) to PWM COMPARATOR Input                                       |                                                                                                                  |       | 1.0  |       | MHz              |

| I <sub>ILIM-SOURCE</sub> | ILIM Source Current                                                                 | V <sub>ILIM</sub> = 0.6V to 3.6V, V <sub>VIN</sub> = 5.5V                                                        | 85    | 94   | 103   | μΑ               |

| V <sub>CL</sub>          | Current Limit Threshold Voltage V <sub>ILIM</sub> – V <sub>CS1(2)</sub>             | $V_{ILIM} = 0.6V$ to 3.6V, $V_{VIN} = 5.5V$                                                                      | -2.5  | 0    | 4.6   | mV               |

| t <sub>D-CL</sub>        | Current Limit Comparator<br>Propagation Delay                                       | V <sub>CS1</sub> or V <sub>CS2</sub> stepped from 0.9V to 1.1V, V <sub>ILIM</sub> = 1V                           |       | 200  |       | ns               |

| t <sub>D-ILIM</sub>      | Master or Slave Fast Current<br>Limit Delay                                         | $V_{FB}$ = 280 mV, 1-phase over-current:<br>$V_{CS1}$ OR $V_{CS2}$ > $V_{ILIM}$                                  |       | 7    |       | Switch cycles    |

|                          |                                                                                     | V <sub>FB</sub> = 280 mV, 2-phase over-current:<br>V <sub>CS1</sub> AND V <sub>CS2</sub> > V <sub>ILIM</sub>     |       | 3    |       | Switch cycles    |

| t <sub>D-HICCUP</sub>    | Master or Slave Over-Current<br>Hiccup Mode Delay                                   | 1-phase over-current:<br>V <sub>CS1</sub> OR V <sub>CS2</sub> > V <sub>ILIM</sub>                                |       | 446  |       | Switch cycles    |

|                          |                                                                                     | 2-phase over-current:<br>V <sub>CS1</sub> AND V <sub>CS2</sub> > V <sub>ILIM</sub>                               |       | 223  |       | Switch cycles    |

| t <sub>D-COOL-DOWN</sub> | Hiccup Over-Current Cool-Down<br>Time                                               |                                                                                                                  |       | 6    |       | ms               |

| Power Good: F            | PGOOD, OVP, UVP                                                                     |                                                                                                                  |       |      | Г     |                  |

| V <sub>OVP</sub>         | OVP Threshold                                                                       | V <sub>FB</sub> rising edge                                                                                      | 125   | 130  | 135   | %V <sub>FB</sub> |

| t <sub>D-RESTART</sub>   | OVP Restart Delay                                                                   |                                                                                                                  |       | 2    |       | ms               |

| N <sub>OVP-LATCH</sub>   | Number of OVP Events Before Latch-Off                                               |                                                                                                                  |       | 7    |       |                  |

| $V_{UVP}$                | UVP Threshold                                                                       | V <sub>FB</sub> falling edge                                                                                     | 75    | 80   | 85    | %V <sub>FB</sub> |

| V <sub>UVP-HYS</sub>     | UVP Threshold Hysteresis                                                            |                                                                                                                  |       | 25   |       | mV               |

| t <sub>D-OVP/UVP</sub>   | OVP/UVP Debounce Time                                                               |                                                                                                                  |       | 5    |       | μs               |

| $V_{PG\text{-}LO}$       | PGOOD Low Level                                                                     | I <sub>PGOOD</sub> = -4 mA                                                                                       |       | 0.14 | 0.25  | V                |

| I <sub>PG-LEAK</sub>     | PGOOD Leakage Current                                                               | $V_{PGOOD} = 5.5V$                                                                                               |       | 5    | 300   | nA               |

Limits in standard type are for  $T_J$  = 25°C only; limits in boldface type apply over the junction temperature ( $T_J$ ) range of -5°C to +125°C. Minimum and Maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J$  = 25°C, and are provided for reference purposes only. Unless otherwise stated  $V_{VIN}$  = 12V,  $V_{VDD}$  = 5V,  $V_{VCC}$  = internal LDO,  $V_{EN}$  = 2V,  $V_{FRQ}$  = 78.7 k $\Omega$ ,  $V_{PH}$  = 0V,  $V_{CS1}$  =  $V_{CS2}$  =  $V_{CSM}$  =  $V_{SS}$  =  $V_{SNSP}$  = 1.8V,  $V_{ILIM}$  -  $V_{CSM}$  = 100 mV,  $V_{SNSM}$  =  $V_{SYNC}$  = 0V,  $V_{SYNCOUT}$  floating.

| Symbol                  | Parameter                                                              | Conditions                                         | Min           | Тур          | Max   | Units |

|-------------------------|------------------------------------------------------------------------|----------------------------------------------------|---------------|--------------|-------|-------|

| AULT                    |                                                                        |                                                    |               |              |       |       |

| I <sub>FAULT</sub>      | Internal Pullup Current in Master Mode                                 |                                                    |               | 325          |       | μA    |

| V <sub>OL-FAULT</sub>   | FAULT Output Low Level                                                 | I <sub>FAULT</sub> sinking 500 μA                  |               | 0.21         |       | V     |

| V <sub>OH-FAULT</sub>   | FAULT Output High Level                                                | I <sub>FAULT</sub> sourcing 50 μA                  |               | VCC -<br>0.1 |       | V     |

| Scillator and           | Synchronization (PLL): SYNC, SY                                        | NCOUT, FREQ                                        |               |              |       | •     |

| f <sub>SW-MIN</sub>     | Minimum Switching Frequency                                            | $R_{FRQ} = 121 \text{ k}\Omega$                    |               | 200          |       | kHz   |

| f <sub>SW-MAX</sub>     | Maximum Switching Frequency                                            | $R_{FRQ} = 21.3 \text{ k}\Omega$                   |               | 1000         |       | kHz   |

| f <sub>SW</sub>         | Switching Frequency Accuracy                                           | $R_{FRQ} = 78.7 \text{ k}\Omega$                   | 282           | 300          | 318   | kHz   |

| f <sub>SYNC</sub>       | SYNC Frequency Capture Range                                           | 200 kHz to 1 MHz                                   |               | ±25          |       | %     |

| V <sub>SYNC-RISE</sub>  | SYNC Rising Threshold                                                  |                                                    |               | 1.46         | 1.68  | V     |

| V <sub>SYNC-FALL</sub>  | SYNC Falling Threshold                                                 |                                                    | 1.12          | 1.3          |       | V     |

| t <sub>SYNC-MIN</sub>   | SYNC Minimum Pulse Width                                               |                                                    |               | 150          |       | ns    |

| I <sub>SYNC</sub>       | SYNC Bias Current (internal or external VCC)                           | V <sub>SYNC</sub> = 0 to 5.5V                      | -15           |              | 25    | μA    |

| V <sub>SYNCOUT-HI</sub> | SYNCOUT Logic High Level                                               | Sourcing 10 mA, V <sub>VCC</sub> = 4.5V external   | VCC -<br>0.42 |              |       | V     |

| V <sub>SYNCOUT-LO</sub> | SYNCOUT Logic Low Level                                                | Sinking 10 mA, V <sub>VCC</sub> = 4.5V external    |               |              | 0.48  | V     |

| PH <sub>RATIO</sub>     | V <sub>PH</sub> /V <sub>VCC</sub> Divider Ratio to Set<br>Phase Number | 2 & 4 Phases                                       |               | 0            | 0.138 |       |

|                         |                                                                        | 3 Phases                                           | 0.152         | 3/14         | 0.279 |       |

|                         |                                                                        | 5 Phases                                           | 0.294         | 5/14         | 0.418 |       |

|                         |                                                                        | 6 Phases                                           | 0.438         | 7/14         | 0.562 |       |

|                         |                                                                        | 8 Phases                                           | 0.587         | 9/14         | 0.703 |       |

|                         |                                                                        | 10 Phases                                          | 0.730         | 11/14        | 0.844 |       |

|                         |                                                                        | 12 Phases                                          | 0.874         | 1            |       |       |

| I <sub>PH</sub>         | PH Bias Current                                                        | $V_{VCC}$ = 4.5V forced, $V_{PH}$ = 0 to $V_{VCC}$ | -150          |              | 150   | nA    |

| Φ <sub>HG1-N2</sub>     | HG1 to HG2 Phase Shift for 2, 4, 6, 8, 10 or 12-Phase Modes            |                                                    |               | 180          |       | 0     |

| Φ <sub>HG1-N3</sub>     | HG1 to HG2 Phase Shift for 3-<br>Phase Mode                            |                                                    |               | 240          |       | 0     |

| Φ <sub>HG1-N5</sub>     | HG1 to HG2 Phase Shift for 5-<br>Phase Mode                            |                                                    |               | 216          |       | 0     |

| Φ <sub>SYNC</sub>       | SYNC to SYNCOUT Phase Shift                                            | N > 2                                              |               | 360/N        |       | o     |

|                         | for N-phase Operation                                                  | N = 2                                              |               | 90           |       |       |

| t <sub>SYNC-ERR</sub>   | SYNC to SYNCOUT Phase Shift Error                                      |                                                    |               | 5            |       | ns    |

| t <sub>SYNC-HG</sub>    | SYNC to HG1(2)                                                         |                                                    |               | 165          |       | ns    |

| $\Phi_{\text{HG-ERR}}$  | HG1 and HG2 Controller-to-<br>Controller Phase Delay Error             | 300 kHz, 6-phase                                   |               | 5            |       | o     |

| oft-Start: SS,          | Pre-Biased Startup                                                     |                                                    | L             | 1            |       | 1     |

| I <sub>SS</sub>         | SS Source Current                                                      | V <sub>SS</sub> = 0.3V                             | 5.7           | 10           | 14.6  | μA    |

| R <sub>DS-SS</sub>      | Soft-Start Pull-Down Resistance                                        |                                                    |               | 750          |       | Ohm   |

| t <sub>LG-PW1</sub>     | First LG High Pulse Width during Soft-Start                            |                                                    |               | 460          |       | ns    |

|                         | +                                                                      | 1                                                  |               |              |       | 1     |

Submit Documentation Feedback

Copyright © 2012–2013, Texas Instruments Incorporated

Limits in standard type are for  $T_J$  = 25°C only; limits in boldface type apply over the junction temperature ( $T_J$ ) range of -5°C to +125°C. Minimum and Maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J$  = 25°C, and are provided for reference purposes only. Unless otherwise stated  $V_{VIN}$  = 12V,  $V_{VDD}$  = 5V,  $V_{VCC}$  = internal LDO,  $V_{EN}$  = 2V,  $V_{FRQ}$  = 78.7 k $\Omega$ ,  $V_{PH}$  = 0V,  $V_{CS1}$  =  $V_{CS2}$  =  $V_{CSM}$  =  $V_{SS}$  =  $V_{SNSP}$  = 1.8V,  $V_{ILIM}$  -  $V_{CSM}$  = 100 mV,  $V_{SNSM}$  =  $V_{SYNC}$  = 0V,  $V_{SYNCOUT}$  floating.

| Symbol                                                                                                             | Parameter                                                                    | Conditions               | Min | Тур | Max | Units |

|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------|-----|-----|-----|-------|

| t <sub>LG-GT</sub>                                                                                                 | LG Asynchronous-to-<br>Synchronous Gradual Transition<br>Time                |                          |     | 2   |     | ms    |

| t <sub>D-EN-SW</sub>                                                                                               | Delay from EN = High to FAULT = High; no pre-bias                            |                          |     | 2   |     | ms    |

| Gate Drivers                                                                                                       |                                                                              |                          |     |     |     |       |

| I <sub>PK-HG-SOURCE</sub>                                                                                          | HG1 and HG2 Peak Source<br>Current                                           | Less than 100 ns         |     | 1.9 |     | Α     |

| R <sub>HG-SOURCE</sub>                                                                                             | HG1 and HG2 Source<br>Resistance                                             | $V_{BOOT} - V_{SW} = 5V$ |     | 2.5 |     | Ω     |

| I <sub>PK-HG-SINK</sub>                                                                                            | HG1 and HG2 Peak Sink Current                                                | Less than 100 ns         |     | 4   |     | Α     |

| R <sub>HG-SINK</sub>                                                                                               | -SINK HG1 and HG2 Sink Resistance V <sub>BOOT</sub> - V <sub>SW</sub> = 5V   |                          |     | 1   |     | Ω     |

| I <sub>PK-LG-SOURCE</sub>                                                                                          | LG1 and LG2 Peak Source<br>Current                                           | Less than 100 ns         |     | 2.3 |     | А     |

| R <sub>LG-SOURCE</sub>                                                                                             | LG1 and LG2 Source Resistance                                                |                          |     | 2   |     | Ω     |

| I <sub>PK-LG-SINK</sub>                                                                                            | LG1 and LG2 Peak Sink Current                                                | Less than 100 ns         |     | 4   |     | Α     |

| $R_{LG-SINK}$                                                                                                      | LG1 and LG2 Sink Resistance                                                  |                          |     | 1   |     | Ω     |

| R <sub>HG-PULLDOWN</sub>                                                                                           | HG-SW Pull-Down Resistor                                                     |                          |     | 16  |     | kΩ    |

| R <sub>LG-PULLDOWN</sub>                                                                                           | LG-PGND Pull-Down Resistor                                                   |                          |     | 16  |     | kΩ    |

| t <sub>D-HG-LG</sub> HG Falling to LG Rising Cross- Conduction Protection Delay (Dead-Time)  SW node not switching |                                                                              | SW node not switching    |     | 30  |     | ns    |

| t <sub>D-LG-HG</sub>                                                                                               | LG Falling to HG Rising Delay                                                |                          |     | 28  |     | ns    |

| t <sub>DS-HG-LG</sub>                                                                                              | HG Falling to LG Rising Cross-<br>Conduction Protection Delay<br>(Dead-Time) | SW node switching        |     | 10  |     | ns    |

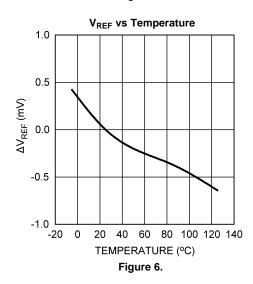

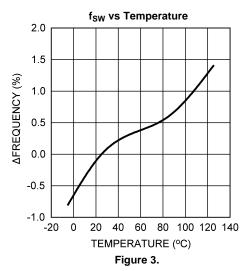

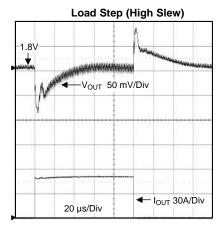

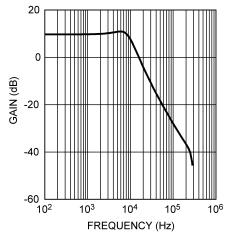

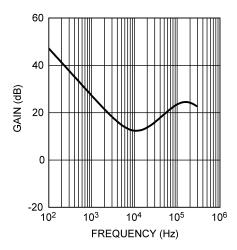

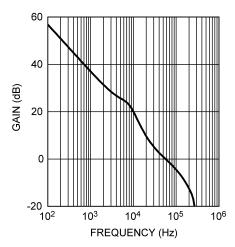

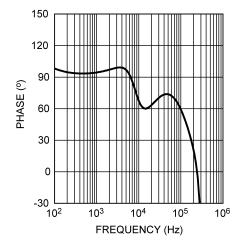

### **Typical Performance Characteristics**

Figure 7.

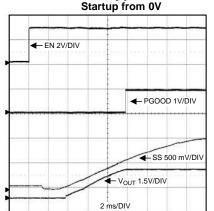

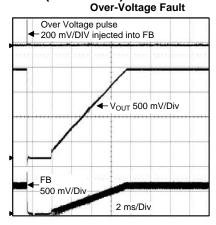

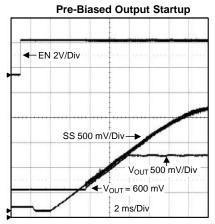

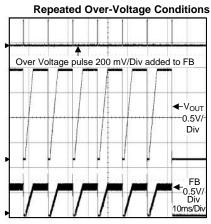

## Typical Performance Characteristics (continued) Startup from 0V Over-Vo

Figure 8.

Figure 9.

Figure 10.

Figure 11.

Figure 12.

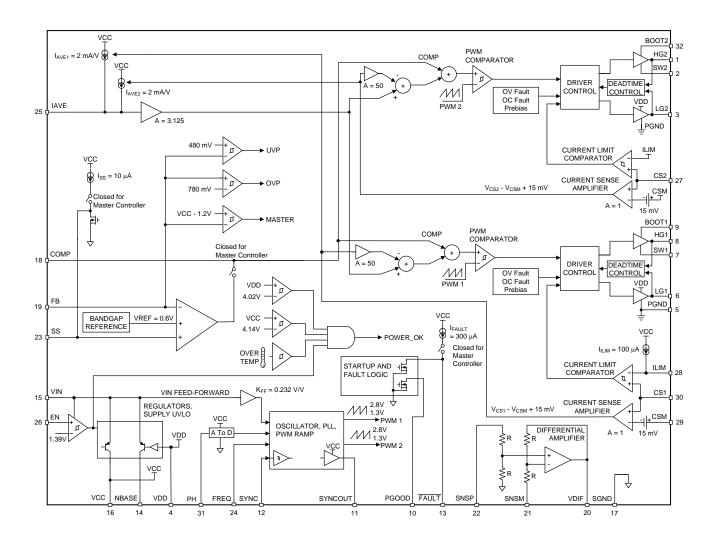

#### **Block Diagram**

#### **Functional Description**

#### General

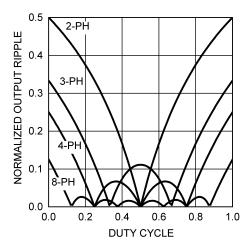

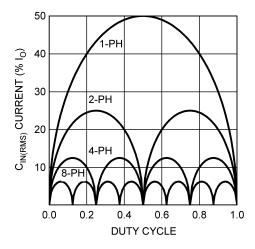

The LM3754 is a two-phase voltage-mode step-down (buck) switching regulator controller. From one to six LM3754 controllers can be connected together to control from two to twelve phases (2, 3, 4, 5, 6, 8, 10, or 12 phases). Since external switching components can typically handle 25A per phase, a 12 phase system can supply a total of 300A.

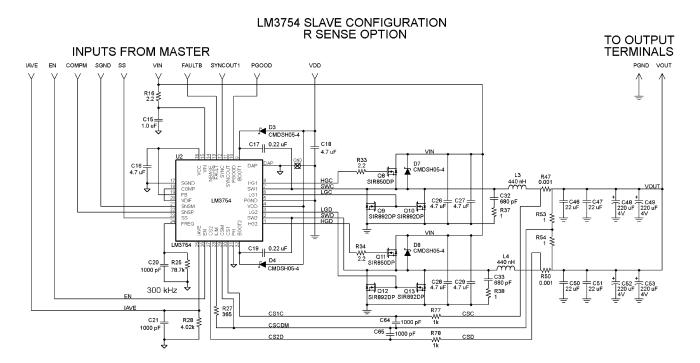

Multiple controllers in a system communicate with each other and work together. They will startup and shut down together, each phase on each controller will share current equally, and all the phases will react in unison to fault conditions. In a multi-controller system, all controllers are the same part. One controller functions as the Master and all the others act as Slaves. The Master and Slave are differentiated by how they are connected in the system. The Master controller senses the system output voltage and VIN (as well as SS) and sets the target duty cycle for each phase on all of the controllers. The Master and Slave controllers monitor the current-sense information from each phase. Based on this current information, the controllers adjust the duty cycle on each phase up or down from the target level, in order to achieve optimal current sharing.

Each controller incorporates a phase locked loop (PLL) that communicates with the PLLs on the other controllers. By this means, the switching edges of the different phases are spread out equally within one switch period. For N phases operating at any switching frequency, the angle in degrees between one phase switching and the next is 360° / N. A SYNC pin is available that can be used to lock the Master switching frequency and phase to an external clock.

The LM3754 has a Soft-Start function. The Master controller sources 10  $\mu$ A out of the SS pin so that the output voltage rise time is controlled by the size of the external SS capacitor. The LM3754 will not pull down a prebiased load. The synchronous NFET switch is not turned on during the soft-start cycle until the SS ramp exceeds either the FB voltage or the internal reference voltage VREF. At this point a gradual transition to synchronous switching is initiated.

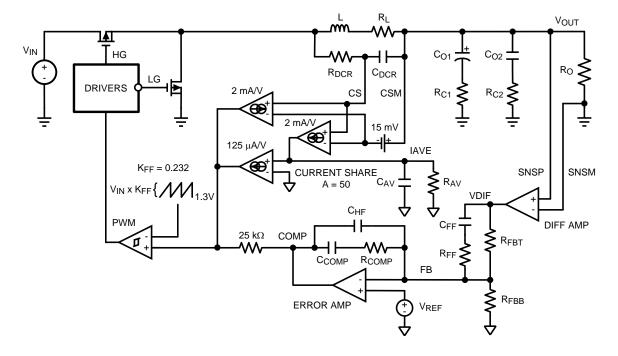

#### **Control Algorithm**

The control architecture is primarily voltage-mode. An error amplifier amplifies the difference between the FB pin voltage and the internal reference voltage to generate a COMP signal. This signal is compared against a ramp that consists of a fixed value plus a term proportional to VIN which controls the duty cycle. In order to facilitate current sharing there is an inner current-sense loop. Information for the current through the inductor in each phase is sensed either with a sense resistor or with a DCR arrangement which uses the DC resistance of the inductor. This current-sense signal is connected to the CS pin (CS1 or CS2). The negative reference for current-sense is V<sub>OUT</sub> which is common for both phases and connected to the controller's CSM pin. The controller amplifies the (CS1(2) – CSM) voltage difference for each phase, and compares it to the voltage on the IAVE pin, which tracks the average current of all phases. Any phase whose current is more than the average has its duty cycle decreased and vice versa. The IAVE signal is common to all controllers in a system. Each controller outputs a current onto the IAVE bus so that the total current on the bus is the sum of the current signals from all of the phases. An external resistor to ground translates this current signal to a voltage, which all of the controllers read back.

The LM3754 includes an uncommitted differential amplifier. On the Master controller this amplifier is used to remotely sense the converter's output voltage, typically at the load. On the Slave controllers this amplifier is used to buffer the Master controller's COMP signal and level shift it to the Slave controller's local ground.

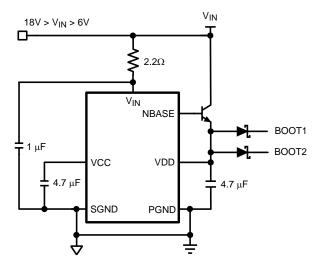

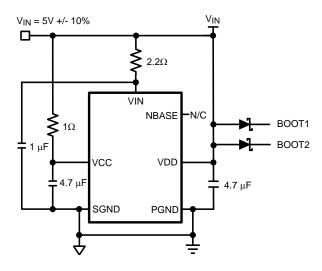

#### **Power Connections**

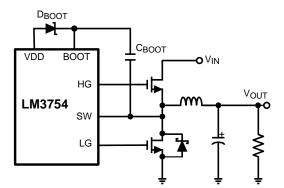

The LM3754 has three supply pins, which are VIN, VCC, and VDD. It employs two ground pins, SGND and PGND. VDD and PGND are the power and ground for the gate driver stage that controls the HG and LG pins. The quiescent current drawn by VDD is very small – around 1 mA. To predict the VDD current requirement one can assume it is mostly switching current and use the standard formula:

$$I_{VDD} = (1 \text{ or } 2) \times f_{SW} \times Q_{TOTAL\_PHASE}$$

(1)

$Q_{\mathsf{TOTAL\_PHASE}}$  is the sum of the high-side switch gate charge and the low-side gate charge. The (1 or 2) factor corresponds to one or two phases running. The low-side driver is powered directly from VDD. The high-side driver draws its power from VDD through the external bootstrap Schottky diode. The rest of the controller is powered by VCC and SGND.

The LM3754 has two on-board regulators, one to generate VCC and one to generate VDD. The VCC regulator is self-contained and only needs a 4.7  $\mu$ F ceramic capacitor to SGND. The VDD regulator uses an external NPN pass device. This device should be sized to meet the VIN to VDD dropout requirements for the calculated I<sub>VDD</sub>. The collector of this device goes to VIN, the base goes to NBASE and the emitter goes to VDD. VDD also needs a 4.7  $\mu$ F bypass capacitor to PGND. The internal VIN to NBASE dropout is approximately 300 mV. The minimum VIN is calculated as:

$$VIN_{MIN} = VDD_{MIN} + V_{BE\_NPN} + 300 \text{ mV}$$

(2)

$$VDD_{MIN} = MAX(VDD_{UVLO}, V_{GATE-MIN})$$

(3)

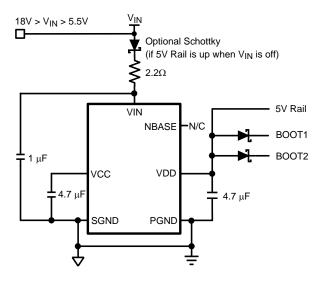

$VDD_{UVLO}$  is the controller's maximum VDD under-voltage lockout voltage, which is 4.06V.  $V_{GATE-MIN}$  is the minimum required gate drive voltage for the power MOSFET switches.  $VIN_{MIN}$  is typically 5.5V to 6.0V. For VIN less than 5.5V, the regulators are omitted and the VCC and VDD pins are connected as shown in Figure 15.

Figure 13. Power Connections Using the Internal Regulator

Figure 14. Power Connections Using a System 5V Rail

Submit Documentation Feedback

Copyright © 2012–2013, Texas Instruments Incorporated

Figure 15. Power Connections for  $V_{IN} = 5V$

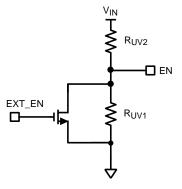

#### **Under-Voltage Lockouts and Enable**

The LM3754 controller has internal under-voltage lockout (UVLO) detection on the VCC and VDD supplies. The under-voltage lockout on VIN is set using the EN pin threshold. Connect a voltage divider between VIN and SGND with the midpoint going to the EN pin. The division ratio and the EN pin threshold determine the VIN level that enables the controller. This divider should be used in all cases. If the system does not have a particular VIN under-voltage lockout requirement, the level is set to be below the minimum VIN level at the worst case combination of tolerances and operating conditions.

$$\frac{R_{UV2}}{R_{UV1}} = \frac{V_{IN\_UVLO}}{V_{EN}} - 1 \tag{4}$$

To ensure startup at the lowest input voltage, set the divider to the  $V_{\text{EN-TH}}$  rising max specification. For a higher accuracy VIN UVLO operation, the resistor divider minimum current should be 1 mA or higher. This will reduce the threshold error contribution of the EN pin bias current, which is specified to be less than 1.7  $\mu$ A over temperature. The enable pin can also be used as a digital on-off. To do this, the enable signal should be used to pull down the midpoint of the voltage divider using open-drain logic or a transistor. A customary implementation uses an external MOSFET.

Figure 16. Input Voltage UVLO with External Enable

While the EN pin has a threshold hysteresis of 140 mV typical, a small noise-filtering capacitor may be added between the EN pin and SGND. This is particularly useful when the controller is turning on via the resistor divider by a slowly rising VIN rail.

#### **Startup Sequence**

When EN is below its threshold, the internal regulators are off and the controller is in a low power state. When EN crosses above its threshold the VCC regulator turns on. When VCC rises above its under-voltage lockout threshold the VDD regulator turns on. When VDD rises above its under-voltage lockout threshold the controller is ready to start.

If VDD or VCC is supplied externally and already sitting above its under-voltage lockout point, then the controller is ready for startup as soon as EN crosses above its threshold. Anytime VCC or VDD drops below its UV threshold, switching stops and the controller goes into a standby state. It will go through normal startup once the supplies recover.

When the controller is ready to start, it reads the voltage on the PH pin and determines how many phases are running in the system. By this means the phase delay from SYNC to SYNCOUT through the PLL is configured. Following this the oscillator and PLL turn on and pulses will be observed on SYNCOUT.

A 2 ms timer is initiated so that all of the PLLs in the system can synchronize up. As each controller times out, it stops pulling its FAULT pin low. At the end of this sequence, the FAULT bus rises and the controllers are ready to switch.

The error amplifier uses a different input stage when SS is below VREF. During normal operation the error amplifier employs a low offset bipolar input stage. At startup, the input bias current of this stage is large enough in relation to the soft-start current to affect the soft-start timing. A MOS input stage is used during the soft-start or track phase which has a lower input bias current but a higher input offset voltage. A 40 mV offset is introduced when SS is less than 70 mV. This offset forces the error amplifier output to be low during startup. The offset transitions progressively to zero as SS moves from 0 to 70 mV.

#### **Soft-Start**

The LM3754 implements a soft-start function, and operates so as to prevent discharge of a pre-biased output. The error amplifier amplifies the minimum of VREF or SS at the FB pin. By means of the closed loop regulation through the switching stage, FB will be regulated to SS. The Master controller sources 10  $\mu$ A onto the SS pin, while the Slaves do not source any current. This sets the total soft-start current in a multi-controller system to 10  $\mu$ A.

The SS pin is automatically pulled down to SGND prior to the onset of switching and during a restart from a fault condition. When SS is initially released, COMP is low and no switching occurs. Both LG and HG are held low while SS is below FB, which ensures that a pre-biased load will not be pulled down. When SS crosses above either FB or VREF, COMP will slew up and switching will start. The first switching pulse is a 300 ns LG pulse to charge the external HG bootstrap capacitor. After this the LG pulse width is reduced to zero. This insures that  $V_{\text{OUT}}$  does not get pulled down while COMP slews up and the system loop is settling. Pulses on HG cause the high-side FET to turn-on so that FB tracks the SS pin as it slews up. During the switch cycle off-time the inductor current can only flow through the body diode of the synchronous switch. During each successive cycle the LG pulse width gradually increases. Over the course of 0.3 ms to 2.0 ms, depending on the amount of pre-bias, LG pulses get longer until full synchronous switching occurs. The internal timer waits 2 ms, regardless of duty cycle, for this transition in LG pulse width to complete.

Following this PGOOD goes high if FB is above the output under-voltage threshold on the Master, SS is above VREF, no fault conditions are present, and SYNC is toggling on the Slaves.

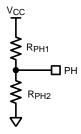

#### **Phase Number Selection**

The voltage at the PH pin determines the phase shift between the two phases of each controller and also the phase shift between the SYNC and SYNCOUT pulses in a Master-Slave configuration. This voltage is read at startup and the resulting phase configuration saved. The PH pin should be connected to the center of a resistor divider between VCC and SGND to select and program the required number of phases and the corresponding phase delays per Table 1. Each controller requires the same resistor divider at the PH pin.

Figure 17. Phase Selection

Table 1. Phase Divider Resistors

| Number Of Phases | Divide Ratio Target | R <sub>PH1</sub><br>(± 1%) | R <sub>PH2</sub><br>(± 1%) |

|------------------|---------------------|----------------------------|----------------------------|

| 2 & 4 Phases     | 0.000               | Omit                       | 0                          |

| 3 Phases         | 0.214               | 7870Ω                      | 2150Ω                      |

| 5 Phases         | 0.357               | 6490Ω                      | 3570Ω                      |

| 6 Phases         | 0.5                 | 4990Ω                      | 4990Ω                      |

| 8 Phases         | 0.643               | 3570Ω                      | 6490Ω                      |

| 10 Phases        | 0.786               | 2150Ω                      | 7870Ω                      |

| 12 Phases        | 1                   | 0                          | Omit                       |

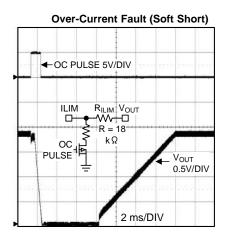

#### **Over-Current and Over-Voltage Faults**

If any controller experiences a fault condition, it will pull the FAULT bus low and all of the controllers will stop switching. From the time when EN is low to the point where FAULT rises, both HG and LG are low so that the SW node of each phase is floating. The FAULT input may be pulled low externally through an open drain MOSFET to disable the system.

The LM3754 employs cycle-by-cycle current limiting. This occurs on each phase for both Master and Slave controllers. The current (that is the CS1(2) – CSM voltage) is continuously compared to the over-current set point (ILIM – CSM). Any time that the current-sense signal exceeds current limit, the cycle is ended.

In order to determine that a current fault has occurred, each controller counts the number of over-current pulses. When the sum of the counts for phase 1 and phase 2 reaches 446 an over-current fault is declared. The counter is reset after 16 consecutive switching cycles with no over-current on either phase.

There is a second method for achieving an over-current fault, which is meant to react to heavy shorts on V<sub>OUT</sub>. The Master controller will determine that an over-current fault has occurred after 7 over-current cycles if the voltage at the FB pin is less than 50% of its target value. This feature is disabled during startup. Since the Slave controllers do not see the FB voltage, they cannot detect this type of fault.

Any controller which sees an over-current fault will respond by pulling the FAULT bus low. All of the controllers will react and stop switching. Both HG and LG on each phase will be pulled low. The inductor current in each phase will decay through the body diodes of the low-side switches. The controller which recognized the over-current fault will hold FAULT low for 6 ms, which determines the hiccup time. This allows the energy stored in the inductors to dissipate. After this, FAULT is released and all of the controllers will restart together.