🕳 Order

Now

LMG3411R150, LMG3410R150

参考資料

JAJSH13A – MARCH 2019 – REVISED JUNE 2019

# LMG341xR150 ドライバおよび保護機能を搭載した 600V、150mΩ GaN

Technical

Documents

# 1 特長

- TI の GaN プロセスは、加速信頼性アプリケー ション内ハード・スイッチング・ミッション・プ ロファイルによる認定済み

- 高密度の電力変換設計が可能

- カスコードまたはスタンドアロンの GaN FET で優 れたシステム性能を実現

- 低インダクタンスの 8mm×8mm QFN パッケージ により設計とレイアウトが容易

- スイッチング性能と EMI 制御のため駆動強度を変 更可能

- デジタルのフォルト・ステータス出力信号

- +12Vの非レギュレート電源のみで動作可能

- 統合型ゲート・ドライバ

- 共通ソース・インダクタンスが0

- 伝播遅延が 20ns で、MHz 動作が可能

- ゲート・バイアス電圧をプロセスで調整することで高い信頼性を実現

- スルー・レートを 25~100V/ns の範囲でユーザー が設定可能

- サイクル単位の過電流保護

- 堅牢な保護

- 外付けの保護部品が不要

- 応答時間 100ns 未満の過電流保護

- 150V/ns を超えるスルー・レート耐性

- 過渡過電圧耐性

- 過熱保護

- すべての電源レールの UVLO 保護

- デバイスのオプション

- LMG3410R150:ラッチ付き過電流保護

- LMG3411R150:サイクル単位の過電流保護

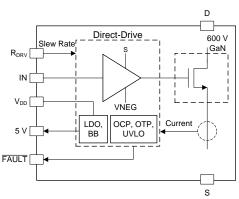

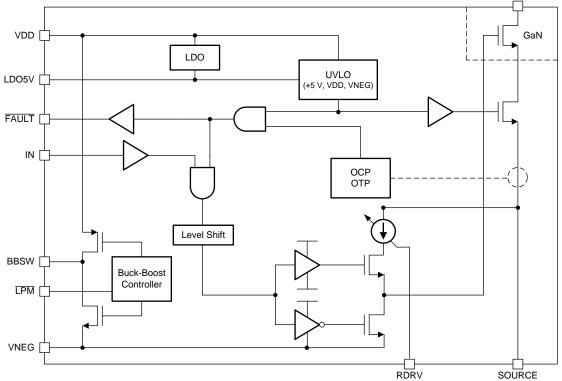

ブロック概略図

2 アプリケーション

🧷 Tools &

Software

- 高密度の産業用および民生用電源

- ノート PC、タブレット、TV、セットトップ・ ボックス、プリンタ用の高密度の AC/DC アダプ タ

Support &

Community

22

- 太陽光インバータ

- 産業用モータ・ドライブ

# 3 概要

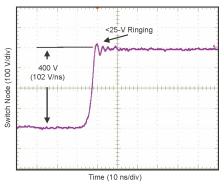

ドライバおよび保護機能を内蔵した LMG341xR150 GaN 電力段を使うと、設計者はパワー・エレクトロニクス・システ ムにおいて、比類ない電力密度と効率を実現できます。シ リコンMOSFETに対するLMG341xの本質的な利点には、 入力および出力容量が非常に小さい、逆方向回復が0 であるためスイッチング損失を約80%低減できる、スイッ チ・ノードのリンギングが小さいためEMIが低減されるという 事実が含まれます。これらの利点により、トーテムポール PFCのような高密度高効率のトポロジが可能になります。

LMG341xR150 は、従来のカスコード GaN およびスタン ドアロン GaN FET に代わる優れたデバイスで、組み込ま れた一連の独自機能により、電源の設計を単純化し、信 頼性を最大化し、性能を最適化できます。内蔵のゲート・ ドライブにより、Vdsリンギングがほぼ0で100V/nsのスイッ チングを行い、100ns未満の電流制限により意図しない貫 通電流からデバイス自身を保護し、過熱シャットダウンによ り熱暴走を防止し、システム・インターフェイス信号により自 己監視を行えます。

製品情報<sup>(1)</sup>

|             | 420 HH IH TK |               |

|-------------|--------------|---------------|

| 型番          | パッケージ        | 本体サイズ(公称)     |

| LMG341xR150 | QFN (32)     | 8.00mm×8.00mm |

(1) 提供されているすべてのパッケージについては、巻末の注文情報 を参照してください。

#### 100V/nsを超えるスイッチング性能

英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、www.ti.comで閲覧でき、その内 容が常に優先されます。TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、必ず最新版の英語版をご参照くださいますようお願いいたします。 English Data Sheet: SNOSD91

#### LMG3411R150, LMG3410R150 JAJSH13A - MARCH 2019 - REVISED JUNE 2019

Copyright © 2019, Texas Instruments Incorporated

**ADVANCE INFORMATION**

# 目次

| 1 | 特長   |                                  | 1              |

|---|------|----------------------------------|----------------|

| 2 | アプ   | リケーション                           | 1              |

| 3 | 概要   | <u>.</u>                         | 1              |

| 4 | 改訂   | 「履歴                              | 2              |

| 5 | Pin  | Configuration and Functions      | 3              |

| 6 | Spe  | cifications                      | 4              |

|   | 6.1  | Absolute Maximum Ratings         |                |

|   | 6.2  | ESD Ratings                      | 4              |

|   | 6.3  | Recommended Operating Conditions |                |

|   | 6.4  | Thermal Information              | 5              |

|   | 6.5  | Electrical Characteristics       | 5              |

|   | 6.6  | Switching Characteristics        | <mark>6</mark> |

| 7 | Para | ameter Measurement Information   | <mark>6</mark> |

| 8 | Deta | ailed Description                | 9              |

|   | 8.1  | Overview                         | 9              |

|   | 8.2  | Functional Block Diagram         | 9              |

|   | 8.3  | Feature Description              | 10             |

|   | 8.4  | Device Functional Modes          | 12             |

| 9 | Арр  | lication and Implementation      | 12             |

|   |      |                                  |                |

| 八 |    |      |                                   |

|---|----|------|-----------------------------------|

|   |    | 9.1  | Application Information 12        |

|   |    | 9.2  | Typical Application               |

|   |    | 9.3  | Paralleling GaN Devices 16        |

|   |    | 9.4  | Do's and Don'ts 16                |

|   | 10 | Pow  | ver Supply Recommendations 17     |

|   |    | 10.1 | Using an Isolated Power Supply 17 |

|   |    | 10.2 | Using a Bootstrap Diode 17        |

|   | 11 | Laye | out 19                            |

|   |    | 11.1 | Layout Guidelines 19              |

|   |    | 11.2 | Layout Example 20                 |

|   | 12 | デバ   | イスおよびドキュメントのサポート 22               |

|   |    | 12.1 | デバイス・サポート                         |

|   |    | 12.2 | ドキュメントのサポート                       |

|   |    | 12.3 | ドキュメントの更新通知を受け取る方法 22             |

|   |    | 12.4 | コミュニティ・リソース 22                    |

|   |    | 12.5 | 商標                                |

|   |    | 12.6 | 静電気放電に関する注意事項 22                  |

|   |    | 12.7 | Glossary 22                       |

|   | 13 | メカニ  | ニカル、パッケージ、および注文情報                 |

| 4 | 改訂履歴 |  |

|---|------|--|

|---|------|--|

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| 2019年3月 | 発行のものから更新 |

|---------|-----------|

|---------|-----------|

|   |                  | ませはおご りいし  | **    |  |

|---|------------------|------------|-------|--|

| • | LMG3410R150 を追加、 | 事前情報データシート | · 変更1 |  |

www.ti.com

Page

www.ti.com

#### LMG3411R150, LMG3410R150 JAJSH13A – MARCH 2019 – REVISED JUNE 2019

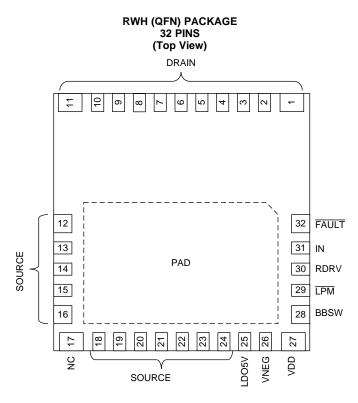

# 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN<br>NAME NO. |              | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                      |  |

|-----------------|--------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------|--|

|                 |              | 1/0(1)             | DESCRIPTION                                                                                                                      |  |

| BBSW            | 28           | Р                  | Internal buck-boost converter switch pin. Connect an inductor from this point to source                                          |  |

| DRAIN           | 1-11         | Р                  | Power transistor drain                                                                                                           |  |

| FAULT           | 32           | 0                  | Fault output, push-pull, active low                                                                                              |  |

| IN              | 31           | I                  | CMOS-compatible non-inverting gate drive input                                                                                   |  |

| LDO5V           | 25           | Р                  | 5-V LDO output for external digital isolator.                                                                                    |  |

| LPM             | 29           | I                  | Enables low-power-mode by connecting the pin to source                                                                           |  |

| SOURCE          | 12-16, 18-24 | Р                  | Power transistor source, die-attach pad, thermal sink, signal ground reference                                                   |  |

| RDRV            | 30           | I                  | Drive strength selection pin. Connect a resistor from this pin to ground to set the turn-on drive strength to control slew rate, |  |

| VDD             | 27           | Р                  | 12-V power input, relative to source. Supplies 5-V rail and gate drive supply.                                                   |  |

| VNEG            | 26           | Р                  | Negative supply output, bypass to source with 1-µF capacitor                                                                     |  |

| NC              | 17           | _                  | Not connected, connect to source or leave floating.                                                                              |  |

| PAD             | _            | Р                  | Thermal Pad, tie to source with multiple vias.                                                                                   |  |

(1) I = Input, O = Output, P = Power

JAJSH13A - MARCH 2019 - REVISED JUNE 2019

www.ti.com

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                                   |                                | MIN  | MAX | UNIT |

|-----------------------------------|--------------------------------|------|-----|------|

| V <sub>DS</sub>                   | Drain-Source Voltage           |      | 600 | V    |

| V <sub>DS,tr</sub> <sup>(2)</sup> | Transient Drain-Source Voltage |      | 800 | V    |

| V <sub>DD</sub>                   | Supply Voltage                 | -0.3 | 20  | V    |

| V <sub>IN</sub>                   | IN, TPM Pin Voltage            | -0.3 | 5.5 | V    |

| T <sub>STG</sub>                  | Storage Temperature            | -55  | 150 | °C   |

| T J                               | Operating Temperature          | -40  | 150 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) <1% duty cycle, <1us, for 1M pulses

# 6.2 ESD Ratings

|                    |                         |                                                                                        | VALUE | UNIT |

|--------------------|-------------------------|----------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins (1)                       | ±1000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins $^{\rm (2)}$ | ±250  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                   |                                                 | MIN | NOM | MAX | UNIT |

|-------------------|-------------------------------------------------|-----|-----|-----|------|

| V <sub>DS</sub>   | Drain-Source Voltage                            |     |     | 480 | V    |

| V <sub>DD</sub>   | Supply Voltage                                  | 9.5 | 12  | 18  | V    |

| I <sub>DS</sub>   | DC Drain-Source Current (T <sub>j</sub> =125°C) |     |     | 6   | А    |

| V <sub>IN</sub>   | IN, TPM Pin Voltage                             |     |     | 5   | V    |

| I <sub>+5V</sub>  | LDO External Load Current                       |     |     | 5   | mA   |

| R <sub>DRV</sub>  | Slew rate control resistor                      | 15  |     | 150 | kΩ   |

| L <sub>DCDC</sub> | DC-DC buck-boost converter output inductor      |     | 10  |     | μH   |

| C <sub>DCDC</sub> | DC-DC buck/boost converter output capacitor     |     | 1   |     | μF   |

| TJ                | Operating Temperature                           | -40 |     | 125 | °C   |

www.ti.com

#### 6.4 Thermal Information

|                       |                                              | LMG3410R150 |      |

|-----------------------|----------------------------------------------|-------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RWH (QFN)   | UNIT |

|                       |                                              | 32 PINS     |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 57          | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 5.3         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1           | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

# 6.5 Electrical Characteristics

over operating free-air temperature range, 9.5 V <  $V_{DD}$  < 18 V, LPM = 5 V,  $V_{NEG}$  = -14 V (unless otherwise noted)

|                         | PARAMETER                                       | TEST CONDITIONS                                                            | MIN | TYP   | MAX | UNIT |

|-------------------------|-------------------------------------------------|----------------------------------------------------------------------------|-----|-------|-----|------|

| GaN POWE                |                                                 |                                                                            |     |       |     |      |

| D                       | On state Desistance                             | $T_J = 25^{\circ}C$                                                        |     | 150   |     |      |

| R <sub>DS,ON</sub>      | On-state Resistance                             | T <sub>J</sub> = 125°C                                                     |     | 235   |     | mΩ   |

| <i>\</i> /              | Third-quadrant mode source-drain                | IN = 0 V, I <sub>SD</sub> = 0.1 A                                          |     | 5     |     | V    |

| V <sub>SD</sub>         | voltage                                         | IN = 0 V, I <sub>SD</sub> = 3 A                                            |     | TBD   |     | V    |

| C <sub>oss</sub>        | GaN output capacitance                          | $IN = 0 V, V_{DS} = 400 V, f_{SW} = 250 \text{ kHz}$                       |     | 30    |     | pF   |

| C <sub>oss,er</sub>     | Effective output capacitance, energy related    | IN = 0 V, V <sub>DS</sub> =0-400 V                                         |     | 40    |     | pF   |

| C <sub>oss,tr</sub>     | Effective output capacitance, time related      | I <sub>D</sub> = 3 A, IN = 0 V, V <sub>DS</sub> = 0-400 V                  |     | 60    |     | pF   |

| Q <sub>rr</sub>         | Reverse recovery charge                         | $V_{R} = 400 V, I_{SD} = 3 A, dI_{SD}/dt = 1 A/ns$                         |     | 0     |     | nC   |

| I <sub>DSS</sub>        | Drain leakage current                           | Vds=600V, T <sub>J</sub> = 25°C                                            |     | 1     |     | uA   |

| I <sub>DSS</sub>        | Drain leakage current                           | Vds=600V, T <sub>J</sub> = 125°C                                           |     | 10    |     | uA   |

| DRIVER SU               | PPLY                                            |                                                                            |     |       |     |      |

| I <sub>VDD,LPM</sub>    | Quiescent current, ultra-low-power mode         | V <sub>LPM</sub> = 0 V, V <sub>DD</sub> = 12 V                             |     | 80    | 95  | μΑ   |

|                         |                                                 | Transistor held off                                                        |     | 0.5   |     |      |

| I <sub>VDD,Q</sub>      | Quiescent current (average)                     | transistor held on                                                         |     | 0.5   |     | mA   |

| I <sub>VDD,op</sub>     | Operating current                               | $V_{DD}$ = 12 V, $f_{SW}$ = 500 KHz, $R_{DRV}$ =40 k\Omega, 50% duty cycle |     | 9     |     | mA   |

| V <sub>+5V</sub>        | 5V LDO output voltage                           | V <sub>DD</sub> = 12 V                                                     | 4.7 |       | 5.3 | V    |

| V <sub>NEG</sub>        | Negative Supply                                 | 15-mA load current                                                         |     | -13.9 |     | V    |

| BUCK BOO<br>CONVERTE    |                                                 |                                                                            |     |       |     |      |

| I <sub>DCDC,PK</sub>    | Peak inductor current                           | $I_{OUT}$ = 15 mA, $V_{IN}$ = 12 V, $V_{OUT}$ = -14 V                      |     | 250   | 350 | mA   |

| $\Delta V_{\text{NEG}}$ | DC-DC output ripple voltage, pk-pk              | $C_{NEG}$ = 1 $\mu$ F, $I_{OUT}$ = 15 mA                                   |     | 200   |     | mV   |

| DRIVER IN               | PUT                                             |                                                                            |     |       |     |      |

| V <sub>IH</sub>         | Input pin, <u>LPM</u> pin, logic high threshold |                                                                            |     |       | TBD | V    |

| V <sub>IL</sub>         | Input pin, LPM pin, low threshold               |                                                                            | 0.8 |       |     | V    |

| V <sub>HYST</sub>       | Input pin, LPM pin, hysteresis                  |                                                                            |     | 0.8   |     | V    |

| R <sub>IN,L</sub>       | Input pull-down resistance                      |                                                                            |     | 150   |     | kΩ   |

| R <sub>LPM</sub>        | LPM pin pull-down resistance                    |                                                                            |     | 150   |     | kΩ   |

# **Electrical Characteristics (continued)**

over operating free-air temperature range, 9.5 V < V<sub>DD</sub> < 18 V, LPM = 5 V, V<sub>NEG</sub> = -14 V (unless otherwise noted)

|                       | PARAMETER                         | TEST CONDITIONS  | MIN | TYP | MAX | UNIT |

|-----------------------|-----------------------------------|------------------|-----|-----|-----|------|

| UNDERVOL              | TAGE LOCKOUT                      |                  |     |     |     |      |

| V <sub>DD,(ON)</sub>  | V <sub>DD</sub> turnon threshold  | Turn-on voltage  |     | 9.1 |     | V    |

| V <sub>DD,(OFF)</sub> | V <sub>DD</sub> turnoff threshold | Turn-off voltage |     | 8.5 |     | V    |

| $\Delta V_{DD,UVLO}$  | UVLO Hysteresis                   |                  |     | 550 |     | mV   |

| FAULT                 |                                   |                  |     |     | ·   |      |

| l <sub>trip</sub>     | Current Fault Trip Point          |                  | 20  | 30  | 40  | А    |

| T <sub>trip</sub>     | Temperature Trip Point            | trip point       |     | 165 |     | °C   |

| T <sub>tripHys</sub>  | Temperature Trip Hysteresis       |                  |     | 20  |     | °C   |

### 6.6 Switching Characteristics

over operating free-air temperature range, 9.5 V < V<sub>DD</sub> < 18 V, V<sub>NEG</sub> = -14 V, V<sub>BUS</sub> = 400 V (unless otherwise noted)

|                        | PARAMETER                                       | TEST CONDITIONS                                                                                       | MIN  | TYP  | MAX | UNIT |

|------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------|------|------|-----|------|

| GaN FET                |                                                 |                                                                                                       |      |      |     |      |

|                        |                                                 | $R_{DRV} = 15 \text{ k}\Omega, I_L = 3 \text{ A}$                                                     | 100  |      |     |      |

| dv/dt                  | Turn-on Drain Slew Rate                         | $R_{DRV} = 55 \text{ k}\Omega, I_L = 3 \text{ A}$                                                     |      | 50   |     | V/ns |

|                        |                                                 | R <sub>DRV</sub> = 150 kΩ, I <sub>L</sub> = 3 A                                                       |      | 25   |     |      |

| ∆dv/dt                 | Slew Rate Variation                             | turn on, $I_L = 3 A$ , $R_{DRV} = 15 k\Omega$ 25                                                      |      |      |     |      |

| dv/dt                  | Edge Rate Immunity                              | Drain dv/dt, device remains off<br>inductor-fed, max di/dt = 10 A/ns                                  |      | 150  |     | V/ns |

| STARTUP                | -                                               | •                                                                                                     |      |      |     |      |

| t <sub>START</sub>     | Startup Time, V <sub>IN</sub> rising above UVLO | Time until gate responds to IN $C_{NEG}$<br>= 1 µF, $C_{LDO}$ = 0 µF                                  | 600  |      |     | μs   |

| DRIVER                 |                                                 | · · ·                                                                                                 |      |      |     |      |

| t <sub>pd,on</sub>     | Propagation delay, turn on                      | IN rising to $I_{DS} > 1$ A, $V_{DS} = 100$ V<br>R <sub>DRV</sub> = 15 k $\Omega$ , $V_{NEG} = -14$ V | 14.4 |      |     | ns   |

| t <sub>delay,on</sub>  | Turn on delay time                              | $I_{DS}$ > 1 A to $V_{DS}$ < 320 V, $R_{DRV}$ = 15k $\Omega$                                          |      | 4.4  |     | ns   |

| t <sub>VDS,ft</sub>    | VDS fall time                                   | $V_{DS} = 320$ V to $V_{DS} = 80$ V, $I_D = 3$ A                                                      | 2.7  |      |     | ns   |

| t <sub>pd,off</sub>    | Propagation delay, turn off                     | IN falling to $V_{DS} > 10 \text{ V}$ ; $I_D = 3 \text{ A}$                                           |      | 17.4 |     | ns   |

| t <sub>delay,off</sub> | Turn off delay time                             | $V_{DS} = 10 \text{ V to } V_{DS} = 80 \text{ V}, I_D = 3 \text{ A}$                                  |      | 5.5  |     | ns   |

| t <sub>VDS,rt</sub>    | VDS rise time                                   | $V_{DS}$ = 80 V to $V_{DS}$ = 320 V, $I_{D}$ = 3 A                                                    |      | 11.7 |     | ns   |

| FAULT                  |                                                 |                                                                                                       |      |      |     |      |

| t <sub>curr</sub>      | Current Fault Delay                             | $I_{DS} > I_{TH}$ to FAULT low                                                                        |      | 50   |     | ns   |

| t <sub>blank</sub>     | Current Fault Blanking Time                     | $V_{IN}$ > $V_{IH}$ to end of blanking,<br>RDRV=15k $\Omega$                                          |      | 55   |     | ns   |

| t <sub>reset</sub>     | Fault reset time                                | IN held low                                                                                           | 250  | 350  | 500 | μs   |

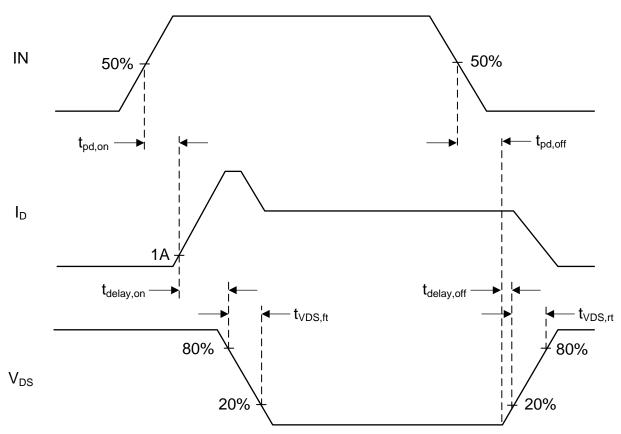

# 7 Parameter Measurement Information

#### **Switching Parameters**

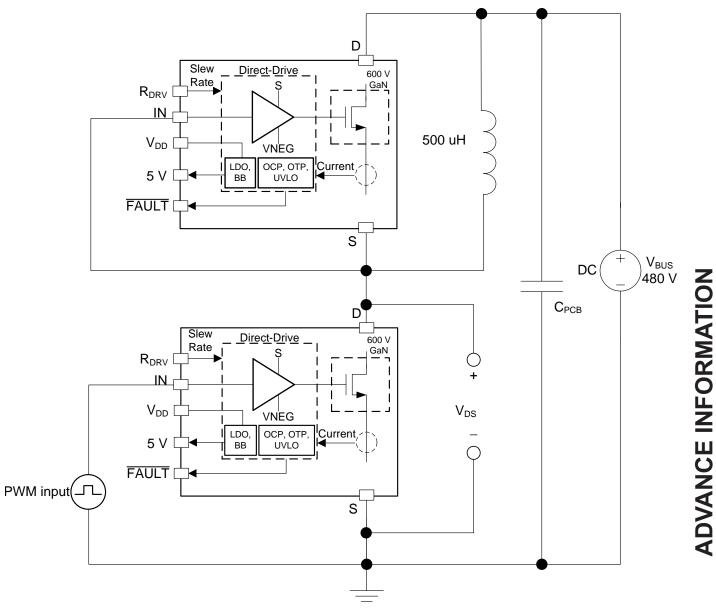

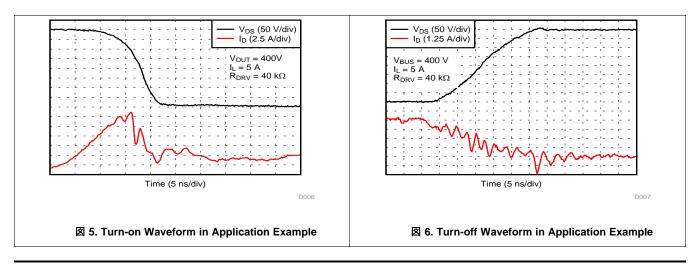

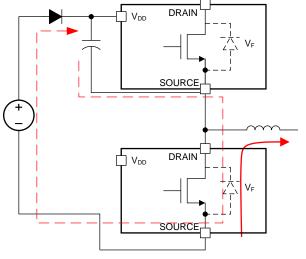

The circuit used to measure most switching parameters is shown in  $\boxtimes$  1. The top LMG341xR150 in this circuit is used to re-circulate the inductor current and functions in third-quadrant mode only. The bottom device is the active device; it is turned on to increase the inductor current to the desired test current. The bottom device is then turned off and on to create switching waveforms at a specific inductor current. Both the drain current (at the source) and the drain-source voltage is measured. The specific timing measurement is shown in  $\boxtimes$  2. It is recommended to use the half-bridge as double pulse tester. Excessive 3rd quadrant operation may over heat the top LMG341xR150.

Parameter Measurement Information (continued)

$\blacksquare$  1. Circuit Used to Determine Switching Parameters

# Parameter Measurement Information (continued)

図 2. Measurement to Determine Propagation Delays and Slew Rates

#### **Turn-on Delays**

The timing of the turn-on transition has three components: propagation delay, turn-on delay and fall time. The first component is the propagation delay of the driver from when the input goes high to when the GaN FET starts turning on (represented by 1 A drain current). The turn-on delay is the delay from when the FET starts turning on to when the drain voltage swings down by 20 percent. Finally, the  $V_{DS}$  fall time is the time it takes the drain voltage to slew between 80 percent and 20 percent of the bus voltage. The drive-strength resistor value has a large effect on turn-on delay and  $V_{DS}$  fall time but does not affect the propagation delay significantly.

# **Turn-off Delays**

The timing of the turn-off transition has three components: propagation delay, turn-off delay and rise time. The first component is the propagation delay of the driver from when the input goes low to when the GaN FET starts turning off. The turn-off delay is the delay from when the FET starts turning of (represented by the drain rising above 10 V) to when the drain voltage swings up by 20 percent. Finally, the  $V_{DS}$  rise time is the time it takes the drain voltage to slew between 20 percent and 80 percent of the bus voltage. The turn-off delays of the LMG341xR150 are independent of the drive-strength resistor but the turn-off delay and the  $V_{DS}$  rise time are heavily dependent on the load current.

#### **Drain Slew Rate**

The slew rate, measured in volts per nanosecond, is measured on the turn-on edge of the LMG341xR150. The slew rate is considered over the  $V_{DS}$  fall time, where the drain falls from 80 percent to 20 percent of the bus voltage. The drain slew rate is thus given by 60 percent of the bus voltage divided by the  $V_{DS}$  fall time. This drain slew rate is dependent on the RDRV value and is only slightly affected by drain current.

# 8 Detailed Description

DRAIN

### 8.1 Overview

LMG341xR150 is a high-performance 600-V GaN transistor with integrated gate driver. The GaN transistor provides ultra-low input and output capacitance and zero reverse recovery. The lack of reverse recovery enables efficient operation in half-bridge and bridge-based topologies.

TI utilizes a Direct Drive architecture to control the GaN FET within the LMG341xR150. When the driver is powered up, the GaN FET is controlled directly with the integrated gate driver. This architecture provides superior switching performance compared with the traditional cascode approach.

The integrated driver solves a number of challenges using GaN devices. The LMG341xR150 contains a driver specifically tuned to the GaN device for fast driving without ringing on the gate. The driver ensures the device stays off for high drain slew rates up to 150 V/ns. In addition, the integrated driver protects against faults by providing over-current and over-temperature protection. This feature can protect the system in case of a device failure, or prevent a device failure in the case of a controller error or malfunction.

Unlike silicon MOSFETs, there is no p-n junction from source to drain in GaN devices. That is why GaN devices have no reverse recovery losses. However, the GaN device can still conduct from source to drain in 3rd quadrant of operation similar to a body diode but with higher voltage drop and higher conduction loss. 3rd quadrant operation can be defined as follows; when the GaN device is turned off and negative current pulls the drain node voltage to be lower than its source. The voltage drop across GaN device during 3rd quadrant operation is high; therefore, it is recommended to operate with synchronous switching and keep the duration of 3rd quadrant operation at minimum.

8.2 Functional Block Diagram

# 8.3 Feature Description

The LMG341xR150 includes numerous features to provide increased switching performance and efficiency in customers' applications while providing an easy-to-use solution.

#### 8.3.1 Direct-Drive GaN Architecture

The LMG341xR150 utilizes a series FET to ensure the GaN module stays off when  $V_{DD}$  is not applied. When this FET is off, the gate of the GaN transistor is held within a volt of the FET's source. As the silicon FET blocks the drain voltage, the  $V_{GS}$  of the GaN transistor decreases until it passes its threshold voltage. Then, the GaN transistor turns off and blocks the remaining drain voltage.

When the LMG341xR150 is powered up, the internal buck-boost converter generates a negative voltage ( $V_{NEG}$ ) that is sufficient to directly turn off the GaN transistor. In this case, the silicon FET is held on and the GaN transistor is gated directly with the negative voltage. During operation, this removes the switching loss of silicon FET.

#### 8.3.2 Internal Buck-Boost DC-DC Converter

An internal inverting buck-boost converter generates a regulated negative rail for the turn-off supply of the GaN device. The buck-boost converter is controlled by a peak current mode, hysteretic controller. In normal operation, the converter remains in discontinuous-conduction mode, but may enter continuous-conduction mode during startup and overload conditions. The converter is controlled internally and requires only a single surface-mount inductor and output bypass capacitor. For recommendations on the required passives, see *Buck-Boost Converter Design*.

#### 8.3.3 Internal Auxiliary LDO

An internal low-dropout regulator is provided to supply external loads, such as digital isolators for the high-side drive signal. It is capable of delivering up to 5 mA to an external load. A bypass capacitor with 0.1  $\mu$ F typical is recommended. If the digital isolator or the LDO output is not used, LMG341xR150 can start up faster with no bypass LDO capacitor.

#### 8.3.4 Fault Detection

The GaN driver includes built-in over-current protection (OCP), over-temperature protection (OTP) and under voltage lockout (UVLO).

#### 8.3.4.1 Over-current Protection

The OCP circuit monitors the LMG341xR150's drain current and compares that current signal with an internallyset limit. Upon detection of the over-current, the family of GaN FETs has two optional protection actions: 1) latched overcurrent protection; and 2) cycle-by-cycle overcurrent protection.

LMG3410R150 provides 1) latched OCP option, by which the FET is shut off and held off until the fault is reset by either holding the IN pin low for more than 350 microseconds or removing power from VDD.

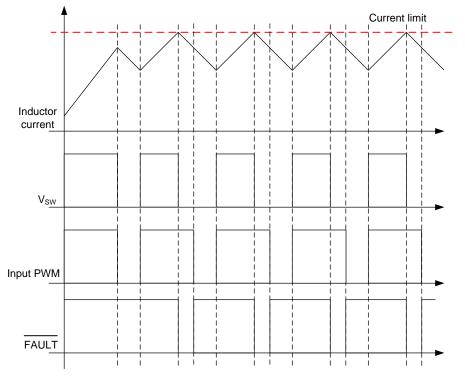

LMG3411R150 provides 2) cycle-by-cycle OCP option. In this mode, the GaN FET is shut off and held off when overcurrent happens but the output fault signal will clear after the input PWM goes low. In the next cycle, the FET can turn on as normal. The cycle-by-cycle function can be used in cases where steady state operation is below the OCP level but transient response can still reach high current, while the circuit operation cannot be paused. It also prevents the power stage from overheating by having overcurrent induced conduction loss.

During cycle-by-cycle operation, after the current reaches the upper limit but the PWM input is still high, the load current can flow through the third quadrant of the other FET of a half-bridge with no synchronous rectification. The extra high negative voltage drop (-6V to -8V) from drain to source could lead to high third quadrant loss, similar to dead time loss but with much longer time. An operation scheme of cycle-by-cycle current limitation is shown as  $\boxtimes$  3.Therefore, it is critical to design the control scheme to make sure the number of switching cycles in cycle-by-cycle mode is limited, or to change PWM input based on the fault signal to shorten the time in third quadrant conduction mode of the power stage.

OCP circuit has a 20ns typical blanking at slew rate of 100V/ns to prevent false triggering during switch node transitions. The blanking time increases with respect to lower slew rates accordingly. This fast response OCP circuit protects the GaN device even under a hard short-circuit condition.

### Feature Description (continued)

図 3. Cycle-by-cycle OCP Operation

#### 8.3.4.2 Over-Temperature Protection and UVLO

The over-temperature protection circuit measures the temperature of the driver die and trips if the temperature exceeds the over-temperature threshold (typically 165 °C). Upon an over-temperature condition, the GaN device is held off until temperature falls below the hysteresis limit, typically 15 degrees below the turn-off threshold.

The FAULT output is a push-pull output indicating the readiness and fault status of the driver. It is held low when starting up until the safety FET is turned on. In an OCP or OTP fault condition, it is held low until the fault latches are reset or fault is cleared. If the power supplies go below the UVLO thresholds, power transistor switching is disabled and FAULT is held low until the power supplies recover.

#### 8.3.5 Drive Strength Adjustment

To allow for an adjustable slew rate to control stability and ringing in the circuit, as well as an adjustment to pass electro-magnetic compliance (EMC) standards, LMG341xR150 allows the user to adjust its drive strength. A resistor is connected the RDRV pin and ground. The value of the resistor determines the slew rate of the device during turn-on between 30V/ns and 100V/ns; The turn-off slew rate is dependent on the load current; therefore, it is not controlled.

#### 8.4 Device Functional Modes

#### 8.4.1 Low-Power Mode

In some applications, it is important to reduce quiescent current during low power mode such as start up or burst. The LPM pins reduces the quiescent current to support low power modes. When LPM is pulled low, the supply current in the low-power mode is typically 80µA. Once this pin is pulled high, the buck-boost converter will start up and LMG341xR150 will be ready to operate within 1 ms.

# 9 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 9.1 Application Information

The LMG341xR150 is a single-channel GaN power stage targeting high-voltage applications. It targets hardswitched and soft-switched applications running from a 350V to 480V bus such as power-factor correction (PFC) applications. As GaN devices such as the LMG341xR150 have zero reverse-recovery charge, they are wellsuited for hard-switched half-bridge applications, such as the totem-pole bridgeless PFC circuit. It is also wellsuited for resonant DC-DC converters, such as the LLC and phase-shifted full-bridge. As both of these converters utilize the half-bridge building block, this section will describe how to use the LMG341xR150 in a halfbridge configuration.

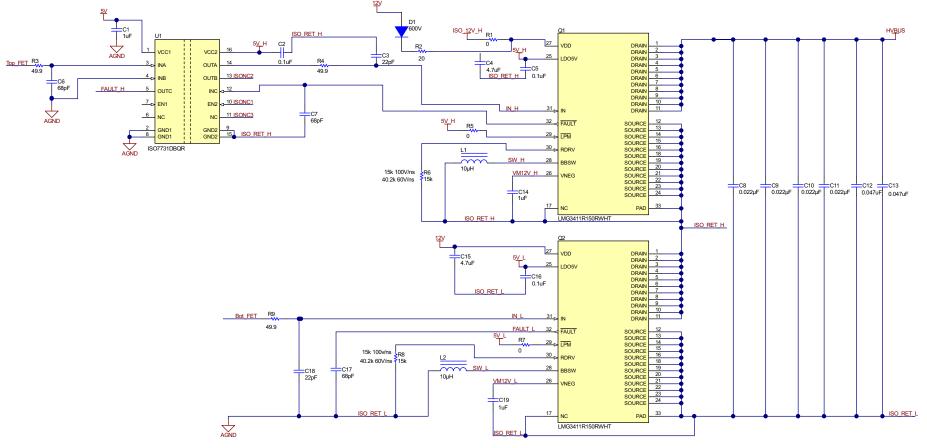

# 9.2 Typical Application

図 4. Typical Half-Bridge Application

**ADVANCE INFORMATION**

#### 9.2.1 Design Requirements

This design example is for a hard-switched boost converter which is representative of PFC applications. The system parameters considered are as follows.

| DESIGN PARAMETER         | EXAMPLE VALUE |

|--------------------------|---------------|

| Input Voltage            | 200 VDC       |

| Output Voltage           | 400 VDC       |

| Input (Inductor) Current | 5 A           |

| Switching Frequency      | 100 kHz       |

#### 表 1. Design Parameters

#### 9.2.2 Detailed Design Procedure

In high-voltage power converters, correct circuit design and PCB layout is essential to obtaining a highperformance and even functional power converter. While the general procedure for designing a power converter is out of the scope of this document, this datasheet describes how to utilize the LMG341xR150 to build efficient, well-behaved power converters.

#### 9.2.2.1 Slew Rate Selection

The LMG341xR150 supports slew rate adjustment through connecting a resistor from RDRV to source. The choice of RDRV will control the slew rate of the drain voltage of the device between approximately 25 V/ns and 100 V/ns. The slew rate adjustment is used to control the following aspects of the power stage:

- Switching loss in a hard-switched converter

- Radiated and conducted EMI generated by the switching stage

- Interference elsewhere in the circuit coupled from the switch node

- Voltage overshoot and ringing on the switch node due to power loop inductance and other parasitics

When increasing the slew rate, the switching power loss will decrease, as the portion of the switching period where the switch simultaneous conducts high current while blocking high voltage is decreased. However, by increasing the slew rate of the device, the other three aspects of the power stage get worse. Following the design recommendations in this datasheet will help mitigate the system-related challenges related to high slew rate. Ultimately, it is up to the power designer to ensure the chosen slew rate provides the best performance in his or her end application.

#### 9.2.2.1.1 Startup and Slew Rate with Bootstrap High-Side Supply

Using a bootstrap supply for the high-side LMG341xR150 places additional constraints on the startup of the circuit. Before the high-side LMG341xR150 functions correctly, its VDD, LDO5V and VNEG power supplies must start up and be functional. Prior to the device powering up, the GaN device operates in cascode mode with reduced performance. In particular, under high drain slew rate (dv/dt), the transistor can conduct to a small extent and cause additional power dissipation. The correct startup procedure for a bootstrap-supplied half-bridge depends on the circuit used.

In a buck converter without pre-bias, where the initial output voltage is zero, the startup procedure is straightforward. In this case, before switching begins, turn on the low-side device to allow the high-side bootstrap transistor to charge up. When the FAULT signal goes high, the high-side device has powered up completely, and normal switching can begin.

In a boost converter or a buck converter with a pre-biased output, it is necessary to operate the circuit in switching PWM mode while the high-side LMG341xR150 is powering up. With a boost converter, if the low-side device is held on, the power inductor current will likely run away and the inductor will saturate. To start up a boost converter, the duty cycle has to be very low and gradually increase to charge the output to the desired value without the inductor current reaching saturation. This pulse sequence can be performed open-loop or using a current-mode controller. This startup mode is standard for boost-type converters.

However, with the LMG341xR150, during the boost converter startup, significant shoot-through current can occur for high drain slew rates while starting up. This shoot-through current is approximately 1.25  $\mu$ C per switching event at 50 V/ns, and is comparable to a reverse-recovery event. If this shoot-through current is undesirable, the drain slew rate of the low-side device must be reduced during startup. In 🛛 4, the FAULT output from the high-side device is used to gate MOSFET Q1. When FAULT from the high-side is high, once the device is powered up, Q1 turns on and reduces the effective resistance connected to RDRV on the low-side LMG341xR150. With this circuit, the dv/dt of the low-side device can be held low to reduce power dissipation and reduce ringing during high-side startup, but then increase to reduce switching loss during normal operation.

#### 9.2.2.2 Signal Level-Shifting

As the LMG341xR150 is a single-channel power stage, two devices are used to construct a half-bridge converter, such as the one shown in  $\boxtimes$  4. A high-voltage level shifter or digital isolator must be used to provide signals to the high-side device. Using an isolator for the low-side device is optional but will equalize propagation delays between the high-side and low-side signal path, as well as providing the ability to use different grounds for the power stage and the controller. If an isolator is not used on the low-side device, the control ground and the power ground must be connected at the LMG341xR150, as described in *Layout Guidelines*, and nowhere else on the board. With the high current slew rate of the fast-switching GaN device, any ground-plane inductance common with the power path may cause oscillation or instability in the power stage without the use of an isolator.

Choosing a digital isolator for level-shifting is an important consideration for fault-free operation. Because GaN switches very quickly, exceeding 50 V/ns in hard-switching applications, isolators with high common-mode transient immunity (CMTI) are required. If an isolator suffers from a CMTI issue, it can output a false pulse or signal which can cause shoot-through. In addition, choosing an isolator that is not edge-triggered can improve circuit robustness. In an edge-triggered isolator, a high dv/dt event can cause the isolator to flip states and cause circuit malfunctioning.

On/off keyed isolators are preferred, such as the TI ISO78xxF series, as a high CMTI event would only cause a short (few nanosecond) false pulse, which can be filtered out. To allow for filtering of these false pulses, an R-C filter at the driver input is recommended to ensure these false pulses can be filtered. If issues are observed, values of 1 k $\Omega$  and 22 pF can be used to filter out any false pulses.

#### 9.2.2.3 Buck-Boost Converter Design

The Buck-boost converter generates the negative voltage necessary to turn off the direct-drive GaN FET. While it is controlled internally, it requires an external power inductor and output capacitor. The converter is designed to use a 10  $\mu$ H inductor and a 1  $\mu$ F output capacitor. As the peak current of the buck-boost is limited to less than 350 mA, the inductor chosen must have a saturation current above 350 mA. A TDK Corporation VLS201610HBX-100M-1 10  $\mu$ H SMT inductor in a 0806 package is recommended. This inductor is connected between the BBSW pin and ground. A 1  $\mu$ F, 25V 0603 bypass capacitor is required between V<sub>NEG</sub> and ground. Due to the voltage coefficient of X7R capacitors, a 1  $\mu$ F capacitor will provide the required minimum 0.45  $\mu$ F capacitance when operating.

#### 9.2.3 Application Curves

### 9.3 Paralleling GaN Devices

LMG341xR150s can be paralleled directly in soft-switching applications. As for hard-switching applications, small decoupling inductors should be utilized to parallel the two half-bridge LMG341xR150s. This type of setup prevents current and thermal unbalances among the parallel devices due to any propagation delay and gate-source threshold voltage mismatches, and other factors.

# 9.4 Do's and Don'ts

The successful use of GaN devices in general and the LMG341xR150 in particular depends on proper use of the device. When using the LMG341xR150, **DO**:

- Read and fully understand the datasheet, including the application notes and layout recommendations

- Use a four-layer board and place the return power path on an inner layer to minimize power-loop inductance

- · Use small, surface-mount bypass and bus capacitors to minimize parasitic inductance

- Use the proper size decoupling capacitors and locate them close to the IC as described in the *Layout Guidelines* section

- Use a signal isolator to supply the input signal for the low side device. If not, ensure the signal source is connected to the signal GND plane which is tied to the power source **only** at the LMG341xR150 IC

- Use the FAULT pin to determine power-up state and to detect over-current and over-temperature events and safely shut off the converter.

To avoid issues in your system when using the LMG341xR150, DON'T:

- Use a single-layer or two-layer PCB for the LMG341xR150 as the power-loop and bypass capacitor inductances will be excessive and prevent proper operation of the IC

- · Reduce the bypass capacitor values below the recommended values

- · Allow the device to experience drain transients above 600 V as they may damage the device

- Allow significant third-quadrant conduction when the device is OFF or unpowered, which may cause overheating. Self-protection feature cannot protect the device in this mode of operation

- Ignore the FAULT pin output.

# **10** Power Supply Recommendations

The LMG341xR150 requires an unregulated 12-V supply to power its internal driver and fault protection circuitry. The low-side supply can be supplied from the local controller supply. The high-side device's supply must come from an isolated supply or bootstrap supply.

#### **10.1** Using an Isolated Power Supply

Using an isolated power supply to power the high-side device has the advantage that it will work regardless of continued power-stage switching or duty cycle. It can also power the high-side device before power-stage switching begins, eliminating the power-loss concern of switching with an unpowered LMG341xR150 (see *Startup and Slew Rate with Bootstrap High-Side Supply* for details). Finally, a properly-selected isolated supply will contribute fewer parasitics to the switching power stage, increasing power-stage efficiency. However, the isolated power supply solution is larger and more expensive than the bootstrap solution.

The isolated supply can be constructed from an output of a flyback or FlyBuck<sup>™</sup> converter, or using an isolated power module. When using an unregulated supply, ensure that the input to the LMG341xR150 does not exceed the maximum supply voltage. If necessary, a 18 V zener to clamp the VDD voltage supplied by the isolated power converter. Minimizing the inter-winding capacitance of the isolated power supply or transformer is necessary to reduce switching loss in hard-switched applications.

#### **10.2 Using a Bootstrap Diode**

When used in a half-bridge configuration, a floating supply is necessary for the top-side switch. Due to the switching performance of LMG341xR150, *a transformer-isolated power supply is recommended*. With caution, a bootstrap supply can be used with the recommendations in this section.

#### 10.2.1 Diode Selection

LMG341xR150 has no reverse-recovery charge and little output charge. Hard-switched circuits using LMG341xR150 also exhibit high voltage slew rates. A compatible bootstrap diode must exhibit low output charge and, if used in a hard-switching circuit, very low reverse-recovery charge.

For soft-switching applications, the MCC UFM15PL ultra-fast silicon diode can be used. The output charge of 2.7 nC is small in comparison with the switching transistors, so it will have little influence on switching performance. In a hard-switching application, the reverse recovery charge of the silicon diode may contribute an additional loss to the circuit.

For hard-switched applications, a silicon carbide diode can be used to avoid reverse-recovery effects. The Cree C3D1P7060Q SiC diode has an output charge of 4.5 nC and a reverse recovery charge of about 5 nC. There will be some losses using this diode due to the output charge, but these will not dominate the switching stage's losses.

#### 10.2.2 Managing the Bootstrap Voltage

In a synchronous buck, totem-pole PFC, or other converter where the low-side switch occasionally operates in third-quadrant mode, it is important to consider the bootstrap supply. During the dead time, the bootstrap supply charges through a path that includes the third-quadrant voltage drop of the low-side LMG341xR150. This third-quadrant drop can be large, which may over-charge the bootstrap supply in certain conditions. The V<sub>DD</sub> supply of LMG341xR150 must not exceed 18 V in bootstrap operation.

TEXAS INSTRUMENTS

www.tij.co.jp

# Using a Bootstrap Diode (continued)

Copyright © 2017, Texas Instruments Incorporated

#### 図 7. Charging Path for Bootstrap Diode

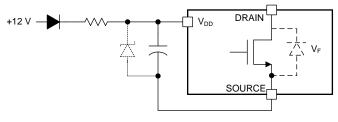

The recommended bootstrap supply connection includes a bootstrap diode and a series resistor with an optional zener as shown in ⊠ 8. The series resistor limits the charging current at startup and when the low-side device is operating in third-quadrant mode. This resistor must be chosen to allow sufficient current to power the LMG341xR150 at the desired operating frequency. At 100 kHz operation, a value of approximately 5.1 ohms is recommended. At higher frequencies, this resistor value should be reduced or the resistor omitted entirely to ensure sufficient supply current.

Copyright © 2017, Texas Instruments Incorporated

図 8. Suggested Bootstrap Regulation Circuit

Using a series resistor with the bootstrap supply will create a charging time constant in conjunction with the bypass capacitance on the order of a microsecond. When the dead time, or third-quadrant conduction time, is much lower than this time constant, the bootstrap voltage will be well-controlled and the optional zener clamp in  $\aleph$  8 will not be necessary. If a large deadtime is needed, a 14-V zener diode can be used in parallel with the V<sub>DD</sub> bypass capacitor to prevent damaging the high-side LMG341xR150.

#### 10.2.3 Reliable Bootstrap Start-up

In some applications such as boost converter, the low side LMG341xR150 may need to start switching at high frequency while high side LMG341xR150 is not fully biased. If low side GaN device turn-on speed is adjusted to achieve high slew rate, the high side GaN device can turn-on unintentionally as high dv/dt can charge high side GaN device drain to source capacitance. For reliable operation, the slew rate should be slowed down to 30 V/ns by changing the resistance of RDRV pin of the low side LMG341xR150 until high side LMG341xR150's bias is fully settled. This can be monitored through the FAULT output of high side LMG341xR150.

### 11 Layout

#### 11.1 Layout Guidelines

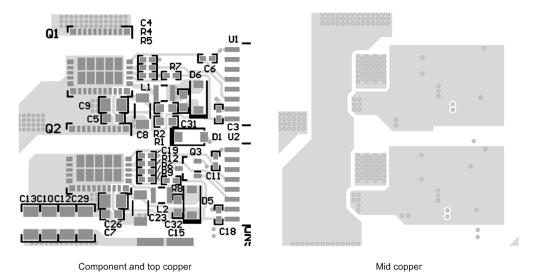

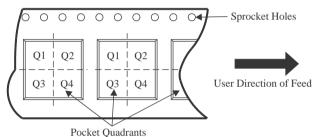

The layout of the LMG341xR150 is critical to its performance and functionality. Because the half-bridge configuration is typically used with these GaN devices, layout recommendations will be considered with this configuration. A four-layer or higher layer count board is required to reduce the parasitic inductances of the layout to achieve suitable performance.

#### 11.1.1 Power Loop Inductance

The power loop, comprising the two devices in the half bridge and the high-voltage bus capacitance, undergoes large *di/dt* during switching events. By minimizing the inductance of this loop, ringing and electro-magnetic interference (EMI) can be reduced, as well as reducing voltage stress on the devices.

This loop inductance is minimized by locating the power devices as close together as possible. The bus capacitance is positioned in line with the two devices, either below the low-side device or above the high-side device, on the same side of the PCB. The return path (PGND in this case) is located on the second layer on the PCB in close proximity to the top layer. By using an inner layer and not the bottom layer, the vertical dimension of the loop is reduced, thus minimizing inductance. A large number of vias near both the device terminal and bus capacitance carries the high-frequency switching current to the inner layer while minimizing impedance.

#### 11.1.2 Signal Ground Connection

The LMG341xR150's SOURCE pin is also signal ground reference. The signal GND plane should be connected to SOURCE with low impedance kelvin connection. In addition, the return path for the passives associated to the driver (e.g. bypass capacitance) must be connected to the GND plane. In 🛛 9, local signal GND planes are located on the second copper layer to act as the return for the local circuitry. The local signal GND planes are isolated from the high-current SOURCE plane except the kelvin connection at the source pin through enough low impedance vias.

#### 11.1.3 Bypass Capacitors

The gate drive loop impedance must also be minimized to yield strong performance. Although the gate driver is integrated on package, the bypass capacitance for the driver is placed externally on the PCB board. As the GaN device is turned off to a negative voltage, the impedance of the negative source is included in the crucial turn-off path. As the critical hold-off path passes through this external bypass capacitor attached to  $V_{NEG}$ , this capacitor must be located close to the LMG341xR150. In the 🖾 9,  $V_{NEG}$  bypass capacitors C9 and C26 are located immediately adjacent to the pins on the IC with a direct connection to the SOURCE pin.

The bypass capacitors for the input supply (C8 and C23) and the 5V regulator (C5 and C7) must also be located immediately next to the IC with a close connection to the ground plane.

#### 11.1.4 Switch-Node Capacitance

GaN devices have very low output capacitance and switch quickly with a high dv/dt, yielding very low switching loss. To preserve this low switching loss, additional capacitance added to the output node must be minimized. The PCB capacitance at the switch node can be minimized by following these guidelines:

- Minimize overlap between the switch-node plane and other power and ground planes

- Thin the GND return path under the high-side device somewhat while still maintaining a low-inductance path

- Choose high-side isolator ICs and bootstrap diodes with low capacitance

- · Locate the power inductor as close to the power stage as possible

- · Power inductors should be constructed with a single-layer winding to minimize intra-winding capacitance

- If a single-layer inductor is not possible, consider placing a small inductor between the primary inductor and the power stage to effectively shield the power stage from the additional capacitance

- If a back-side heat-sink is used, restrict the switch-node copper coverage on the bottom copper layer to the minimum area necessary to extract the needed heat

#### Layout Guidelines (continued)

#### 11.1.5 Signal Integrity

The control signals to the LMG341xR150 must be protected from the high dv/dt that the GaN power stage produces. Coupling between the control <u>signals</u> and the drain may cause circuit instability and potential destruction. Route the control signals (IN, FAULT and LPM) over a ground plane located on an adjacent layer. For example, in the layout in 🛛 9, all the signals are routed on the top layer directly over the signal GND plane on the first inner copper layer.

The signals for the high-side device are often particularly vulnerable. Coupling between these signals and system ground planes could cause issues in the circuit. Keep the traces associated with the control signals away from drain copper. For the high-side level shifter, ensure no copper from either the input or output side extends beneath the isolator or the device's CMTI may be compromised.

#### 11.1.6 High-Voltage Spacing

Circuits using the LMG341xR150 involve high voltage, potentially up to 600V. When laying out circuits using the LMG341xR150, understand the creepage and clearance requirements in your application and how they apply to the power stage. Functional (or working) isolation is required between the source and drain of each transistor, and between the high-voltage power supply and ground. Functional isolation or perhaps stronger isolation (such as reinforced isolation) may be required between the input circuitry to the LMG341xR150 and the power controller. Choose signal isolators and PCB spacing (creepage and clearance) distances which meet your isolation requirements.

If a heatsink is used to manage thermal dissipation of the LMG341xR150, ensure necessary electrical isolation and mechanical spacing is maintained between the heatsink and the PCB.

#### 11.1.7 Thermal Recommendations

The LMG341xR150 is a lateral transistor grown on a Si substrate. The thermal pad is connected to the Source node. The LMG341xR150 may be used in applications with significant power dissipation, for example, hard-switched power converters. In these converters, cooling using just the PCB may not be sufficient to keep the part at a reasonable temperature. To improve the thermal dissipation of the part, TI recommends a heatsink is connected to the back of the PCB to extract additional heat. Using power planes and numerous thermal vias, the heat dissipated in the LMG341xR150(s) can be spread out in the PCB and effectively passed to the other side of the PCB. A heat sink can be applied to bare areas on the back of the PCB using an adhesive thermal interface material (TIM). The soldermask from the back of the board underneath the heatsink can be removed for more effective heat removal.

Please refer to the *High Voltage Half Bridge Design Guide for LMG3410x Smart GaN FET* application note for more recommendations and performance data on thermal layouts.

# 11.2 Layout Example

Correct layout of the LMG341xR150 and its surrounding components is essential for correct operation. The layout shown here reflects the power stage schematic in  $\mathbb{Z}$  4. It may be possible to obtain acceptable performance with alternate layout schemes, however this layout has been shown to produce good results and is intended as a guideline.

# Layout Example (continued)

Texas INSTRUMENTS

www.tij.co.jp

# 12 デバイスおよびドキュメントのサポート

# 12.1 デバイス・サポート

# 12.1.1 デベロッパー・ネットワークの製品に関する免責事項

デベロッパー・ネットワークの製品またはサービスに関するTIの出版物は、単独またはTIの製品、サービスと一緒に提供さ れる場合に関係なく、デベロッパー・ネットワークの製品またはサービスの適合性に関する是認、デベロッパー・ネットワーク の製品またはサービスの是認の表明を意味するものではありません。

# 12.2 ドキュメントのサポート

#### 12.2.1 関連資料

『LMG3411xスマートGaN FETの高電圧ハーフブリッジ設計ガイド』アプリケーション・レポート

### 12.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.comのデバイス製品フォルダを開いてください。右上の「アラートを受 け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細に ついては、修正されたドキュメントに含まれている改訂履歴をご覧ください。

# 12.4 コミュニティ・リソース

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E<sup>™</sup> Online Community TI's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

Design Support TI's Design Support Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 12.5 商標

FlyBuck, E2E are trademarks of Texas Instruments.

#### 12.6 静電気放電に関する注意事項

これらのデバイスは、限定的なESD(静電破壊)保護機能を内 蔵しています。保存時または取り扱い時は、MOSゲートに対す る静電破壊を防 ▲ ● 上するために、リード線同士をショートさせておくか、デバイスを導電フォームに入れる必要があります。

# 12.7 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

# 13 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、そのデバイスに ついて利用可能な最新のデータです。このデータは予告なく変更されることがあり、ドキュメントが改訂される場合もありま す。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

# PACKAGING INFORMATION

| Orderable Device | Status | Package Type | •       | Pins | •    | Eco Plan               | Lead finish/  | MSL Peak Temp       | Op Temp (°C) | Device Marking  | Samples |

|------------------|--------|--------------|---------|------|------|------------------------|---------------|---------------------|--------------|-----------------|---------|

|                  | (1)    |              | Drawing |      | Qty  | (2)                    | Ball material | (3)                 |              | (4/5)           |         |

| LMG3410R150RWHR  | ACTIVE | VQFN         | RWH     | 32   | 2000 | RoHS-Exempt<br>& Green | NIPDAU        | Level-3-260C-168HRS | -40 to 150   | LMG3410<br>R150 | Samples |

| LMG3410R150RWHT  | ACTIVE | VQFN         | RWH     | 32   | 250  | RoHS-Exempt<br>& Green | NIPDAU        | Level-3-260C-168HRS | -40 to 150   | LMG3410<br>R150 | Samples |

| LMG3411R150RWHR  | ACTIVE | VQFN         | RWH     | 32   | 2000 | RoHS-Exempt<br>& Green | NIPDAU        | Level-3-260C-168HRS | -40 to 150   | LMG3411<br>R150 | Samples |

| LMG3411R150RWHT  | ACTIVE | VQFN         | RWH     | 32   | 250  | RoHS-Exempt<br>& Green | NIPDAU        | Level-3-260C-168HRS | -40 to 150   | LMG3411<br>R150 | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

www.ti.com

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

Texas

www.ti.com

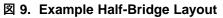

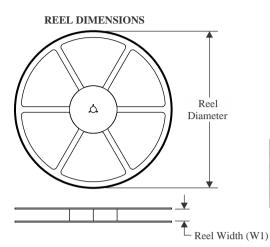

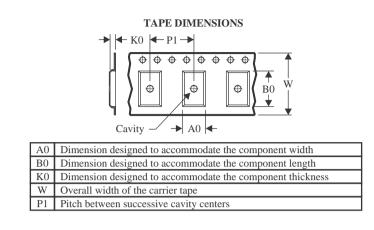

# TAPE AND REEL INFORMATION

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |      |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | -    | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| LMG3410R150RWHR             | VQFN | RWH                | 32 | 2000 | 330.0                    | 16.4                     | 8.3        | 8.3        | 2.25       | 12.0       | 16.0      | Q2               |

| LMG3411R150RWHR             | VQFN | RWH                | 32 | 2000 | 330.0                    | 16.4                     | 8.3        | 8.3        | 2.25       | 12.0       | 16.0      | Q2               |

www.ti.com

# PACKAGE MATERIALS INFORMATION

19-Apr-2024

\*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LMG3410R150RWHR | VQFN         | RWH             | 32   | 2000 | 350.0       | 350.0      | 43.0        |

| LMG3411R150RWHR | VQFN         | RWH             | 32   | 2000 | 350.0       | 350.0      | 43.0        |

# TEXAS INSTRUMENTS

www.ti.com

# TRAY

PACKAGE MATERIALS INFORMATION

L - Outer tray length without tabs КО -Outer trav height + + + + +╋ ++++++++**W** -+Outer trav +width +++ + + ++P1 - Tray unit pocket pitch CW - Measurement for tray edge (Y direction) to corner pocket center - CL - Measurement for tray edge (X direction) to corner pocket center

Chamfer on Tray corner indicates Pin 1 orientation of packed units.

| Device          | Package<br>Name | Package<br>Type | Pins | SPQ  | Unit array<br>matrix | Max<br>temperature<br>(°C) | L (mm) | W<br>(mm) | K0<br>(µm) | P1<br>(mm) | CL<br>(mm) | CW<br>(mm) |

|-----------------|-----------------|-----------------|------|------|----------------------|----------------------------|--------|-----------|------------|------------|------------|------------|

| LMG3410R150RWHR | RWH             | VQFN            | 32   | 2000 | 10 x 26              | 150                        | 315    | 135.9     | 7620       | 11.8       | 10         | 10.35      |

| LMG3410R150RWHT | RWH             | VQFN            | 32   | 250  | 10 x 26              | 150                        | 315    | 135.9     | 7620       | 11.8       | 10         | 10.35      |

| LMG3411R150RWHR | RWH             | VQFN            | 32   | 2000 | 10 x 26              | 150                        | 315    | 135.9     | 7620       | 11.8       | 10         | 10.35      |

| LMG3411R150RWHT | RWH             | VQFN            | 32   | 250  | 10 x 26              | 150                        | 315    | 135.9     | 7620       | 11.8       | 10         | 10.35      |

\*All dimensions are nominal

19-Apr-2024

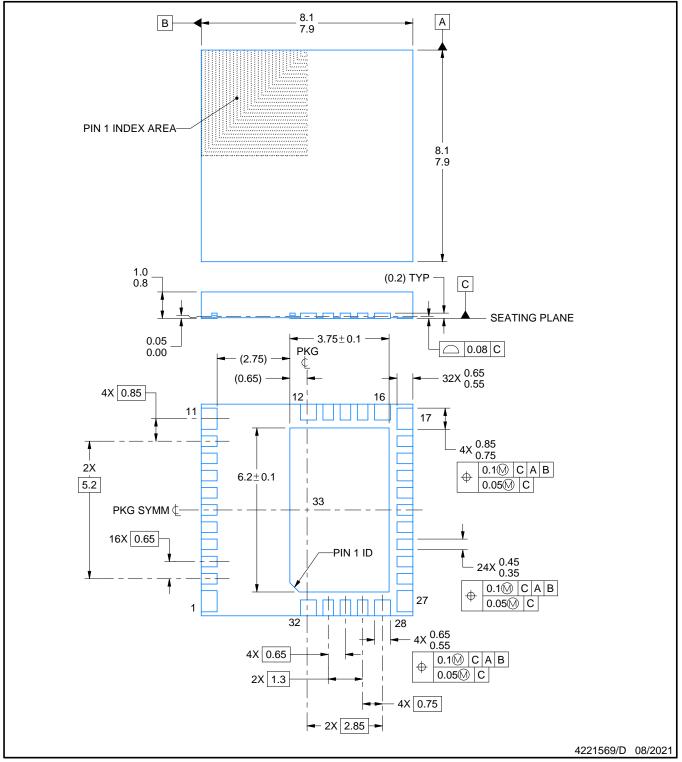

# **RWH0032A**

# **PACKAGE OUTLINE**

# VQFN - 1 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

This drawing is subject to change without notice.

The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

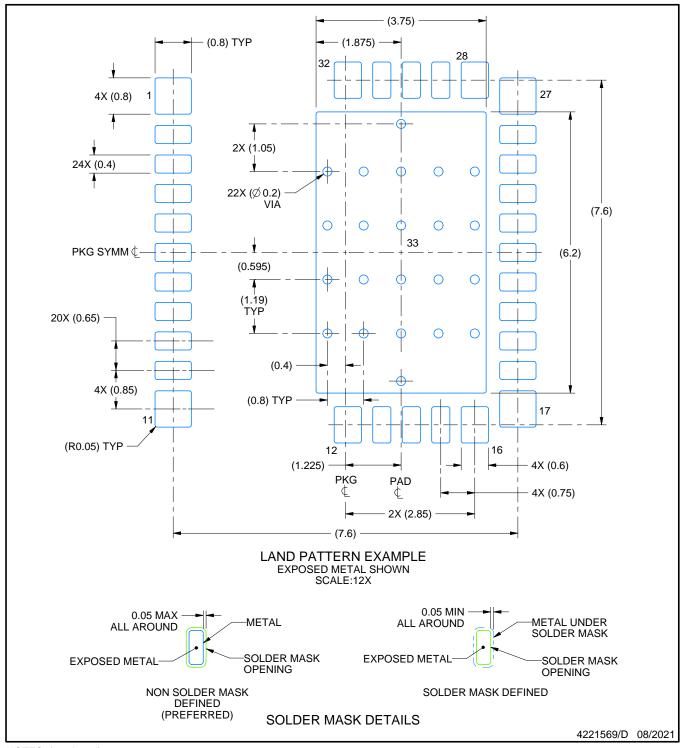

# **RWH0032A**

# **EXAMPLE BOARD LAYOUT**

# VQFN - 1 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

5. Vias are optional depending on application, refer to device data sheet. If some or all are implemented, recommended via locations are shown.

# **RWH0032A**

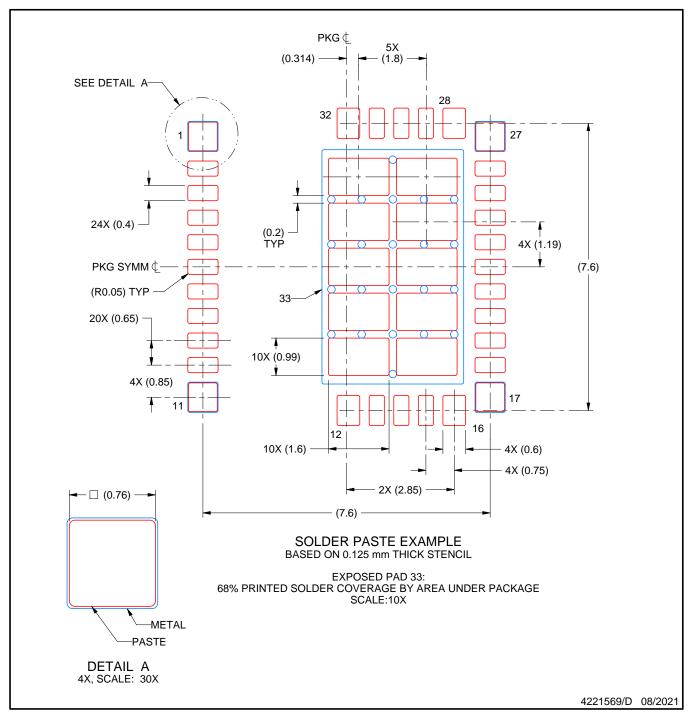

# **EXAMPLE STENCIL DESIGN**

# VQFN - 1 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### 重要なお知らせと免責事項

TIは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや 設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供してお り、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的に かかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあら ゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプ リケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載す ることは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを 自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供され ています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありま せん。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated