TLVM13620

JAJSN58 - APRIL 2022

# TLVM13620 高密度、3V~36V 入力、1V~6V 出力、2A パワー・モジュール、 Enhanced HotRod™ QFN パッケージ

### 1 特長

- 多用途な同期整流降圧 DC/DC モジュール

- MOSFET、インダクタ、コントローラを内蔵

- 広い入力電圧範囲:3V~36V

- 出力電圧を調整可能、1V~6V、温度範囲全体 にわたってセットポイント精度 1%

- 4mm×6mm×1.8mmのオーバーモールド・ パッケージ

- 接合部温度範囲:-40℃~125℃

- 200kHz~2.2MHz の範囲で周波数を調整可能

- 負電圧出力に対応可能

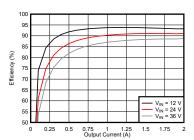

- 全負荷範囲にわたって極めて高い効率を実現

- 93%のピーク効率 (12V<sub>IN</sub>、5V<sub>OUT</sub>、1MHz)

- 外部バイアス・オプションによる効率向上

- シャットダウン時静止電流: 0.6µA (標準値)

- 2A 負荷でのドロップアウト電圧: 0.3V (標準

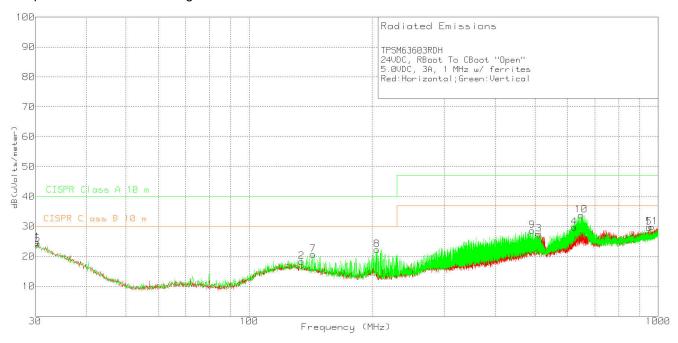

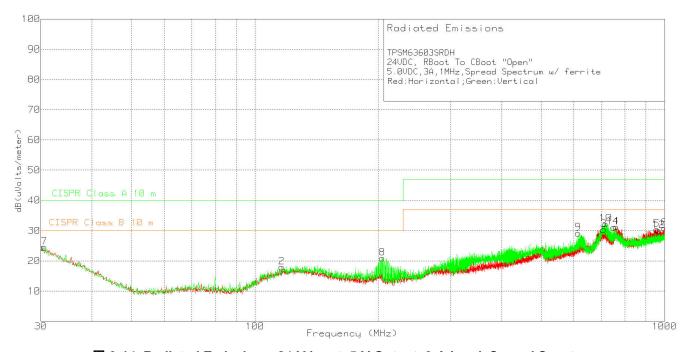

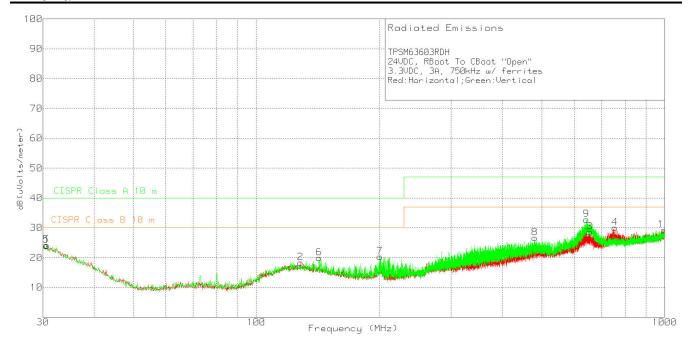

- 非常に小さい伝導および放射 EMI シグネチャ

- デュアル入力パスと内蔵コンデンサを備えた低 ノイズ・パッケージにより、スイッチのリンギ ングが減少

- 固定周波数 FPWM 動作モード

- CISPR 11 および 32 Class B の放射規格に準拠

- スケーラブルな電源に好適

- TLVM13630 (36V、3A) とピン互換

- 堅牢な設計のための本質的な保護機能

- 高精度のイネーブル入力とオープン・ドレイン の PGOOD インジケータによるシーケンシン グ、制御、V<sub>IN</sub> UVLO

- ヒカップ・モードによる過電流保護

- ヒステリシス付きのサーマル・シャットダウン

- ・ WEBENCH® Power Designer により、 TLVM13620 を使用するカスタム設計を作成

# 2 アプリケーション

- 試験および測定、航空宇宙および防衛

- ファクトリ・オートメーションおよび制御

- 降圧および反転型の昇降圧電源

### 3 概要

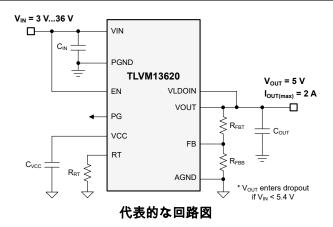

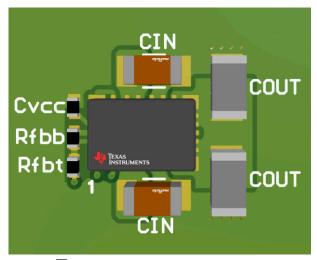

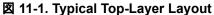

TLVM13620 同期整流降圧パワー・モジュールは、パ ワー MOSFET、シールド付きインダクタ、受動部品 を Enhanced HotRod™ QFN パッケージに実装した、 高集積 36V、2A DC/DC ソリューションです。このモ ジュールは、VIN と VOUT のピンをパッケージの角 に配置し、入力および出力コンデンサのレイアウト配 置を最適化しています。モジュールの下面には大きな 4つのサーマル・パッドがあるため、単純なレイアウ トが可能で、製造時の扱いも容易です。

出力電圧範囲が 1V~6V であるため、TLVM13620 は 小さい PCB フットプリントで低 EMI の設計を迅速か つ容易に実装できるようになっています。このトータ ル・ソリューションを使用すると、外付け部品はわず か 4 個で済み、設計プロセスで磁気および補償のた めの部品選択も不要です。

TLVM13620 モジュールは、スペースが制約される用 途での小型化と簡素化をめざして設計されているだけ でなく、堅牢性の高い性能を実現するためのさまざま な機能を備えています。その例としては、可変入力電 圧 UVLO 用のヒステリシス付き高精度イネーブル、 内蔵 VCC ブートストラップおよび入力コンデンサに よる信頼性向上と高密度化、全負荷電流範囲にわたっ て一定のスイッチング周波数による負荷過渡性能の強 化、 反転アプリケーションでの負電圧出力能力、シ ーケンシング、障害保護、出力電圧監視用の PGOOD インジケータがあります。

#### 製品情報

|           | MANUAL IN  |               |

|-----------|------------|---------------|

| 部品番号(1)   | パッケージ      | 本体サイズ (公称)    |

| TLVM13620 | B0QFN (30) | 4.0mm × 6.0mm |

利用可能なすべてのパッケージについては、このデータシー トの末尾にある注文情報を参照してください。

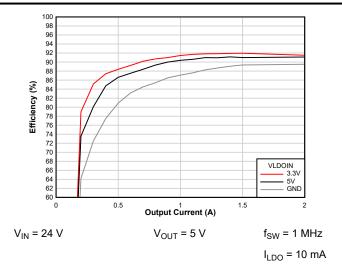

代表的な効率 ( $V_{OUT}$  = 5V、 $f_{SW}$  = 1MHz)

## **Table of Contents**

| <b>1 特長</b> 1                                                       | 8.2 Functional Block Diagram                         | 15   |

|---------------------------------------------------------------------|------------------------------------------------------|------|

| 2 アプリケーション1                                                         | 8.3 Feature Description                              |      |

| 3 概要1                                                               | 8.4 Device Functional Modes                          | 22   |

| 4 Revision History3                                                 | 9 Applications and Implementation                    | 23   |

| 5 Device Comparison Table4                                          | 9.1 Application Information                          | . 23 |

| 6 Pin Configuration and Functions4                                  | 9.2 Typical Applications                             |      |

| 7 Specifications6                                                   | 10 Power Supply Recommendations                      |      |

| 7.1 Absolute Maximum Ratings6                                       | 11 Layout                                            |      |

| 7.2 ESD Ratings6                                                    | 11.1 Layout Guidelines                               |      |

| 7.3 Recommended Operating Conditions7                               | 11.2 Layout Example                                  |      |

| 7.4 Thermal Information7                                            | 12 Device and Documentation Support                  | 33   |

| 7.5 Electrical Characteristics8                                     | 12.1 Device Support                                  | . 33 |

| 7.6 System Characteristics10                                        | 12.2 Documentation Support                           | 34   |

| 7.7 Typical Characteristics11                                       | 12.3 Receiving Notification of Documentation Updates | 34   |

| 7.8 Typical Characteristics — 2-A Device (V <sub>IN</sub> = 12 V)12 | 12.4 サポート・リソース                                       | 34   |

| 7.9 Typical Characteristics — 2-A Device (V <sub>IN</sub> = 24 V)13 | 12.5 Trademarks                                      | 34   |

| 7.10 Typical Characteristics — 2-A Device (V <sub>IN</sub> = 36     | 12.6 Electrostatic Discharge Caution                 | 34   |

| V)14                                                                | 12.7 Glossary                                        | 34   |

| 8 Detailed Description15                                            | 13 Mechanical, Packaging, and Orderable              |      |

| 8.1 Overview                                                        | Information                                          | 35   |

|                                                                     |                                                      |      |

4 Revision History 資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| DATE       | REVISION | NOTES           |

|------------|----------|-----------------|

| April 2022 | *        | Initial Release |

# **5 Device Comparison Table**

| Device    | Orderable Part<br>Number | Mode | Spread<br>Spectrum | Output Voltage | External<br>Sync | Junction<br>Temperature |

|-----------|--------------------------|------|--------------------|----------------|------------------|-------------------------|

| TLVM13620 | TLVM13620RDHR            | FPWM | No                 | Adjustable     | No               | –40°C to 125°C          |

# **6 Pin Configuration and Functions**

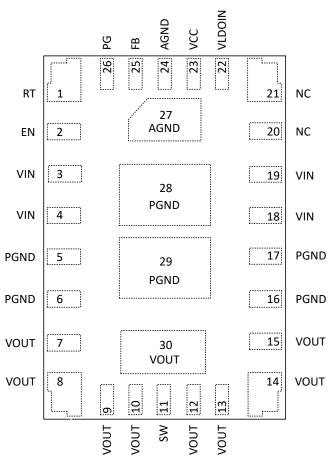

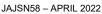

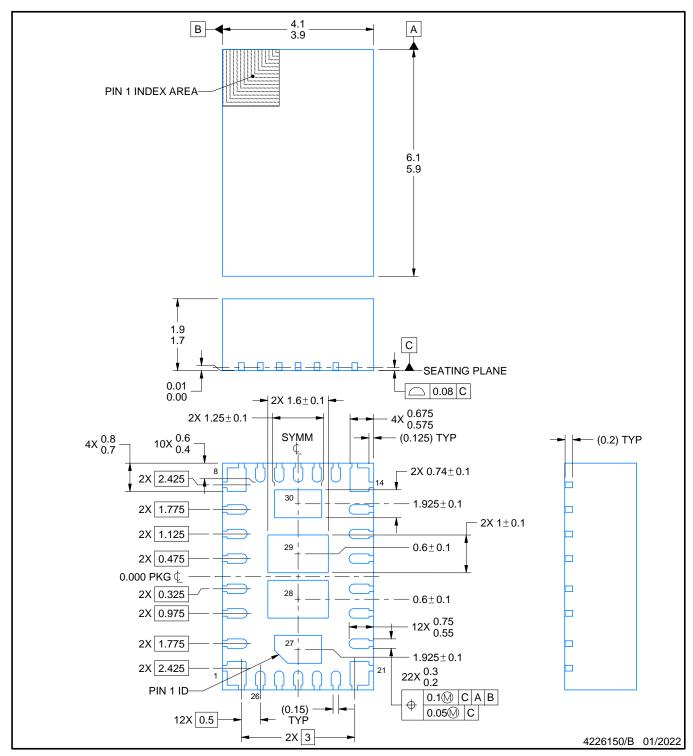

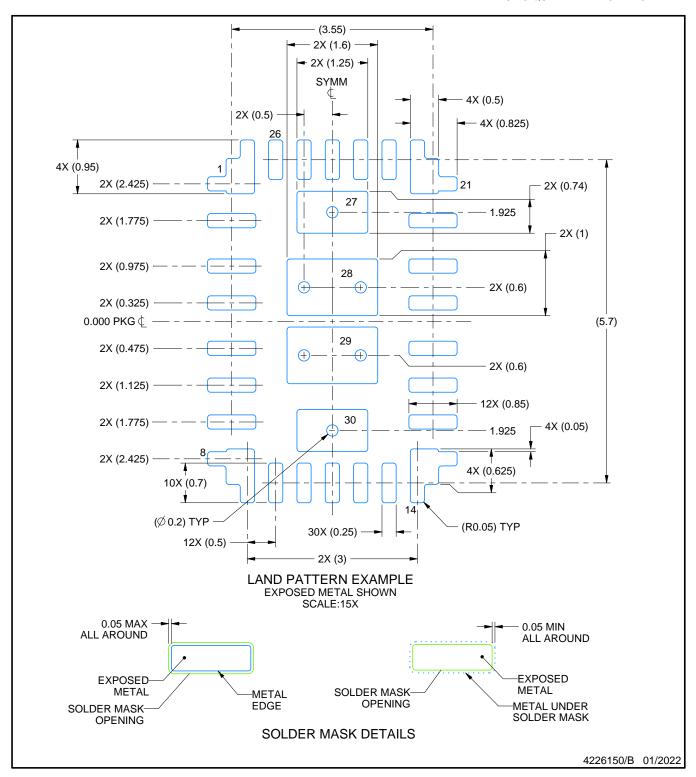

図 6-1. 30-Pin QFN, RDH Package (Top View)

### 表 6-1. Pin Functions

| PIN    | l                          | (1)                 | 3X 0-1. Fill I dilictions                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|----------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO.                        | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RT     | 1                          | I                   | Frequency setting pin. This analog pin is used to set the switching frequency between 200 kHz and 2.2 MHz by placing an external resistor from this pin to AGND. Do not leave open or connect to ground.                                                                                                                                                                                                                                                                                            |

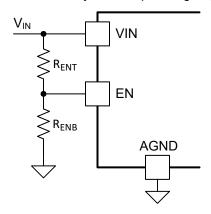

| EN     | 2                          | I                   | Precision enable input pin. High = on, low = off. Can be connected to VIN. Precision enable allows the pin to be used as an adjustable UVLO. Place an external voltage divider between this pin, AGND, and VIN to create an external UVLO.                                                                                                                                                                                                                                                          |

| VIN    | 3, 4, 18,<br>19            | Р                   | Input supply voltage. Connect the input supply to these pins. Connect input capacitors between these pins and PGND in close proximity to the device. Refer to セクション 11.2 for input capacitor placement example.                                                                                                                                                                                                                                                                                     |

| PGND   | 5, 6, 16,<br>17, 28,<br>29 | G                   | Power ground. This pin is the return current path for the power stage of the device. Connect this pad to the input supply return, the load return, and the capacitors associated with the VIN and VOUT pins. See セクション 11.2 for a recommended layout.                                                                                                                                                                                                                                               |

| VOUT   | 7-10,<br>12–15,<br>30      | Р                   | Output voltage. These pins are connected to the internal output inductor. Connect these pins to the output load and connect external output capacitors between these pins and PGND.                                                                                                                                                                                                                                                                                                                 |

| SW     | 11                         | 0                   | Switch node. Do not place any external component on this pin or connect to any signal. The amount of copper placed on these pins must be kept to a minimum to prevent issues with noise and EMI.                                                                                                                                                                                                                                                                                                    |

| NC     | 20, 21                     |                     | No connect. Do not connect these pins to ground, to another DNC pin, or to any other voltage. These pins are connected to internal circuitry. Each pin must be soldered to an isolated pad.                                                                                                                                                                                                                                                                                                         |

| VLDOIN | 22                         | Р                   | Optional LDO supply input. Connect to VOUT or to other voltage rail to improve efficiency. Connect an optional high quality 0.1-µF to 1-µF capacitor from this pin to ground for improved noise immunity. Do not connect to a voltage above 12 V or to a voltage greater than V <sub>IN</sub> . If unused, connect this pin to ground.                                                                                                                                                              |

| VCC    | 23                         | 0                   | Internal LDO output. Used as a supply to the internal control circuits. Do not connect to any external loads. Connect a high-quality 1-µF ceramic capacitor from this pin to PGND.                                                                                                                                                                                                                                                                                                                  |

| AGND   | 24, 27                     | G                   | Analog ground. Zero voltage reference for internal references and logic. All electrical parameters are measured with respect to this pin. <i>This pin must be connected to PGND at a single point</i> . See セクション11.2 for a recommended layout.                                                                                                                                                                                                                                                     |

| FB     | 25                         | I                   | Feedback input. For the adjustable output version, connect the mid-point of the feedback resistor divider to this pin. Connect the upper resistor ( $R_{FBT}$ ) of the feedback divider to $V_{OUT}$ at the desired point of regulation. Connect the lower resistor ( $R_{FBB}$ ) of the feedback divider to AGND. When connecting with a feedback resistor divider, keep this FB trace short and as small as possible to avoid noise coupling. See $20.00$ 11.2 for a feedback resistor placement. |

| PG     | 26                         | 0                   | Power-good monitor. Open-drain output that asserts low if the feedback voltage is not within the specified window thresholds. A $10$ -k $\Omega$ to $100$ -k $\Omega$ pullup resistor is required to a suitable pullup voltage. If not used, this pin can be left open or connected to PGND.                                                                                                                                                                                                        |

<sup>(1)</sup> P = Power, G = Ground, I = Input, O = Output, NC = No connect

### 7 Specifications

### 7.1 Absolute Maximum Ratings

Limits apply over  $T_J = -40^{\circ}$ C to 125°C (unless otherwise noted). (1)

|                         |                                            | MIN  | MAX  | UNIT |

|-------------------------|--------------------------------------------|------|------|------|

|                         | VIN to AGND, PGND                          | -0.3 | 40   |      |

|                         | VLDOIN to AGND, PGND                       | -0.3 | 16   |      |

|                         | EN to AGND, PGND                           | -0.3 | 40   |      |

| Input voltage           | RT to AGND, PGND                           | -0.3 | 5.5  | V    |

|                         | FB to AGND, PGND                           | -0.3 | 16   |      |

|                         | PG to AGND, PGND                           | 0    | 20   |      |

|                         | PGND to AGND                               | -1   | 2    |      |

| Output voltage          | VCC to AGND, PGND                          | -0.3 | 5.5  |      |

|                         | SW to AGND, PGND <sup>(2)</sup>            | -0.3 | 40   | V    |

|                         | VOUT to AGND, PGND                         | -0.3 | 6    |      |

| Input current           | PG                                         | _    | 10   | mA   |

| TJ                      | Junction temperature                       | -40  | 125  | °C   |

| T <sub>A</sub>          | Ambient temperature                        | -40  | 105  | °C   |

| T <sub>stg</sub>        | Storage temperature                        | -55  | 150  | °C   |

| Peak reflow case temper |                                            |      | 260  | °C   |

| Maximum number of refle | aximum number of reflows allowed           |      | 3    |      |

| Mechanical shock        |                                            |      | 1500 | G    |

| Mechanical vibration    | Mil-STD-883D, Method 2007.2, 20 to 2000 Hz |      | 20   | G    |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

#### 7.2 ESD Ratings

|                    | SD) Electrostatic discharge |                                                                                |       | UNIT  |

|--------------------|-----------------------------|--------------------------------------------------------------------------------|-------|-------|

| V                  |                             | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2500 | V     |

| V <sub>(ESD)</sub> |                             | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1500 | \ \ \ |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> A voltage of 2 V below PGND and 2 V above VIN can appear on this pin for ≤ 200 ns with a duty cycle of ≤ 0.01%.

### 7.3 Recommended Operating Conditions

Limits apply over  $T_J = -40^{\circ}$ C to 125°C (unless otherwise noted).

|                |                                          | MIN | NOM MAX | UNIT |

|----------------|------------------------------------------|-----|---------|------|

| Input voltage  | VIN (Input voltage range after start-up) | 3   | 36      | V    |

| Input voltage  | VLDOIN                                   |     | 12      | V    |

| Output voltage | VOUT <sup>(1)</sup>                      | 1   | 6       | V    |

| Output current | IOUT <sup>(2)</sup>                      | 0   | 2       | Α    |

| Frequency      | f <sub>SW</sub> set by RT                | 200 | 2200    | kHz  |

| Input current  | PG                                       |     | 2       | mA   |

| Output voltage | PG                                       | 0   | 16      | V    |

| TJ             | Operating junction temperature           | -40 | 125     | °C   |

| T <sub>A</sub> | Operating ambient temperature            | -40 | 105     | °C   |

- (1) Do not allow the output voltage be allowed to fall below 0 V.

- (2) Maximum continuous DC current can be derated when operating with high switching frequency, high ambient temperature, or both. Refer to the *Typical Characteristics* section for details.

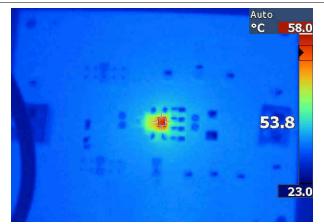

### 7.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> RDH (QFN)  30 PINS  R <sub>BJA</sub> Junction-to-ambient thermal resistance (TPSM63603 EVM)  R <sub>BJA</sub> Junction-to-ambient thermal resistance <sup>(2)</sup> W <sub>JT</sub> Junction-to-top characterization parameter <sup>(3)</sup> Junction-to-board characterization parameter <sup>(4)</sup> Junction-to-board characterization parameter <sup>(4)</sup> 21.5  *CW | LINIT                                                       |         |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------|------|

|                                                                                                                                                                                                                                                                                                                                                                                                               | I HERMAL METRIC!                                            | 30 PINS | UNII |

| $R_{\theta JA}$                                                                                                                                                                                                                                                                                                                                                                                               | Junction-to-ambient thermal resistance (TPSM63603 EVM)      | 29.1    | °C/W |

| $R_{\theta JA}$                                                                                                                                                                                                                                                                                                                                                                                               | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 33.5    | °C/W |

| ΨЈТ                                                                                                                                                                                                                                                                                                                                                                                                           | Junction-to-top characterization parameter <sup>(3)</sup>   | 4.1     | °C/W |

| ΨЈВ                                                                                                                                                                                                                                                                                                                                                                                                           | Junction-to-board characterization parameter <sup>(4)</sup> | 21.5    | °C/W |

- For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

- (2) The junction-to-ambient thermal resistance, R<sub>θJA</sub>, applies to devices soldered directly to a 64-mm × 83-mm four-layer PCB with 2-oz. copper and natural convection cooling. Additional airflow and PCB copper area reduces R<sub>θJA</sub>. For more information see the *Layout* section.

- (3) The junction-to-top board characterization parameter, ψ<sub>JT</sub>, estimates the junction temperature, T<sub>J</sub>, of a device in a real system, using a procedure described in JESD51-2A (section 6 and 7). T<sub>J</sub> = ψ<sub>JT</sub> × P<sub>dis</sub> + T<sub>T</sub>; where P<sub>dis</sub> is the power dissipated in the device and T<sub>T</sub> is the temperature of the top of the device.

- (4) The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature,  $T_{J}$ , of a device in a real system, using a procedure described in JESD51-2A (sections 6 and 7).  $T_{J} = \psi_{JB} \times P_{dis} + T_{B}$ , where  $P_{dis}$  is the power dissipated in the device and  $T_{B}$  is the temperature of the board 1 mm from the device.

Copyright © 2022 Texas Instruments Incorporated

### 7.5 Electrical Characteristics

Limits apply over  $T_J = -40^{\circ}\text{C}$  to 125°C,  $V_{IN} = 24 \text{ V}$ ,  $V_{OUT} = 3.3 \text{ V}$ ,  $V_{LDOIN} = 5 \text{ V}$ ,  $f_{SW} = 800 \text{ kHz}$  (unless otherwise noted). Minimum and maximum limits are specified through production test or by design. Typical values represent the most likely parametric norm and are provided for reference only.

|                          | PARAMETER                                                                                          | TEST CONDITIONS                                                                                              | MIN   | TYP   | MAX               | UNIT |

|--------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------|-------|-------------------|------|

| SUPPLY VOLT              | AGE                                                                                                |                                                                                                              |       |       |                   |      |

|                          |                                                                                                    | Needed to start up (over I <sub>OUT</sub> range)                                                             | 3.95  |       | 36                | V    |

| V <sub>IN</sub>          | Input operating voltage range                                                                      | Once operating (over I <sub>OUT</sub> range)                                                                 | 3     |       | 36                | V    |

| V <sub>IN HYS</sub>      | Hysteresis <sup>(1)</sup>                                                                          |                                                                                                              |       | 1.0   |                   | V    |

| I <sub>Q VIN</sub>       | Input operating quiescent current (non-switching)                                                  | T <sub>A</sub> = 25°C, V <sub>EN</sub> = 3.3 V, V <sub>FB</sub> = 1.5 V                                      |       | 4     |                   | μA   |

| I <sub>SDN VIN</sub>     | VIN shutdown quiescent current                                                                     | V <sub>EN</sub> = 0 V, T <sub>A</sub> = 25°C                                                                 |       | 3     |                   | μA   |

| ENABLE                   |                                                                                                    |                                                                                                              |       |       |                   |      |

| V <sub>EN RISE</sub>     | EN voltage rising threshold                                                                        |                                                                                                              | 1.161 | 1.263 | 1.365             | V    |

| V <sub>EN_FALL</sub>     | EN voltage falling threshold                                                                       |                                                                                                              |       | 0.91  |                   | V    |

| V <sub>EN HYS</sub>      | EN voltage hysteresis                                                                              |                                                                                                              | 0.275 | 0.353 | 0.404             | V    |

| V <sub>EN WAKE</sub>     | EN wake-up threshold                                                                               |                                                                                                              | 0.4   |       |                   | V    |

| I <sub>EN</sub>          | Input current into EN (non-switching)                                                              | V <sub>EN</sub> = 3.3 V, V <sub>FB</sub> = 1.5 V                                                             |       | 1.65  |                   | μA   |

| t <sub>EN</sub>          | EN HIGH to start of switching delay <sup>(1)</sup>                                                 |                                                                                                              |       | 0.7   |                   | ms   |

| INTERNAL LD              | o vcc                                                                                              |                                                                                                              |       |       |                   |      |

|                          |                                                                                                    | $3.4 \text{ V} \le \text{V}_{\text{LDOIN}} \le 12.5 \text{ V}$                                               |       | 3.3   |                   | V    |

| V <sub>CC</sub>          | Internal LDO VCC output voltage                                                                    | V <sub>LDOIN</sub> = 3.1 V, non-switching                                                                    |       | 3.1   | 36<br>36<br>1.365 | V    |

|                          |                                                                                                    | V <sub>LDOIN</sub> < 3.1 V <sup>(1)</sup>                                                                    |       | 3.6   |                   | V    |

| V <sub>CC_UVLO</sub>     | VCC UVLO rising threshold                                                                          | V <sub>IN</sub> < 3.6 V <sup>(2)</sup>                                                                       |       | 3.6   |                   | V    |

| V <sub>CC UVLO HYS</sub> | VCC UVLO hysteresis <sup>(2)</sup>                                                                 | Hysteresis below V <sub>CC UVLO</sub>                                                                        |       | 1.1   |                   | V    |

| I <sub>VLDOIN</sub>      | Input current into VLDOIN pin (non-switching, maximum at T <sub>A</sub> = 125°C) <sup>(3)</sup>    | V <sub>EN</sub> = 3.3 V, V <sub>FB</sub> = 1.5 V                                                             |       | 25    | 31.2              | μA   |

| FEEDBACK                 |                                                                                                    |                                                                                                              |       |       |                   |      |

| V <sub>OUT</sub>         | Adjustable output voltage range                                                                    | Over the I <sub>OUT</sub> range                                                                              | 1     |       | 6                 | V    |

| V <sub>FB</sub>          | Feedback voltage                                                                                   | T <sub>A</sub> = 25°C, I <sub>OUT</sub> = 0 A                                                                |       | 1.0   |                   | V    |

| V <sub>FB_ACC</sub>      | Feedback voltage accuracy                                                                          | Over the V <sub>IN</sub> range, V <sub>OUT</sub> = 1 V, I <sub>OUT</sub> = 0<br>A, f <sub>SW</sub> = 200 kHz | -1%   |       | +1%               |      |

| V <sub>FB</sub>          | Load regulation                                                                                    | T <sub>A</sub> = 25°C, 0 A ≤ I <sub>OUT</sub> ≤ 3 A                                                          |       | 0.1%  |                   |      |

| V <sub>FB</sub>          | Line regulation                                                                                    | $T_A = 25$ °C, $I_{OUT} = 0$ A, $4.0 \text{ V} \le V_{IN} \le 36 \text{ V}$                                  |       | 0.1%  |                   |      |

| I <sub>FB</sub>          | Input current into the FB pin                                                                      | V <sub>FB</sub> = 1.0 V                                                                                      |       | 10    |                   | nA   |

| CURRENT                  | 1                                                                                                  |                                                                                                              |       |       |                   |      |

| I <sub>OUT</sub>         | Output current                                                                                     | T <sub>A</sub> = 25°C                                                                                        | 0     |       | 2.0               | Α    |

| I <sub>OCL</sub>         | Output overcurrent (DC) limit threshold                                                            |                                                                                                              |       | 3.8   |                   | Α    |

| I <sub>L_HS</sub>        | High-side switch current limit                                                                     | Duty cycle approaches 0%                                                                                     | 4.48  | 4.87  | 5.32              | Α    |

| <br>I <sub>L LS</sub>    | Low-side switch current limit                                                                      |                                                                                                              | 2.07  | 2.4   | 2.80              | Α    |

| I <sub>L NEG</sub>       | Negative current limit                                                                             |                                                                                                              |       | -3    |                   | Α    |

| V <sub>HICCUP</sub>      | Ratio of FB voltage to in-regulation FB voltage to enter hiccup                                    | Not during soft start                                                                                        |       | 40%   |                   |      |

| t <sub>W</sub>           | Short circuit wait time ("hiccup" time before soft start)                                          |                                                                                                              |       | 80    |                   | ms   |

| SOFT START               | 1                                                                                                  |                                                                                                              |       |       |                   |      |

| t <sub>SS</sub>          | Time from first SW pulse to V <sub>REF</sub> at 90%                                                | V <sub>IN</sub> ≥ 4.2 V                                                                                      | 3.5   | 5     | 7                 | ms   |

| t <sub>SS2</sub>         | Time from first SW pulse to release of FPWM lockout if the output not in regulation <sup>(1)</sup> | V <sub>IN</sub> ≥ 4.2 V                                                                                      | 9.5   | 13    | 17                | ms   |

Product Folder Links: TLVM13620

Submit Document Feedback

### 7.5 Electrical Characteristics (continued)

Limits apply over  $T_J = -40^{\circ}\text{C}$  to  $125^{\circ}\text{C}$ ,  $V_{\text{IN}} = 24 \text{ V}$ ,  $V_{\text{OUT}} = 3.3 \text{ V}$ ,  $V_{\text{LDOIN}} = 5 \text{ V}$ ,  $f_{\text{SW}} = 800 \text{ kHz}$  (unless otherwise noted). Minimum and maximum limits are specified through production test or by design. Typical values represent the most likely parametric norm and are provided for reference only.

|                          | PARAMETER                                                                   | TEST CONDITIONS                                        | MIN  | TYP  | MAX      | UNIT |

|--------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------|------|------|----------|------|

| POWER GOO                | D                                                                           |                                                        | •    |      | <u> </u> |      |

| PG <sub>OV</sub>         | PG upper threshold — rising                                                 | % of V <sub>OUT</sub> setting                          | 105% | 107% | 110%     |      |

| PG <sub>UV</sub>         | PG lower threshold — falling                                                | % of V <sub>OUT</sub> setting                          | 92%  | 94%  | 96.5%    |      |

| PG <sub>HYS</sub>        | PG upper threshold hysteresis (rising and falling)                          | % of V <sub>OUT</sub> setting                          |      | 1.3% |          |      |

| V <sub>IN_PG_VALID</sub> | Input voltage for valid PG output                                           | 46-μA pullup, V <sub>EN</sub> = 0 V                    | 1.0  |      |          | V    |

| V <sub>PG_LOW</sub>      | Low level PG function output voltage                                        | 2-mA pullup to the PG pin, V <sub>EN</sub> = 3.3 V     |      |      | 0.4      | V    |

| I <sub>PG</sub>          | Input current into the PG pin when open-drain output is high                | V <sub>PG</sub> = 3.3 V                                |      | 10   |          | nA   |

| lov                      | Pulldown current at the SW node under overvoltage condition                 |                                                        |      | 0.5  |          | mA   |

| t <sub>PG_FLT_RISE</sub> | Delay time to PG high signal                                                |                                                        | 1.5  | 2.0  | 2.5      | ms   |

| t <sub>PG_FLT_FALL</sub> | Glitch filter time constant for PG function                                 |                                                        |      | 120  |          | μs   |

| SWITCHING F              | REQUENCY                                                                    |                                                        |      |      | •        |      |

| f <sub>SW_RANGE</sub>    | Switching frequency range by R <sub>T</sub> or SYNC                         |                                                        | 200  |      | 2200     | kHz  |

| f <sub>SW_RT1</sub>      | Default switching frequency by R <sub>T</sub>                               | $R_{RT} = 66.5 \text{ k}\Omega$                        | 180  | 200  | 220      | kHz  |

| f <sub>SW_RT2</sub>      | Default switching frequency by R <sub>T</sub>                               | $V_{IN} = 12 \text{ V}, R_{RT} = 5.76 \text{ k}\Omega$ | 1980 | 2200 | 2420     | kHz  |

| SYNCHRONIZ               | ZATION                                                                      |                                                        |      |      |          |      |

| t <sub>B</sub>           | Blanking of EN after rising or falling edges <sup>(1)</sup>                 |                                                        | 4    |      | 28       | μs   |

| t <sub>SYNC_EDGE</sub>   | Enable sync signal hold time after edge for edge recognition <sup>(1)</sup> |                                                        | 100  |      |          | ns   |

| POWER STAC               | GE                                                                          |                                                        |      |      |          |      |

| V <sub>BOOT_UVLO</sub>   | Voltage on CBOOT pin compared to SW which will turn off high-side switch    |                                                        |      | 2.1  |          | V    |

| t <sub>ON_MIN</sub>      | Minimum ON pulse width <sup>(1)</sup>                                       | V <sub>OUT</sub> = 1 V, I <sub>OUT</sub> = 1 A         |      | 55   | 70       | ns   |

| t <sub>ON_MAX</sub>      | Maximum ON pulse width <sup>(1)</sup>                                       |                                                        |      | 9    |          | μs   |

| t <sub>OFF_MIN</sub>     | Minimum OFF pulse width                                                     | V <sub>IN</sub> = 4 V, I <sub>OUT</sub> = 1 A          |      | 65   | 85       | ns   |

| THERMAL SH               | IUTDOWN                                                                     |                                                        | •    |      | <u>'</u> |      |

| T <sub>SDN</sub>         | Thermal shutdown threshold <sup>(1)</sup>                                   | Temperature rising                                     | 158  | 168  | 180      | °C   |

| T <sub>HYST</sub>        | Thermal shutdown hysteresis <sup>(1)</sup>                                  |                                                        |      | 10   |          | °C   |

<sup>(1)</sup> Parameter specified by design, statistical analysis and production testing of correlated parameters. Not production tested.

<sup>(2)</sup> Production tested with  $V_{IN} = 3 \text{ V}$ .

<sup>(3)</sup> This specification is the current used by the device while not switching, open loop, with FB pulled to +5% of nominal. This specification does not represent the total input current to the system while regulating. For additional information, reference the Systems Characteristics and the Input Supply Current sections.

### 7.6 System Characteristics

The following specifications apply only to the typical applications circuit, with nominal component values. Specifications in the typical (TYP) column apply to  $T_J = 25^{\circ}$ C only. These specifications are not ensured by production testing.

|                  | PARAMETER                               | TEST CONDITIONS                                                                                                                                 | MIN | TYP   | MAX | UNIT |

|------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|------|

| SUPPLY           | 1                                       |                                                                                                                                                 |     |       |     |      |

| I <sub>IN</sub>  | Input supply current when in regulation | $ V_{IN}  = 24 \text{ V}, V_{OUT} = 3.3 \text{ V}, V_{EN} = V_{IN}, V_{VLDOIN} = V_{OUT}, f_{SW} = 800 \text{ kHz}, $ $ I_{OUT}  = 0 \text{ A}$ |     | 10    |     | mA   |

| OUTPU            | T VOLTAGE                               |                                                                                                                                                 |     |       |     |      |

| $V_{FB}$         | Load regulation                         | V <sub>OUT</sub> = 3.3 V, V <sub>IN</sub> = 24 V, I <sub>OUT</sub> = 0.1 A to full load                                                         |     | 1     |     | mV   |

| $V_{FB}$         | Line regulation                         | V <sub>OUT</sub> = 3.3 V, V <sub>IN</sub> = 4 V to 36 V, I <sub>OUT</sub> = 3 A                                                                 |     | 6     |     | mV   |

| V <sub>OUT</sub> | Load transient                          | $V_{OUT}$ = 3.3 V, $V_{IN}$ = 24 V, $I_{OUT}$ = 1 A to 2.5 A at 2 A/ $\mu$ s, $C_{OUT(derated)}$ = 49 $\mu$ F                                   |     | 50    |     | mV   |

| EFFICIE          | NCY                                     |                                                                                                                                                 |     |       | '   |      |

|                  |                                         | V <sub>OUT</sub> = 3.3 V, V <sub>IN</sub> = 12 V, I <sub>OUT</sub> = 2.5 A, V <sub>LDOIN</sub> = V <sub>OUT</sub> , f <sub>SW</sub> = 800 kHz   |     | 89.5% |     |      |

|                  |                                         | V <sub>OUT</sub> = 3.3 V, V <sub>IN</sub> = 24 V, I <sub>OUT</sub> = 2.5 A, V <sub>LDOIN</sub> = V <sub>OUT</sub> , f <sub>SW</sub> = 800 kHz   |     | 87.5% |     |      |

| η                | Efficiency                              | V <sub>OUT</sub> = 5 V, V <sub>IN</sub> = 24 V, I <sub>OUT</sub> = 2.5 A, V <sub>LDOIN</sub> = V <sub>OUT</sub> , f <sub>SW</sub> = 1 MHz       |     | 91%   |     |      |

|                  |                                         | V <sub>OUT</sub> = 5 V, V <sub>IN</sub> = 36 V, I <sub>OUT</sub> = 2.5 A, V <sub>LDOIN</sub> = V <sub>OUT</sub> , f <sub>SW</sub> = 1 MHz       |     | 88.1% |     |      |

|                  |                                         | V <sub>OUT</sub> = 12 V, V <sub>IN</sub> = 24 V, I <sub>OUT</sub> = 1.5 A, V <sub>LDOIN</sub> = V <sub>OUT</sub> , f <sub>SW</sub> = 2 MHz      |     | 94.1% |     |      |

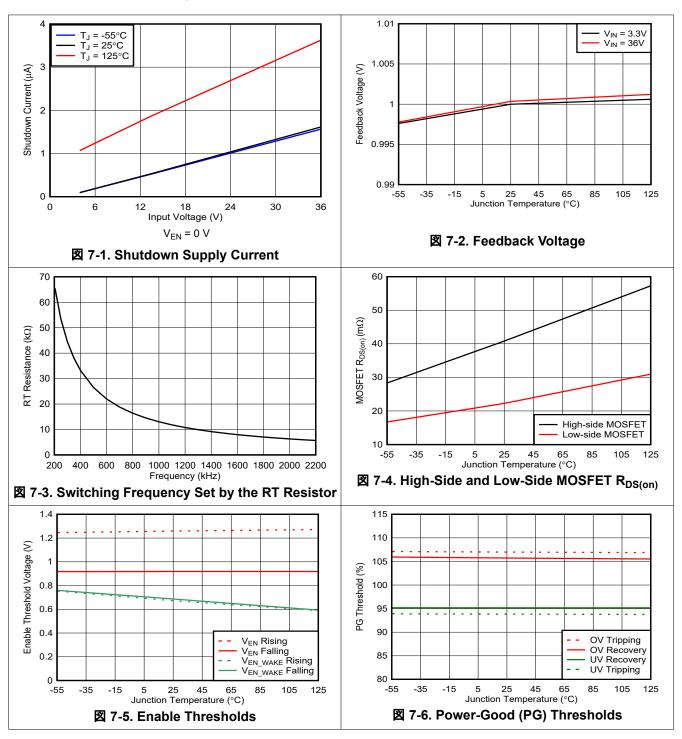

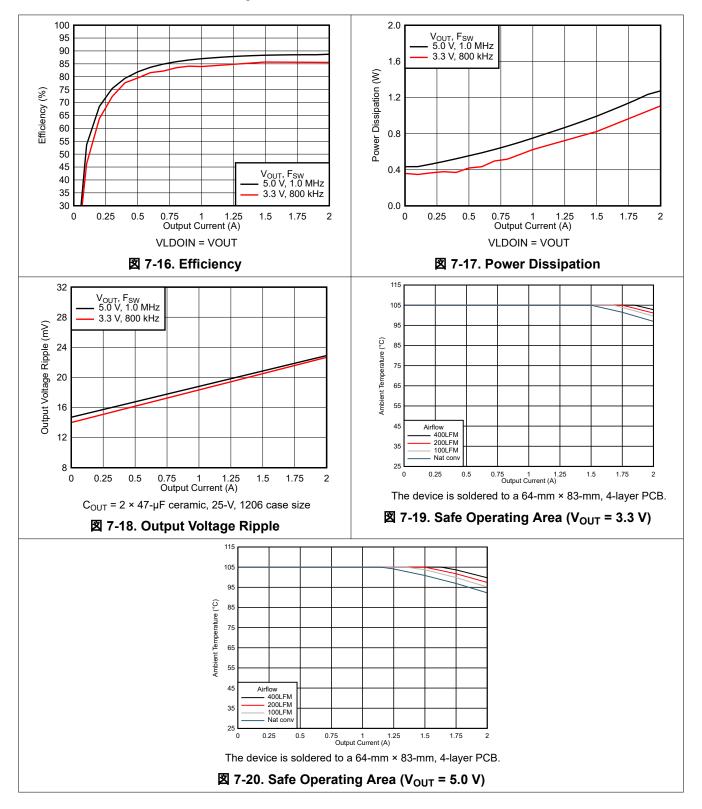

### 7.7 Typical Characteristics

V<sub>IN</sub> = 24 V, unless otherwise specified

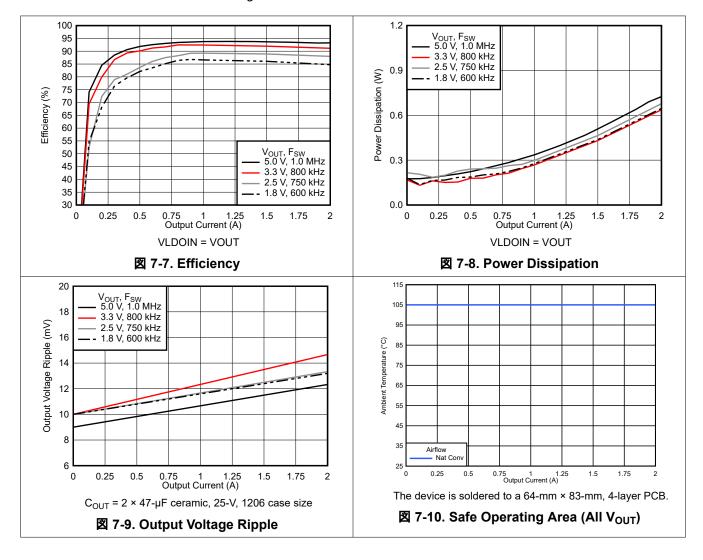

# 7.8 Typical Characteristics — 2-A Device ( $V_{IN} = 12 \text{ V}$ )

Refer to セクション 9.2 for circuit designs.

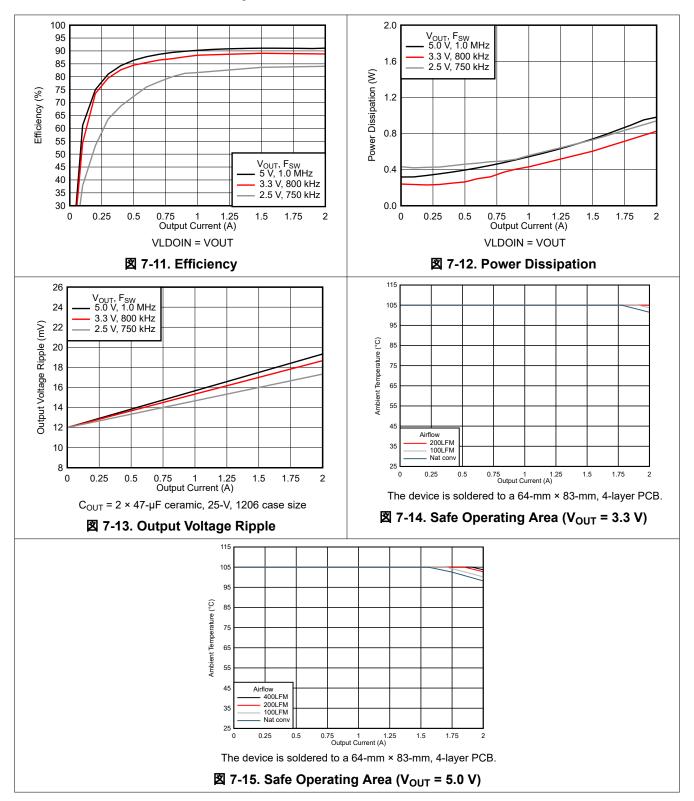

# 7.9 Typical Characteristics — 2-A Device ( $V_{IN}$ = 24 V)

Refer to セクション 9.2 for circuit designs.

# 7.10 Typical Characteristics — 2-A Device ( $V_{IN}$ = 36 V)

Refer to セクション 9.2 for circuit designs.

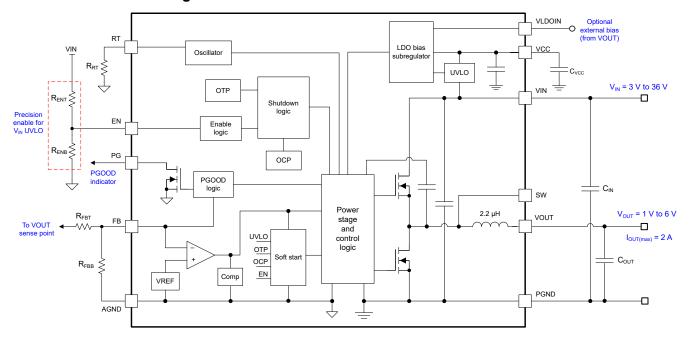

## 8 Detailed Description

#### 8.1 Overview

The TLVM13620 is an easy-to-use, synchronous buck, DC-DC power module that operates from a 3-V to 36-V supply voltage. The device is intended for step-down conversions from 5-V, 12-V, and 24-V supply rails. With an integrated power controller, inductor, and MOSFETs, the TLVM13620 delivers up to 3-A DC load current with high efficiency and ultra-low input quiescent current in a very small solution size. Although designed for simple implementation, this device offers flexibility to optimize its usage according to the target application. Control-loop compensation is not required, reducing design time and external component count.

With a programmable switching frequency from 200 kHz to 2.2 MHz using its RT pin, the TLVM13620 incorporates specific features to improve EMI performance in noise-sensitive applications:

- · An optimized package and pinout design enables a shielded switch-node layout that mitigates radiated EMI.

- Parallel input and output paths with symmetrical capacitor layouts minimize parasitic inductance, switch-voltage ringing, and radiated field coupling.

- Clock synchronization and FPWM mode enable constant switching frequency across the load current range.

- Integrated power MOSFETs with enhanced gate drive control enable low-noise PWM switching.

- Adjustable switch-node slew rate allows optimization of EMI at higher frequency harmonics.

The TLVM13620 module also includes inherent protection features for robust system requirements:

- An open-drain PGOOD indicator for power-rail sequencing and fault reporting

- · Precision enable input with hysteresis, providing:

- Programmable line undervoltage lockout (UVLO)

- Remote ON and OFF capability

- · Internally fixed output-voltage soft start with monotonic start-up into prebiased loads

- · Hiccup-mode overcurrent protection with cycle-by-cycle peak and valley current limits

- · Thermal shutdown with automatic recovery

These features enable a flexible and easy-to-use platform for a wide range of applications. The pin arrangement is designed for a simple layout, requiring few external components. See セクション 11 for a layout example.

### 8.2 Functional Block Diagram

### 8.3 Feature Description

#### 8.3.1 Input Voltage Range

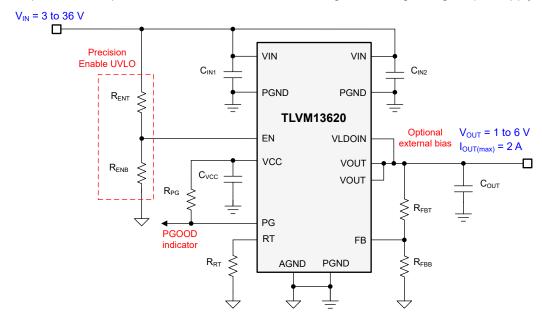

With a steady-state input voltage range from 3 V to 36 V, the TLVM13620 module is intended for step-down conversions from typical 12-V, 24-V, and 28-V input supply rails. The schematic circuit in 🗵 8-1 shows all the necessary components to implement a TLVM13620-based buck regulator using a single input supply.

図 8-1. TLVM13620 Schematic Diagram with Input Voltage Operating Range of 3 V to 36 V

Take extra care to make sure that the voltage at the VIN pins does not exceed the absolute maximum voltage rating of 40 V during line or load transient events. Voltage ringing at the VIN pins that exceeds the absolute maximum ratings can damage the IC.

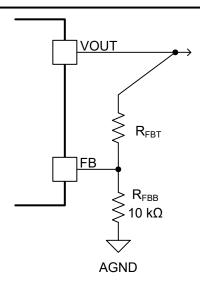

### 8.3.2 Adjustable Output Voltage (FB)

The TLVM13620 has an adjustable output voltage range of 1 V to 6 V. Setting the output voltage requires two resistors,  $R_{FBT}$  and  $R_{FBB}$  (see  $\boxtimes$  8-2). Connect  $R_{FBT}$  between VOUT, at the regulation point, and the FB pin. Connect  $R_{FBB}$  between the FB pin and AGND (pin 10). The recommended value of  $R_{FBB}$  is 10 kΩ. The value for  $R_{FBT}$  can be calculated using  $\rightrightarrows$  1.  $\gtrapprox$  8-1 lists the standard resistor values for several output voltages and the recommended switching frequency. The minimum required output capacitance for each output voltage is also included in  $\gtrapprox$  8-1. The capacitance values listed represent the effective capacitance, taking into account the effects of DC bias and temperature variation.

$$R_{FBT} \left[ k\Omega \right] = R_{FBB} \left[ k\Omega \right] \cdot \left( \frac{V_{OUT} \left[ V \right]}{1V} - 1 \right)$$

(1)

図 8-2. FB Resistor Divider

表 8-1. Standard  $\mathsf{R}_\mathsf{FBT}$  Values, Recommended  $\mathsf{f}_\mathsf{SW}$  and Minimum  $\mathsf{C}_\mathsf{OUT}$

|                      |                           |                                   | 101                                       |                      | 011                                  | - 001                             |                                           |

|----------------------|---------------------------|-----------------------------------|-------------------------------------------|----------------------|--------------------------------------|-----------------------------------|-------------------------------------------|

| V <sub>OUT</sub> (V) | $R_{FBT} (k\Omega)^{(1)}$ | Recommended f <sub>SW</sub> (kHz) | C <sub>OUT(MIN)</sub> (μF)<br>(Effective) | V <sub>OUT</sub> (V) | R <sub>FBT</sub> (kΩ) <sup>(1)</sup> | Recommended f <sub>SW</sub> (kHz) | C <sub>OUT(MIN)</sub> (μF)<br>(Effective) |

| 1.0                  | Short                     | 400                               | 300                                       | 2.5                  | 15                                   | 750                               | 65                                        |

| 1.2                  | 2                         | 500                               | 200                                       | 3.0                  | 20                                   | 750                               | 50                                        |

| 1.5                  | 4.99                      | 500                               | 160                                       | 3.3                  | 23.2                                 | 800                               | 40                                        |

| 1.8                  | 8.06                      | 600                               | 120                                       | 5.0                  | 40.2                                 | 1000                              | 25                                        |

| 2.0                  | 10                        | 600                               | 100                                       | 6.0                  | 49.9                                 | 1000                              | 22                                        |

(1)

$$R_{FBB} = 10 \text{ k}\Omega$$

#### 8.3.3 Input Capacitors

Input capacitors are required to limit the input ripple voltage to the module due to switching-frequency AC currents. TI recommends using ceramic capacitors to provide low impedance and high RMS current rating over a wide temperature range.  $\pm$  2 gives the input capacitor RMS current. The highest input capacitor RMS current occurs at D = 0.5, at which point, the RMS current rating of the capacitors must be greater than half the output current.

$$I_{CIN,rms} = \sqrt{D \cdot \left(I_{OUT}^2 \cdot (1-D) + \frac{\Delta I_L^2}{12}\right)}$$

(2)

#### where

D = V<sub>OUT</sub> / V<sub>IN</sub> is the module duty cycle.

Ideally, the DC and AC components of the input current to the buck stage are provided by the input voltage source and the input capacitors, respectively. Neglecting inductor ripple current, the input capacitors source current of amplitude  $(I_{OUT}-I_{IN})$  during the D interval and sink  $I_{IN}$  during the 1 – D interval. Thus, the input capacitors conduct a square-wave current of peak-to-peak amplitude equal to the output current. The resulting capacitive component of the AC ripple voltage is a triangular waveform. Together with the ESR-related ripple component,  $\vec{\pi}$  3 gives the peak-to-peak ripple voltage amplitude.

$$\Delta V_{IN} = \frac{I_{OUT} \cdot D \cdot (1 - D)}{F_{SW} \cdot C_{IN}} + I_{OUT} \cdot R_{ESR}$$

(3)

式 4 gives the input capacitance required for a particular load current.

$$C_{IN} \ge \frac{D \cdot (1 - D) \cdot I_{OUT}}{F_{SW} \cdot (\Delta V_{IN} - R_{ESR} \cdot I_{OUT})}$$

(4)

where

ΔV<sub>IN</sub> is the input voltage ripple specification.

The TLVM13620 requires a minimum of 2 × 4.7-µF ceramic type input capacitance. Only use high-quality ceramic type capacitors with sufficient voltage and temperature rating. The ceramic input capacitors provide a low impedance source to the converter in addition to supplying the ripple current and isolating switching noise from other circuits. Additional capacitance can be required for applications with transient load requirements. The voltage rating of the input capacitors must be greater than the maximum input voltage. To compensate for the derating of ceramic capacitors, TI recommends a voltage rating of twice the maximum input voltage or placing multiple capacitors in parallel. 表 8-2 includes a preferred list of capacitors by vendor.

| 表 8-2. Recommended input Capacitors |            |                        |           |                    |                                 |  |

|-------------------------------------|------------|------------------------|-----------|--------------------|---------------------------------|--|

| Vendor <sup>(1)</sup>               | Dielectric | Part Number            | Case Size | Capacitor C        | haracteristics                  |  |

| Vendor                              | Dielectric | Part Nulliber Case Siz | Case Size | Voltage Rating (V) | Capacitance (µF) <sup>(2)</sup> |  |

| TDK                                 | X7R        | C3216X7R1H475K160AC    | 1206      | 50                 | 4.7                             |  |

| Murata                              | X7R        | GRM31CR71H475KA12L     | 1206      | 50                 | 4.7                             |  |

| TDK                                 | X7R        | CGA6P3X7R1H475K250AB   | 1210      | 50                 | 4.7                             |  |

| Murata                              | X7S        | GCM31CC71H475KA03L     | 1206      | 50                 | 4.7                             |  |

表 8-2. Recommended Input Capacitors

#### 8.3.4 Output Capacitors

表 8-1 lists the TLVM13620 minimum amount of required output capacitance. The effects of DC bias and temperature variation must be considered when using ceramic capacitance. For ceramic capacitors, the package size, voltage rating, and dielectric material contribute to differences between the standard rated value and the actual effective value of the capacitance.

When adding additional capacitance above  $C_{OUT(MIN)}$ , the capacitance can be ceramic type, low-ESR polymer type, or a combination of the two. See  $\frac{1}{2}$  8-3 for a preferred list of output capacitors by vendor.

表 8-3. Recommended Output Capacitors

| Vendor <sup>(1)</sup> | Temperature | Part Number          | Case Size | Capacitor Characteristics |                                 |  |

|-----------------------|-------------|----------------------|-----------|---------------------------|---------------------------------|--|

| vendor                | Coefficient | Fait Number          | Case Size | Voltage (V)               | Capacitance (μF) <sup>(2)</sup> |  |

| TDK                   | X7R         | CGA5L1X7R1C106K160AC | 1206      | 16                        | 10                              |  |

| Murata                | X7R         | GCM31CR71C106KA64L   | 1206      | 16                        | 10                              |  |

| TDK                   | X7R         | C3216X7R1E106K160AB  | 1206      | 25                        | 10                              |  |

| Murata                | X7S         | GCJ31CC71E106KA15L   | 1206      | 25                        | 10                              |  |

| Murata                | X6S         | GRM31CC81E226K       | 1206      | 25                        | 22                              |  |

| Murata                | X7R         | GRM32ER71E226M       | 1210      | 25                        | 22                              |  |

<sup>(1)</sup> Consult capacitor suppliers regarding availability, material composition, RoHS and lead-free status, and manufacturing process requirements for any capacitors identified in this table. See the *Third-Party Products Disclaimer*.

(2) Nameplate capacitance values (the effective values are lower based on the applied DC voltage and temperature.)

<sup>(1)</sup> Consult capacitor suppliers regarding availability, material composition, RoHS and lead-free status, and manufacturing process requirements for any capacitors identified in this table. See the *Third-Party Products Disclaimer*.

<sup>(2)</sup> Nameplate capacitance values (the effective values are lower based on the applied DC voltage and temperature.)

### 8.3.5 Switching Frequency (RT)

The switching frequency range of the TLVM13620 is 200 kHz to 2.2 MHz. The switching frequency can easily be set by connecting a resistor ( $R_{RT}$ ) between the RT pin and AGND. Use  $\pm$  5 to calculate the  $R_{RT}$  value for a desired frequency or simply select from  $\pm$  8-4. Note that a resistor value outside the recommended range can cause the device to shut down. This value prevents unintended operation if the RT pin is shorted to ground or left open. Do not apply a pulsed signal to this pin to force synchronization.

The switching frequency must be selected based on the output voltage setting of the device. See  $\frac{1}{5}$  8-4 for R<sub>RT</sub> resistor values and the allowable output voltage range for a given switching frequency for common input voltages.

$$R_{RT}\left[k\Omega\right] = \frac{13.46}{F_{SW}\left[MHz\right]} - 0.44$$

(5)

表 8-4. Switching Frequency Versus Output Voltage (I<sub>OUT</sub> = A)

|                       | V <sub>IN</sub> = 5 V V <sub>IN</sub> = 12 V V <sub>IN</sub> = 24 V V <sub>IN</sub> = 36 V |                     |          |                     |          |                     |          | 26 V                |          |

|-----------------------|--------------------------------------------------------------------------------------------|---------------------|----------|---------------------|----------|---------------------|----------|---------------------|----------|

|                       |                                                                                            |                     |          |                     |          |                     |          | ***                 |          |

| F <sub>SW</sub> (kHz) | R <sub>RT</sub> (kΩ)                                                                       | V <sub>OUT</sub> Ra | ange (V) |

|                       |                                                                                            | Min                 | Max      | Min                 | Max      | Min                 | Max      | Min                 | Max      |

| 200                   | 66.5                                                                                       | 1.0                 | 2.0      | 1.0                 | 2.0      | 1.0                 | 1.5      | 1.0                 | 1.5      |

| 400                   | 33.2                                                                                       | 1.0                 | 3.0      | 1.0                 | 4.0      | 1.0                 | 3.3      | 1.2                 | 3.0      |

| 600                   | 22.1                                                                                       | 1.0                 | 3.5      | 1.0                 | 6.0      | 1.5                 | 6.0      | 1.8                 | 5.0      |

| 800                   | 16.5                                                                                       | 1.0                 | 3.5      | 1.0                 | 6.0      | 1.5                 | 6.0      | 2.5                 | 6.0      |

| 1000                  | 13.0                                                                                       | 1.0                 | 3.0      | 1.0                 | 6.0      | 2.0                 | 6.0      | 3.0                 | 6.0      |

| 1200                  | 10.7                                                                                       | 1.0                 | 3.0      | 1.5                 | 6.0      | 2.5                 | 6.0      | 3.5                 | 6.0      |

| 1400                  | 9.09                                                                                       | 1.0                 | 3.0      | 1.5                 | 6.0      | 3.0                 | 6.0      | 4.0                 | 6.0      |

| 1600                  | 8.06                                                                                       | 1.0                 | 3.0      | 1.5                 | 6.0      | 3.0                 | 6.0      | 4.5                 | 6.0      |

| 1800                  | 6.98                                                                                       | 1.0                 | 3.0      | 2.0                 | 6.0      | 3.5                 | 6.0      | 5.0                 | 6.0      |

| 2000                  | 6.34                                                                                       | 1.2                 | 2.5      | 2.0                 | 6.0      | 4.0                 | 6.0      | 5.5                 | 6.0      |

| 2200                  | 5.626                                                                                      | 1.2                 | 2.5      | 2.0                 | 6.0      | 4.5                 | 6.0      | _                   | _        |

### 8.3.6 Output ON and OFF Enable (EN) and VIN UVLO

The EN pin provides precision ON and OFF control for the TLVM13620. Once the EN pin voltage exceeds the threshold voltage and  $V_{\text{IN}}$  is above the minimum turn-on threshold, the device starts operation. The simplest way to enable the TLVM13620 is to connect EN directly to VIN, allowing the TLVM13620 to start up when  $V_{\text{IN}}$  is within its valid operating range. However, many applications benefit from the employment of an enable divider network as shown in  $\boxtimes$  8-3, which establishes a precision input undervoltage lockout (UVLO). This network can be used for sequencing, to prevent re-triggering the device when used with long input cables, or to reduce the occurrence of deep discharge of a battery power source. An external logic signal can also be used to drive the enable input to toggle the output on and off and for system sequencing or protection.

図 8-3. V<sub>IN</sub> UVLO Using the EN Pin

$R_{ENB}$  can be calculated using  $\pm$  6.

$$R_{ENB} [k\Omega] = R_{ENT} [k\Omega] \cdot \left( \frac{V_{EN\_RISE} [V]}{V_{IN(on)} [V] - V_{EN\_RISE} [V]} \right)$$

(6)

#### where

- $R_{ENT}$  is 100  $k\Omega$  (typical).

- V<sub>EN</sub> is 1.263 V (typical).

- V<sub>IN(ON)</sub> is the desired start-up input voltage.

#### 8.3.7 Power-Good Monitor (PG)

The TLVM13620 provides a PGOOD signal to indicate when the output voltage is within regulation. Use the PGOOD signal for output monitoring, fault protection, or start-up sequencing of downstream converters. The PGOOD pin voltage goes low when the feedback voltage is outside of the PGOOD thresholds, which occurs during the following:

- · While the device is disabled

- · In current limit

- In thermal shutdown

- During normal start-up, when the output voltage has not reach its regulation value

A glitch filter prevents false flag operation for short excursions (< 120 µs typical) of the output voltage, such as during line and load transients.

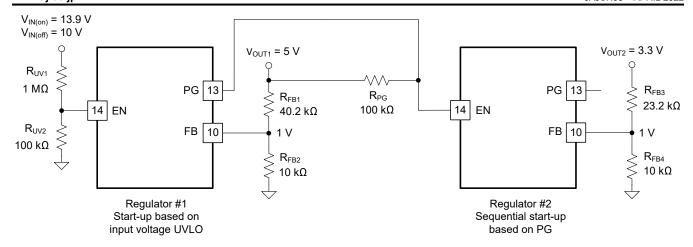

PGOOD is an open-drain output that requires a pullup resistor to a DC supply not greater than 20 V. The typical range of pullup resistance is 10 k $\Omega$  to 100 k $\Omega$ . When EN is pulled low, the flag output is also forced low. With EN low, power good remains valid as long as the input voltage is above 1 V (typical). Use the PG signal for start-up sequencing of downstream regulators, as shown in  $\boxtimes$  8-4, or for fault protection and output monitoring.

図 8-4. TLVM13620 Sequencing Implementation Using PG and EN

#### 8.3.8 Internal LDO, VCC Output, and VLDOIN Input

The TLVM13620 has an internal LDO to power internal circuitry. The VCC pin is the output of the internal LDO. This pin must not be used to power external circuitry. Connect a high-quality, 1-μF capacitor from this pin to AGND, close to the device pins. Do not load the VCC pin or short it to ground.

The VLDOIN pin is an optional input to the internal LDO. Connect an optional high quality 0.1-μF to 1-μF capacitor from this pin to ground for improved noise immunity.

The LDO generates the VCC voltage from one of the two inputs:  $V_{IN}$  or the VLDOIN input. When VLDOIN is tied to ground or below 3.1 V, the LDO is powered from  $V_{IN}$ . When VLDOIN is tied to a voltage higher than 3.1 V, the LDO input is powered from VLDOIN. VLDOIN voltage must be lower than both  $V_{IN}$  and 12.5 V.

The VLDOIN input is designed to reduce the LDO power loss. The LDO power loss is:

$$P_{LDO-LOSS} = I_{LDO} \times (V_{IN} LDO - V_{VCC})$$

(7)

The higher the difference between the input and output voltages of the LDO, the more loss occurs to supply the same LDO output current. The VLDOIN input provides an option to supply the LDO with a lower voltage than  $V_{IN}$ , to reduce the difference of the input and output voltages of the LDO, and reduce power loss. For example, if the LDO current were 10 mA at a certain frequency with  $V_{IN}$  = 24 V and  $V_{OUT}$  = 5 V. The LDO loss with VLDOIN tied to ground is:

$$10 \text{ mA} \times (24 \text{ V} - 3.3 \text{ V}) = 207 \text{ mW}$$

(8)

The loss with VLDOIN tied to V<sub>OUT</sub> (5 V) is:

$$10 \text{ mA} \times (5 \text{ V} - 3.3 \text{ V}) = 17 \text{ mW}$$

(9)

The efficiency improvement is more significant at light and mid loads because the LDO loss is a higher percentage of the total loss. The improvement is more significant with higher switching frequency because the LDO current is higher at higher switching frequency. The improvement is more significant when  $V_{IN} \gg V_{OUT}$  because the voltage difference is higher.

☑ 8-5 shows typical efficiency waveforms with VLDOIN powered by different input voltages.

図 8-5. Efficiency Improvements with VLDOIN ( $V_{OUT} = 5 \text{ V}$ )

#### 8.3.9 Overcurrent Protection (OCP)

The TLVM13620 is protected from overcurrent conditions using cycle-by-cycle current limiting of the peak inductor current. The current is compared every switching cycle to the current limit threshold. During an overcurrent condition, the output voltage decreases.

The TLVM13620 employs hiccup overcurrent protection if there is an extreme overload. In hiccup mode, the regulator is shut down and kept off for 80 ms (typical) before the TLVM13620 tries to start again. If an overcurrent or short-circuit fault condition still exists, hiccup repeats until the fault condition is removed. Hiccup mode reduces power dissipation under severe overcurrent conditions and prevents overheating and potential damage to the device. Once the fault is removed, the module automatically recovers and returns to normal operation.

#### 8.3.10 Thermal Shutdown

Thermal shutdown is an integrated self-protection used to limit junction temperature and prevent damage related to overheating. Thermal shutdown turns off the device when the junction temperature exceeds 168°C (typical) to prevent further power dissipation and temperature rise. Junction temperature decreases after shutdown, and the TLVM13620 attempts to restart when the junction temperature falls to 158°C (typical).

#### 8.4 Device Functional Modes

#### 8.4.1 Shutdown Mode

The EN pin provides ON and OFF control for the TLVM13620. When  $V_{EN}$  is below approximately 0.4 V, the device is in shutdown mode. Both the internal LDO and the switching regulator are off. The input quiescent current in shutdown mode drops to 0.6  $\mu$ A (typical). The TLVM13620 also employs internal undervoltage protection. If the input voltage is below its UV threshold, the regulator remains off.

#### 8.4.2 Standby Mode

The internal LDO has a lower enable threshold than the regulator itself. When  $V_{EN}$  is above 1.1 V (maximum) and below the precision enable threshold of 1.263 V (typical), the internal LDO is on and regulating. The precision enable circuitry is turned on once the internal  $V_{CC}$  is above its UVLO threshold. The switching action and voltage regulation are not enabled until  $V_{EN}$  rises above the precision enable threshold.

#### 8.4.3 Active Mode

The TLVM13620 is in active mode when  $V_{IN}$  and  $V_{EN}$  are above their relevant thresholds and no fault conditions are present. The simplest way to enable the operation is to connect the EN pin to  $V_{IN}$ , which allows self-start–up when the applied input voltage exceeds the minimum start-up voltage.

### 9 Applications and Implementation

#### Note

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 9.1 Application Information

The TLVM13620 only requires a few external components to convert from a wide range of supply voltages to a fixed output voltage. The following section describes the design procedure to configure the TLVM13620 power module. To expedite and streamline the design process, WEBENCH® online software is available to generate complete designs, leveraging iterative design procedures and access to comprehensive component databases.

As mentioned previously, the TLVM13620 also integrates several optional features to meet system design requirements, including the following:

- Precision enable with hysteresis

- External adjustable UVLO

- · Adjustable SW node slew rate

- A power-good indicator

The following application circuits show the TLVM13620 configuration options suitable for several application use cases.

### 9.2 Typical Applications

The following designs show sample typical applications and design procedures to implement the TLVM13620.

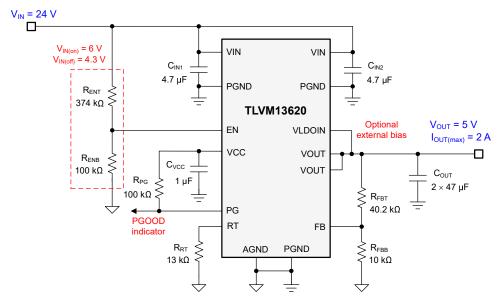

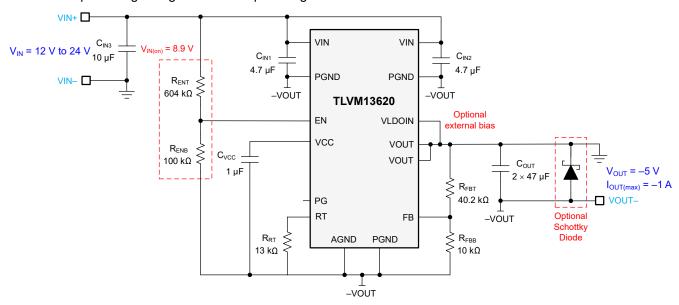

#### 9.2.1 Design 1 — 2-A Synchronous Buck Regulator for Industrial Applications

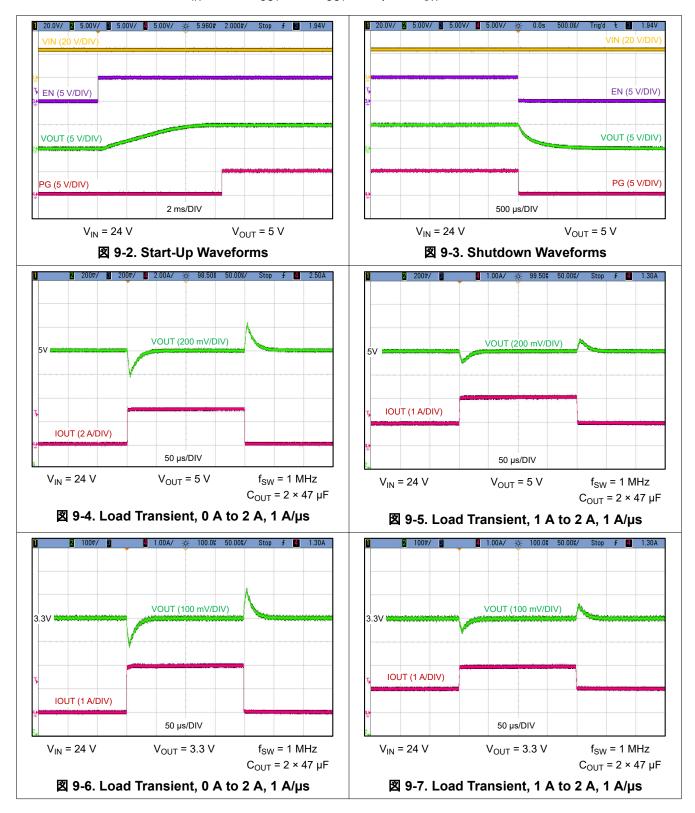

$\boxtimes$  9-1 shows the schematic diagram of a 5-V, 2-A buck regulator with a switching frequency of 1 MHz. The nominal input voltage for the sample design is 24 V. A 13-k $\Omega$  R<sub>RT</sub> resistor sets the free-running switching frequency at 1 MHz. An optional SYNC input signal allows adjustment of the switching frequency for this specific application.

図 9-1. Circuit Schematic

### 9.2.1.1 Design Requirements

For this design example, use the parameters listed in 表 9-1 as the input parameters and follow the design procedures in セクション 9.2.1.2.

表 9-1. Design Example Parameters

| Design Parameter    | Value      |

|---------------------|------------|

| Input voltage       | 24 V       |

| Output voltage      | 5 V        |

| Output current      | 0 A to 2 A |

| Switching frequency | 1 MHz      |

表 9-2 gives the selected buck module power-stage components with availability from multiple vendors. This design uses an all-ceramic output capacitor implementation.

表 9-2. List of Materials for Application Circuit 1

| Reference<br>Designator               | Qty | Specification                               | Manufacturer <sup>(1)</sup> | Part Number          |

|---------------------------------------|-----|---------------------------------------------|-----------------------------|----------------------|

|                                       |     | 4.7 μF, 50 V, X7R, 1210, ceramic            | Taiyo Yuden                 | UMK325B7475KN-TR     |

| C <sub>IN1</sub> , C <sub>IN2</sub>   | 2   | 4.7 µr, 50 V, X/IX, 1210, Ceramic           | TDK                         | CGA6P3X7R1H475K250AB |

|                                       |     | 4.7 μF, 100 V, X7S, 1206, ceramic           | Murata                      | GRM31CC72A475KE11L   |

| C C                                   | 2   | 47 μF, 10 V, X7R, 1210, ceramic             | Murata                      | GRM32ER71A476ME15L   |

| C <sub>OUT1</sub> , C <sub>OUT2</sub> | 2   | 47 μr, 10 v, λ/1λ, 1210, ceramic            | AVX                         | 1210ZC476MAT2A       |

| Const                                 | 1   | 1 μF, 16 V, X7R, 0603, ceramic              | Murata                      | GCM188R71C105KA64J   |

| C <sub>VCC</sub>                      |     | 1 μF, 16 V, X5R, 0402, ceramic              | Taiyo Yuden                 | EMK105BJ105KVHF      |

| U <sub>1</sub>                        | 1   | TLVM13620 36-V, 2-A synchronous buck module | Texas Instruments           | TLVM13620RDLR        |

<sup>(1)</sup> See the *Third-Party Products Disclaimer*.

More generally, the TLVM13620 module is designed to operate with a wide range of external components and system parameters. However, the integrated loop compensation is optimized for a certain range of output capacitance.

#### 9.2.1.2 Detailed Design Procedure

#### 9.2.1.2.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the TLVM13620 device with the WEBENCH® Power Designer.

- Start by entering the input voltage (V<sub>IN</sub>), output voltage (V<sub>OUT</sub>), and output current (I<sub>OUT</sub>) requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- Run electrical simulations to see important waveforms and circuit performance.

- Run thermal simulations to understand board thermal performance.

- Export customized schematic and layout into popular CAD formats.

- Print PDF reports for the design, and share the design with colleagues.

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

#### 9.2.1.2.2 Output Voltage Setpoint

Submit Document Feedback

The output voltage of the TLVM13620 device is externally adjustable using a resistor divider. The recommended value of  $R_{FBB}$  is 10 kΩ. The value for  $R_{FBB}$  can be selected from  $\frac{1}{8}$  8-1 or calculated using  $\frac{1}{8}$  10:

Product Folder Links: TLVM13620

$$R_{FBT} \left[ k\Omega \right] = R_{FBB} \left[ k\Omega \right] \cdot \left( \frac{V_{OUT} \left[ V \right]}{1V} - 1 \right)$$

(10)

For the desired output voltage of 5 V, the formula yields a value of 40.2 k $\Omega$ . Choose the closest available standard value of 40.2 k $\Omega$  for R<sub>FBT</sub>.

#### 9.2.1.2.3 Switching Frequency Selection

The recommended switching frequency for standard output voltages can be found in  $\frac{1}{2}$  8-1. For a 5-V output, the recommended switching frequency is 1 MHz. To set the switching frequency to 1 MHz, connect a 13.0-kΩ resistor between the RT pin and AGND.

### 9.2.1.2.4 Input Capacitor Selection

The TLVM13620 requires a minimum input capacitance of  $2 \times 4.7$ - $\mu$ F ceramic type. High-quality ceramic type capacitors with sufficient voltage and temperature rating are required. The voltage rating of input capacitors must be greater than the maximum input voltage.

For this design, select two 4.7- $\mu$ F, 50-V, 1210 case size, ceramic capacitors.

#### 9.2.1.2.5 Output Capacitor Selection

For a 5-V output, the TLVM13620 requires a minimum of 25  $\mu$ F of effective output capacitance for proper operation (see  $\frac{1}{8}$  8-1). High-quality ceramic type capacitors with sufficient voltage and temperature rating are required. Additional output capacitance can be added to reduce ripple voltage or for applications with transient load requirements.

For this design example, select two 47- $\mu$ F, 10-V, 1210 case size, ceramic capacitors, which have a total effective capacitance of approximately 48  $\mu$ F at 5 V.

#### 9.2.1.2.6 Other Connections

- Connect VLDOIN to VOUT to improve efficiency.