TPA3138D2

JAJSEX8A - MARCH 2018 - REVISED JUNE 2018

## TPA3138D2 10W、3.5V~14.4V、インダクタ不要、ステレオClass-Dス ピーカー・アンプ

### 特長

- 3.5V~14.4Vの広い電源電圧範囲

- 1% THD+N、12V電源で6Ωへ2×10W

- 10% THD+N、12V電源で4Ωへ1×18.5W

- THD+N: 1W、1kHz入力、6Ωで0.04%

- 携帯アプリケーションのバッテリ駆動時間延長

- 1SPWモードでアイドル電流20mA (12V)

- 90%を超えるClass-D効率

- ソリューションのサイズとコストを低減

- インダクタなしで動作

- インダクタ不使用でEN55013およびEN55022 EMC準拠

- 外部ヒートシンク不要

- 柔軟なオーディオ・ソリューション

- シングルエンドまたは差動アナログ入力

- 20dBと26dBのゲインを選択可能

- 起動時にポップやクリック音が発生しない

- 保護および自動復元機能を内蔵

- ピン間、ピンからグランド、ピンから電源への短絡 保護

- サーマル保護、低電圧保護、過電圧保護

- 電力リミッタ―およびDCスピーカー保護

- TPA3110D2、TPA3136D2、TPA3136AD2とピン 互換

## 2 アプリケーション

- テレビおよびモニタ

- Bluetooth®スピーカーおよびワイヤレス・スピー カー

- スマート家電のオーディオ・アンプ

- モノのインターネットのオーディオ・スピーカー

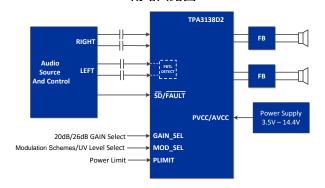

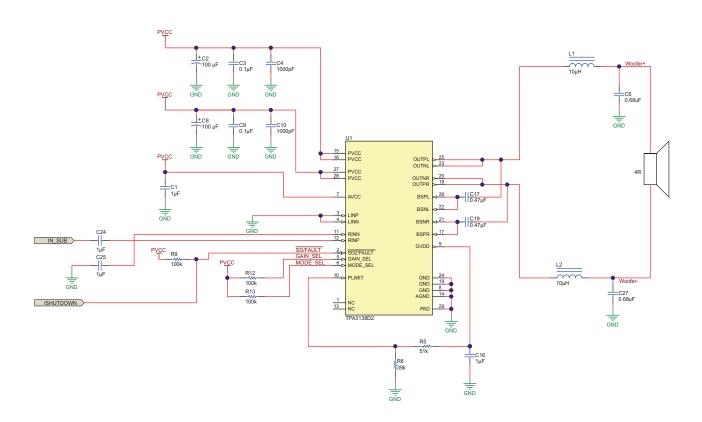

- 消費者向けオーデ<u>ィオ機器</u> 概略回路図

## 3 概要

TPA3138D2は10W/ch、 高効率でアイドル電流の低い Class-Dステレオ・オーディオ・アンプです。最小で3.2 $\Omega$ の負荷のステレオ・スピーカーを駆動できます。1SPW モードでは、わずか21mA (12V)のアイドル電流しか消費 せず、最低3.5Vで動作できるため、Bluetoothスピー カー、バッテリ駆動の家電、その他消費電力が重要なアプ リケーションで、長時間オーディオを再生でき、熱特性も 向上します。

高度なEMI抑制と拡散スペクトラム制御により、出力に安 価なフェライト・ビーズ・フィルタを使用しながらEMC要件 を満たすことができ、システム・コストを削減できます。

設計をさらに簡素化するため、TPA3138D2には低電圧、 過電圧、電力制限、短絡、過熱などの不可欠な保護機能 に加えて、DCスピーカー保護機能が内蔵されています。 これらの保護機能にはすべて、自動回復機能があります。

TPA3138D2はTPA3110D2、TPA3136D2、 TPA3136AD2とピン互換なので、顧客はTPA3138D2 のすべての機能を既存の設計で活用できます。

#### 製品情報(1)

|           | 2CHH    1   1   M |               |

|-----------|-------------------|---------------|

| 型番        | パッケージ             | 本体サイズ(公称)     |

| TPA3138D2 | HTSSOP (28)       | 9.70mm×4.40mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

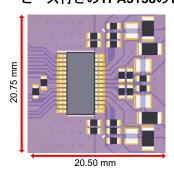

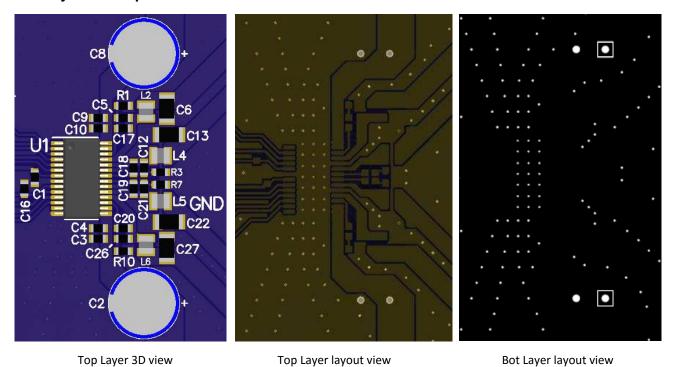

### フェライト・ビーズ付きのTPA3138のレイアウト

## 目次

| 1 | 特長1                                  |    | 9.3 Feature Description                      | 13 |

|---|--------------------------------------|----|----------------------------------------------|----|

| 2 | アプリケーション1                            |    | 9.4 Device Functional Modes                  | 16 |

| 3 | 概要 1                                 | 10 | Application and Implementation               | 18 |

| 4 | 改訂履歴                                 |    | 10.1 Application Information                 | 18 |

| 5 | Device Comparison Table              |    | 10.2 Typical Applications                    | 18 |

| 6 | Pin Configuration and Functions      | 11 | Power Supply Recommendations                 | 25 |

| 7 | Specifications5                      |    | 11.1 Power Supply Decoupling, C <sub>S</sub> | 25 |

| • | 7.1 Absolute Maximum Ratings         | 12 | Layout                                       | 26 |

|   | 7.1 Absolute Maximum Ratings         |    | 12.1 Layout Guidelines                       | 26 |

|   | 7.3 Recommended Operating Conditions |    | 12.2 Layout Example                          |    |

|   | 7.4 Thermal Information              | 13 | デバイスおよびドキュメントのサポート                           | 28 |

|   | 7.5 Electrical Characteristics       |    | <b>13.1</b> デバイス・サポート                        | 28 |

|   | 7.6 Switching Characteristics        |    | 13.2 ドキュメントのサポート                             | 28 |

|   | 7.7 Typical Characteristics          |    | 13.3 ドキュメントの更新通知を受け取る方法                      | 28 |

| 8 | Parameter Measurement Information    |    | 13.4 コミュニティ・リソース                             | 28 |

| 9 |                                      |    | 13.5 商標                                      | 28 |

| 9 | Detailed Description                 |    | 13.6 静電気放電に関する注意事項                           | 28 |

|   | 9.1 Overview                         |    | 13.7 Glossary                                | 28 |

|   | 9.2 Functional Block Diagram         | 14 | メカニカル、パッケージ、および注文情報                          | 28 |

|   |                                      |    |                                              |    |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| 20 | <b>)18</b> 年3月発行のものから更新       | Page |

|----|-------------------------------|------|

| •  | デバイスのステータスを「事前情報」から「量産データ」に変更 |      |

## 5 Device Comparison Table

| Product    | Supply Voltage  | Modulation Scheme | Package                                | Rdson     | Gain                       | Inductor Free |     |

|------------|-----------------|-------------------|----------------------------------------|-----------|----------------------------|---------------|-----|

| TPA3138D2  | 3.5-V to 14.4-V | BD, 1SPW          | BD, 1SPW HTSSOP-28 180-mΩ 20-dB, 26-dB |           | HTSSOP-28 180-m $\Omega$   |               | YES |

| TPA3110D2  | 8-V to 26-V     | BD                | HTSSOP-28                              | 240-m $Ω$ | 20-dB, 26-dB, 32-dB, 36-dB | NO            |     |

| TPA3136D2  | 4.5-V to 14.4-V | BD                | HTSSOP-28                              | 240-m $Ω$ | 26-dB                      | YES           |     |

| TPA3136AD2 | 8-V to 14.4-V   | BD                | HTSSOP-28                              | 240-mΩ    | 26-dB                      | YES           |     |

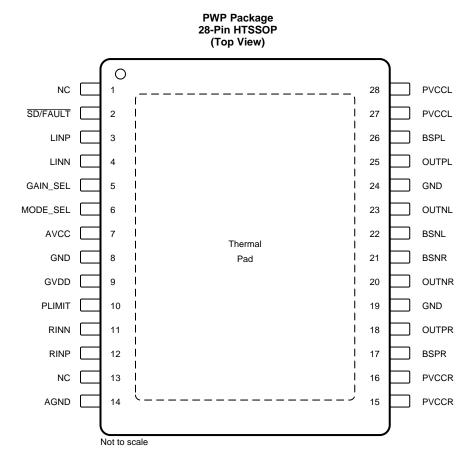

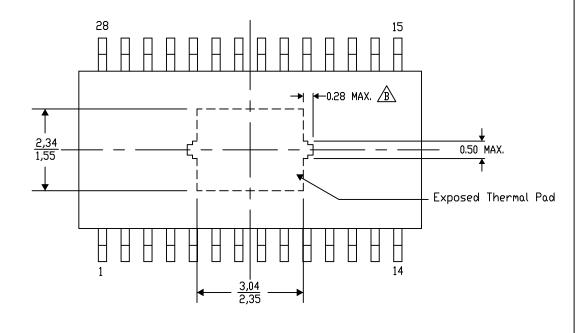

## 6 Pin Configuration and Functions

#### **Pin Functions**

| PIN NAME NO. |   | I/O/P <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                        |  |  |

|--------------|---|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|              |   | I/O/F · /            | DESCRIPTION                                                                                                                                                                                                                                                                                                                        |  |  |

| NC           | 1 | -                    | No Connect Pin. Can be shorted to PVCC or shorted to GND or left open.                                                                                                                                                                                                                                                             |  |  |

| SD/FAULT     | 2 | Ю                    | TTL logic levels with compliance to AVCC. Shutdown logic input for audio amp (LOW, outputs Hi-Z; HIGH, outputs enabled). General fault reporting including Over-Temp, Over-Current, DC Detect. SD/FAULT= High, normal operation, SD/FAULT= Low, fault condition Device will auto-recover once the OT/OC/DC Fault has been removed. |  |  |

| LINP         | 3 | I                    | Positive audio input for left channel. Biased at 2.5 V. Connect to GND for PBTL mode.                                                                                                                                                                                                                                              |  |  |

| LINN         | 4 | 1                    | Negative audio input for left channel. Biased at 2.5 V. Connect to GND for PBTL mode.                                                                                                                                                                                                                                              |  |  |

| GAIN_SEL     | 5 | I                    | Gain select least significant bit. TTL logic levels with compliance to AVDD. Low = 20 dB Gain, High = 26 dB Gain, Floating = 26 dB Gain.                                                                                                                                                                                           |  |  |

## Pin Functions (continued)

| PIN          |                    | I/O/P <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                       |  |  |  |  |

|--------------|--------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME         | NO.                | I/O/P(**)            | DESCRIPTION                                                                                                                                                                                                                       |  |  |  |  |

| MODE_SEL     | 6                  | I                    | Mode select least significant bit. TTL logic levels with compliance to AVDD. Low = BD Mode/UV Threshold = 7.5 V, High = Low-Idle-Current 1SPW Mode/UV Threshold = 3.4V, Floating = Low-Idle-Current 1SPW Mode/UV threshold = 3.4V |  |  |  |  |

| AVCC         | 7 P Analog supply. |                      |                                                                                                                                                                                                                                   |  |  |  |  |

| GND          | 8                  | -                    | Analog signal ground.                                                                                                                                                                                                             |  |  |  |  |

| GVDD         | 9                  | 0                    | FET gate drive supply. Nominal voltage is 5 V.                                                                                                                                                                                    |  |  |  |  |

| PLIMIT       | 10                 | 1                    | Power limiter level control. Connect a resistor divider from GVDD to GND to set power limit. Connect directly to GVDD for no power limit.                                                                                         |  |  |  |  |

| RINN         | 11                 | I                    | Negative audio input for right channel. Biased at 2.5 V.                                                                                                                                                                          |  |  |  |  |

| RINP         | 12                 | I                    | Positive audio input for right channel. Biased at 2.5 V.                                                                                                                                                                          |  |  |  |  |

| NC           | 13                 | -                    | No Connect Pin. Can be shorted to PVCC or shorted to GND or left open.                                                                                                                                                            |  |  |  |  |

| AGND         | 14                 | -                    | Analog signal ground. Connect to the thermal pad.                                                                                                                                                                                 |  |  |  |  |

| PVCCR 15, 16 |                    | Р                    | Power supply for right channel H-bridge. Right channel and left channel power supply inputs are connected internally.                                                                                                             |  |  |  |  |

| BSPR         | 17                 | Р                    | Bootstrap supply (BST) for right channel, positive high-side FET.                                                                                                                                                                 |  |  |  |  |

| OUTPR        | 18                 | 0                    | Class-D H-bridge positive output for right channel.                                                                                                                                                                               |  |  |  |  |

| GND          | 19                 | -                    | Power ground for the H-bridges.                                                                                                                                                                                                   |  |  |  |  |

| OUTNR        | 20                 | 0                    | Class-D H-bridge negative output for right channel.                                                                                                                                                                               |  |  |  |  |

| BSNR         | 21                 | Р                    | Bootstrap supply (BST) for right channel, negative high-side FET.                                                                                                                                                                 |  |  |  |  |

| BSNL         | 22                 | Р                    | Bootstrap supply (BST) for left channel, negative high-side FET.                                                                                                                                                                  |  |  |  |  |

| OUTNL        | 23                 | 0                    | Class-D H-bridge negative output for left channel.                                                                                                                                                                                |  |  |  |  |

| GND          | 24                 | -                    | Power ground for the H-bridges.                                                                                                                                                                                                   |  |  |  |  |

| OUTPL        | 25                 | 0                    | Class-D H-bridge positive output for left channel.                                                                                                                                                                                |  |  |  |  |

| BSPL         | 26                 | Р                    | Bootstrap supply (BST) for left channel, positive high-side FET.                                                                                                                                                                  |  |  |  |  |

| PVCCL 27, 28 |                    | Р                    | Power supply for left channel H-bridge. Right channel and left channel power supply inputs are connected internally.                                                                                                              |  |  |  |  |

| Thermal Pad  |                    | -                    | Connect to GND for best thermal and electrical performance                                                                                                                                                                        |  |  |  |  |

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                             |                                                     | MIN  | MAX                       | UNIT |

|---------------------------------------------|-----------------------------------------------------|------|---------------------------|------|

| Supply voltage                              | AVCC to GND, PVCC to GND                            | -0.3 | 20                        | V    |

| Input current                               | To any pin except supply pins                       |      | 10                        | mA   |

|                                             | SD/FAULT to GND <sup>(2)</sup> , GAIN_SEL, MODE_SEL | -0.3 | AVCC + 0.3                | V    |

| lateria a nia valtana                       | SD/FAULT to GND , GAIN_SEL, MODE_SEL                |      | 10                        | V/ms |

| Interface pin voltage                       | PLIMIT                                              | -0.3 | GVDD + 0.3                | V    |

|                                             | RINN, RINP, LINN, LINP                              | -0.3 | 5.5                       | V    |

|                                             | BTL, (10 V < PVCC < 14.4 V)                         | 4.8  |                           |      |

| Minimum load registeres D                   | BTL, (3.5 V < PVCC < 10 V)                          | 3.2  |                           | 0    |

| Minimum load resistance, R <sub>L</sub>     | PBTL, (10 V < PVCC < 14.4 V)                        | 2.4  |                           | Ω    |

|                                             | PBTL, (3.5 V < PVCC < 10 V)                         | 1.6  |                           |      |

| Continuous total power dissipation          |                                                     |      | ne Thermal<br>ation Table |      |

| Operating Juncation Temperature rang        | erating Juncation Temperature range                 |      | 150                       | °C   |

| Storage temperature range, T <sub>stg</sub> |                                                     | -40  | 125                       | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±1000 | V    |

| V <sub>(ESD)</sub> |                         | Charged device model (CDM), per JEDEC specification JESD22-C101 (2) | ±250  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> The voltage slew rate of these pins must be restricted to no more than 10 V/ms. For higher slew rates, use a 100 kΩ resister in series with the pins.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 | PARAMETER                          | TEST CONDITIONS                                                                          | MIN | MAX  | UNIT |

|-----------------|------------------------------------|------------------------------------------------------------------------------------------|-----|------|------|

| $V_{CC}$        | Supply voltage                     | PVCC, AVCC                                                                               | 3.5 | 14.4 | V    |

| $V_{IH}$        | High-level input voltage           | SD/FAULT (1), GAIN_SEL, MODE_SEL                                                         | 2   | AVCC | V    |

| $V_{IL}$        | Low-level input voltage            | SD/FAULT, GAIN_SEL, MODE_SEL <sup>(2)</sup>                                              |     | 0.8  | V    |

| $V_{OL}$        | Low-level output voltage           | $\overline{SD}/\overline{FAULT}$ , $R_{PULL-UP} = 100 \text{ k}\Omega$ , PVCC = 14.4 V   |     | 8.0  | V    |

| I <sub>IH</sub> | High-level input current           | $\overline{SD}/\overline{FAULT}$ , GAIN_SEL, MODE_SEL, V <sub>I</sub> = 2 V, AVCC = 12 V |     | 50   | μΑ   |

| I <sub>IL</sub> | Low-level input current            | SD/FAULT, GAIN_SEL, MODE_SEL, V <sub>I</sub> = 0.8 V, AVCC = 12 V                        |     | 5    | μΑ   |

| T <sub>A</sub>  | Operating free-air temperature (3) |                                                                                          | -10 | 85   | °C   |

| TJ              | Operating junction temperature (3) |                                                                                          | -10 | 150  | °C   |

- Set  $\overline{SD/FAULT}$  to high level, make sure the pull-up resistor is larger than 4.7 k $\Omega$  and smaller than 500 k $\Omega$  Set GAIN\_SEL and MODE\_SEL to low level, make sure pull down resistor<10k $\Omega$

- The TPA3138D2 incorporates an exposed thermal pad on the underside of the chip. This acts as a heatsink, and it must be connected to a thermally dissipating plane for proper power dissipation. Failure to do so may result in the device going into thermal protection shutdown. See TI Technical Briefs SLMA002 for more information about using the TSSOP thermal pad.

## 7.4 Thermal Information

|                        |                                              | TPA3138D2    |      |

|------------------------|----------------------------------------------|--------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | PWP (HTSSOP) | UNIT |

|                        |                                              | 28 PINS      |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 30.3         | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 33.5         | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 17.5         | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.9          | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 7.2          | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 0.9          | °C/W |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

## 7.5 Electrical Characteristics

$T_A = 25^{\circ}C$ , AVCC = PVCC = 12 V, RL = 6  $\Omega$ . Over operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                                       | TEST                                                            | CONDITIONS                                                                                 | MIN | TYP  | MAX | UNIT |

|---------------------|-------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----|------|-----|------|

| AC CHA              | RACTERISTICS                                    |                                                                 |                                                                                            |     |      |     |      |

| PSRR                | Power supply ripple rejection                   | 200-mV <sub>PP</sub> ripple at 1 kH<br>Gain = 26 dB, Inputs ac- |                                                                                            |     | -70  |     | dB   |

| Po                  | Continuous output power, BTL                    | THD+N = 1%, f = 1 kHz,                                          | $PV_{CC}$ = 12 V, $R_L$ = 6 $\Omega$                                                       |     | 10   |     | W    |

| Po                  | Continuous output power, BTL                    | THD+N = 10%, f = 1 kH                                           | z, $PV_{CC} = 12 \text{ V}$ , $R_L = 6 \Omega$                                             |     | 12   |     | W    |

| Po                  | Continuous output power, BTL                    | THD+N = 1%, f = 1 kHz,                                          | $PV_{CC}$ = 12 V, $R_L$ = 8 $\Omega$                                                       |     | 8    |     | W    |

| Po                  | Continuous output power, BTL                    | THD+N = 10%, f = 1 kH                                           | z, PV <sub>CC</sub> = 12 V, R <sub>L</sub> = 8 Ω                                           |     | 9.9  |     | W    |

| Po                  | Continuous output power, PBTL (mono)            | THD+N = 10%, f = 1 kH;                                          | z, $PV_{CC}$ = 12 V, $R_L$ = 4 $\Omega$                                                    |     | 18.5 |     | W    |

| Io                  | Maximum output current                          | $f = 1 \text{ kHz}, R_L = 3 \Omega$                             |                                                                                            |     | 3.5  |     | Α    |

| THD+N               | Total harmonic distortion + noise               | f = 1 kHz, P <sub>O</sub> = 5 W (hal                            | f-power)                                                                                   |     | 0.04 |     | %    |

|                     |                                                 |                                                                 |                                                                                            |     | 85   |     | μV   |

| .,                  |                                                 | 20 Hz to 22 kHz, A-weig                                         | nted filter, Gain = 26 dB                                                                  |     | -81  |     | dBV  |

| V <sub>n</sub>      | Output integrated noise                         |                                                                 |                                                                                            |     | 72   |     | μV   |

|                     |                                                 | 20 Hz to 22 kHz, A-weig                                         | 20 Hz to 22 kHz, A-weighted filter, Gain = 20 dB                                           |     |      |     | dBV  |

|                     | Crosstalk                                       | V <sub>O</sub> = 1 Vrms, Gain = 26                              | dB, f = 1 kHz                                                                              |     | -95  |     | dB   |

| SNR                 | Signal-to-noise ratio                           | Maximum output at THD f = 1 kHz, Gain = 26 dB,                  |                                                                                            |     |      | dB  |      |

| OTE                 | Thermal trip point                              |                                                                 |                                                                                            |     | 150  |     | °C   |

|                     | Thermal hysteresis                              |                                                                 |                                                                                            |     | 15   |     | °C   |

| DC CHA              | RACTERISTICS                                    |                                                                 |                                                                                            |     |      |     |      |

| Vos                 | Output offset voltage (measured differentially) | V <sub>I</sub> = 0 V, Gain = 26 dB                              |                                                                                            |     | 1.5  |     | mV   |

| I <sub>CC</sub>     | Quiescent supply current                        | SD/FAULT = 2 V, 10 μF<br>1SPW Mode, PV <sub>CC</sub> = 12       |                                                                                            |     | 20   |     | mA   |

| I <sub>CC</sub>     | Quiescent supply current                        | SD/FAULT = 2 V, 10 μF<br>BD Mode, PV <sub>CC</sub> = 12 V       | + 680 nF output filter,                                                                    |     | 37   |     | mA   |

| I <sub>CC(SD)</sub> | Quiescent supply current in shutdown mode       | SD/FAULT = 0.8 V, no le                                         | pad                                                                                        |     | 10   |     | μA   |

| ,                   |                                                 | I <sub>O</sub> = 500 mA, T <sub>J</sub> = 25°C                  | High Side                                                                                  |     | 180  |     |      |

| r <sub>DS(on)</sub> | Drain-source on-state resistance                | excluding metal and bond wire resistance                        | Low side                                                                                   |     | 180  |     | mΩ   |

| G                   | Gain                                            | GAIN_SEL= 0.8 V                                                 |                                                                                            | 19  | 20   | 21  | dB   |

| G                   | Gain                                            | GAIN_SEL= 2 V                                                   |                                                                                            | 25  | 26   | 27  | dB   |

| t <sub>ON</sub>     | Turn-on time                                    | SD/FAULT = 2 V                                                  | SD/FAULT = 2 V                                                                             |     | 50   |     | ms   |

| t <sub>OFF</sub>    | Turn-off time                                   | SD/FAULT = 0.8 V                                                |                                                                                            |     | 2.9  |     | μs   |

| GVDD                | Gate drive supply                               | I <sub>GVDD</sub> = 2 mA                                        |                                                                                            | 4.8 | 5    | 5.2 | V    |

| t <sub>DCDET</sub>  | DC detect time                                  |                                                                 | $V_{RINP}$ = 2.6 V and $V_{RINN}$ = 2.4 V,<br>or $V_{RINP}$ = 2.4 V and $V_{RINN}$ = 2.6 V |     | 800  |     | ms   |

| OVP                 | Over Voltage Protection                         |                                                                 |                                                                                            |     | 15.8 |     | V    |

| UVP                 | Under Voltage Protection                        | MODE_SEL = 0.8 V (BE                                            | ) mode)                                                                                    |     | 7.5  |     | V    |

| UVP                 | Under Voltage Protection                        | MODE_SEL = 2 V, or flo                                          | pating (1SPW mode)                                                                         |     | 3.4  |     | V    |

## 7.6 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

|                      | • • • • • • • • • • • • • • • • • • • •  |     |     |     |      |

|----------------------|------------------------------------------|-----|-----|-----|------|

|                      | PARAMETER                                | MIN | NOM | MAX | UNIT |

| f <sub>OSC, SS</sub> | Oscillator frequency, Spread Spectrum ON | 305 |     | 340 | kHz  |

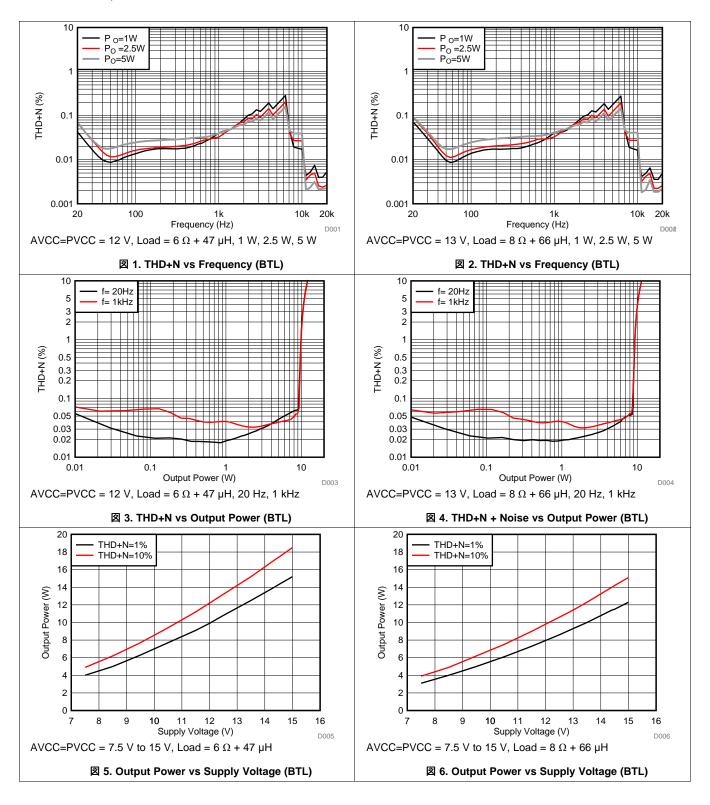

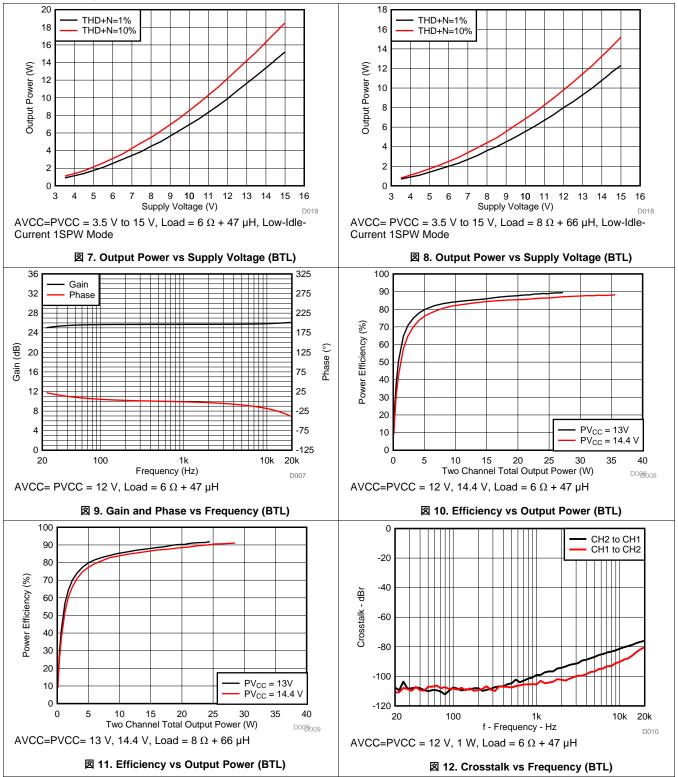

### 7.7 Typical Characteristics

All measurements taken at audio frequency = 1 kHz, closed-loop gain = 26 dB, BD mode, T  $_{A}$ = 25°C, AES17 filter using the TPA3138D2EVM, unless otherwise noted.

## **Typical Characteristics (continued)**

All measurements taken at audio frequency = 1 kHz, closed-loop gain = 26 dB, BD mode, T  $_{A}$ = 25°C, AES17 filter using the TPA3138D2EVM, unless otherwise noted.

## **Typical Characteristics (continued)**

All measurements taken at audio frequency = 1 kHz, closed-loop gain = 26 dB, BD mode, T  $_{A}$ = 25°C, AES17 filter using the TPA3138D2EVM, unless otherwise noted.

#### 8 Parameter Measurement Information

All parameters are measured according to the conditions described in the Specifications section.

Most audio analyzers does not give correct readings of Class-D amplifiers' performance due to their sensitivity to the out-of-band noise present at the amplifier outputs. An AES-17 pre-analyzer filter is recommended to use for Class-D amplifier measurements. In absence of such filters, a 30-kHz low-pass filter (10  $\Omega$  + 47 nF) can be used to reduce the out-of-band noise remaining on the amplifier outputs.

## 9 Detailed Description

#### 9.1 Overview

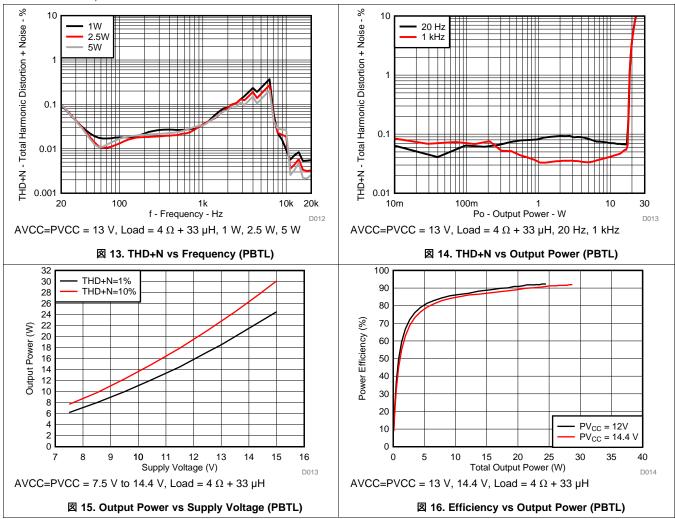

The TPA3138D2 is designed as a low-idle-power, cost-effective, general-purpose Class-D audio amplifier. The built-in spread spectrum control efficiently reduces EMI and enables the use of the ferrite beads instead of the inductors for ≤2x10W applications.

To facilitate system design, the TPA3138D2 needs only a single power supply between 3.5 V and 14.4 V for operation. An internal voltage regulator provides suitable voltage levels for the gate driver, digital, and low-voltage analog circuitry. Additionally, all circuitry requiring a floating voltage supply, as in the high-side gate drive, is accommodated by built-in bootstrap circuitry with integrated boot strap diodes requiring only an external capacitor for each half-bridge.

The audio signal path, including the gate drive and output stage, is designed as identical, independent full-bridges. All decoupling capacitors should be placed as close as possible to their associated pins. The physical loop with the power supply pins, decoupling capacitors, and GND return path to the device pins must be kept as short as possible, and with as little area as possible to minimize induction (see reference board documentation for additional information).

For a properly functioning bootstrap circuit, a small ceramic capacitor must be connected from each bootstrap pin (BSXX) to the power-stage output pin (OUTXX). When the power-stage output is low, the bootstrap capacitor is charged through an internal diode connected between the gate-drive power-supply pin (GVDD) and the bootstrap pins. When the power-stage output is high, the bootstrap capacitor potential is shifted above the output potential and thus provides a suitable voltage supply for the high-side gate driver. In an application with PWM switching frequencies in the datasheet specified range, use ceramic capacitors with at least 220-nF capacitance, size 0603 or 0805, for the bootstrap supply. These capacitors ensure sufficient energy storage, even during clipped low frequency audio signals, to keep the high-side power stage FET (LDMOS) fully turned on during the remaining part of its ON cycle.

Special attention should be paid to the power-stage power supply; this includes component selection, PCB placement, and routing. For optimal electrical performance, EMI compliance, and system reliability, each PVCC pin should be decoupled with ceramic capacitors that are placed as close as possible to each supply pin. It is recommended to follow the PCB layout of the reference design. For additional information on recommended power supply and required components, see the application diagrams in this data sheet.

The PVCC power supply should have low output impedance and low noise. The power-supply ramp and SD/FAULT release sequence is not critical for device reliability as facilitated by the internal power-on-reset circuit, but it is recommended to release SD/FAULT after the power supply is settled for minimum turn on audible artifacts.

## 9.2 Functional Block Diagram

#### 9.3 Feature Description

## 9.3.1 Analog Gain

The analog gain of the TPA3138D2 can be changed by GAIN\_SEL pin. Low Level, Gain = 20 dB; High Level, Gain = 26 dB.

#### 9.3.2 SD/FAULT Operation

The TPA3138D2 device employs a shutdown mode of operation designed to reduce supply current (I<sub>CC</sub>) to the absolute minimum level during periods of nonuse for power conservation. The SD/FAULT input pin should be held high (see Specifications table for trip point) during normal operation when the amplifier is in use. Pulling SD/FAULT low causes the outputs to mute and the amplifier to enter a low-current state. Never leave SD/FAULT unconnected, because the amplifier operation would be unpredictable.

For the best power-off pop performance, place the amplifier in the shutdown mode prior to removing the power supply voltage.

#### **9.3.3 PLIMIT**

If selected, the PLIMIT operation limits the output voltage level to a voltage level below the supply rail. If the amplifier operates like it is powered by a lower supply voltage, then it limits the output power by voltage clipping. Add a resistor divider from GVDD to ground to set the threshold voltage at the PLIMIT pin.

図 17. PLIMIT Circuit Operation

The PLIMIT circuit sets a limit on the output peak-to-peak voltage. The limiting is done by limiting the duty cycle to a fixed maximum value. The limit can be thought of as a "virtual" voltage rail which is lower than the supply connected to PVCC. The "virtual" rail is approximately 5.7 times (with BD mode) and 11.4 times (with 1SPW mode) the voltage at the PLIMIT pin. The output voltage can be used to calculate the maximum output power for a given maximum input voltage and speaker impedance.

(1)

### **Feature Description (continued)**

$$P_{OUT} = \frac{\left( \left( \frac{R_L}{R_L + 2 \times R_S} \right) \times V_P \right)^2}{2 \times R_L}$$

for unclipped power

where

- $P_{OUT}$  (10%THD) = 1.25 ×  $P_{OUT}$  (unclipped)

- R<sub>I</sub> is the load resistance.

- $R_S$  is the total series resistance including  $R_{DS(on)}$ , and output filter resistance.

- V<sub>P</sub> is the peak amplitude, which is limited by "virtual" voltage rail.

#### 9.3.4 Spread Spectrum and De-Phase Control

The TPA3138D2 device has built-in spread spectrum control of the oscillator frequency and de-phase of the PWM outputs to improve EMI performance. The spread spectrum scheme is internally fixed and is always turned on.

De-phase inverts the phase of the output PWM such that the idle output PWM waveforms of the two audio channels are inverted. De-phase does not affect the audio signal, or its polarity. De-phase only works with BD mode, it is auto-disabled in 1SPW mode

## 9.3.5 GVDD Supply

The GVDD Supply is used to power the gates of the output full-bridge transistors. Add a  $1-\mu F$  capacitor to ground at this pin.

#### 9.3.6 DC Detect

The TPA3138D2 device integrates a circuitry which protects the speakers from DC current that might occur due to defective capacitors on the input or shorts on the printed circuit board at the inputs. A DC detect fault is reported on the SD/FAULT pin as a low state. The DC Detect fault also causes the amplifier to shutdown by changing the state of the outputs to Hi-Z.

A DC Detect Fault is issued when the output DC voltage sustain for more than 800 msec at the same polarity. This feature protects the speaker from <a href="Iarge DC currents">Iarge DC currents</a> or AC currents less than 1 Hz. To avoid nuisance faults due to the DC detect circuit, hold the <a href="SD/FAULT">SD/FAULT</a> pin low at power-up until the signals at the inputs are stable. Also, take care to match the impedance seen at the positive and negative inputs to avoid nuisance DC detect faults.

#### 9.3.7 PBTL Select

The TPA3138D2 device offers the feature of Parallel BTL operation with two outputs of each channel connected directly. Connecting LINP and LINN directly to Ground (without capacitors) sets the device in Mono Mode during power up. Connect the OUTPR and OUTNR together for the positive speaker terminal and OUTNL and OUTPL together for the negative speaker terminal. Analog input signal is applied to INPR and INNR. For an example of the PBTL connection, see the schematic in the *Typical Applications* section.

#### 9.3.8 Short-Circuit Protection and Automatic Recovery Feature

The TPA3138D2 features over-current conditions against the output stage short-circuit conditions. The short-circuit protection fault is reported on the  $\overline{\text{SD/FAULT}}$  pin as a low state. The amplifier outputs are switched to a Hi-Z state when the short circuit protection latch is triggered .

The device recovers automatically once the over-current condition has been removed.

## 9.3.9 Over-Temperature Protection (OTP)

Thermal protection on the TPA3138D2 device prevents damage to the device when the internal die temperature exceeds 150°C. This triggering point has a ±15°C tolerance from device to device. Once the die temperature exceeds the thermal triggering point, the device is switched to the shutdown state and the outputs are disabled.

Thermal protection faults are reported on the SD/FAULT pin.

#### **Feature Description (continued)**

The device recovers automatically once the over temperature condition has been removed.

### 9.3.10 Over-Voltage Protection (OVP)

The TPA3138D2 device monitors the voltage on PVCC voltage threshold. When the voltage on PVCCL pin and PVCCR pin exceeds the over-voltage threshold (15.8 V typ), the OVP circuit puts the device into shutdown mode.

The device recovers automatically once the over-voltage condition has been removed.

## 9.3.11 Under-Voltage Protection (UVP)

When the voltage on PVCCL pin and PVCCR pin falls below the under-voltage threshold, the UVP circuit puts the device into shutdown mode. When MODE\_SEL pin is set to LOW (BD mode), the under-voltage threshold is 7.5 V typical. When MODE\_SEL pin is set to HIGH or floating, the TPA3138D2 operates in 1SPW mode, and the under-voltage threshold is 3.4 V typical.

The device recovers automatically once the under-voltage condition has been removed.

#### 9.4 Device Functional Modes

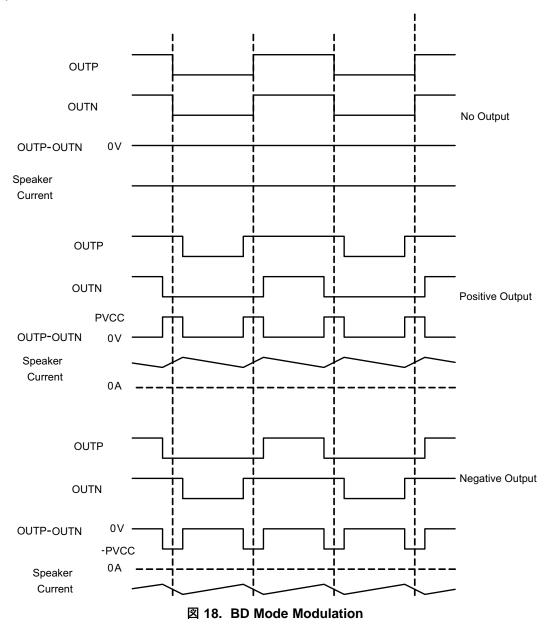

### 9.4.1 MODE SEL = LOW: BD Modulation

This is a modulation scheme that allows operation without the classic LC reconstruction filter when the amp is driving an inductive load with short speaker wires. Each output is switching from 0 volts to the supply voltage. The OUTPx and OUTNx are in phase with each other with no input so that there is little or no current in the speaker. The duty cycle of OUTPx is greater than 50% and OUTNx is less than 50% for positive output voltages. The duty cycle of OUTPx is less than 50% and OUTNx is greater than 50% for negative output voltages. The voltage across the load sits at 0 V throughout most of the switching period, reducing the switching current, which reduces any I<sup>2</sup>R losses in the load.

## **Device Functional Modes (continued)**

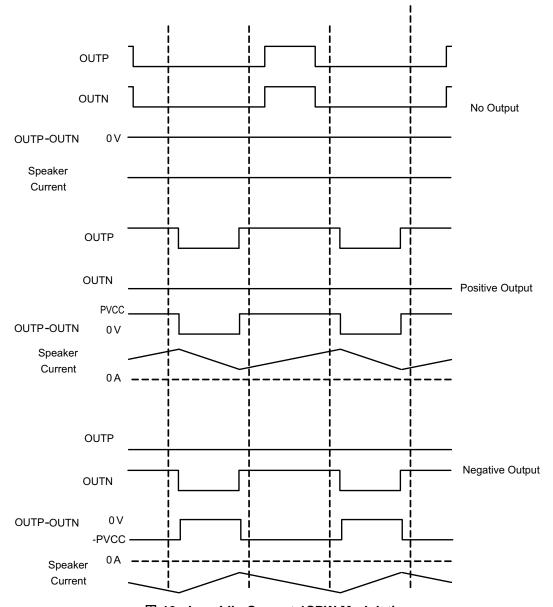

#### 9.4.2 MODE\_SEL = HIGH: Low-Idle-Current 1SPW Modulation

The 1SPW mode alters the normal modulation scheme in order to achieve higher efficiency with a slight penalty in THD degradation and more attention required in the output filter selection. In 1SPW mode the outputs operate at ~15% modulation during idle conditions. When an audio signal is applied one output decreases and the other output increases. The decreasing output signal rails to GND. At which point all the audio modulation takes place through the rising output. The result is that only one output is switching during a majority of the audio cycle. Efficiency is improved in this mode due to the reduction of switching losses.

図 19. Low-Idle-Current 1SPW Modulation

## 10 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 10.1 Application Information

The TPA3138D2 device is designed for use in inductor-free applications with limited distance wire length between amplifier and speakers, suitable for applications such as TV sets, sound docks and Bluetooth speakers. The TPA3138D2 device can either be configured in stereo or mono mode. Depending on the output power requirements and necessity for (speaker) load protection, the built-in PLIMIT circuit can be used to control the system power, see functional description of these features.

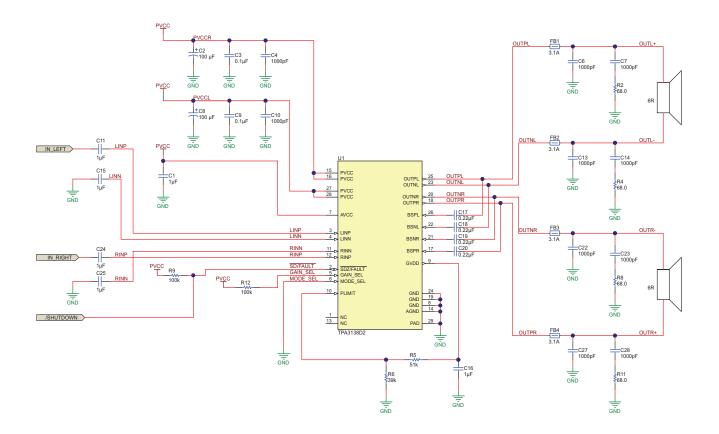

### 10.2 Typical Applications

図 20. Stereo Class-D Amplifier in BTL Configuration with Single-Ended Inputs, Spread Spectrum Modulation and BD Mode

図 21. Stereo Class-D Amplifier in PBTL Configuration with Single-Ended Input, Spread Spectrum Modulation and 1SPW Mode

### 10.2.1 Design Requirements

### 10.2.1.1 PCB Material Recommendation

FR-4 Glass Epoxy material with 1 oz. (35  $\mu$ m) is recommended for use with the TPA3138D2. The use of this material can provide higher power output, improved thermal performance, and better EMI margin (due to lower PCB trace inductance). It is recommended to use several GND underneath the device thermal pad for thermal coupling to a bottom-side copper GND plane for best thermal performance.

#### 10.2.1.2 PVCC Capacitor Recommendation

The large capacitors used in conjunction with each full-bridge, are referred to as the PVCC capacitors. These capacitors should be selected for proper voltage margin and adequate capacitance to support the power requirements. In practice, with a well designed system power supply, a capacitor with 100  $\mu$ F and 16 V supports most applications with 12-V power supply. 25-V capacitor rating is recommended for power supply voltage higher than 12 V. For The PVCC capacitors should be low ESR type because they are used in a circuit associated with high-speed switching.

#### 10.2.1.3 Decoupling Capacitor Recommendations

In order to design an amplifier that has robust performance, passes regulatory requirements, and exhibits good audio performance, good quality decoupling capacitors should be used. In practice, X7R should be used in this application.

The voltage of the decoupling capacitors should be selected in accordance with good design practices. Temperature, ripple current, and voltage overshoot must be considered. This fact is particularly true in the selection of the ceramic capacitors that are placed on the power supply to each full-bridge. They must withstand the voltage overshoot of the PWM switching, the heat generated by the amplifier during high power output, and the ripple current created by high power output. A minimum voltage rating of 16 V is required for use with a 12-V power supply.

## 10.2.2 Detailed Design Procedure

A rising-edge transition on SD/FAULT input allows the device to start switching. It is recommended to ramp the PVCC voltage to its desired value before releasing SD/FAULT for minimum audible artifacts.

The device is not inverting the audio signal from input to output.

The GVDD pin is not recommended to be used as a voltage source for external circuitry.

#### 10.2.2.1 Ferrite Bead Filter Considerations

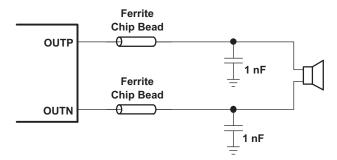

With Advanced Emissions Suppression Technology, the TPA3138D2 amplifier delivers high-efficiency Class-D performance while minimizing interference to surrounding circuits, even with a low-cost ferrite bead filter. But couple factors need to be taken into considerations when selecting the ferrite beads.

One important aspect of the ferrite bead selection is the type of material used in the ferrite bead. Not all ferrite material is alike, so it is important to select a material that is effective in the 10 to 100 MHz range which is key to the operation of the Class-D amplifier. Many of the specifications regulating consumer electronics have emissions limits as low as 30 MHz. It is important to use the ferrite bead filter to block radiation in the 30-MHz and above range from appearing on the speaker wires and the power supply lines which are good antennas for these signals. The impedance of the ferrite bead can be used along with a small capacitor with a value in the range of 1000 pF to reduce the frequency spectrum of the signal to an acceptable level. For best performance, the resonant frequency of the ferrite bead and capacitor filter should be less than 10 MHz.

Also, it is important that the ferrite bead is large enough to maintain its impedance at the peak currents expected for the amplifier. Some ferrite bead manufacturers specify the bead impedance at a variety of current levels. If it is possible, make sure the ferrite bead maintains an adequate amount of impedance at the peak current that the amplifier detects. If these specifications are not available, it is possible to estimate the bead's current handling capability by measuring the resonant frequency of the filter output at low power and at maximum power. A change of resonant frequency of less than fifty percent under this condition is desirable. Examples of ferrite beads which have been tested and work well with the TPA3138D2 device include NFZ2MSM series from Murata.

A high-quality ceramic capacitor is also required for the ferrite bead filter. A low ESR capacitor with good temperature and voltage characteristics works best.

Additional EMC improvements may be obtained by adding snubber networks from each of the class-D outputs to ground. Suggested values for a simple RC series snubber network would be  $68~\Omega$  in series with a 100-pF capacitor although design of the snubber network is specific to every application and must be designed taking into account the parasitic reactance of the printed circuit board as well as the audio amp. Take care to evaluate the stress on the component in the snubber network especially if the amp is running at high PVCC. Also, make sure the layout of the snubber network is tight and returns directly to the GND or the thermal pad beneath the chip.

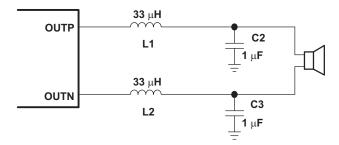

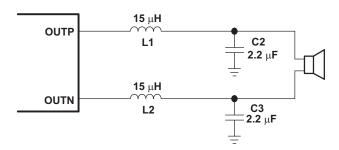

#### 10.2.2.2 Efficiency: LC Filter Required with the Traditional Class-D Modulation Scheme

The main reason that the traditional class-D amplifier requires an output filter is that the switching waveform results in maximum current flow. This causes more loss in the load, which causes lower efficiency. The ripple current is large for the traditional modulation scheme, because the ripple current is proportional to voltage multiplied by the time at that voltage. The differential voltage swing is  $2 \times V_{CC}$ , and the time at each voltage is half the period for the traditional modulation scheme. An ideal LC filter is required to store the ripple current from each half cycle for the next half cycle, while any resistance causes power dissipation. The speaker is both resistive and reactive, whereas an LC filter is almost purely reactive.

The TPA3138D2 modulation scheme has little loss in the load without a filter because the pulses are short and the change in voltage is  $V_{CC}$  instead of 2 ×  $V_{CC}$ . As the output power increases, the pulses widen, making the ripple current larger. Ripple current could be filtered with an LC filter for increased efficiency, but for most applications the filter is not required.

An LC filter with a cutoff frequency less than the class-D switching frequency allows the switching current to flow through the filter instead of the load. The filter has less resistance but higher impedance at the switching frequency than the speaker, which results in less power dissipation, therefore increasing efficiency.

#### 10.2.2.3 When to Use an Output Filter for EMI Suppression

The TPA3138D2 device has been tested with a simple ferrite bead filter for a variety of applications including long speaker wires up to 100 cm and high power. The TPA3138D2 EVM passes FCC Class B specifications under these conditions using twisted speaker wires. The size and type of ferrite bead can be selected to meet application requirements. Also, the filter capacitor can be increased if necessary with some impact on efficiency.

There may be a few circuit instances where it is necessary to add a complete LC reconstruction filter. These circumstances might occur if there are nearby circuits which are sensitive to noise. In these cases a classic second order Butterworth filter similar to those shown in the figures below can be used.

Some systems have little power supply decoupling from the AC line but are also subject to line conducted interference (LCI) regulations. These include systems powered by "wall warts" and "power bricks." In these cases, LC reconstruction filters can be the lowest cost means to pass LCI tests. Common mode chokes using low frequency ferrite material can also be effective at preventing line conducted interference.

図 22. Typical Ferrite Chip Bead Filter (Chip Bead Example: NFZ2MSM series from Murata)

$\boxtimes$  23. Typical LC Output Filter, Cutoff Frequency of 27 kHz, Speaker Impedance = 8  $\Omega$

24. Typical LC Output Filter, Cutoff Frequency of 27 kHz, Speaker Impedance = 6 Ω

#### 10.2.2.4 Input Resistance

The typical input resistance of the amplifier is fixed to 20 k $\Omega$  ±15% for 26dB Gain and 40k $\Omega$  ±15% for 20dB Gain .

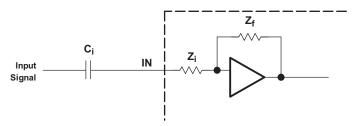

#### 10.2.2.5 Input Capacitor, Ci

In the typical application, an input capacitor  $(C_i)$  is required to allow the amplifier to bias the input signal to the proper dc level for optimum operation. In this case,  $C_i$  and the input impedance of the amplifier  $(Z_i)$  form a high-pass filter with the corner frequency determined in  $\vec{x}$  2.

$$f_{c} = \frac{1}{2\pi Z_{i} C_{i}}$$

(2)

The value of  $C_i$  is important, as it directly affects the bass (low-frequency) performance of the circuit. Consider the example where  $Z_i$  is 20 k $\Omega$  (26dB Gain) and the specification calls for a flat bass response down to 20 Hz.  $\vec{\pm}$  2 is reconfigured as  $\vec{\pm}$  3.

$$C_{i} = \frac{1}{2\pi Z_{i} f_{c}} \tag{3}$$

In this example,  $C_i$  is 0.4  $\mu$ F; so, one would likely choose a value of 0.39  $\mu$ F as this value is commonly used. A further consideration for this capacitor is the leakage path from the input source through the input network ( $C_i$ ) and the feedback network to the load. This leakage current creates a dc offset voltage at the input to the amplifier that reduces useful headroom. For this reason, a low-leakage tantalum or ceramic capacitor is the best choice. When polarized capacitors are used, the positive side of the capacitor should face the amplifier input in most applications as the dc level there is held at 3 V, which is likely higher than the source dc level. Note that it is important to confirm the capacitor polarity in the application. Additionally, lead-free solder can create dc offset voltages and it is important to ensure that boards are cleaned properly.

#### 10.2.2.6 BSN and BSP Capacitors

The full H-bridge output stages use only NMOS transistors. Therefore, they require bootstrap capacitors for the high side of each output to turn on correctly. A 0.22- $\mu$ F ceramic capacitor, rated for at least 25 V, must be connected from each output to its corresponding bootstrap input. Specifically, one 0.22- $\mu$ F capacitor must be connected from OUTPx to BSPx, and one 0.22- $\mu$ F capacitor must be connected from OUTNx to BSNx. (See the application circuit diagram in 20.)

The bootstrap capacitors connected between the BSxx pins and corresponding output function as a floating power supply for the high-side N-channel power MOSFET gate drive circuitry. During each high-side switching cycle, the bootstrap capacitors hold the gate-to-source voltage high enough to keep the high-side MOSFETs turned on.

## 10.2.2.7 Differential Inputs

The differential input stage of the amplifier cancels any noise that appears on both input lines of the channel. To use the TPA3138D2 device with a differential source, connect the positive lead of the audio source to the INP input and the negative lead from the audio source to the INN input. To use the TPA3138D2 with a single-ended source, ac ground the INP or INN input through a capacitor equal in value to the input capacitor on INN or INP and apply the audio source to either input. In a single-ended input application, the unused input should be ac grounded at the audio source instead of at the device input for best noise performance. For good transient performance, the impedance seen at each of the two differential inputs should be the same.

The impedance seen at the inputs should be limited to an RC time constant of 3 ms or less if possible. This is to allow the input dc blocking capacitors to become completely charged during the 50-ms power-up time. If the input capacitors are not allowed to completely charge, there is some additional sensitivity to component matching which can result in pop if the input components are not well matched.

### 10.2.2.8 Using Low-ESR Capacitors

Low-ESR capacitors are recommended throughout this application section. A real (as opposed to ideal) capacitor can be modeled simply as a resistor in series with an ideal capacitor. The voltage drop across this resistor minimizes the beneficial effects of the capacitor in the circuit. The lower the equivalent value of this resistance, the more the real capacitor behaves like an ideal capacitor.

## 10.2.3 Application Performance Curves

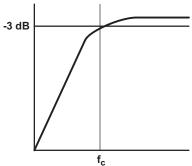

#### 10.2.3.1 EN55013 Radiated Emissions Results

TPA3138D2 EVM, PVCC = 12 V,  $8-\Omega$  speakers,  $P_O$  = 4 W

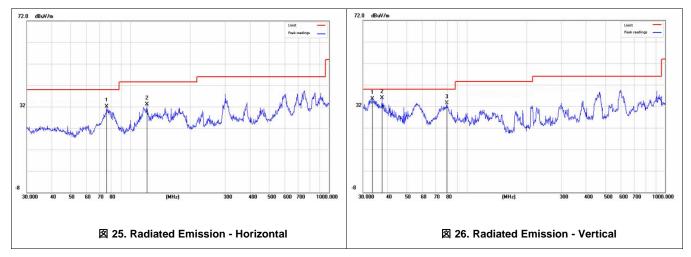

## 10.2.3.2 EN55022 Conducted Emissions Results

TPA3138D2 EVM, PVCC = 12 V, 8- $\Omega$  speakers, P<sub>O</sub> = 4 W

## 11 Power Supply Recommendations

### 11.1 Power Supply Decoupling, C<sub>s</sub>

The TPA3138D2 device is a high-performance CMOS audio amplifier that requires adequate power supply decoupling to ensure that the output total harmonic distortion (THD) is as low as possible. Power supply decoupling also prevents oscillations for long lead lengths between the amplifier and the speaker. Optimum decoupling is achieved by using a network of capacitors of different types that target specific types of noise on the power supply leads. For higher frequency transients due to parasitic circuit elements such as bond wire and copper trace inductances as well as lead frame capacitance, a good quality low equivalent-series-resistance (ESR) ceramic capacitor of value between 220 pF and 1000 pF works well. This capacitor should be placed as close to the device PVCC pins and system ground (either GND pins or thermal pad) as possible. For midfrequency noise due to filter resonances or PWM switching transients as well as digital hash on the line, another good quality capacitor typically 0.1 μF to 1 μF placed as close as possible to the device PVCC leads works best. For filtering lower frequency noise signals, a larger aluminum electrolytic capacitor of 100 μF or greater placed near the audio power amplifier is recommended. The 100-μF capacitor also serves as a local storage capacitor for supplying current during large signal transients on the amplifier outputs. The PVCC pins provide the power to the output transistors, so a 100-uF or larger capacitor should be placed on each PVCC pin. A 1-uF capacitor on the AVCC pin is adequate. Also, a small decoupling resistor between AVCC and PVCC can be used to keep high frequency class-D noise from entering the linear input amplifiers.

## 12 Layout

#### 12.1 Layout Guidelines

The TPA3138D2 device can be used with a small, inexpensive ferrite bead output filter for most applications. However, since the Class-D switching edges are fast, it is necessary to take care when planning the layout of the printed circuit board. The following suggestions help meet EMC requirements.

- Decoupling capacitors—The high-frequency decoupling capacitors should be placed as close to the PVCC and AVCC pins as possible. Large (100-μF or greater) bulk power supply decoupling capacitors should be placed near the TPA3138D2 device on the PVCC supplies. Local, high-frequency bypass capacitors should be placed as close to the PVCC pins as possible. These caps can be connected to the thermal pad directly for an excellent ground connection. Consider adding a small, good quality low ESR ceramic capacitor between 220 pF and 1000 pF and a larger mid-frequency cap of value between 0.1 μF and 1 μF also of good quality to the PVCC connections at each end of the chip.

- Keep the current loop from each of the outputs through the ferrite bead and the small filter cap and back to GND as small and tight as possible. The size of this current loop determines its effectiveness as an antenna.

- Grounding—The AVCC (pin 7) decoupling capacitor should be connected to ground (GND). The PVCC decoupling capacitors should connect to GND. Analog ground and power ground should be connected at the thermal pad, which should be used as a central ground connection or star ground for the TPA3138D2.

- Output filter—The ferrite EMI filter (22) should be placed as close to the output pins as possible for the best EMI performance. The capacitors used in the ferrite should be grounded to power ground.

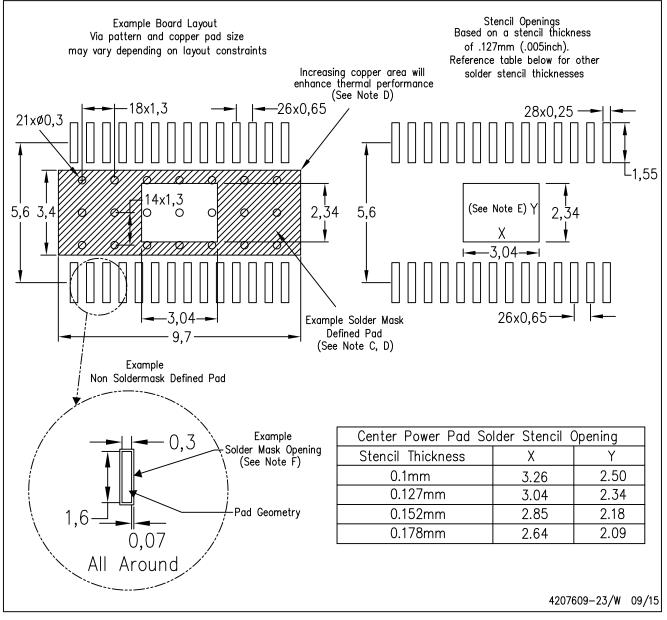

- Thermal Pad—The thermal pad must be soldered to the PCB for proper thermal performance and optimal reliability. The dimensions of the thermal pad and thermal land should be 3.04 mm x 2.34 mm. Seven rows of solid vias (three vias per row, 0.3302 mm or 13 mils diameter) should be equally spaced underneath the thermal land. The vias should connect to a solid copper plane, either on an internal layer or on the bottom layer of the PCB. The vias must be solid vias, not thermal relief or webbed vias. See the TI Application Report SLMA002 for more information about using the TSSOP thermal pad. For recommended PCB footprints, see figures at the end of this data sheet.

For an example layout, see the TPA3138D2 Evaluation Module (TPA3138D2EVM) User Manual. Both the EVM user manual and the thermal pad application report are available on the TI Web site at http://www.ti.com.

## 12.2 Layout Example

図 29. BTL Layout Example

Bot Layer layout view

## 13 デバイスおよびドキュメントのサポート

#### 13.1 デバイス・サポート

#### 13.1.1 デベロッパー・ネットワークの製品に関する免責事項

デベロッパー・ネットワークの製品またはサービスに関するTIの出版物は、単独またはTIの製品、サービスと一緒に提供さ れる場合に関係なく、デベロッパー・ネットワークの製品またはサービスの適合性に関する是認、デベロッパー・ネットワーク の製品またはサービスの是認の表明を意味するものではありません。

### 13.2 ドキュメントのサポート

#### 13.2.1 関連資料

『熱特性強化型パッケージPowerPAD™』アプリケーション・レポート(SLMA002)

#### 13.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.comのデバイス製品フォルダを開いてください。右上の隅にある「通 知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の 詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

### 13.4 コミュニティ・リソース

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™オンライン・コミュニティ *TIのE2E(Engineer-to-Engineer)コミュニティ。*エンジニア間の共同作業を促進するために開設されたものです。e2e.ti.comでは、他のエンジニアに質問し、知識を共有 し、アイディアを検討して、問題解決に役立てることができます。

設計サポート *TIの設計サポート* 役に立つE2Eフォーラムや、設計サポート・ツールをすばやく見つけることが できます。技術サポート用の連絡先情報も参照できます。

#### 13.5 商標

E2E is a trademark of Texas Instruments.

Bluetooth is a registered trademark of Bluetooth SIG, Inc.

All other trademarks are the property of their respective owners.

## 13.6 静電気放電に関する注意事項

これらのデバイスは、限定的なESD(静電破壊)保護機能を内 蔵しています。保存時または取り扱い時は、MOSゲートに対す る静電破壊を防 ▲ 上するために、リード線同士をショートさせておくか、デバイスを導電フォームに入れる必要があります。

## 13.7 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 14 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、そのデバイスに ついて利用可能な最新のデータです。このデータは予告なく変更されることがあり、ドキュメントが改訂される場合もありま す。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

## PACKAGE OPTION ADDENDUM

10-Dec-2020

#### **PACKAGING INFORMATION**

www.ti.com

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| TPA3138D2PWP     | ACTIVE     | HTSSOP       | PWP                | 28   | 50             | RoHS & Green | NIPDAU                        | Level-3-260C-168 HR | -40 to 85    | TPA3138D2               | Samples |

| TPA3138D2PWPR    | ACTIVE     | HTSSOP       | PWP                | 28   | 2000           | RoHS & Green | NIPDAU                        | Level-3-260C-168 HR | -40 to 85    | TPA3138D2               | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

10-Dec-2020

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 5-Dec-2023

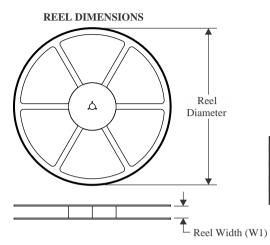

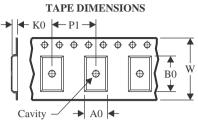

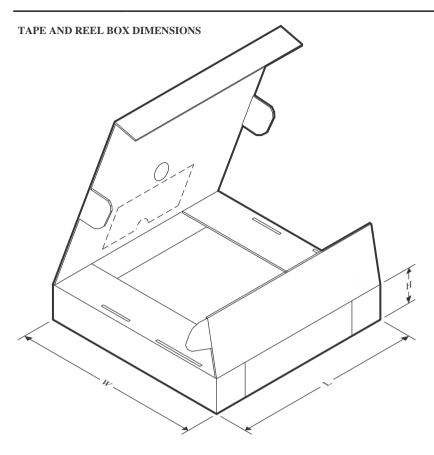

## TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPA3138D2PWPR | HTSSOP          | PWP                | 28 | 2000 | 330.0                    | 16.4                     | 6.9        | 10.2       | 1.8        | 12.0       | 16.0      | Q1               |

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 5-Dec-2023

### \*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| TPA3138D2PWPR | HTSSOP       | PWP             | 28   | 2000 | 350.0       | 350.0      | 43.0        |  |

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 5-Dec-2023

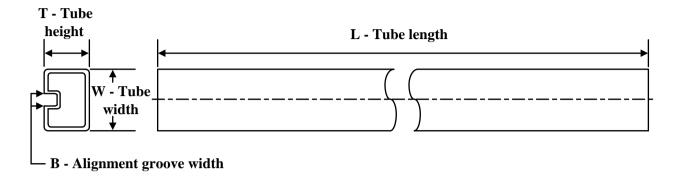

## **TUBE**

#### \*All dimensions are nominal

| Device       | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|--------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| TPA3138D2PWP | PWP          | HTSSOP       | 28   | 50  | 530    | 10.2   | 3600   | 3.5    |

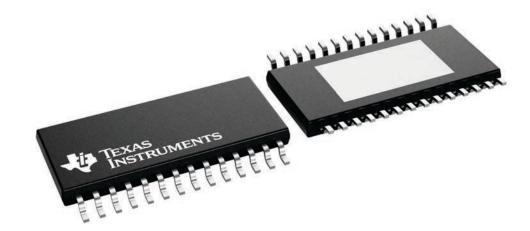

4.4 x 9.7, 0.65 mm pitch

SMALL OUTLINE PACKAGE

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

PWP (R-PDSO-G28)

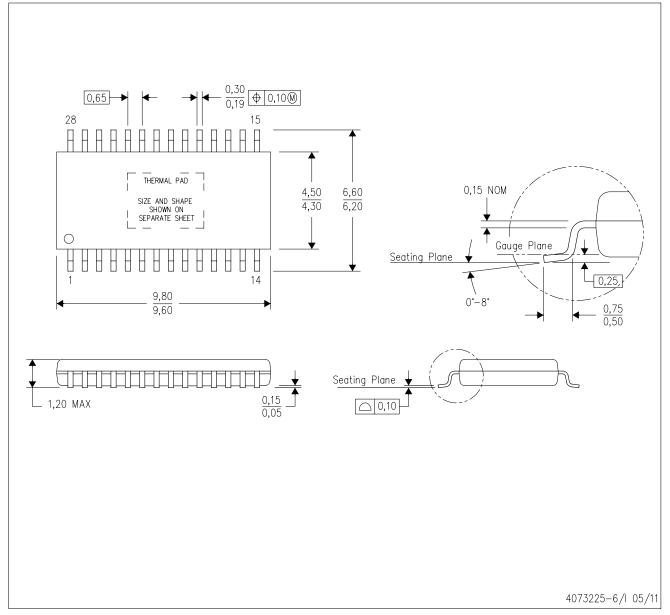

## PowerPAD™ PLASTIC SMALL OUTLINE

NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">www.ti.com</a>.

E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

# PWP (R-PDSO-G28) PowerPAD™ SMALL PLASTIC OUTLINE

#### THERMAL INFORMATION

This PowerPAD<sup>TM</sup> package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Top View

Exposed Thermal Pad Dimensions

4206332-39/AO 01/16

NOTE: A. All linear dimensions are in millimeters

Exposed tie strap features may not be present.

PowerPAD is a trademark of Texas Instruments

## PWP (R-PDSO-G28)

## PowerPAD™ PLASTIC SMALL OUTLINE

#### NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

- F. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、TI の販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated