# LVDS Application and Data Handbook

# High-Performance Linear Products Technical Staff

Literature Number: JAJD001 WAS SLLD010 November 2004

#### 目 次

| 第1章 データ伝送の基礎                                            | 1-1 |

|---------------------------------------------------------|-----|

| 伝送ラインとその特性                                              | 1-2 |

| シングルエンド対差動                                              | 1-3 |

| ポイント・ツー・ポイント、マルチドロップ、およびマルチポイント・バス                      | 1-5 |

| 規格化の利点                                                  | 1-6 |

| 644対644a対LVDM対M-LVDS                                    | 1-7 |

| LVDS/M-LVDSの要約                                          |     |

| ### 11/20 to 14/21 11/20 0 = 45 . = 45 d = 64t to 14t = |     |

| 第2章 LVDSおよびM-LVDSのライン・デバイスの特性と特長                        |     |

| ドライバ出力電圧                                                |     |

| 差動入力電圧スレッシュホールド                                         |     |

| 同相入力電圧範囲                                                |     |

| 信号レート                                                   |     |

| 電力消費                                                    |     |

| 電源電圧                                                    |     |

| 信頼性                                                     |     |

| 内蔵終端抵抗                                                  |     |

| フォールトトレランスとフェィルセーフ                                      |     |

| 活線挿抜(ホットプラグ)                                            | 2-9 |

|                                                         |     |

|                                                         |     |

| 図1-1. 各種インターフェイスのおよその信号レート対伝送距離                         |     |

| 図1-2. イニシャル波の回路モデル                                      |     |

| 図1-3. ラインと負荷の境界                                         |     |

| 図1-4. 反射波の例                                             |     |

| 図1-5. シングルエンドのインターフェイス回路構成図                             |     |

| 図1-6. 差動インターフェイス回路構成図                                   |     |

| 図1-7. ポイント・ツー・ポイントのデータ・インターチェンジ回路                       |     |

| 図1-8. マルチドロップのデータ・インターチェンジ回路                            |     |

| 図1-9. マルチポイントのデータ・インターチェンジ回路                            |     |

| 図1-10. TIA/EIA-644ドライバ出力試験回路                            |     |

| 図1-11. TIA/EIA-644-Aドライバ出力試験回路                          |     |

| 図1-12. 差動信号の負荷電力の比較                                     |     |

| 図1-13. TIA/EIA規格の電圧範囲                                   | 1-9 |

| 図2-1. V <sub>OD</sub> の定義                               | 2-1 |

| 図2-2. ドライバ同相出力電圧の測定用回路                                  | 2-1 |

| 図2-3. LVDSおよびM-LVDS差動入力信号スレッシュホールド                      |     |

| 図2-4. 差動ライン·レシーバの同相除去試験                                 |     |

| 図2-5. TIA/EIA-644-A信号品質推奨条件                             |     |

| 図2-6. MC100LVEP111とSN65LVDS116の電力比較                     | _   |

| 図2-6. MC100LVEP111とSN65LVDS116の電力比較                     | _   |

| 図2-8. 電圧モードおよび電流モード・ドライバの、正規化電力対スピードの比較                 |     |

| 図2-9. パワーアップ/ダウン時の波形                                    |     |

| 表                                                       |     |

|                                                         |     |

| 表2-1. 差動信号規格のノイズ電圧許容度                                   | 2-4 |

## 第1章 データ伝送の基礎

データ伝送とは、その名の示す通り、データをある場所から別の場所へ移す手段のことです。それを実現する最適の伝送方式を選択するには、多くのシステム・パラメータを評価する必要があります。ここで最初に考慮すべき2つの事項は、「どれだけ速く?」と「どこまで遠く?」です。「どれだけ速く?」とは、信号レートすなわち1秒あたりに伝送されるビット数になります。

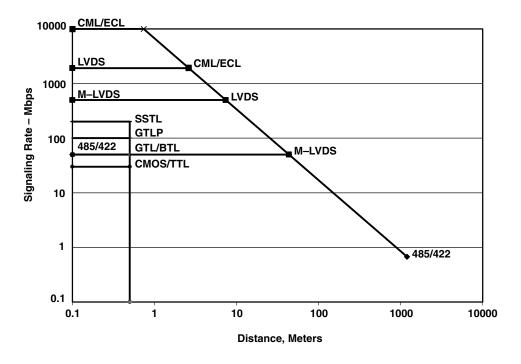

「どこまで遠く?」とは、データの送り手と受け手間の物理的な距離に関することです。この2つの主要なシステム・パラメータに関して考察すると、考えられるソリューションをかなり絞り込めるのが通例です。図1-1は、よく知られたいくつかのデータ伝送方式の速度と距離範囲について示します。

図1-1. 各種インターフェイスのおよその信号レート対伝送距離

図1-1で分かるように、伝送距離が増加するにつれて信号レートは低下していきます。最長の伝送距離においては定常状態損失が重要な要素になります。その一方で、距離が増加するにつれて、信号レートを制限する主要な要因は時間的な変化になります。ケーブル帯域の限界は信号の遷移時間を劣化させ、インターシンボル干渉(ISI)を引き起こし、伝送距離が増加した場合の最大信号レートを低下させる主要な要因になります。

また、図1-1は次のことも示しています。すなわち、伝送距離が短く(< 0.5m)信号レートが中程度の場合、バックプレーン・トランシーバ・ロジック(BTL IEEE1194.1)、ガンニング・トランシーバ・ロジック(GTL)、およびガンニング・トランシーバ・ロジック・プラス(GTLP)を含む汎用のシングルエンド・ロジックは、インターフェイスに十分なソリューションを提供できます。伝送距離がそれより増加すると、より高い電圧振幅や差動信号の方式がデータを転送します。

約30メートル以上かつ50Mbps以下のデータ伝送が必要な場合、差動信号方式のTIA/EIA-422およびTIA/EIA-485を検討すべきです。これらのインターフェイスは、高差動出力、高感度レシーバ、および最大7Vのグランド・ノイズまで動作する能力のため、装置間を長距離で直結するのに最適です。TIA/EIA-422およびTIA/EIA-485は近い値の電圧を使用しますが、それらがサポートできるバス構成は異なります。TIA/EIA-422はマルチドロップ(1ドライバと多数のレシーバ)動作に使用され、TIA/EIA-485はマルチポイント伝送(多くのドライバおよびレシーバ)が可能です。

50Mbpsより高い信号レートや低消費電力アプリケーションには、低電圧差動信号方式(LVDS)あるいはマルチポイント低電圧差動信号方式(M-LVDS)が魅力的なソリューションを提供します。1996年に導入され、TIA/EIA-644で規定されるLVDSは、ポイント・ツー・ポイントあるいはマルチドロップのバス方式において高信号レートと低消費電力を実現します。TIA/EIA-899で規定されるM-LVDSは2002年に導入され、マルチポイントのアプリケーションに上記と同様の利点を提供します。LVDSとM-LVDSに関する上記の利点、優れた特長、およびアプリケーションが本ハンドブックの主題です。

信号レート条件がLVDSの能力を超える場合、電流モード・ロジック(CML)すなわちエミッタ・カップルド・ロジック(ECL)およびポジティブECL(PECL)の両ファミリが主に使用されます。ECL/PECLデバイスは10Gbpsの信号レートも可能です。この高速性は大消費電力という犠牲のもとに実現されます。

#### 伝送ラインとその特性

LVDSの出力電圧は一方のロジック状態から他方へ260psでスイッチできるので、ほとんどのアプリケーションにおいて、そのインターフェイスは分布定数回路としてモデル化しなければなりません。このモデルは、大部分のユーザが解析に苦労するものです。しかし幸運なことに、ほとんどのアプリケーションのユーザは伝送ラインモデルを相互接続に適用できます。多くの文献が伝送ラインの特性と数式について解いていますので、ここではその要約だけを示します。

伝送ラインモデルをLVDSデバイス間の相互接続に適用するには、満たすべき2条件が必要になります。

1. 相互接続する回路の物理的寸法が信号の最短波長(最高周波数)に比較して長いこと。バイナリ信号の最高周波数成分は、ロジック状態間を遷移する電圧(あるいは電流)で決まります。そのため、立ち上がり・立ち下がり時間がドライバ出力電圧の重要パラメータになります。なぜなら、回路内で最も高速な信号変化がこのポイントで生じるからです。相互接続する回路の遅延時間が信号の10%-90%遷移時間の3倍以上であれば、一般にその回路は伝送ラインとしてモデル化するのに十分長いと言えます。

2. 導線の寸法すなわち、信号線と帰線間の距離およびその周辺の絶縁体が一定であること。伝送ラインによる解法は、伝送路に沿った各微小部分が電気的に等しく、かつ微小部分をゼロに収束させたモデルに基づいています。伝送路に沿った物理的特性に不連続性があれば、多伝送ラインモデルあるいは分布定数による解法が必要になります。

上の2条件によって、分布容量(単位長あたり)Cと分布インダクタンスLによって特性が決まる理想伝送ラインとして相互接続をモデル化できます。下記の特性には優れた近似結果が得られています。

- 理想伝送ラインには特性インピーダンスがあり、ライン上のあらゆる点における電圧と電流は、 $Z_0 = v/i$ で関係づけられます。特性インピーダンスは実数(抵抗)であり、 $R_0 = \sqrt{LC}\Omega$ です。

- 理想伝送ラインの単位長あたりの遅延時間は一定であり、 $v_0 = \sqrt{LC} \Omega$  秒/長の値になります。

- 理想伝送ラインは無損失であり、ラインに沿って入力信 号の減衰がありません。

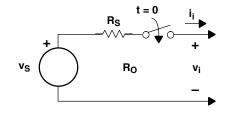

ラインドライバが出力状態を変えると、イニシャル(最初の) 電圧波が伝送ラインに発されます。このとき、ドライバ出力特性と伝送ラインの特性インピーダンスが、電圧および電流波形を決定します(図1-2参照)。

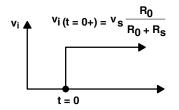

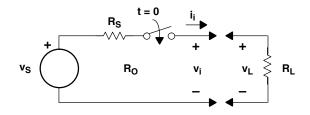

理想伝送ラインモデルでは、イニシャル波は無限に伝播し続けようとします。しかし、実際の回路には終端があるため、イニシャル波は負荷抵抗  $R_L$ に出会います(図1-3参照)。この点において存在する全信号電力は、しばらく前に入力された電力に等しく、 $P_i = v_i^2/R_0$ になります。負荷における電力は $P_L = v_i^2/R_0$ であり、エネルギーは一定のはずですから、 $v_i^2/R_0 = v_i^2/R_0$ と思うかもしれません。しかし、 $R_0$ が $R_L$ より大きく、かつ入力電圧と負荷にかかる電圧が等しいとすると、負荷にはラインに入力された以上の電力があることになります。しかし、エネルギー不変の法則からそれはあり得ず、電力の一定性のゆえに $v_i^2/R_0 = v_i^2/R_L + v_i^2/R_0$ のように欠けていた項があることを意味します。ここで、 $v_i^2/R_0$ は負荷によって吸収されない電力であり、伝送ラインに反射されます。

図1-2. イニシャル波の回路モデル

1ソリューションの1つとして文献4を参照願います。

図1-3. ラインと負荷の境界

わずかな代数的処理により、エネルギー的平衡を維持するのに必要な $v_r$ と $v_i$ の比を表すと、 $\frac{v_r}{v_i} = \frac{R_L - R_O}{R_L + R_O}$  になります。これは負荷の電圧反射係数と定義され、しばしば $\rho_{v_L}$ と記されます。

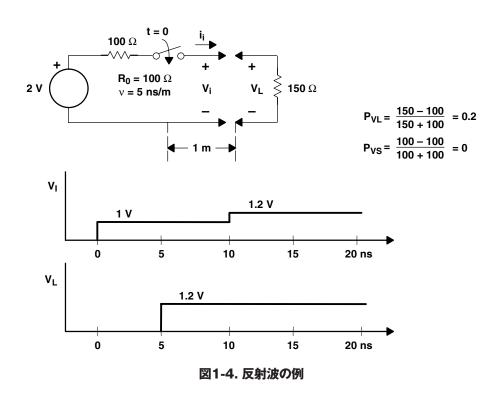

**例**: 図1-4は、150 $\Omega$ で終端した1mのケーブルを出力抵抗100 $\Omega$ の 2V信号源でドライブする例です。t=0において、1ボルトのイニシャル電圧波が信号源で発生しています。これは信号源と伝送ラインの特性インピーダンスの100 $\Omega$ で2Vを分圧したものです。この電圧波はケーブルを5ns/mで伝播し、150 $\Omega$ の負荷抵抗に到達します。その瞬間、 $v_r=v_i\times \rho_{vL}=0.2$ Vの反射が発生します。反射電圧は $v_i$ に加わり、 $R_L$ の両端の電圧は $v_i+v_r=v_i$ (1+ $\rho_{vL}$ )=1.2Vになります。反射波は信号源に向かって戻り、信号源では反射係数が0と書いてあるので、100 $\Omega$ の信号源抵抗がすべての信号電力を吸収します。

伝送ラインが理想的で無損失ならば、どれほどケーブルが長くても制限が無く、入力信号を回復できることになります。しかし、図1-1に示すように、ケーブル長が増加するにつれて最大信号レートは低下します。これは、理想伝送ラインモデルには含まれない2次効果に起因します。表皮、近接、誘電損失、および放散損失の各効果は、すべてラインの主要なパラメータに影響し、信号を劣化させます。これらの効果については実験的に評価するのが最善であり、本文献のアプリケーションの章でそのガイドラインを述べています。

#### シングルエンド対差動

先に、シングルエンド方式データ伝送(BTL、GTL、GTLP、TIA/EIA-232などで採用)と差動方式データ伝送(TIA/EIA-422、TIA/EIA-485、TIA/EIA-644(LVDS)などで使用)について述べました。これらの伝送方式には長所と短所があります。

#### シングルエンド方式データ伝送

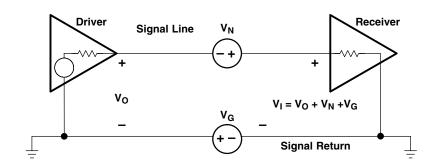

シングルエンド伝送は、情報チャネルごとに1本の信号ライン、および多数の情報チャネル用に1本の共通グランド帰線を使用しています。図1-5はシングルエンド伝送システムの電気的構成図を示します。シングルエンド・レシーバは、その入力におけるグランドを基準にしたシングル入力ライン電圧により、ロジック状態を判定します。

シングルエンド伝送の長所は、その単純さと導入費用の安さです。シングルエンドのシステムは、1信号あたり1ラインだけが必要になります。それゆえ、ケーブルとコネクタの費用が信号レートや伝送距離よりも重要な場合に理想的です。このトレードオフは、パラレル・プリンタ・ポートや多くのハンドシェーク・

ラインのあるシリアル・コミュニケーションのような、低速PC アプリケーションで見られます。

シングルエンド伝送の主な短所は、高信号レートあるいは長伝送距離の場合に比較的ノイズ特性が弱いことです。なぜなら、回路に結合したノイズが信号電圧に加わり、それがデータ・エラーになりやすいからです。シングルエンド回路の信号ラインは、電界を輻射および受信するアンテナとして作用します。その一方で、回路周辺に形成された領域は磁界のアンテナになります。図1-5に示す電圧源 $V_N$ は、この高周波電磁界結合を表します。シングルエンドのインターフェイス回路は、一般に他の回路と帰線を共有します。そのため、グランド電流の変化が作り出す $V_G$ で表されるグランド雑音電圧成分もあります。このノイズは一般に低周波(例えば主電源からの60Hz)です。

図1-5. シングルエンドのインターフェイス回路構成図

#### 差動方式データ伝送

差動伝送は各情報チャネルに信号ラインのペア(対)を使用することで、シングルエンド方式の多くの短所に対処しています。図1-6は差動伝送システムの電気的構成図を示します。差動ドライバは相補出力のペアを使用して、伝送すべき状態を出力します。差動レシーバはグランドとの比較ではなく、信号ペア間の電位差を検出して、その出力状態を設定します。

この伝送モードには、シングルエンドと比較していくつかの重要な長所があります。図1-6では、差動入力電圧 $V_{ID}$ に起因する基本的な長所が見られます。ノイズ源の $V_N$ と $V_G$ は、シングルエンド回路の場合と同様に入力信号の $V_{IA}$ と $V_{IB}$ に加わります。しかし、その2入力電圧の差をとると、必要な信号からコモン・ノイズ項が相殺されます。これを差動レシーバは実現するとともに、小さな差動入力電圧スレッシュホールドで大きなSN比を得ています。

図1-6. 差動インターフェイス回路構成図

各信号ラインと結合する $V_N$ は等しいか、ほぼ等しいと推定されます。また、互いに近接した差動信号ペアは一般に同じノイズ源にさらされます。したがって、信号ラインを互いにより線にすると、この長所が活用できます。このようにして、電界への露出を同程度にできます。同時に、より合わせによってできる近傍のループの極性が逆になり、磁界との結合による起電力を相殺できます。

ノイズ耐性に加えて、差動回路が輻射するノイズはシングルエンド回路よりもかなり少なくなります。これは主として、各信号ペアのラインにおける相補電流が、相互に発生した電界を相殺することによります。また、信号帰線を巡回する同相電流が少ないため伝導ノイズも低くなります。

差動信号システムは、コストおよびチップとハードウエア接続上の複雑さが増し、シングルエンド・インターフェイスの場合のおよそ2倍になります。しかし、信号レートと回路数が増加するにつれ、シングルエンド方式を機能させるためにグランド線を追加することに比べれば、この2倍ということは短所でなくなります。したがって、10Mbps以上あるいは0.5mやそれ以上の距離では、差動方式でないデータ・インターフェイスはほとんど見られません。

#### ポイント・ツー・ポイント、マルチドロップ、 およびマルチポイント・バス

それぞれの電気的なインターフェイス設計は異なりますが、インターフェイス問題はいくつかの共通のトポロジーあるいはアーキテクチャーに分類できます。共通の媒体によって物理的に相互接続されたドライバとレシーバの数量がアーキテクチャーを決定し、使用可能なインターフェイス方式を制限し、ライン回路に関する必要条件を与えます。

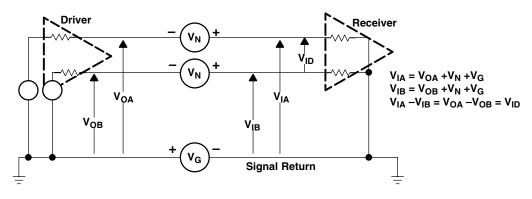

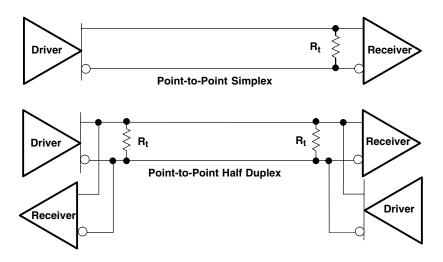

#### ポイント・ツー・ポイント

ポイント・ツー・ポイント・インターフェイスは、2本のみの伝送媒体の接続で構成されます。この構成では、1個のドライバと1個のレシーバによるシンプレックス接続(単方向伝送)、あるいは両端でトランシーバが動作する半2重(双方向伝送)が可能です。ポイント・ツー・ポイント接続は、性能の観点から最適の構成が可能です。ポイント・ツー・ポイント接続は、メインライン上での分岐および他の不連続性がなく、可能な範囲での最高のサンプリングレートが得られます。図1-7は、差動ポイント・ツー・ポイント単方向接続および半2重接続を示します。

図1-7. ポイント・ツー・ポイントのデータ・インターチェンジ回路

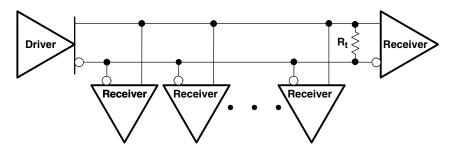

#### マルチドロップ

マルチドロップあるいは分散型単方向ディストリビューション・バスは、次に一般的な相互接続のアプローチです。マルチドロップ・バスは、1個のドライバと複数のレシーバが主伝送ラインで接続している構成です。そのライン終端は、ほとんどの場

合ラインの最遠端にあります。ポイント・ツー・ポイントと同様に、マルチドロップは単方向伝送になります。マルチドロップによる通信は、1個のマスターが複数のスレーブに同じ情報を同時伝達する必要がある場合に一般的です。図1-8は差動マルチドロップ接続を示します。

図1-8. マルチドロップのデータ・インターチェンジ回路

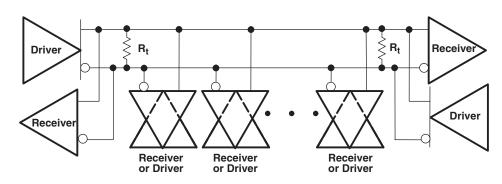

#### マルチポイント

最後に述べるアーキテクチャーはマルチポイント通信です。これはマルチプレックスとも呼ばれます。マルチポイント・バスは、共通伝送ラインに接続する3個以上のステーションあるいはノードで構成され、その中の2ノードが通信を確立します。このライン回路の電気的な必要条件はポイント・ツー・ポイント半2重接続と同じですが、リスン・オンリー、トーク・オンリー、およびトーク・アンド・リスン・ステーションの数の融通がききます。図1-9はマルチポイント接続を示します。

ステーションの物理的な位置によっては、他のシステム・トポロジーも必要です。しかし、伝送ラインモデルを採用したならば、これら3種類の基本的な相互接続およびリピータ(中継器)やコンセントレータ(集中器)を用いて構築し、ひとつの伝送ラインのセグメントに接続するステーション間の電気的パスをクリーンに維持しなければなりません。これらのハイブリッド構造のデータ・フロー処理は複雑であり、本ハンドブックの範囲を超えています。

図1-9. マルチポイントのデータ・インターチェンジ回路

#### 規格化の利点

データ伝送とは、その名の示す通り、データをある場所から別の場所へ移すことです。これを実現するには、送り手と受け手が次の項目に関して合意しなければなりません。すなわち、伝送レートの名目値、情報ービットマップ・パターン、通信プロトコル、およびバスのロジック状態を表すのに使用する電気的状態とパルス・コードです。これら(他にも)の合意は、公式あるいは非公式のいずれかのインターフェイス規格でなされ、階層の深さに関する必要条件を定義します。本ハンドブックはインターフェイスの最下層(電気的特性)についてのみ取り扱います。

規格化は異なる製造業者による装置や部品の相互運用を可能にし、単独の製造業者に依存しないですみます。また、多数の製造業者間の競争を活発にします。複数の納入業者が同一規格のビジネスで競争すると、革新的な設計と生産効率が競争の重要な要素になります。その結果、一層の高品質と入手しやすい低価格の量産品という利点が得られます。

規格化しないと、ねじ、ナット、電球、タイヤ、およびコンピュータ部品のような共通品目が極端に高価になり、その代用品を探し出すのはより困難になります。規格化しない場合のコストアップと代用品探しがどれだけ困難になるか、その単純な例が蛇口のバルブ・ステムです。ローカル・ビルディング・センターや上下水道供給会社には非常に多くの製品があり、まったく同一のものを探すのは高い費用がかかり、しばしばギャンブルでさえあります。

本文書は電気的なインターフェイスの分野について取り扱います。この分野では異なる業者により生産されたシステムが、規格化によって相互運用可能になっています。コンピュータおよび通信の分野は規格に基づいています。民生市場におけるIBM互換のパーソナル・コンピュータの爆発的な成長は、公的に入手可能な電気的および機械的インターフェイス規格が多数あるためと分かります。他の多数の個人向けコンピュータ・システムは商業的に失敗しました。それらのメーカーがインターフェイスを公表しなかったり、そのシステムが既存のよく知られた規格と互換性がなかったからです。

#### 644対644a対LVDM対M-LVDS

規格化団体はLVDS(TIA/EIA-644で定義)を考案し、ポイント・ツー・ポイントのシンプレックス・インターフェイスで、ドライバとレシーバが接続された汎用目的の電気的層仕様を提供しました。この規格はレシーバの入力リーク電流が20μAより小であることを要求しており、これがレシーバの入力インピーダンスの必要条件になります。図1-10はドライバの試験回路です。

644に準拠するデバイスは、ポイント・ツー・ポイント通信にて急速かつ広範に受け入れられましたが、644規格はマルチドロップ動作に必要なドライバ特性を定量化していません(先に述

べたように、マルチドロップ・アプリケーションには複数のレシーバと1個のドライバがあります。)644レシーバのリーク電流20 $\mu$ Aという条件は、1個のレシーバだけが接続されている場合、ドライバ出力電圧にわずかな影響しか与えません。しかし、ドライバに接続されるレシーバ数が増えるにつれて、この影響はもっと顕著になります。そこで、TIA/EIA-644-Aと指定されるLVDSの改訂版は、マルチドロップ構成で使用されるLVDSデバイスのドライバ条件を規格化しています。ドライバ出力に要求される全負荷試験により、644-A準拠デバイスを特定します。図1-11は、644-A試験回路を示します。これによって、マルチドロップ構成における32個のレシーバ接続を保証します。

図1-10. TIA/EIA-644ドライバ出力試験回路

半2重のポイント・ツー・ポイントあるいはマルチポイントのバス対、単方向ポイント・ツー・ポイントあるいはマルチドロップのバス間のドライバに関する明確な相違は、出力がスイッチするときのドライバへの負荷です。ライン端から伝送する場合、他ドライバからの反射防止に使用する終端抵抗に並列な特性インピーダンス $R_0$ の伝送ラインがドライバの負荷になります。したがって、適正に終端されていれば終端抵抗値は $R_0$ になり、等価負荷は $R_0$ /2となります。バスの中央にあるドライバの負荷は並列の2本の伝送ラインであり、時間とともに変化する $R_0$ の負荷です。また、反射防止にはラインの両端に $R_0$ /2の終端抵抗が必要なので、定常状態の負荷も $R_0$ /2になります。

マルチポイントのLVDSのようなドライバへの必要性が急速に現れ、TIとナショナル・セミコンダクタが固有のソリューションを提供しました。TIはドライバのLVDMファミリを提供しました。これは、出力電流が2倍である以外は644LVDS規格に準拠しています。これらLVDMドライバは、マルチドロップある

いはポイント・ツー・ポイント接続でのノイズ・マージンを高めるのにも有効です。

これらの固有のソリューションは必ずしも互換性があるわけでなく、厳しいマルチポイント・インターフェイスデバイスの必要条件に対処したものではありませんでした。それに答えて、TIAの技術委員会はTIA/EIA-899を開発し、マルチポイント環境でのLVDSの利点を規格化しました。TIA/EIAはマルチポイントLVDSあるいはM-LVDSとしてよく知られたこの規格を承認し、2002年の初期に発行しました。TIはこの規格の開発に参加し、それに完全に準拠した製品を開発しました。

TIA/EIA-644-AのLVDSおよびTIA/EIA-899は、ともにANSI公認の国際規格であり、より高レベルの規格がデータ・インターフェイスの電気的層について両者を参照しています。この高レベル規格は、機械的およびプロトコルの必要条件を取り扱っています。

図1-11. TIA/EIA-644-Aドライバ出力試験回路

#### LVDS/M-LVDSの要約

LVDSの最も魅力的な特長には、その高信号レート、低消費電力、および電磁的互換性があります。以下に続く節はこれらの利点の要約です。また、2章の「LVDSおよびM-LVDSライン回路特性と特長」ではより詳細な説明を行います。

#### 信号レート

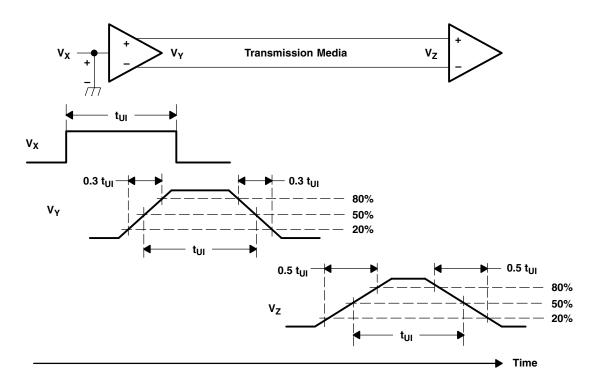

単位時間あたりの状態変化数をインターフェイスの信号レートと定義します。状態変化間の単位インターバル時間t<sub>UI</sub>を知れば、単位インターバルの逆数として信号レートを求めることができます。

TIA/EIA-644-AおよびTIA/EIA-899は、ドライバ出力の遷移時間が単位インターバルの30%以下であり、その下限がそれぞれ260psおよび1nsであることを要求しています。また、レシーバ入力での遷移時間が単位インターバルの50%以下であることを推奨しています。このドライバ出力の立ち上がり時間と、レシーバ入力の立ち上がり時間との時間差は、接続媒体を通しての信号劣化を許容しています。

規格により要求されるドライバの遷移時間と、推奨のレシーバ入力立ち上がり時間とを結合して、LVDSは理論的最大信号レートの1.923Gbps、M-LVDSは500Mbpsをサポートしています。またこの規格では、より低い信号レートとなる長い遷移時

間も可能です。ここで、この規格がバスとのインターフェイスでの特性について定義しており、ライン・デバイスについてではないことに注意願います。もし規格の準拠が必要なければ、ライン・デバイスは260psより高速の遷移時間およびより高信号レートをサポートできます。

ある特定のライン・デバイスについて最低の信号レートを見積もる場合、設計者は最大出力遷移時間を使用すべきです。例えばSN65LVDS31の場合、20%から80%で定義された最大差動出力遷移時間は600psです。立ち上がり時間と単位インターバルに30%の関係を使用すると、単位インターバル600ps/0.3 = 2000psすなわち500Mbpsの信号レートの規格を、このドライバがサポートできると分かります。この30%ルールは保守的であり、ユーザは適切なタイミング配分によりもっと高い信号レートが得られます。

#### 電力

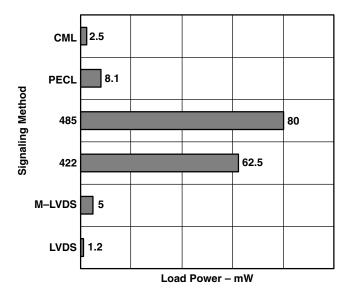

名前が意味するように、LVDSは低電圧信号規格です。LVDSの出力ドライバは、 $100\Omega$ 負荷に対して標準値で350mVを提供します。これは負荷に約1.2mWを供給することになります。図1-12はLVDSと他の差動信号技術の負荷電力を比較し、LVDSが他の信号アプローチの1.5%から50%であることを示しています。一般に、低負荷電力はインターフェイス全体の低電力と強い相関があります。

図1-12. 差動信号の負荷電力の比較

#### 電磁的適合性

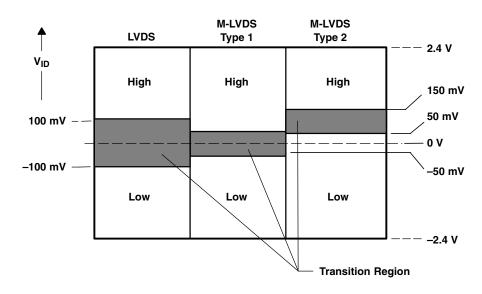

差動信号のため、LVDSは電磁的ノイズの中で動作できると同時に、自身のノイズ輻射を最小にします。また、外部から結合した同相ノイズが差動レシーバの入力範囲内の場合、差動信

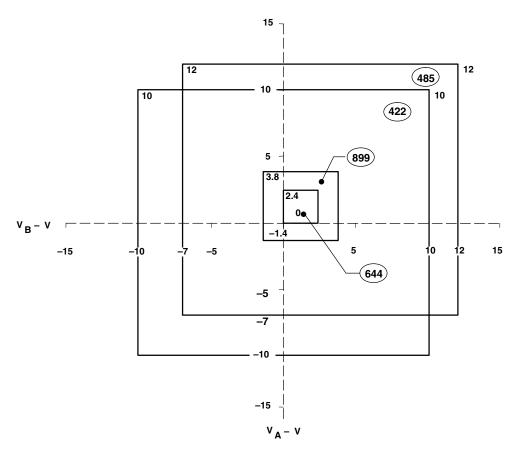

号はそれを除去できます。図1-13は、異なるTIA/EIA規格のインターフェイスの電圧範囲を示します。この図にECL、CML、あるいはその他の非公式な規格を含めようとすると、単一仕様がなく類似したデバイスの仕様書のファミリであるため、含めるのが困難あるいは不可能です。これは興味深い着眼点です。

図1-13. TIA/EIA規格の電圧範囲

#### 参考文献

- 1. TIA/EIA-644: 低電圧差動信号(LVDS)インターフェイス・デバイスの電気的特性 1996年

- 2. TIA/EIA-899:マルチポイント低電圧差動信号(M-LVDS)の電気的特性

- 3. Hayt, William H.著 Engineering Electromagnetics マクグローヒル社 1974年 407-424

#### 第2章

### LVDSおよびM-LVDSの ライン・デバイスの特性と特長

本章は第1章に示した導入の題材を基にして、ライン・デバイスの特長とそのシステム性能への影響に関する洞察を読者に提供しようと思います。また本章は、TIA/EIA-644-Aおよび-899規

格に特有の必要条件を、全体の性能に影響する規格化されていない特性とともに説明します。

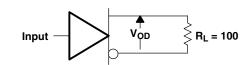

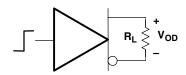

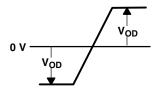

図2-1. V<sub>OD</sub>の定義

#### ドライバ出力電圧

ドライバの主要な機能は、1あるいは2本の伝送ラインに電磁波を送出することです。先に説明したように、これは抵抗(小抵抗値)の両端に電圧を発生するのと等価です。ほとんどのデバイス仕様で差動出力電圧はV<sub>OD</sub>と表記され、反転出力を基準にしています。最小および最大出力電圧はともに重要なパラメータであり、最小出力電圧はインターフェイスの最小ノイズ・マージンを規定し、最大出力電圧はバスに接続されたデバイスの入力電圧範囲を規定します。

TIA/EIA-644-Aドライバは100 $\Omega$ の両端に247mVから454mVの $V_{OD}$ を発生しなければならず、899ドライバはさらに大きな480mVから650mVの電圧を、より小さな負荷の50 $\Omega$ で必要になります。この相違の理由は、先に述べたポイント・ツー・ポイントに対するマルチポイント環境の余分なノイズ要因によります。

基本機能以外に、相補出力の対称性がラインからのノイズ輻射に関する重要な特性のひとつになります。すなわち、信号ペアの各導体を流れる電流は、理想的には等しく方向が反対です。しかし、一般に理想状態を実現するのは非常に高価になります。したがって、ある程度の不平衡と呼ばれる不均等がその2電流

間に常にあることを意味します。不平衡は、相補ドライバ出力 回路または負荷の電気的特性の相違か、あるいは出力スイッチ ング遅延時間の相違の結果として発生します。スイッチングの 不平衡期間に発生する同相成分は高周波であり、かつ容易に放 射されるため、後者の件は特に重要です。

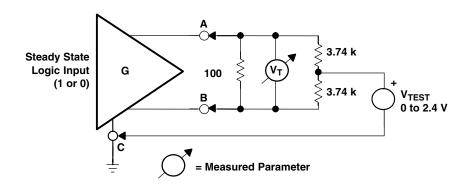

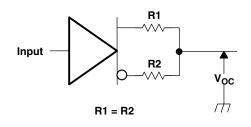

その点に関して重要な差動ドライバのパラメータは、同相出力電圧 $V_{OC}$ (時には $V_{OS}$ とも記す)です。これは2つの相補出力電圧の代数的な平均値です。このドライバ特性は図2-2に示すように、ラインの両端に接続した2個の等しい抵抗間のノードを直接測定します。この同相出力は定常状態 $V_{OC(SS)}$ とピーク・ツー・ピーク $V_{OC(PP)}$ のパラメータに分解できます。このときの輻射ノイズの基本波周波数は、 $V_{OC(SS)}$ について $0.5/t_{UI}$  Hz、および $V_{OC(PP)}$ について $3/t_{UI}$  Hzおよびそれ以上になります。

$V_{OC(PP)}$ パラメータが小さいほど、インターフェイスのノイズ 輻射特性は小さくなります。TIA/EIA-644およびTIA/EIA-899は、ともにそのドライバの $V_{OC(PP)}$ が150mV以下であることを要求しています。データ・ラインのノイズ輻射能力を比較する場合、 $V_{OC(PP)}$ はシングルエンド信号の電圧振幅と直接比較が可能であるため、この点に関するシングルエンド信号に対する差動の優位性が明瞭になります。

図2-2. ドライバ同相出力電圧の測定用回路

#### 差動入力電圧スレッシュホールド

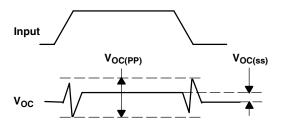

伝送ラインへの入力信号はドライバの出力電圧になり、差動レシーバはドライバから入ってきたものを検出しなければなりません。最初に考察すべきレシーバのパラメータは、差動入力電圧のスレッシュホールド(しきい値) $V_{IT}$ です。これは、レシーバの出力状態を切り換えるのに必要な電圧を定義します。規定された最大および最小 $V_{IT}$ がスレッシュホールドに関するリミットになります。それより高い・低いという差電圧は、レシーバ出力が適正なロジック状態を示す保証になります。

TIA/EIA-644-A規格は、全動作範囲および入力同相電圧範囲において $V_{IT}$ の最大値100mVおよび最小値-100mVを規定しています。したがって、最小ドライバ出力電圧が247mVなので、差動

ノイズ・マージンは最悪ケースで147mVになります。このマージンは小さい値に思えるかもしれませんが、十分に平衡した差動伝送システムでは、干渉があってもほとんど差動ノイズを引き起こしません。

TIA/EIA-899の場合、400mVの差動ノイズ・マージンを得るために、高いドライバ出力電圧の最小値に加えて、レシーバはタイプ1レシーバで $V_{IT}$ の最大値50mVおよび最小値-50mVでなければなりません。また、TIA/EIA-899のタイプ2レシーバは、 $V_{IT}$ の最大値を150mVおよび最小値を50mVに規定しています。このタイプ2レシーバの $V_{IT}$ オフセットにより、0Vの差電圧が適正なバス状態になります。これはワイド・ロジック信号やフェイル・セーフ対策に有効です。図2-3は入力電圧スレッシュホールドを図形で要約したものです。

図2-3. LVDSおよびM-LVDS差動入力信号スレッシュホールド

最大および最小スレッシュホールド間の差動入力電圧は遷移 領域にあり、レシーバの出力状態が不定になります。このとき の出力は、ハイ、ロー、あるいはその両状態の途中になります。 遷移時の出力動作の時間的な変化は、レシーバの帯域と入力電 圧の時間的な変動に依存します。

ここで、LVDS ライン・レシーバが約100,000倍のゲインを持つ差動アンプであると考えます。すると $V_{IT}$ は、出力がハイとローの中点にあるときの入力電圧になります。そして、ヒステリシスのためのフィードバックがなければ、入力電圧がスレッシュホールドよりわずか数十 $\mu$ V上あるいは下にあるだけで、出力はハイあるいはロー状態にスイッチします。システムにはこの差動ノイズが多くありがちで、もしそれがスレッシュホールドに近い場合、レシーバ出力の発振の原因になります<sup>2</sup>。

しかし幸いなことに、高周波におけるゲインは、デバイスが入力信号に載ったノイズに反応しない点まで低下します。その経験的な目安は、入力遷移領域( $V_{IT(MAX)} - V_{IT(MIN)}$ )を $10 \times t_T$ 以下で横切ることです。ここで、 $t_T$ はレシーバ出力が20%から80%に変化する遷移時間です。例えば、出力遷移時間が1nsのレシーバでは、入力信号が遷移領域を10ns以下で横切るようにします。設計上この入力遷移時間を保証できない場合、内部帰還回路による入力電圧ヒステリシスを持つレシーバを推奨します。TIには25mVのヒステリシスを持つLVDSおよびM-LVDSレシーバがあります。

$^2$ この条件については、本章の後にある「フォールト許容度およびフェイルセーフ・レシーバ」の節を参照願います。

#### 同相入力電圧範囲

第1章の図1-6とその関連説明を参照すると、ノイズは両信号ラインに共通であり、それが除去されるから差動信号は良く機能するとあります。しかし、他の全デバイスと同様に、差動レシーバが除去できるノイズの大きさと周波数には限度があります。したがって、一般にV<sub>ICR</sub>と記述されるレシーバの同相入力電圧範囲を規定する必要があります。インターフェイス・デバイスの同相入力電圧範囲は、可能な半導体技術、信号レート、ケーブル・インピーダンス、伝送距離の目標、および環境に関連する他の要素、という非常に多くの要素を考慮した折衷を表します。

完全な平衡差動伝送ラインでのEMIの影響は、2本の導体の各々に等しい純粋な同相電圧の誘起になります。この誘起同相電圧の大きさは、いくつかの要素の関数になります。すなわち、ノイズ源の強度、方向、および近接度、さらにあらゆるシールド効果、および伝送システムの同相インピーダンス特性です。EMIにより誘起される同相電圧の性質を正確に予測するのは困難ですが、常にある一定の量が存在すると考えるべきです。

グランドの電位差は、もうひとつの主要な同相ノイズ電圧源です3。それはEMIや電力分配システム、あるいはローカル電源のグランド帰路電流によって発生します。同相電圧によって誘起されるグランド電位のシフトの大きさを予測するのは、これもまた非常に困難です。設計者は各種の設置に配慮し、優れた設計およびレイアウト手法を用い、これらの問題を低減あるいは除去する必要があります。

同相除去は完全な差動レシーバに固有の特長であり、オペアンプのような他の差動デバイスとまったく同様です。差動アンプやレシーバが除去できる同相電圧の程度は、いくつかの要素の関数になります。可能なかぎり理想に近い平衡を保証するには、レシーバ・デバイスとその接続に関する電気的および機構的設計を注意深く行う必要があります。設計者はアッテネータ(減衰器)を使用して、デバイス入力から見える同相電圧を低減でき

ます。ただし、一般に差動信号も比例して減衰します。このアッテネータには能動帰還回路を使用して、受信した同相電圧を検出および部分的に補償し、差動信号成分より同相成分をより多く減衰できます。また、このアッテネータは応答時間が有限であり、そのため周波数が増加すると減衰量が低下します。

受動フィルタ終端回路も、レシーバ入力端子から見える同相 ノイズを差動信号よりも減衰できます。中点にコンデンサを接 続した分圧終端抵抗に接続した同相チョークあるいはバランが、 しばしばこのフィルタ実装に使用されます。

レシーバ同相入力電圧は、両入力の電圧 $V_{IA}$ および $V_{IB}$ の平均値です。第1章の図1-6からこれら2電圧を加算して2で割ると、定義式より下記の同相電圧の表現になります。

$$V_{IC} = \frac{V_{IA} + V_{IB}}{2} = \frac{V_{OA} + V_{N} + V_{OB} + V_{N} + V_{G}}{2}$$

これを整理すると、

$$V_{IC} = \frac{V_{OA} + V_{OB}}{2} + V_{N} + V_{G}$$

$$ZZ_{\text{C}}, \frac{V_{\text{OA}} + V_{\text{OB}}}{2} = V_{\text{OC}} \text{ $x$ oc.}$$

$V_{IC} = V_{OC} + V_N + V_G$ になります。

この式は、レシーバの同相入力電圧範囲がノイズの項と同様に、ドライバの $V_{OC}$ を含むことを意味しています。また、 $V_{IC}$ が時間変化する成分と同様に、時間的に定常状態(DC)の成分を含むと認識することが重要です。

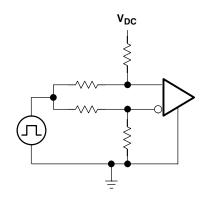

差動ライン・レシーバの出力状態は2つしかないので、TIはその同相除去対周波数をGO/NO-GO試験として判定しています。 差動アンプに適用される同相除去比(CMRR)のようなパラメータには、差動ライン・レシーバの内部回路のノードにおける意味しかありません。その代わり弊社は、定常状態(DC)のV<sub>IT</sub>の最大・最小値(LVDSの場合、100mV)および-100mV)および同相試

図2-4. 差動ライン・レシーバの同相除去試験

$^3$ 同相ノイズ電圧およびLVDSに関する情報は、他にもいくつかのTIアプリケーション・レポートにあります。「同相ノイズの統計的調査(SLLA057)」、「次世代レシーバの厳しい環境におけるLVDS(SLLA061)」、および「ノイズ問題の解決(SLLA073)」。

験パルスを図2-4に示すように両入力に印加して、差動ライン・レシーバの同相除去を評価しています。この同相試験パルスは V<sub>ICR</sub>を横切るので、そのときレシーバ出力の状態が変化しないことを検証します。この試験はパルス・エッジで発生する高調波により、同相成分の周波数応答を測定します。またこの試験では、デバイスの意図した最小単位インターバルの20%以下の遷移時間を一般に指定します。例えば、500psの遷移時間にするとギガHz帯までの高調波を供給します。

表2-1は、種々の差動信号デバイスの同相ノイズ電圧に対する許容度を示します。また、広い $V_{ICR}$ のLVDSレシーバであるSN65LVDS33の紹介もしています。TIのLVDSファミリ製品には、TIA/EIA-644-Aで規定された $V_{ICR}$ の最小値を超える、広い同相入力電圧範囲のレシーバがいくつかあります。 $V_{ICR}$ が広いLVDSは、標準LVDSには本来厳しいであろう環境でも使用できます。これらのデバイスの多くは、よく知られたレシーバとピン互換性があります。

表2-1. 差動信号規格のノイズ電圧許容度

| STANDARD                            | MAXIMUM<br>RECEIVER<br>INPUT<br>VOLTAGE | MINIMUM<br>RECEIVER<br>INPUT<br>VOLTAGE | RECEIVER<br>COMMON-MODE<br>INPUT VOLTAGE<br>RANGE              | MAXIMUM DRIVER<br>COMMON-MODE<br>OUTPUT VOLTAGE | MINIMUM DRIVER<br>COMMON-MODE<br>OUTPUT VOLTAGE | MAXIMUM<br>COMMON-MODE<br>NOISE VOLTAGE                                                                            |

|-------------------------------------|-----------------------------------------|-----------------------------------------|----------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Generic                             | V <sub>I(MAX)</sub>                     | V <sub>I(MIN)</sub>                     | V <sub>ICR</sub> =<br>V <sub>I(MAX)</sub> -V <sub>I(MIN)</sub> | V <sub>OC(MAX)</sub>                            | V <sub>OC(MIN)</sub>                            | $ \begin{aligned} &V_N + V_G = \\ &MIN(V_{I(MAX)} - \\ &V_{OC(MAX)}, \\ &V_{OC(MIN)} - V_{I(MIN)}) \end{aligned} $ |

| ECL <sup>4</sup>                    | -0.88                                   | -1.81                                   | 0.93                                                           | -1.25                                           | -1.417                                          | 0.37                                                                                                               |

| PECL                                | 4.12                                    | 3.19                                    | 0.93                                                           | 3.75                                            | 3.583                                           | 0.37                                                                                                               |

| LVPECL <sup>5</sup>                 | 2.42                                    | 1.355                                   | 1.065                                                          | 2.005                                           | 1.73                                            | 0.375                                                                                                              |

| TIA/EIA-644-A                       | 2.4                                     | 0                                       | 2.4                                                            | 1.375                                           | 1.125                                           | 1.025                                                                                                              |

| TIA/EIA-899                         | 3.8                                     | -1.4                                    | 5.2                                                            | 2.1                                             | 0.3                                             | 1.7                                                                                                                |

| SN65LVDS33<br>with M-LVDS<br>Driver | 5                                       | -4                                      | 9                                                              | 2.1                                             | 0.3                                             | 2.9                                                                                                                |

| SN65LVDS33<br>with LVDS Driver      | 5                                       | -4                                      | 9                                                              | 1.375                                           | 1.125                                           | 3.625                                                                                                              |

| TIA/EIA-485-A                       | 12                                      | <b>-</b> 7                              | 19                                                             | 3                                               | -1                                              | 6                                                                                                                  |

| TIA/EIA-422-B                       | 10                                      | -10                                     | 20                                                             | 3                                               | -3                                              | 7                                                                                                                  |

#### 信号レート

ライン・ドライバあるいはレシーバの基本機能は、離れた場所でのロジック状態変化の再生です。信号レートすなわちデータ信号レートは、単なる単位時間当たりの状態変化の数です。また、信号レートはデータ、クロック、あるいはハンドシェーク信号での区別はなく、バスのアーキテクチャーやプロトコルに依存しません。それは、単に1ビットの伝送あるいは受信のレートについて述べたものです。したがって、ビット/秒(bps)という単位が使用されます(これはバイナリ伝送システムにおけるボーという名称にとって代わりました)。

信号レートは、ライン・ドライバ、接続媒体、およびライン・レシーバというデータ交換回路の帯域条件を設定する際に重要

なパラメータです。2個の連続した状態変化を伝送すると、回路に沿って電圧および電流パルスの最初と最後を形成します。 誰もが想像する通り、信号チェーンの他端で適正に受信できるようにするには、パルス期間がとり得る最小限界があります。

回路の最小パルス期間すなわち最大信号レートを規定あるいは記述する、信号品質の基準がなければなりません。多くの仕様が、パルス期間に対する状態間の遷移に要する時間の量で、このバイナリ・データ・パルスの品質について述べています。TIA/EIA-644とTIA/EIA-899および他の仕様は、この基準を定義しています。これらの規格は、パルス期間を単位インターバルすなわちtulとして定義し、最大遷移時間をtulの少数として定義しています。図2-5にTIA/EIA-644-Aの信号品質基準を示します。

<sup>4</sup>100Eシリーズ、高性能ECLデータ、モトローラ、DL140/D、1995年 <sup>5</sup>MC100EP16 データシート、オン・セミコンダクタ、2001年4月

図2-5. TIA/EIA-644-A信号品質推奨条件

伝送ラインの他端で信号遷移時間が0.5 tulに達すると、ひとつのインターフェイス回路の最小パルス期間すなわち最大信号レートを達成したことになります。しかし、ライン・デバイスの信号レート能力を評価する場合、たいてい無損失ラインを想定し、ドライバとレシーバの両方に0.3 tulを適用します。(遷移時間の0.5 tulまでの減衰が伝送媒体での損失を考慮し、ライン・デバイスを考慮していないからです。)このことは、ライン・デバイスの信号レート能力が、その出力の立ち上がり・立ち下がり時間で決まると言えることを意味します。また、この条件で良い近似結果が得られています。

#### 注記

図2-5は、全体の信号振幅を測定した遷移時間を示し、レシーバのスレッシュホールドに関連したものではありません。例えば $0.5~t_{UI}$ の遷移時間でも、最小パルス期間で定常状態(DC)レベルを取り込めます。

信号レートはデータ・パルスの実際の波形を基準にすると、サンプリングの瞬間に対してバス状態が適正になる場合を無視することになります。サンプリング時間が安定であり続けると仮定すると、バス状態の変化時間の変動は、サンプリングに必要

なセットアップ・タイムあるいはホールド・タイムを足したり引いたりします。この変動を総称してジッタと呼び、いくつかのライン・デバイスの信号源から発生します。

理想的には、ライン・ドライバあるいはレシーバは、その入力で状態変化が発生してからある一定の時間後に、その出力で状態を変化します。しかし実際には、温度、電源電圧、製造プロセス、先行ビットの順序、およびノイズにより遅延時間は変動します。これらの要素はすべて、状態がサンプリングおよびその先の処理に適正になるタイミングに影響します。したがって、インターフェイス設計者は伝送システムのタイミングの予定内で、各要素に時間を配分しなければなりません。これらの変動に関する評価と規定に使用される方法は数少ないですが、ここでは一般的な観察と結論について述べます。

最高速インターフェイス・デバイスでは、普通、タイミング情報をデータ内あるいは分離した並列デバイスで符号化し、データとともに送ります。このタイミング情報(クロック)を伝送する方法では、どのタイプのライン・デバイスのジッタにタイミングを配分すべきか決めます。一般的に、クロック符号化データでは高周波ジッタ成分だけが重要であり、並列クロックのアプローチではすべてのジッタ成分が配分の対象になります。

温度や製造プロセスによる遅延時間のバラツキは、周波数的には非常に小さく、デバイスの仕様書に遅延時間のリミット値が指定されています。ほとんどのデバイスは等しい温度と電源電圧で動作するので、製造プロセス変動のみを評価するデバイス間スキュー $t_{SK(PP)}$ と呼ばれる別のパラメータを仕様書は指定しています。このパラメータは、別個にパッケージされたライン・デバイスが、推奨動作範囲で同じ電源電圧および温度において動作する場合の遅延時間です。これに関連するパラメータが出力スキューすなわち $t_{SK(O)}$ です。これは、同一のライン・デバイスIC内にある2個の回路間の遅延時間差です。モノリシック・デバイスでは2回路は同じ製造プロセスで作られ、その遅延時間は非常に整合がとれています。

伝送前に発生した状態変化やビットは、ライン・デバイス内の最初の動作点および遅延時間に影響します。この影響について、仕様書はしばしば2つのパラメータを指定しています。まず、パルス・スキューすなわち $t_{SK(P)}$ は、定常状態の入力状態からハイからローおよびローからハイへ遷移する遅延時間の単なる差です。これはパターン依存性がある遅延時間変動の最大値を表します。次に、 $t_{SK(P)}$ の部分集合である決定論的ジッタすなわち $t_{SK(P)}$ です。これは擬似ランダム・ビット順序による遅延時間変動を測定したものであり、このジッタ成分の統計的記述についての中間動作点を含みます。このジッタは周波数(信号レートか、それ以上)的に大きく影響します。

最後に、ノイズによるジッタの影響をライン・デバイスについて評価し、その仕様を設定するのは困難です。したがって、実際のインターフェイスとその環境で評価するのが最善です。仕様書は、ノイズ起因のジッタをデバイスの一般特性の節で以下

のように示すことができます。すなわち、ランダム・ジッタのパラメータの設定、多数チャネルのライン・デバイスについて各種動作の組み合わせにおけるジッタのピーク・ツー・ピーク値の比較を表示、遅延時間対同相あるいは差動入力電圧のグラフ化などです。

#### 電力消費

高信号レートとローパワーは、しばしばデータ・ライン・インターフェイスにおいて相互に排他的な特長になります。信号レートが増加するにつれ、電圧を生成するためより多くの電流が必要になり、回路インピーダンスは低下する傾向にあります。電力は電圧と電流の積なので、電力レベルを維持あるいは低減するには、動作電圧の低下が必要になります。これがLVDSおよびM-LVDSライン・デバイスの開発の背後にある動機です。

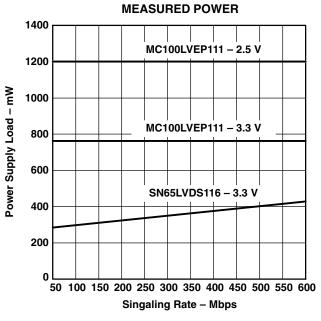

電源および信号電圧を低減する利点が明らかになる一方で、 提案者はグランドに対する低インピーダンスのパスがない完全 な差動ライン終端を使用して、同相電力を最小化するように LVDSおよびM-LVDSの両規格を設計しました。これは、LVDS とECLデバイスを比較すると最も明瞭になります。図2-6のグラフは、10出力ECLリピータと16出力LVDSリピータの電力対信 号レート特性の比較を示します6。LVDSが1.6倍の出力数にもかかわらず、LVDSデバイスが大体半分の電力消費であると分かります。ただし、ほとんどのECL/PECLデバイスは、現在入手可能なLVDSデバイスより高速で動作します。したがって、ECL/PECLの余分な電力が正当化される状況は、ある程度残っています。

図2-6. MC100LVEP111とSN65LVDS116の電力比較

<sup>6</sup>SLLA103「LVPECLとLVDSの消費電力の比較」テキサス・インスツルメンツ株式会社、2001

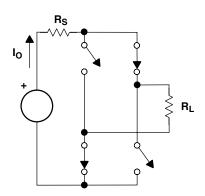

LVDSおよびM-LVDSドライバは、高インピーダンス(負荷に対して)出力を共通に使用することで、この電力の浪費をさらに低減しています。図2-7を参照すると、信号源抵抗( $R_S$ )が増加するにつれ、 $I_O$ は負荷抵抗の変化に敏感でなくなります。これには $R_L$ の変動ばかりでなく、もっと重要な瞬間的な内部の短絡が含まれます。この短絡は、トランジスタが図2-7の理想スイッチに置き換わると、 $R_S$ とグランド間で発生します。

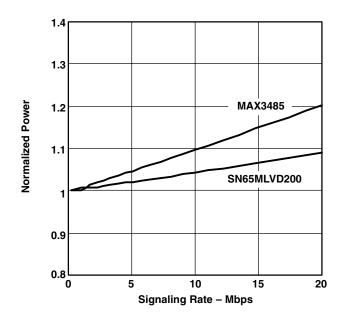

比較的低い出力インピーダンスのドライバ(ほとんどのRS-422とRS485ドライバ)と比較すると、高インピーダンス出力は

増加する信号レートに対して、より安定した電力消費になります。これを説明するため、図2-8にMAX3485(3.3VのRS-485)およびSN65MLVD200(M-LVDSドライバ)の正規化した電力消費を示します7。ここで、次の2点に注目することが重要です。定常状態でMAX3485が142mWを消費するのに、SN65MLVD200はわずか54mWしか消費しません。また、SN65MLVD200の信号レートは200Mbpsまで伸びます。

図2-6. MC100LVEP111とSN65LVDS116の電力比較

図2-8. 電圧モードおよび電流モード・ドライバの、正規化電力対スピードの比較

<sup>7</sup>SLLA106「TIA/EIA-485とM-LVDSの消費電力および動作速度の比較」テキサス・インスツルメンツ株式会社、2001

#### 電源電圧

LVDSおよびM-LVDS規格は約3.3V電源システム向けに設計されましたが、インターフェイス・デバイスの電源電圧を指定していません。インターフェイス設計者がインターフェイス規格を満たせば、LVDSおよびM-LVDSデバイスは大抵の電圧で動作可能です。5VのLVDSデバイスや、SN65LVDS1050のように2.5Vまで動作するデバイスもあります。

#### 信頼性

推奨動作条件内で動作するのであれば、インターフェイス・デバイスは他のシリコンで作られたデバイスと同様の信頼性が得られます。しかし、長い伝送ラインに結合した過渡的なノイズ、あるいはコネクタ・ピン経由の静電気にさらすと、インターフェイス・デバイスは破壊されることがあります。

設計者はインターフェイス・デバイスの一般的なアプリケーションにおけるノイズをランダムなものとみなす必要がありますが、製造者はノイズ源をある種の再現性のあるタイプにモデル化し、集積回路レベルでの許容度を規定します。以下はいくつかの一般的なモデルに関する概要です8。

人体モデル(HBM): HBMは、人体が蓄積した静電気をデバイス経由でグランドへ放電する作用をシミュレートし、100pFのコンデンサと1500Ωの抵抗で構成する直列のRC回路を使用します。

機械モデル(MM): MMは、機械が蓄積した静電気をデバイス 経由でグランドへ放電する作用をシミュレートします。また、 MMは200pFのコンデンサと、標準値で $1\Omega$ 以下の抵抗からなる 直列のRC回路で構成されています。その出力波形は、一般に ピーク電流と与えられた放電電圧の発振周波数で表されます。

デバイス帯電モデル(CDM): CDMは製造装置や製造工程で発生する充放電をシミュレートします。CDMによる静電破壊は、製造時の金属同士の接触で発生する可能性があります。よくある例のひとつに、デバイスが出荷チューブ内をすべり落ち、金属表面と接触する場合があります。CDMは以下のような可能性をとり扱っています。すなわち、まず、電荷がリードフレームやパッケージに常にあり(例えば、出荷時から)、次にピンを通してグランドへ放電し、このとき放電パスにおける静電気に弱いデバイスを破壊するというものです。寄生インピーダンスとデバイスの容量が放電電流を制限します。CDM試験は、パッケージを規定の電圧まで充電し、次にその電圧をパッケージの対象リードを通して放電させるという、2つの部分で構成されています。TIは電界誘導CDM(FCDM)シミュレータを使用して、CDM試験を実施しています。CDM試験を実施しています。CDM試験を実施しています。CDM試験を実施しています。CDM試験を実施しています。CDM試験を実施しています。

上記のノイズモデルの高度な仕様はいずれも、デバイスが基板や筺体に取り付けられる際に、どれだけの過渡ノイズを許容できるかを表すものです。デバイス仕様書では、しばしばバス・ピン(伝送ラインに接続するピン)のESD許容度を電源ピンと分離して規定しています。これは、バス・ピンが取り付け後に最もESDに敏感だからです。残念ながら、デバイスの取り付けはESD特性と最も関係があります。そのため、システムレベルの仕様に沿ったESDに関する要求は、すべてESD試験条件の仕様に完全に含まれなければなりません。

TIが提供するLVDSデバイスには、そのバス・ピンにHBMで15kVのESD保護回路がついています。この優れたESD特性は、TIでは使用されているが、他社にはほとんど無い先進のアナログ用シリコン・プロセス9による直接の成果です。

#### 内蔵終端抵抗

伝送ラインの反射信号を低減するには適切な終端が必要です。 反射信号はデータ・エラーの増加に結びつくため、伝送システム 規格では非常に注意深く終端条件を定義しています。 EIA/TIA-644-Aでは、ライン終端インピーダンスとレシーバを組合せた 「終端レシーバ」 負荷を定義しています。また、この規格はライン終端インピーダンスがない場合のレシーバ特性についても定義しています。 終端レシーバの差動入力インピーダンスは、 $90\Omega$ から132 $\Omega$ の間すなわち111 $\Omega$ ±19%であることと定義しています。

EIA/TIA-644-Aでは、ライン終端インピーダンスが終端レシーバの一部として、終端レシーバから物理的にどれだけの位置にあるべきか特に述べていません。しかし、スタブ(分岐)や反射が無いようにとの注意書きが、いくつか明記されています。ライン終端の理想的な位置は、レシーバに可能なかぎり近づけることです。そうすると、スタブ長がほとんどゼロになります。TIはいくつかのLVDSレシーバに終端抵抗を集積化しました。それによって、エンド・ユーザが外付け部品を購入して取りつける必要がなくなるだけでなく、スタブ長が理想的にほぼゼロになります。

終端抵抗をレシーバ・デバイス内に集積化するのは、ASICに使用するような標準的なデジタル向けシリコン・プロセスでは基本的に不可能です。その理由は、その種のプロセスのほとんどが、この規格の許容条件を満たす抵抗性素子を作りこむのが不可能だからです。TIの終端化レシーバの製造に使用する先進アナログ向けプロセスには、必要な安定した抵抗性素子を提供する独自の工程が追加されています。

<sup>8</sup>SSY010「静電気放電(ESD)」TI、2000

<sup>9</sup>SLLA065「LVDSに関するLinBiCMOSおよびCMOSプロセス技術の比較」テキサス・インスツルメンツ株式会社、2001

TIの内部的に終端化したLVDSレシーバの使用による潜在的な省コストには、購買および在庫コストが含まれます。また、製造、品質管理(QC)、および保守点検(R&M)さらに余分なプリント基板面積もあります。この基板面積の節約は、複数の並列信号パスがある状況において特に顕著になります。TIには8あるいは16チャネルのLVDSレシーバのファミリがあり、その両方に内部終端有り/無しがあります。これらのデバイスは、その各々に関する8あるいは16の終端回路の節約にくわえて、プリント基板の配線レイアウトおよび信号品質を維持するためのスタブの排除が容易になります。

#### フォールトトレランスとフェィルセーフ

フォールト条件は、規格の中で記述はされているが、必ずしも規定されていない特性分野のひとつです。それには、ドライバがパワーオフ、レシーバが接続されていない、および伝送ラインが開放あるいは短絡であるという状態が含まれます。これらの条件は、すべて差動入力電圧をレシーバの遷移領域10まで低下させ、出力状態を不定にします。「フェイルセーフ」は、これらのフォールト条件下でレシーバの動作を定義します。フェイルセーフを対策していないと、ランダムノイズを適正なデータあるいはレシーバの発振として検出することになります。これは、アプリケーションによっては重大なシステム応答問題になります。

経験を積んだデバイス設計者は、数多くのレシーバ設計技術を用いて上記の異なるフォールト条件下でも予期できる応答のレシーバを提供します。遷移領域内での差動入力電圧については、レシーバ出力段からの少量の正帰還により、正方向の入力スレッシュホールドを負方向の入力スレッシュホールドより高くし、応答時のヒステリシスが作れます。この機能により、ヒステリシス値より低い差動ノイズに対して、レシーバ出力の発振を防止します。このフェイルセーフ機能は、出力を予め決めておいた状態にするのではなく、入力が遷移領域に入る前の最後の出力状態を維持します。LVDSおよびM-LVDSレシーバは、感度の高いスレッシュホールドと高信号レートのため、大きなヒステリシス電圧を作るのは不可能であり、またその必要もありません。レシーバの仕様書では、一般に電気的特性の表内で入力ヒステリシス電圧を規定しています。

フォールト条件がレシーバ入力間の高抵抗あるいは開放状態の場合(例えばケーブルの切断)、TI製のほとんどの差動レシーバは、開放フェイルセーフ機能を提供します。この手法は、レシーバ入力がどこにも接続されていない場合、内部の高抵抗をレシーバ入力に接続し、それを内部の適当な電圧でバイアスします。仕様書ではこのフェイルセーフ機能について、特長リスト、ファンクション・テーブル、さらに入力の等価回路図で規定しています。

TIA/EIA-899のM-LVDS規格で規定されるタイプ2レシーバは、他の手段によるフェイルセーフ応答を提供しています。この規格では、タイプ2レシーバが差動入力電圧スレッシュホールドのオフセットを0Vから持ち、ラインが短絡(差動電圧が0V)している場合でも、レシーバが正しいバス状態すなわち正しいレシーバ出力状態を与えることを要求しています。このスレッシュホールドのオフセットにより、スレッシュホールドが0V付近であるタイプ1レシーバよりもノイズ・マージンが低減し、パルス分布(ジッタ)は拡大します。そこで、回路設計者はタイプ2レシーバをタイプ1レシーバに並列に接続すると、入力信号の損失を検出し、タイプ1レシーバ出力をゲートすることができます。

TIはSN65LVDS33のレシーバ・ファミリーに、より洗練されたフォールト検出とフェイルセーフ技術を導入しました。その設計では新回路を追加して、差動入力電圧を監視しています。すなわち、差動入力電圧が遷移領域に600ns以上とどまると、フェイルセーフ回路が出力をハイ状態に強制します。このシステムにより、ドライバのオフや切断、または伝送ラインの短絡という場合に生じる入力信号の損失条件を検出します<sup>11</sup>。

#### 活線挿抜(ホットプラグ)

活線挿抜、ホットプラグ、およびホットスワップとはすべて、バス全体の電源を停止することなく、デバイスを共通データバスへ挿入したり、そこから取り外したりすることです。こうした各語は情報源により、特性や絶縁の程度に関して異なる意味合いを帯びています。本文書では活線挿抜という語を、バスとの接続に関する挿入・抜取りおよび接続されたデバイスへのパワー・サイクリングという一般的な意味で用いています。活線挿抜に関する設計範囲は、デバイス設計とともにパワーマネージメントも含み、システム・アーキテクチャーから部品選定に至る全階層の設計に影響します。

電気的層における活線挿抜に関する2つの主要な問題は、デバイス破壊とデータコラプションです。ライン・デバイス挿入時に、バスとデバイスとの間に大きな電位差があると破壊が起こり得ます。活線挿抜対策の設計がなされた装置の大部分は、信号ピンよりも先にグランドピンが接続して電位が等しくなるように保証しています。しかし、それでも高インピーダンスのデバイスは内部に静電気を蓄積している場合があり、ユーザはデバイスのESD構造によって静電気を放電しなければなりません。したがって、高ESD特性が有利になります。バス上で他のドライバと競合しても、規格によって出力電流が制限されているため、LVDSあるいはM-LVDSデバイスは破壊されません。

バスに接続したノードのパワーサイクリングによってバス信号が乱されないように、その間はライン・ドライバ/レシーバともにバスに対して高インピーダンスである必要があります。電源電圧が0V時のレシーバ入力電流規格、およびライン・ドライ

<sup>&</sup>lt;sup>11</sup>SN65LVDS33の優れたフェイルセーフ機能に関する詳細はSLLA082Aにあります。

<sup>10</sup>本章の「差動入力電圧スレッシュホールド」節を参照。

バのパワーアップ/ダウン時のグリッチ・フリー特性をご覧ください。パワーアップ/ダウン時にグリッチ・フリーなドライバは、電源電圧があるスレッシュホールド以下ではドライバの入力条件にかかわらず、その出力がオフかつ高インピーダンスを維持するように設計されています。この設計によって、低動作電圧時のロジックあるいは電源シーケンスの両方について、ドライバ入力を安定化しています。しばしば、この特長はデータシートの冒頭の箇条書きとしてのみ表記されます。もし規定するならば、ドライバ出力電流の試験条件として表されます。

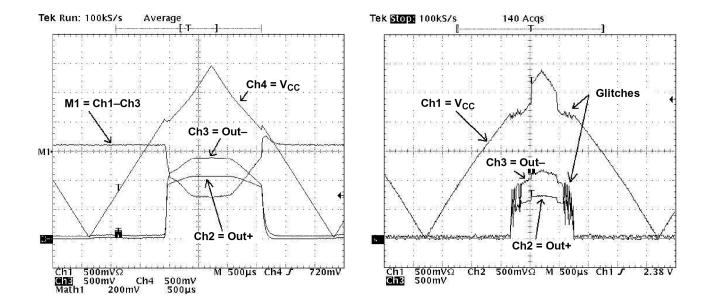

図2-9の左図は、グリッチ・フリーでないドライバの出力に見られるパワーアップ/ダウン時のグリッチを示します。右図は、パワーサイクリング時に単調な出力遷移を示すSN65LVDS050です。

図2-9. パワーアップ/ダウン時の波形

## ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます) 及びTexas Instruments Incorporated(TIJの親会社、以下TIJおよびTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIの標準契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、且つその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、 条件その他のパラメーターと異なる、あるいは、それを超えてなされ た説明で当該TI製品もしくはサービスを再販売することは、当該 TI製品もしくはサービスに対する全ての明示的保証、及び何らか の黙示的保証を無効にし、且つ不公正で誤認を生じさせる行為 です。TIは、そのような説明については何の義務も責任もありません。

なお、日本テキサス・インスツルメンツ株式会社半導体集積回路 製品販売用標準契約約款もご覧下さい。

http://www.tij.co.jp/jsc/docs/stdterms.htm

Copyright © 2004, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

#### 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点 を遵守して下さい。

- 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装) 又は製品単品で取り扱いを行う場合は、接地された導 電性のテーブル上で(導電性マットにアースをとったも の等)、アースをした作業者が行うこと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる 全ての装置類は、静電気の帯電を防止する措置を施す こと。

- 前記のリストストラップ・導電性手袋・テーブル表面 及び実装装置類の接地等の静電気帯電防止措置は、常 に管理されその機能が確認されていること。

- 2. 温·湿度環境

- 温度:0~40℃、相対湿度:40~85%で保管・輸送 及び取り扱いを行うこと。(但し、結露しないこと。)

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に 従い基板実装すること。

- 4. 機械的衝擊

- 梱包品(外装、内装、個装)及び製品単品を落下させたり、 衝撃を与えないこと。

- 5. 熱衝撃

- はんだ付け時は、最低限260°C以上の高温状態に、10 秒以上さらさないこと。(個別推奨条件がある時はそれ に従うこと。)

- 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。 (不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上